#### ISL28133A

Single Micro-Power, High-Precision, RRIO, CMOS Operational Amplifier

## **Description**

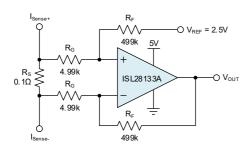

The ISL28133A is a single micropower, chopper-stabilized operational amplifier designed for precision and efficiency in compact spaces. With a quiescent current of just 22µA and rail-to-rail input/output, it delivers exceptional performance across a wide supply range of 1.8V to 5.5V. Its ultra-low input offset voltage (10µV max) and minimal noise make it ideal for high-accuracy applications like medical instrumentation, temperature sensing, and electronic weigh scales.

The low supply current of  $22\mu A$  and wide input range enable this device to be an excellent high-precision op amp for a wide range of application where low power is paramount.

The device operates across the temperature range of -40°C to +125°C and is available in a wide variety of packages.

| Part Number | Package<br>Description | Body Size (nom) |

|-------------|------------------------|-----------------|

| ISL28133A   | SC70-5                 | 1.25mm×2.00mm   |

| 10220100A   | SOT23-5                | 1.60mm×2.90mm   |

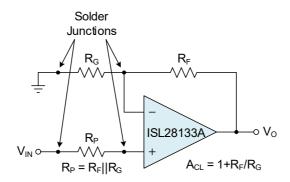

Figure 1. Typical Application Circuit - Bidirectional Current Sense Amplifier

#### **Features**

- Single-Supply Operation: 1.8V to 5.5V

- Rail-To-Rail Input and Output

- Low Input Offset Voltage: ±10µV (Maximum)

- Low Offset Drift: ±0.075µV/°C (Maximum)

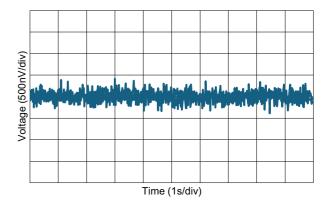

- 0.01Hz to 10Hz Noise: 1.1µV<sub>PP</sub>

- Low Supply Current: 22µA

- Gain Bandwidth Product: 340kHz

- Unity-Gain Stable

- Temperature Range: -40°C to 125°C

### **Applications**

- Low-Ohmic Current Sensing

- Temperature Measurement

- Precision/Strain Gauge Sensors

- High-Gain Amplifiers

- Smoke Detectors

- Appliances

- Medical Equipment

- Motor Control

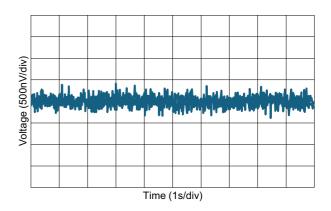

Figure 2. 0.1Hz to 10Hz Noise

# **Contents**

| 1. | Pin Ir | nformation  | n                                           | 3  |

|----|--------|-------------|---------------------------------------------|----|

|    | 1.1    | Pin Ass     | signments                                   | 3  |

|    | 1.2    |             | scriptions                                  |    |

| 2. | Spec   | ifications  | ·                                           | 4  |

|    | 2.1    |             | te Maximum Ratings                          |    |

|    | 2.2    |             | mended Operating Conditions                 |    |

|    | 2.3    |             | al Specifications                           |    |

|    | 2.4    |             | cal Specifications                          |    |

| 3. | Typic  | al Perforn  | mance Graphs                                | 6  |

| 4. | Detai  | led Descr   | ription                                     |    |

|    | 4.1    |             | •<br>ew                                     |    |

|    | 4.2    | Functio     | onal Block Diagram                          | ξ  |

|    | 4.3    | Feature     | e Description                               |    |

|    |        | 4.3.1       | Low Offset and Drift                        |    |

|    |        | 4.3.2       | Rail-To-Rail Input and Output (RRIO)        |    |

|    |        | 4.3.3       | Layout Guidelines for High Impedance Inputs | 10 |

|    |        | 4.3.4       | Input and Output ESD Protection             | 10 |

| 5. | Appli  | cation Inf  | formation                                   | 10 |

|    | 5.1    | Typical     | Applications                                | 10 |

|    |        | 5.1.1       | High Gain, Precision DC-Coupled Amplifier   | 10 |

|    |        | 5.1.2       | Design Procedure                            | 11 |

|    | 5.2    | Layout      | Considerations                              | 12 |

| 6. | Pack   | age Outlir  | ne Drawings                                 | 13 |

| 7. | Orde   | ring Inforr | mation                                      | 13 |

| 8. | Revis  | sion Histo  | ory                                         | 13 |

| Δ  | FCAI   | ) Design I  | Information                                 | 14 |

# 1. Pin Information

# 1.1 Pin Assignments

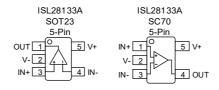

Figure 3. Pin Assignments - Top View

## 1.2 Pin Descriptions

| Pin Name  | ISL28133A | ISL28133A | Function                   |

|-----------|-----------|-----------|----------------------------|

| PIII Name | SOT23     | SC70      | Function                   |

| IN+       | 3         | 1         | Non-inverting Signal Input |

| IN-       | 4         | 3         | Inverting Signal Input     |

| OUT       | 1         | 4         | Signal Output              |

| V+        | 5         | 5         | Positive Supply Voltage    |

| V-        | 2         | 2         | Negative Supply Voltage    |

## 2. Specifications

## 2.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                       | Minimum | Maximum | Unit |

|-----------------------------------------------------------------|---------|---------|------|

| Supply Voltage, V+ to V-                                        | -       | 6.0     | V    |

| Input Voltage, IN± to GND                                       | -0.5    | 6.0     | V    |

| Input Voltage, IN+ to IN-                                       | -       | 6.0     | V    |

| Input Current                                                   | -       | 20      | mA   |

| Output Short-Circuit                                            | Conti   | nuous   | mA   |

| Ambient Temperature, T <sub>A</sub>                             | -40     | 125     | °C   |

| Junction Temperature, T <sub>J</sub>                            | -       | 150     | °C   |

| Storage Temperature, T <sub>stg</sub>                           | -65     | 150     | °C   |

| ESD Ratings                                                     |         |         |      |

| Human-Body Model (HBM), per ANSI/ESDA/JEDEC JS-001              | -       | ±2      | kV   |

| Charged-Device Model (CDM), per JEDEC specification JESD22-C101 | -       | ±2      | kV   |

| Latch-Up (Tested per JESD78B), T <sub>A</sub> = 125°C           | -       | ±100    | mA   |

## 2.2 Recommended Operating Conditions

| Parameter                    | Symbol         | Min        | Max        | Unit |

|------------------------------|----------------|------------|------------|------|

| Supply Voltage [(V+) – (V-)] | V <sub>S</sub> | 1.8        | 5.5        | V    |

| Input Voltage Range          | VI             | (V-) - 0.1 | (V+) + 0.1 | V    |

| Output Voltage range         | Vo             | V-         | V+         | V    |

| Ambient Temperature          | T <sub>A</sub> | -40        | 125        | °C   |

## 2.3 Thermal Specifications

| Parameter          | Package            | Symbol                         | Conditions          | Typical<br>Value | Unit |

|--------------------|--------------------|--------------------------------|---------------------|------------------|------|

| Thermal Resistance | 5 Ld SOT23 Package | θ <sub>JA</sub> <sup>[1]</sup> | Junction to ambient | 188              | °C/W |

| memai Resistance   | 3 Lu 30123 Fackage | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 137              | °C/W |

| Thermal Resistance | 5 Ld SC70 Package  | θ <sub>JA</sub> [1]            | Junction to ambient | 227              | °C/W |

| Thermal Nesistance | 3 Lu 3070 Fackage  | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 141              | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See TB379 for details.

# 2.4 Electrical Specifications

$V_S = (V+) - (V-) = 5V$  at  $T_A = 25$ °C,  $R_L = 10$ k $\Omega$  connected to  $V_S/2$ ,  $V_{CM} = V_S/2$  (unless otherwise noted)

| Parameter            | Symbol          | Test Condition                              | Min <sup>[1]</sup> | Тур | Max <sup>[1]</sup> | Unit |

|----------------------|-----------------|---------------------------------------------|--------------------|-----|--------------------|------|

| DC Parameters        |                 |                                             |                    |     |                    |      |

| Input Offset Voltage | V               | V <sub>S</sub> = 5V, V <sub>CM</sub> = 2.5V | -                  | ±2  | ±10                | μV   |

| input Onset voltage  | V <sub>OS</sub> | T <sub>A</sub> = -40°C to 125°C             | -                  | -   | ±17                | μV   |

<sup>2.</sup> For  $\theta_{\text{JC}},$  the case temperature location is taken at the package top center.

$V_S = (V+) - (V-) = 5V \text{ at } T_A = 25^{\circ}C, \ R_L = 10 \text{k}\Omega \text{ connected to } V_S/2, \ V_{CM} = V_S/2 \text{ (unless otherwise noted)}$

| Parameter                                       | Symbol            | Test Condition                                                                                          | Min <sup>[1]</sup>       | Тур  | Max <sup>[1]</sup> | Unit             |

|-------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------|------------------|

| Input Offset Voltage Temperature<br>Coefficient | TCV <sub>OS</sub> | T <sub>A</sub> = -40°C to 125°C                                                                         | -                        | 0.02 | 0.075              | μV/°C            |

| Input Bias Current                              | Ι <sub>Β</sub>    | T <sub>A</sub> = -40°C to 125°C                                                                         | -                        | ±37  | ±600               | pA               |

| Input Offset Current                            | Ios               | T <sub>A</sub> = -40°C to 125°C                                                                         | -                        | ±73  | ±400               | pA               |

| Common-Mode Input Range                         | V <sub>ICM</sub>  | V <sub>S</sub> = 1.8V to 5.5V                                                                           | (V <sub>S</sub> -) - 0.1 | -    | $(V_S+) + 0.1$     | V                |

| Common-Mode Rejection Ratio                     | CMRR              | V <sub>S</sub> = 1.8V to 5.5V, T <sub>A</sub> = -40°C to 125°C<br>(V-) - 0.1V < VCM < (V+) + 0.1V       | 106                      | 127  | -                  | dB               |

| Power Supply Rejection Ratio                    | PSRR              | V <sub>S</sub> = 1.8V to 5.5V, T <sub>A</sub> = -40°C to 125°C                                          | 106                      | 124  | -                  | dB               |

| Open-Loop Gain                                  | A <sub>OL</sub>   | (V-) + 100mV < V <sub>O</sub> < (V+) – 100mV,<br>R <sub>L</sub> = 10kΩ, T <sub>A</sub> = -40°C to 125°C | 106                      | 143  | -                  | dB               |

| Output Valtage Swing from Daile                 | V <sub>OFR+</sub> | $R_L$ = 10kΩ, $T_A$ = -40°C to 125°C                                                                    | -                        | 28   | 70                 | mV               |

| Output Voltage Swing from Rails                 | V <sub>OFR-</sub> | $R_L = 10k\Omega$ , $T_A = -40^{\circ}C$ to 125°C                                                       | -                        | 24   | 70                 | mV               |

| Sourcing Short-Circuit Current                  | I <sub>SC+</sub>  | V <sub>OUT</sub> connected to V-                                                                        | -                        | 19   | 30                 | mA               |

| Sinking Short-Circuit Current                   | I <sub>SC-</sub>  | V <sub>OUT</sub> connected to V+                                                                        | -35                      | -14  | -                  | mA               |

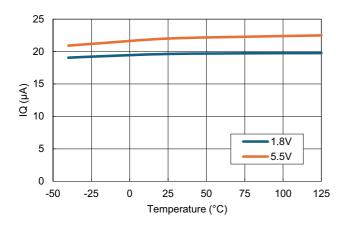

| Supply Current per Amplifier                    | ΙQ                | R <sub>L</sub> = ∞, T <sub>A</sub> = -40°C to 125°C                                                     | -                        | 22   | 35                 | μA               |

| AC Parameters                                   |                   |                                                                                                         |                          |      |                    |                  |

| Input Noise Voltage                             | _                 | f = 0.01 to 1Hz                                                                                         | -                        | 0.9  | -                  | μV <sub>pp</sub> |

| input Noise voitage                             | E <sub>n</sub>    | f = 0.1 to 10Hz                                                                                         | -                        | 1.1  | -                  | μV <sub>pp</sub> |

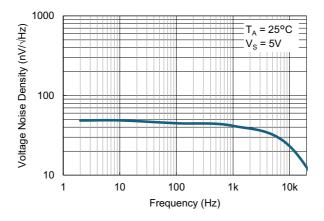

| Voltage Noise Density                           | e <sub>n</sub>    | f = 1kHz                                                                                                | -                        | 43.5 | -                  | nV/√Hz           |

| Current Noise Density                           | i <sub>n</sub>    | f = 10Hz                                                                                                | -                        | 76   | -                  | fA/√Hz           |

| Gain Bandwidth Product                          | GBW               | $G = 100, R_L = 10kΩ$                                                                                   | -                        | 340  | -                  | kHz              |

| Transient Response                              |                   |                                                                                                         | '                        |      |                    |                  |

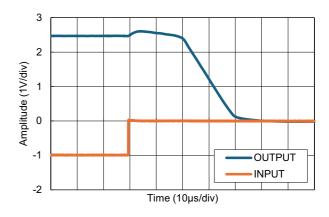

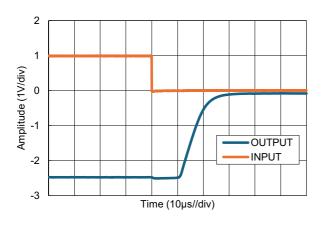

| Positive Slew Rate                              | SR+               | $V_{OUT}$ = 1V to 4V, $R_L$ = 10k $\Omega$ , $G$ = 1                                                    | -                        | 0.2  | -                  | V/µs             |

| Negative Slew Rate                              | SR-               | $V_{OUT}$ = 1V to 4V, $R_L$ = 10k $\Omega$ , $G$ = 1                                                    | -                        | 0.2  | -                  | V/µs             |

| Settling Time to 0.1% V <sub>O</sub>            | t <sub>S</sub>    | V <sub>S</sub> = ±2.5V, G =1, 2V-Step, C <sub>L</sub> = 1.2pF                                           | -                        | 22.5 | -                  | μs               |

<sup>1.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

# 3. Typical Performance Graphs

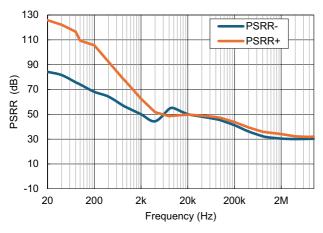

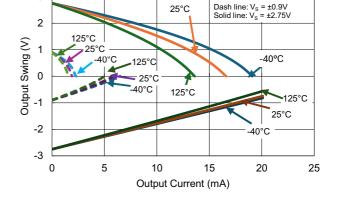

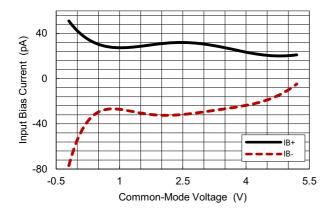

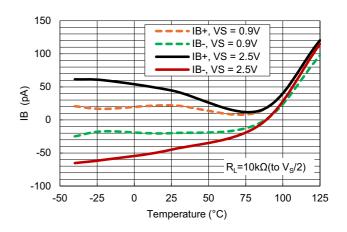

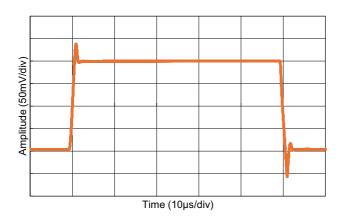

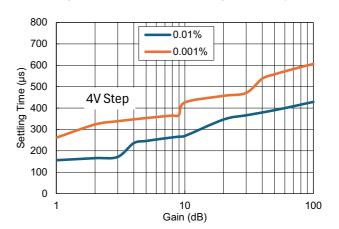

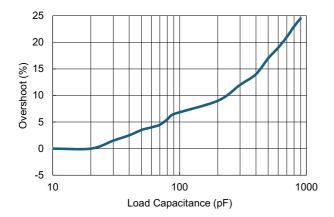

$V_S$  = 5V (±2.5V) at  $T_A$  = 25°C, RL = 10k $\Omega$  connected to  $V_S/2$ ,  $V_{CM}$  =  $V_S/2$  (unless otherwise noted)

130 CMRR

110 90

90

30

10

-10

10 100 1k 10k 100k 1M 10M

Frequency (Hz)

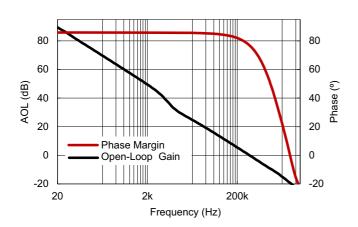

Figure 4. Open-Loop Gain and Phase vs Frequency

Figure 5. CMRR vs Frequency

3

Figure 6. PSRR vs Frequency

Figure 7. Output Voltage Swing vs Output Current

Figure 8. Input Bias Current vs Common-Mode Voltage

Figure 9. Input Bias Current vs Temperature

$V_S = 5V \ (\pm 2.5V) \ at \ T_A = 25^{\circ}C, \ RL = 10k\Omega \ connected \ to \ V_S/2, \ V_{CM} = V_S/2 \ (unless \ otherwise \ noted) \ (Cont.)$

Time (50µs)

Figure 10. Quiescent Current vs Temperature

Figure 11. Large Signal Step Response

Figure 12. Small Signal Step Response

Figure 13. Positive Overvoltage Recovery

Figure 14. Negative Overvoltage Recovery

Figure 15. Settling Time vs Closed-Loop Gain

$V_S = 5V \; (\pm 2.5V) \; \text{at T}_A = 25^{\circ}C, \; \text{RL} = 10 \text{k}\Omega \; \text{connected to} \; V_S/2, \; V_{CM} = V_S/2 \; \text{(unless otherwise noted)} \; \text{(Cont.)}$

Figure 16. Small Signal Overshoot vs Load Capacitance

Figure 17. 0.1Hz to 10Hz Noise

Figure 18. Voltage Noise Spectral Density

## 4. Detailed Description

#### 4.1 Overview

The ISL28133A auto-zero operational amplifier (op amp) is a low-power device with rail-to-rail input and outputs. This op amp operates from supply voltages as low as 1.8V up to 5.5V. The device is unity-gain stable and designed for a wide range of precision and general-purpose applications.

Its input common-mode voltage range extends 100mV above and below the power supply voltage rails, allowing this op amp to be used in virtually any single-supply application. The rail-to-rail input and output swing capability increases the signal dynamic range and therefore, signal-to-noise ratio, a performance feature highly necessary in low-supply applications. The combination of low-offset voltage and low drift over temperature and time makes this device ideal for the use in high-gain amplifiers and precision sensor signal conditioners.

## 4.2 Functional Block Diagram

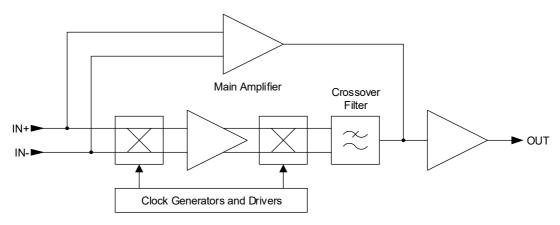

Figure 19. Block Diagram of a Single Amplifier Stage

## 4.3 Feature Description

#### 4.3.1 Low Offset and Drift

The ISL28133A device uses a proprietary chopper-stabilized technique that combines a 340kHz main amplifier with a high open-loop gain chopper amplifier to achieve low offset voltage and drift, while consuming only 22µA of supply current per channel.

This multi-path amplifier architecture contains a time continuous main amplifier whose DC offset input is corrected by a parallel connected, high gain chopper stabilized DC correction amplifier operating at 100kHz. From DC to about 5kHz, both amplifiers are active with DC offset correction and most of the low frequency gain is provided by the chopper amplifier. A 5kHz crossover filter cuts off the low frequency amplifier path, leaving the main amplifier active out to the 340kHz gain-bandwidth product of the device.

The key benefits of this architecture for precision applications are very high open-loop gain, very low DC offset, and low 1/f noise. The noise is virtually flat across the frequency range from a few millihertz out to 100kHz, except for the narrow noise peak at the amplifier crossover frequency.

#### 4.3.2 Rail-To-Rail Input and Output (RRIO)

The RRIO CMOS amplifier uses parallel input PMOS and NMOS that enable the inputs to swing 100mV beyond either supply rail. The inverting and non-inverting inputs do not have back-to-back input clamp diodes and can maintain high input impedance at high differential input voltages. This is effective in eliminating output distortion caused by high slew-rate input signals.

The output stage uses common source connected PMOS and NMOS devices to achieve rail-to-rail output drive capability within 17mA current limit and the capability to swing to within 25mV of either rail while driving a  $10k\Omega$  load.

### 4.3.3 Layout Guidelines for High Impedance Inputs

To achieve the maximum performance of the high input impedance and low offset voltage of the ISL28133A amplifier, care should be taken in the circuit board layout. The surface of the printed circuit board must remain clean and free of moisture to avoid leakage-currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board.

#### 4.3.4 Input and Output ESD Protection

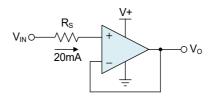

ISL28133A incorporates internal ESD protection circuits on all pins. For the input and output pins, this protection primarily consists of current-steering diodes that are connected between the input and output pins and the power-supply pins. If the input voltage is expected to exceed the specified value in the Absolute Maximum Ratings, insert a series resistor (R<sub>S</sub>) to limit the input current to about 20mA (Figure 20).

**Figure 20. Input Current Protection**

## 5. Application Information

The ISL28133A features 340kHz gain-bandwidth and  $0.2V/\mu s$  slew rate with only  $22\mu A$  of supply current per channel. Its low input offset of  $2\mu V$  enables the design of DC-coupled high-gain amplifiers. However, care must be applied when designing for maximum dynamic output range to prevent signal distortions due to the low slew rate. Also, PCB layout considerations are different to that of a standard op amp.

## 5.1 Typical Applications

## 5.1.1 High Gain, Precision DC-Coupled Amplifier

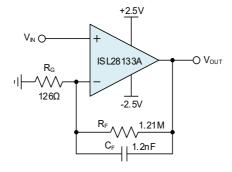

The circuit in Figure 21 implements a single-stage DC-coupled amplifier with an input DC sensitivity of under 100nV that is only possible using a low  $V_{OS}$  amplifier with high open-loop gain. High gain DC amplifiers operating from low voltage supplies are not practical using typical low offset precision op amps. For example, a typical precision amplifier in a gain of 10kV/V with a  $\pm 100\mu V$   $V_{OS}$  and an offset drift of  $0.5\mu V/^{\circ}C$  of a low offset op amp would produce a DC error of >1V with an additional  $5mV/^{\circ}C$  of temperature dependent error, making it difficult to resolve DC input voltage changes in the mV range.

Figure 21. High-Gain, Precision DC-Coupled Amplifier with ISL28133A

The  $\pm 10 \mu V$  max  $V_{OS}$  and  $0.075 \mu V/^{\circ}C$  maximum temperature drift of the ISL28133A produces a temperature stable maximum DC output error of only  $\pm 100 m V$  with a maximum output temperature drift of  $0.75 m V/^{\circ}C$ . The additional benefit of a low 1/f noise corner frequency and some feedback filtering enables DC voltages and voltage fluctuations well below 100 n V to be easily detected with a simple single stage amplifier.

#### 5.1.2 Design Procedure

The following are design requirements for this design:

- Input voltage and frequency range:  $V_{IN} = 0$  to  $500\mu V_{P-P}$ ,  $f_{IN} = 0$  to 10Hz

- Required Signal output range: V<sub>O</sub> = 0 to 4.8V<sub>P-P</sub>

- Low-pass filter cut-off frequency: f<sub>C</sub> = 100Hz

The signal gain of the amplifier is:

(EQ. 1)

$$G = \frac{V_O}{V_{IN}} = \frac{4.8V_{P-P}}{500\mu V_{P-P}} = 9600V/V \text{ or } 96.65dB$$

This gain is defined by the feedback and gain resistors,  $R_F$  and  $R_G$ , with  $G = 1 + R_F/R_G$ . Solving for the resistor ratio gives:

(EQ. 2)

$$R_F/R_G = G-1 = 9599$$

Making  $R_F$  = 1.21M $\Omega$  and  $R_G$  = 126 $\Omega$  yields a gain of 9604 and therefore, a gain error of 0.04%. The cut-off frequency of the low-pass filter is defined by  $f_C$  = 1/(2 $\pi$ ×C $_F$ ×R $_F$ ). Solving for C $_F$  gives:

(EQ. 3)

$$C_F = \frac{1}{2\pi \times f_C \times R_F} = \frac{1}{2\pi \times 100 Hz \times 1.21 M\Omega} = 13.15 nF$$

Selecting the closest standard value makes C<sub>F</sub> = 12nF, resulting in a cut-off frequency of f<sub>C</sub> = 109Hz.

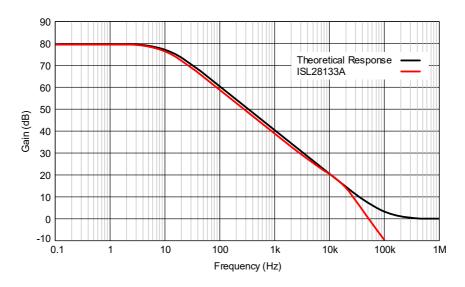

Figure 22 shows the gain response of the high-gain amplifier using ISL28133A in comparison with the gain response of an ideal op amp. *Note*: The output impedance of low-power CMOS op amps increases significantly at high frequencies. This causes the gain response to divert from theoretical response, which assumes an op amp output impedance of  $Z_O = 0\Omega$ .

Figure 22. High-Gain Amplifier Frequency Response

## 5.2 Layout Considerations

When using the highest-precision amplifier available, the overall accuracy of your application might still fall short of expectations. Specifically, employing an auto-zero amplifier often shifts the precision limitation from the amplifier itself to the design and layout of the printed circuit board (PCB).

One significant contributor to offset voltage errors on a PCB is thermoelectric voltage, commonly referred to as thermocouple or Seebeck voltage. This voltage is generated at the junction between two dissimilar metals and is directly proportional to the junction temperature. The magnitude of Seebeck voltage varies considerably depending on the specific metals involved, typically ranging from microvolts up to millivolts. Additionally, temperature-induced variations in these voltages can span from several microvolts to tens of microvolts per degree Celsius.

Typical metallic junctions found on PCBs include solder-to-trace interfaces and solder-to-component lead connections. If a temperature gradient exists across the PCB, resulting in different temperatures at each end of a component, the resulting Seebeck voltages differs, thereby producing a thermal voltage error. Figure 23 illustrates this scenario.

Figure 23. Using Dummy Resistor minimizes Offset Errors due to Seebeck Voltages and Bias Currents

In a high-gain configuration, where feedback resistor ( $R_F$ ) is significantly larger than gain resistor ( $R_G$ ), any difference in Seebeck voltages appearing across  $R_G$  manifests as an offset voltage directly at the amplifier's inverting input. This initial offset voltage is subsequently amplified by the closed-loop gain, therefore causing a substantially larger output voltage error.

Thermocouple errors can be mitigated by using a dummy component to match the thermoelectric error source. For instance, adding a resistor ( $R_P$ ) in series with the non-inverting input does not impact the amplifier's AC performance but, when placed physically close to  $R_G$ , ensures that their Seebeck potentials are closely matched, thereby minimizing thermocouple-induced errors. Matching  $R_P$  to the parallel combination of  $R_G$  and  $R_F$  further reduces offset errors caused by input bias currents.

The Seebeck voltage difference across the feedback resistor ( $R_F$ ) is less critical because this error appears directly at the output and is not amplified by the closed-loop gain.

Another effective approach for reducing offset errors due to Seebeck voltages is maintaining a uniform ambient temperature across the PCB. Implementing a ground plane helps distribute heat evenly throughout the PCB and provides additional benefits, such as reducing susceptibility to electromagnetic interference (EMI).

The PCB surface should be clean and moisture-free to prevent leakage currents between adjacent traces. Applying a surface coating creates a humidity barrier, reducing surface moisture and thereby minimizing parasitic resistance on the board.

Further reduction of leakage currents can be achieved by using guard rings around the amplifier inputs. While the guard rings do not require a specific width, each guard ring should form a continuous loop around the inverting and non-inverting inputs of the amplifier. By setting the guard ring voltage equal to the voltage at the non-inverting input, both parasitic resistance and capacitance are effectively reduced.

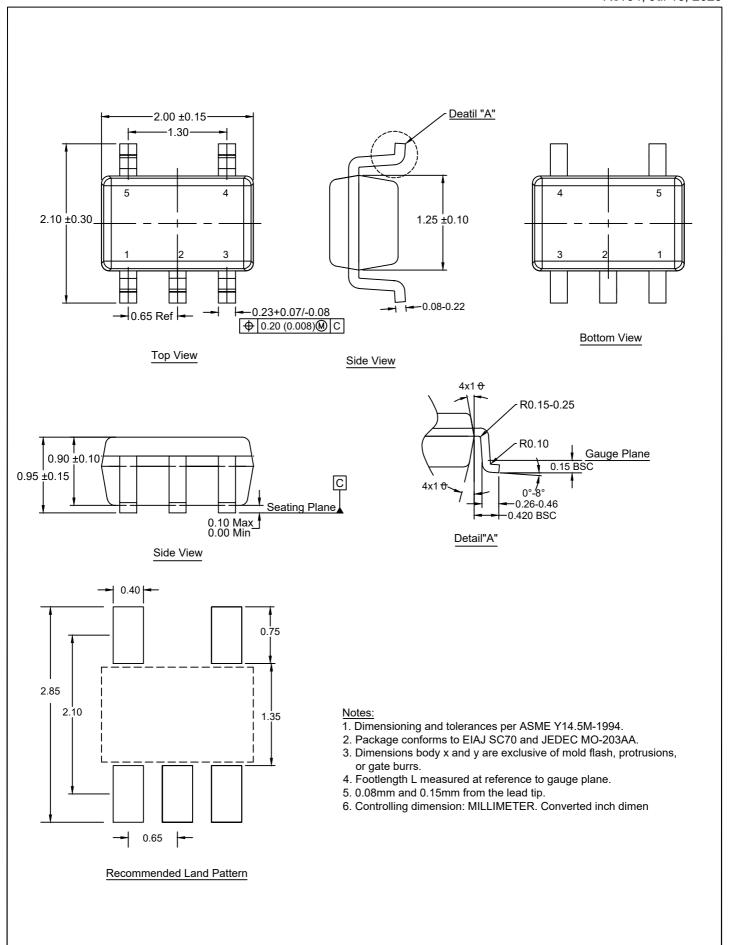

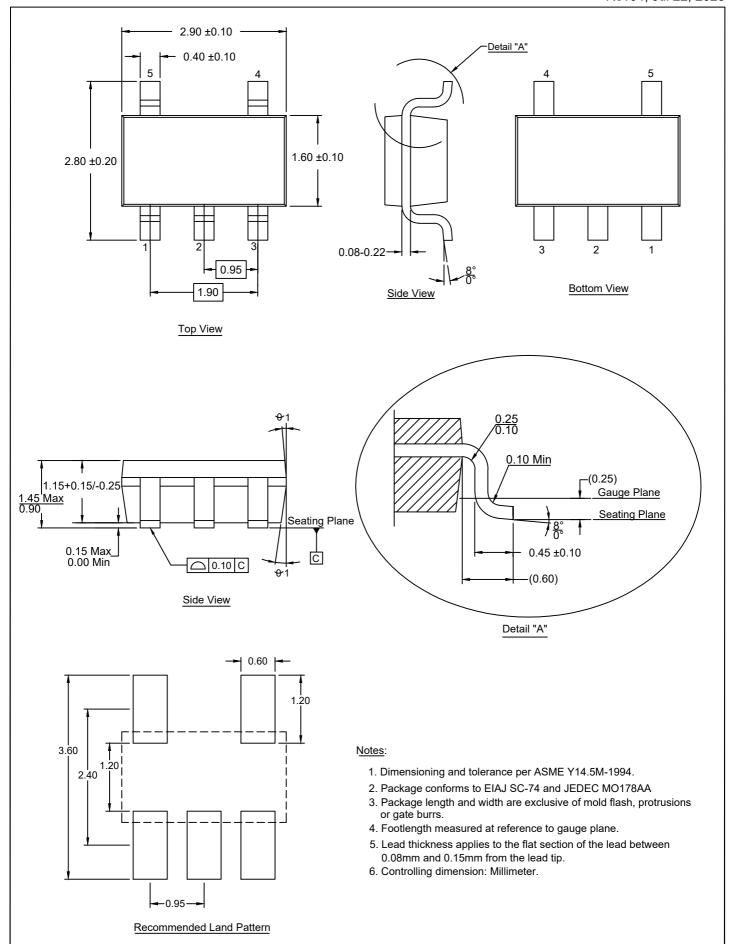

## 6. Package Outline Drawings

The package outline drawings are located at the end of this document and are accessible from the Renesas website. The package information is the most current data available and is subject to change without revision of this document.

# 7. Ordering Information

| Part Number <sup>[1]</sup> | #<br>Channels | Part<br>Marking     | Package<br>Description <sup>[2]</sup><br>(RoHS Compliant) | Pkg. Dwg. # | Carrier<br>Type <sup>[3]</sup> | MSL<br>Rating <sup>[4]</sup> | Temp. Range  |

|----------------------------|---------------|---------------------|-----------------------------------------------------------|-------------|--------------------------------|------------------------------|--------------|

| ISL28133AFEZ-T7            | 1             | 133 <sup>[5]</sup>  | SC70-5                                                    | P5.049      | Reel, 3k                       | 1                            | -40 to 125°C |

| ISL28133AFHZ-T7            | 1             | 133A <sup>[5]</sup> | SOT23-5                                                   | P5.064      | Reel, 3k                       | 1                            | -40 to 125°C |

- These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin

plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 2. For the Pb-Free Reflow Profile, see TB493.

- 3. See TB347 for details about reel specifications.

- 4. Moisture Sensitivity Level (MSL) tested per JEDEC J-STD-020. For more information about MSL, see TB363.

- 5. The part marking is located on the bottom of the part.

## 8. Revision History

| Revision | Date         | Description                                                |  |  |

|----------|--------------|------------------------------------------------------------|--|--|

| 1.01     | Sep 10, 2025 | Updated PODs to the latest format. Added ECAD Information. |  |  |

| 1.00     | Jul 8, 2025  | Initial release.                                           |  |  |

#### **ECAD Design Information** Α.

This information supports the development of the PCB ECAD model for this device. It is intended to be used by PCB designers.

#### **Part Number Indexing A.1**

| Orderable Part Number | Number of Pins | Package Type | Package Code/POD Number |

|-----------------------|----------------|--------------|-------------------------|

| ISL28133AFEZ-T7       | 5              | SC70         | P5.049                  |

| ISL28133AFHZ-T7       | 5              | SOT23        | P5.064                  |

#### **A.2 Symbol Pin Information**

#### A.2.1 5-SC70

| Pin Number | Primary Pin Name | Primary Electrical Type | Alternate Pin Name(s) |

|------------|------------------|-------------------------|-----------------------|

| 1          | IN+              | Input                   | -                     |

| 2          | V-               | Power                   | -                     |

| 3          | IN-              | Input                   | -                     |

| 4          | OUT              | Ouput                   | -                     |

| 5          | V+               | Power                   | -                     |

#### A.2.2 5-SOT-23

| Pin Number | Primary Pin Name | Primary Electrical Type | Alternate Pin Name(s) |

|------------|------------------|-------------------------|-----------------------|

| 1          | OUT              | OUT Ouput               |                       |

| 2          | V-               | Power                   | -                     |

| 3          | IN+              | Input                   | -                     |

| 4          | IN-              | Input                   | -                     |

| 5          | V+               | Power                   | -                     |

# A.3 Symbol Parameters

| Orderable Part<br>Number | Qualification | Mounting<br>Type | RoHS      | Min<br>Operating<br>Temperature | Max<br>Operating<br>Temperature | Min<br>Supply<br>Voltage | Max<br>Supply<br>Voltage | Number of<br>Channels | Supply<br>Current | Max<br>Input<br>Offset<br>Voltage |

|--------------------------|---------------|------------------|-----------|---------------------------------|---------------------------------|--------------------------|--------------------------|-----------------------|-------------------|-----------------------------------|

| ISL28133AFEZ-T7          | Commercial    | SMD              | Compliant | -40 °C                          | +125 °C                         | 1.8 V                    | 5.5 V                    | 1                     | 22 µA             | ±10 μV                            |

| ISL28133AFHZ-T7          | Commercial    | SMD              | Compliant | -40 °C                          | +125 °C                         | 1.8 V                    | 5.5 V                    | 1                     | 22 µA             | ±10 μV                            |

# A.4 Footprint Design Information

## A.4.1 5-SC70

| IPC Footprint Type | Package Code/ POD Number | Number of Pins |

|--------------------|--------------------------|----------------|

| SC70               | P5.049                   | 5              |

| Description                                                                                    | Dimension | Value (mm) | Diagram         |

|------------------------------------------------------------------------------------------------|-----------|------------|-----------------|

| Minimum body span (vertical side)                                                              | Dmin      | 1.85       | D               |

| Maximum body span (vertical side)                                                              | Dmax      | 2.15       | . B .           |

| Minimum lead span (horizontal side)                                                            | Emin      | 1.80       | ]               |

| Maximum lead span (horizontal side)                                                            | Emax      | 2.40       | -     n n-1     |

| Minimum lead width                                                                             | Bmin      | 0.15       | 1               |

| Maximum lead width                                                                             | Bmax      | 0.30       |                 |

| Minimum body width (horizontal side)                                                           | E1min     | 1.15       | ]               |

| Maximum body width (horizontal side)                                                           | E1max     | 1.35       | ] <u>E</u>   E1 |

| Number of leads: 3, 4, 5 or 6                                                                  | PinCount  | 5          | ]               |

| Comma separated list showing pin sequence (Na,Nb,). Example: 1,2,3 or 1,2,3,4,5,6 or 5,4,1,3,2 | PinOrder  | 1,2,3,4,5  |                 |

| Distance between the center of any two adjacent pins                                           | Pitch     | 0.65       | 1 + 4 4         |

| Overall pitch (e1)                                                                             | Pitch1    | 1.30       |                 |

| Maximum Height                                                                                 | Amax      | 1.10       | Pitch -         |

| Minimum standoff height                                                                        | A1min     | 0.00       | Pitch1——        |

| Maximum body height                                                                            | A2max     | 1.00       | Bottom View     |

| Minimum Lead Thickness                                                                         | cmin      | 0.08       |                 |

| Maximum Lead Thickness                                                                         | cmax      | 0.22       | T + + (         |

| Minimum Lead Length                                                                            | Lmin      | 0.26       | A2 H            |

| Maximum Lead Length                                                                            | Lmax      | 0.46       | A1              |

|                                                                                                |           |            | Side View       |

| Recommended Land Pattern                           |           |            |              |  |  |  |

|----------------------------------------------------|-----------|------------|--------------|--|--|--|

| Description                                        | Dimension | Value (mm) | Diagram      |  |  |  |

| Distance between pads. Measured from outside edges | Z         | 2.85       | X            |  |  |  |

| Distance between pads. Measured from inside edges  | G         | 1.35       |              |  |  |  |

| Pad width                                          | х         | 0.40       | 7 G          |  |  |  |

| Pad length                                         | Y         | 0.75       |              |  |  |  |

| Row spacing. Distance between pad centers          | С         | 2.10       | PCB Top View |  |  |  |

## A.4.2 5-SOT23

| IPC Footprint Type | Package Code/ POD Number | Number of Pins |

|--------------------|--------------------------|----------------|

| SOT23              | P5.064                   | 5              |

| Description                                                                                    | Dimension | Value (mm) | Diagram                                       |

|------------------------------------------------------------------------------------------------|-----------|------------|-----------------------------------------------|

| Minimum body span (vertical side)                                                              | Dmin      | 2.80       | ь— D — ы                                      |

| Maximum body span (vertical side)                                                              | Dmax      | 3.00       | B. B.                                         |

| Minimum lead span (horizontal side)                                                            | Emin      | 2.60       | <b>-</b>                                      |

| Maximum lead span (horizontal side)                                                            | Emax      | 3.00       | -     n n-1                                   |

| Minimum lead width                                                                             | Bmin      | 0.30       | 1                                             |

| Maximum lead width                                                                             | Bmax      | 0.50       | 1                                             |

| Minimum body width (horizontal side)                                                           | E1min     | 1.50       | 1                                             |

| Maximum body width (horizontal side)                                                           | E1max     | 1.70       | ] <u>E</u>   E1                               |

| Number of leads: 3, 4, 5 or 6                                                                  | PinCount  | 5          | 1                                             |

| Comma separated list showing pin sequence (Na,Nb,). Example: 1,2,3 or 1,2,3,4,5,6 or 5,4,1,3,2 | PinOrder  | 1,2,3,4,5  |                                               |

| Distance between the center of any two adjacent pins                                           | Pitch     | 0.95       | 1 <u>+                                   </u> |

| Overall pitch (e1)                                                                             | Pitch1    | 1.90       | 1 2                                           |

| Maximum Height                                                                                 | Amax      | 1.45       | Pitch -                                       |

| Minimum standoff height                                                                        | A1min     | 0.00       | Pitch1——                                      |

| Maximum body height                                                                            | A2max     | 1.30       | Bottom View                                   |

| Minimum Lead Thickness                                                                         | cmin      | 0.08       |                                               |

| Maximum Lead Thickness                                                                         | cmax      | 022        |                                               |

| Minimum Lead Length                                                                            | Lmin      | 0.35       | Δ A2                                          |

| Maximum Lead Length                                                                            | Lmax      | 0.55       | A1 C                                          |

|                                                                                                |           |            | Side View                                     |

| Recommended Land Pattern                           |           |            |              |  |  |  |

|----------------------------------------------------|-----------|------------|--------------|--|--|--|

| Description                                        | Dimension | Value (mm) | Diagram      |  |  |  |

| Distance between pads. Measured from outside edges | Z         | 3.60       | X            |  |  |  |

| Distance between pads. Measured from inside edges  | G         | 1.20       |              |  |  |  |

| Pad width                                          | х         | 0.60       | 7 G          |  |  |  |

| Pad length                                         | Y         | 1.20       |              |  |  |  |

| Row spacing. Distance between pad centers          | С         | 2.40       | PCB Top View |  |  |  |

## **Package Outline Drawing**

P5.049

KA0005AA

5-SC70 2.0 x 1.25 x 0.95 mm Body, 0.65mm Pitch Lead Small Outlibe Transistor Plastic Package Rev04, Jul 16, 2025

## **Package Outline Drawing**

RENESAS

P5.064 KA0005AB

5-SOT 2.90 x 1.60 x 1.45 mm Body, 0.95mm Pitch Lead Small Outline Transistor Plastic Package Rev04, Jul 22, 2025

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.