## ISL5957

14-Bit, +3.3V, 260+MSPS, High Speed D/A Converter

FN6080 Rev 2.00 September 29, 2015

The ISL5957 is a 14-bit, 260+MSPS (Mega Samples Per Second), CMOS, high speed, low power, D/A (digital to analog) converter, designed specifically for use in high performance communication systems such as base transceiver stations utilizing 2.5G or 3G cellular protocols.

This device complements the ISL5x57 family of high speed converters, which include 10, 12, and 14-bit devices.

## Ordering Information

| PART<br>NUMBER                                                                                     | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(RoHS<br>Complant) | PKG.<br>DWG.# | CLOCK<br>SPEED |

|----------------------------------------------------------------------------------------------------|------------------------|-------------------------------|---------------|----------------|

| ISL5957IBZ<br>(See Note)<br>(No longer<br>available,<br>recommended<br>replacement:<br>ISL5957IAZ) | -40 to 85              | 28 Ld SOIC                    | M28.3         | 260MHz         |

| ISL5957IAZ<br>(See Note)                                                                           | -40 to 85              | 28 Ld TSSOP                   | M28.173       | 260MHz         |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C.

#### **Features**

- Low Power . . . . 103mW with 20mA Output at 130MSPS

- Adjustable Full Scale Output Current..... 2mA to 20mA

- +3.3V Power Supply

- · 3V LVCMOS Compatible Inputs

- Excellent Spurious Free Dynamic Range (75dBc to Nyquist, f<sub>S</sub> = 130MSPS, f<sub>OUT</sub> = 10MHz)

- UMTS Adjacent Channel Power =71dB at 19.2MHz

- EDGE/GSM SFDR = 94dBc at 11MHz in 20MHz Window

- Pin compatible, 3.3V, Lower Power Replacement For The AD9754 and HI5960

- · Pb-Free Available (RoHS Compliant)

## Applications

- Cellular Infrastructure Single or Multi-Carrier: IS-136, IS-95, GSM, EDGE, CDMA2000, WCDMA, TDS-CDMA

- · BWA Infrastructure

- · Medical/Test Instrumentation

- · Wireless Communication Systems

- · High Resolution Imaging Systems

- · Arbitrary Waveform Generators

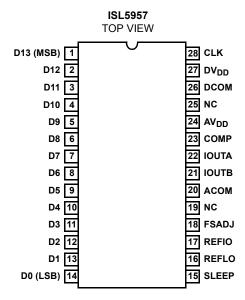

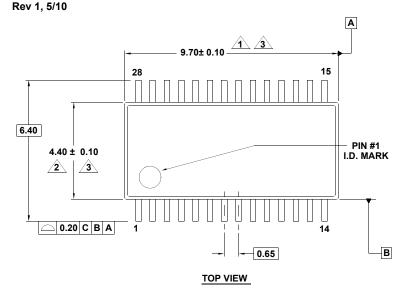

#### **Pinout**

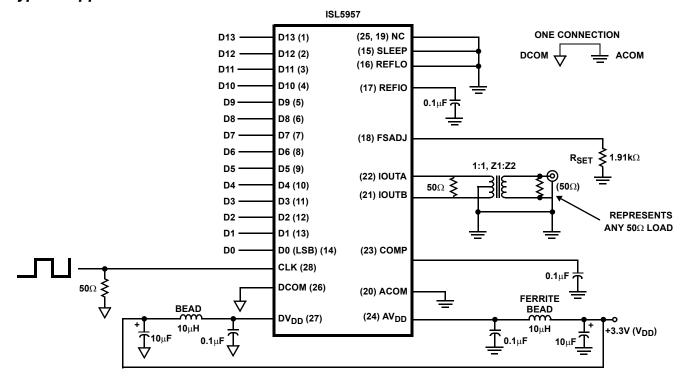

## **Typical Applications Circuit**

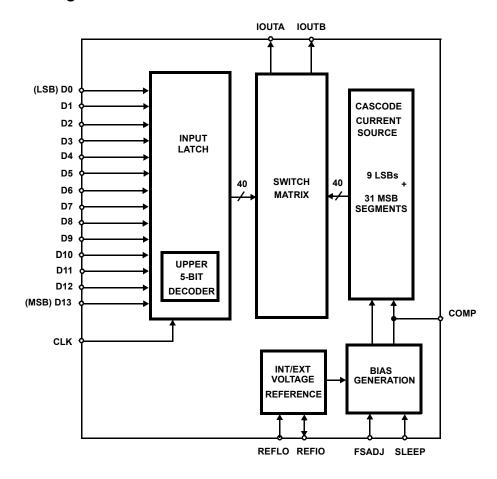

## Functional Block Diagram

## Pin Descriptions

| PIN NO. | PIN NAME                      | DESCRIPTION                                                                                                                                                                             |

|---------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-14    | D13 (MSB) Through<br>D0 (LSB) | Digital Data Bit 13, (Most Significant Bit) through Digital Data Bit 0, (Least Significant Bit).                                                                                        |

| 15      | SLEEP                         | Control Pin for Power-Down mode. Sleep Mode is active high; Connect to ground for Normal Mode. Sleep pin has internal 20µA active pulldown current.                                     |

| 16      | REFLO                         | Connect to analog ground to enable internal 1.2V reference or connect to AV <sub>DD</sub> to disable internal reference.                                                                |

| 17      | REFIO                         | Reference voltage input if internal reference is disabled. Reference voltage output if internal reference is enabled. Use $0.1 \mu F$ cap to ground when internal reference is enabled. |

| 18      | FSADJ                         | Full Scale Current Adjust. Use a resistor to ground to adjust full scale output current. Full Scale Output Current = 32 x V <sub>FSADJ</sub> /R <sub>SET</sub> .                        |

| 19, 25  | NC                            | No Connect. These should be grounded, but can be left disconnected.                                                                                                                     |

| 21      | IOUTB                         | The complementary current output of the device. Full scale output current is achieved when all input bits are set to binary 0.                                                          |

| 22      | IOUTA                         | Current output of the device. Full scale output current is achieved when all input bits are set to binary 1.                                                                            |

| 23      | COMP                          | Connect 0.1µF capacitor to ACOM.                                                                                                                                                        |

| 24      | AV <sub>DD</sub>              | Analog Supply (+2.7V to +3.6V).                                                                                                                                                         |

| 20      | ACOM                          | Connect to Analog Ground.                                                                                                                                                               |

| 26      | DCOM                          | Connect to Digital Ground.                                                                                                                                                              |

| 27      | DV <sub>DD</sub>              | Digital Supply (+2.7V to +3.6V).                                                                                                                                                        |

| 28      | CLK                           | Clock Input.                                                                                                                                                                            |

### **Absolute Maximum Ratings**

| Digital Supply Voltage DV <sub>DD</sub> to DCOM            | +3.6V    |

|------------------------------------------------------------|----------|

| Analog Supply Voltage AV <sub>DD</sub> to ACOM             | +3.6V    |

| Grounds, ACOM TO DCOM0.3V                                  | to +0.3V |

| Digital Input Voltages (D9-D0, CLK, SLEEP) DV <sub>D</sub> | D + 0.3V |

| Reference Input Voltage Range AVD                          | D + 0.3V |

| Analog Output Current (I <sub>OUT</sub> )                  | 24mA     |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| SOIC Package                             | 75                     |

| TSSOP Package                            | 110                    |

| Maximum Junction Temperature             |                        |

| Maximum Storage Temperature Range65      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s) | 300°C                  |

| (SOIC - Lead Tips Only)                  |                        |

### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications**  $AV_{DD} = DV_{DD} = +3.3V$ ,  $V_{REF} = Internal 1.2V$ , IOUTFS = 20mA,  $T_A = 25$ °C for All Typical Values

|                                      | TEST CONDITIONS                                                                                         |        | T <sub>A</sub> = -40°C TO 85°C |        |               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------|--------|--------------------------------|--------|---------------|

| PARAMETER                            |                                                                                                         |        | TYP                            | MAX    | UNITS         |

| SYSTEM PERFORMANCE                   |                                                                                                         |        | <u>I</u>                       | II.    | J.            |

| Resolution                           |                                                                                                         | 14     | -                              | -      | Bits          |

| Integral Linearity Error, INL        | "Best Fit" Straight Line (Note 8)                                                                       | -5     | ±2.5                           | +5     | LSB           |

| Differential Linearity Error, DNL    | (Note 8)                                                                                                | -3     | ±1.5                           | +3     | LSB           |

| Offset Error, IOS                    | IOUTA (Note 8)                                                                                          | -0.006 |                                | +0.006 | % FSR         |

| Offset Drift Coefficient             | (Note 8)                                                                                                | -      | 0.1                            | -      | ppm<br>FSR/°C |

| Full Scale Gain Error, FSE           | With External Reference (Notes 2, 8)                                                                    | -3     | ±0.5                           | +3     | % FSR         |

|                                      | With Internal Reference (Notes 2, 8)                                                                    | -3     | ±0.5                           | +3     | % FSR         |

| Full Scale Gain Drift                | With External Reference (Note 8)                                                                        | -      | ±50                            | -      | ppm<br>FSR/°C |

|                                      | With Internal Reference (Note 8)                                                                        | -      | ±100                           | -      | ppm<br>FSR/°C |

| Full Scale Output Current, IFS       |                                                                                                         | 2      | -                              | 20     | mA            |

| Output Voltage Compliance Range      | (Note 3)                                                                                                | -1.0   | -                              | 1.25   | V             |

| DYNAMIC CHARACTERISTICS              |                                                                                                         | '      |                                | •      |               |

| Maximum Clock Rate, f <sub>CLK</sub> |                                                                                                         | 260    | 300                            | -      | MHz           |

| Output Rise Time                     | Full Scale Step                                                                                         | -      | 1.5                            | -      | ns            |

| Output Fall Time                     | Full Scale Step                                                                                         | -      | 1.5                            | -      | ns            |

| Output Capacitance                   |                                                                                                         | -      | 10                             | -      | pF            |

| Output Noise                         | IOUTFS = 20mA                                                                                           | -      | 50                             | -      | pA/√Hz        |

|                                      | IOUTFS = 2mA                                                                                            | -      | 30                             | -      | pA/√Hz        |

| AC CHARACTERISTICS (Using Figu       | ire 13 with R <sub>DIFF</sub> = $50\Omega$ and R <sub>LOAD</sub> = $50\Omega$ , Full Scale Output = -2. | .5dBm) |                                | •      |               |

| Spurious Free Dynamic Range,         | f <sub>CLK</sub> = 210MSPS, f <sub>OUT</sub> = 80.8MHz, 30MHz Span (Notes 4, 8)                         | -      | 73                             | -      | dBc           |

| SFDR Within a Window                 | f <sub>CLK</sub> = 210MSPS, f <sub>OUT</sub> = 40.4MHz, 30MHz Span (Notes 4, 8)                         | -      | 82                             | -      | dBc           |

|                                      | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 20.2MHz, 20MHz Span (Notes 4, 8)                         | -      | 86                             | -      | dBc           |

Electrical Specifications AV<sub>DD</sub> = DV<sub>DD</sub> = +3.3V, V<sub>REF</sub> = Internal 1.2V, IOUTFS = 20mA, T<sub>A</sub> = 25°C for All Typical Values (Continued)

|                                                                       |                                                                                                                |         | T <sub>A</sub> = -40°C TO 85°C |     |        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|--------------------------------|-----|--------|

| PARAMETER                                                             | TEST CONDITIONS                                                                                                | MIN TYP |                                | MAX | UNITS  |

| Spurious Free Dynamic Range,<br>SFDR to Nyquist (f <sub>CLK</sub> /2) | f <sub>CLK</sub> = 260MSPS, f <sub>OUT</sub> = 80.8MHz (Notes 4, 8)                                            | -       | 47                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 260MSPS, f <sub>OUT</sub> = 40.4MHz (Notes 4, 8)                                            | -       | 61                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 260MSPS, f <sub>OUT</sub> = 20.2MHz (Notes 4, 8)                                            |         | 64                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 210MSPS, f <sub>OUT</sub> = 80.8MHz (Notes 4, 8)                                            |         | 52                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 210MSPS, f <sub>OUT</sub> = 40.4MHz (Notes 4, 8, 10)                                        |         | 61                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 200MSPS, f <sub>OUT</sub> = 20.2MHz, T = 25°C (Notes 4, 8)                                  |         | 64                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 200MSPS, f <sub>OUT</sub> = 20.2MHz, T = -40°C to 85°C (Notes 4, 8)                         | 60      | -                              | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 50.5MHz (Notes 4, 8)                                            | -       | 59                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 40.4MHz (Notes 4, 8)                                            | -       | 63                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 20.2MHz (Notes 4, 8)                                            | -       | 70                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 10.1MHz (Notes 4, 8)                                            | -       | 75                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 5.05MHz, T = 25°C (Notes 4, 8)                                  | 72      | 79                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 130MSPS, f <sub>OUT</sub> = 5.05MHz, T = -40°C to 85°C (Notes 4, 8)                         | 70      | -                              | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 100MSPS, f <sub>OUT</sub> = 40.4MHz (Notes 4, 8)                                            | -       | 61                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 30.3MHz (Notes 4, 8)                                             | -       | 65                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 20.2MHz (Notes 4, 8)                                             | -       | 71                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 10.1MHz (Notes 4, 8, 10)                                         | -       | 71                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 5.05MHz (Notes 4, 8)                                             | -       | 78                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 50MSPS, f <sub>OUT</sub> = 20.2MHz (Notes 4, 8)                                             | -       | 70                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 50MSPS, f <sub>OUT</sub> = 10.1MHz (Notes 4, 8)                                             | -       | 75                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 50MSPS, f <sub>OUT</sub> = 5.05MHz (Notes 4, 8)                                             | -       | 79                             | -   | dBc    |

| Spurious Free Dynamic Range,<br>SFDR in a Window with Eight Tones     | f <sub>CLK</sub> = 210MSPS, f <sub>OUT</sub> = 28.3MHz to 45.2MHz, 2.1MHz Spacing, 50MHz Span (Notes 4, 8, 10) | -       | 67                             | -   | dBc    |

|                                                                       | $f_{\rm CLK}$ = 130MSPS, $f_{\rm OUT}$ = 17.5MHz to 27.9MHz, 1.3MHz Spacing, 35MHz Span (Notes 4, 8)           | -       | 70                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 10.8MHz to 17.2MHz, 811kHz Spacing, 15MHz Span (Notes 4, 8)      | -       | 77                             | -   | dBc    |

|                                                                       | f <sub>CLK</sub> = 50MSPS, f <sub>OUT</sub> = 6.7MHz to 10.8MHz, 490kHz Spacing, 10MHz Span (Notes 4, 8)       | -       | 78                             | -   | dBc    |

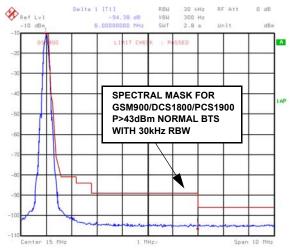

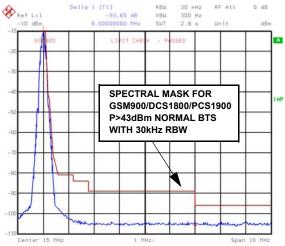

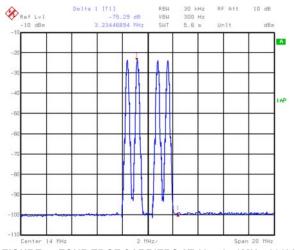

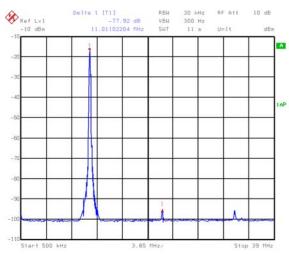

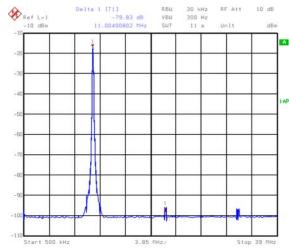

| Spurious Free Dynamic Range,<br>SFDR in a Window with EDGE or GSM     | f <sub>CLK</sub> = 78MSPS, f <sub>OUT</sub> = 11MHz, in a 20MHz Window, RBW = 30kHz (Notes 4, 8, 10)           |         | 94                             | -   | dBc    |

| Adjacent Channel Power Ratio,<br>ACPR with UMTS                       | f <sub>CLK</sub> = 76.8MSPS, f <sub>OUT</sub> = 19.2MHz, RBW = 30kHz (Notes 4, 8, 10)                          | -       | 71                             | -   | dB     |

| VOLTAGE REFERENCE                                                     |                                                                                                                |         |                                |     |        |

| Internal Reference Voltage, V <sub>FSADJ</sub>                        | Pin 18 Voltage with Internal Reference                                                                         | 1.2     | 1.23                           | 1.3 | V      |

| Internal Reference Voltage Drift                                      |                                                                                                                | -       | ±40                            | -   | ppm/°0 |

| Internal Reference Output Current<br>Sink/Source Capability           | Reference is not intended to be externally loaded                                                              | -       | 0                              | -   | μА     |

| Reference Input Impedance                                             |                                                                                                                | -       | 1                              | -   | МΩ     |

| Reference Input Multiplying Bandwidth                                 | (Note 8)                                                                                                       | -       | 1.0                            | -   | MHz    |

## **Electrical Specifications** $AV_{DD} = DV_{DD} = +3.3V$ , $V_{REF} = Internal 1.2V$ , IOUTFS = 20mA, $T_A = 25^{\circ}C$ for All Typical Values (Continued)

|                                                            |                              | T <sub>A</sub> = | $T_A = -40$ °C TO 85°C |        |                 |  |

|------------------------------------------------------------|------------------------------|------------------|------------------------|--------|-----------------|--|

| PARAMETER                                                  | TEST CONDITIONS              |                  | TYP                    | MAX    | UNITS           |  |

| DIGITAL INPUTS D13-D0, CLK                                 |                              |                  |                        |        |                 |  |

| Input Logic High Voltage with 3.3V Supply, V <sub>IH</sub> | (Note 3)                     | 2.3              | 3.3                    | -      | V               |  |

| Input Logic Low Voltage with 3.3V Supply, V <sub>IL</sub>  | (Note 3)                     | -                | 0                      | 1.0    | V               |  |

| Sleep Input Current, I <sub>IH</sub>                       |                              | -25              | -                      | +25    | μА              |  |

| Input Logic Current, I <sub>IH, IL</sub>                   |                              | -20              | -                      | +20    | μА              |  |

| Clock Input Current, I <sub>IH, IL</sub>                   |                              | -10              | -                      | +10    | μА              |  |

| Digital Input Capacitance, C <sub>IN</sub>                 |                              | -                | 5                      | -      | pF              |  |

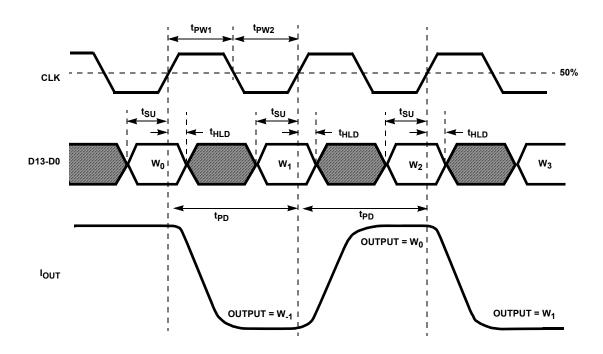

| TIMING CHARACTERISTICS                                     |                              |                  |                        |        |                 |  |

| Data Setup Time, t <sub>SU</sub>                           | See Figure 15                | -                | 1.5                    | -      | ns              |  |

| Data Hold Time, t <sub>HLD</sub>                           | See Figure 15                | -                | 1.5                    | -      | ns              |  |

| ropagation Delay Time, t <sub>PD</sub> See Figure 15       |                              | -                | 1                      | -      | Clock<br>Period |  |

| CLK Pulse Width, t <sub>PW1</sub> , t <sub>PW2</sub>       | See Figure 15 (Note 3)       | 0.9              | -                      | -      | ns              |  |

| POWER SUPPLY CHARACTERISTIC                                | cs                           | 1                |                        |        |                 |  |

| AV <sub>DD</sub> Power Supply                              | (Note 9)                     | 2.7              | 3.3                    | 3.6    | V               |  |

| DV <sub>DD</sub> Power Supply                              | (Note 9)                     | 2.7              | 3.3                    | 3.6    | V               |  |

| Analog Supply Current (I <sub>AVDD</sub> )                 | 3.3V, IOUTFS = 20mA          | -                | 27.5                   | 28.5   | mA              |  |

|                                                            | 3.3V, IOUTFS = 2mA           | -                | 10                     | -      | mA              |  |

| Digital Supply Current (I <sub>DVDD</sub> )                | 3.3V (Note 5)                | -                | 3.7                    | 5      | mA              |  |

|                                                            | 3.3V (Note 6)                | -                | 6.5                    | 8      | mA              |  |

| Supply Current (I <sub>AVDD</sub> ) Sleep Mode             | 3.3V, IOUTFS = Don't Care    | -                | 1.5                    | -      | mA              |  |

| Power Dissipation                                          | 3.3V, IOUTFS = 20mA (Note 5) | -                | 103                    | 111    | mW              |  |

|                                                            | 3.3V, IOUTFS = 20mA (Note 6) | -                | 110                    | 120    | mW              |  |

|                                                            | 3.3V, IOUTFS = 20mA (Note 7) | -                | 157                    | -      | mW              |  |

|                                                            | 3.3V, IOUTFS = 2mA (Note 5)  | -                | 45                     | -      | mW              |  |

| Power Supply Rejection                                     | Single Supply (Note 8)       | -0.125           | -                      | +0.125 | %FSR/V          |  |

### NOTES:

- Gain Error measured as the error in the ratio between the full scale output current and the current through R<sub>SET</sub> (typically 625μA). Ideally the ratio should be 32.

- 3. Parameter guaranteed by design or characterization and not production tested.

- 4. Spectral measurements made with differential transformer coupled output and no external filtering. For multitone testing, the same pattern was used at different clock rates, producing different output frequencies but at the same ratio to the clock rate.

- 5. Measured with the clock at 130MSPS and the output frequency at 5MHz.

- 6. Measured with the clock at 200MSPS and the output frequency at 20MHz.

- 7. Measured with the clock at 260MSPS and the output frequency at 40MHz.

- 8. See "Definition of Specifications."

- 9. Recommended operation is from 3.0V to 3.6V. Operation below 3.0V is possible with some degradation in spectral performance. Reduction in analog output current may be necessary to maintain spectral performance.

- 10. See Typical Performance Plots.

## **Typical Performance** (+3.3V Supply, Using Figure 13 with $R_{DIFF}$ = $100\Omega$ and $R_{LOAD}$ = $50\Omega$ )

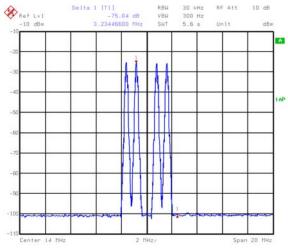

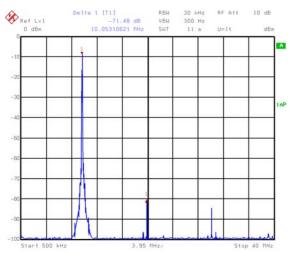

FIGURE 1. EDGE AT 11MHz, 78MSPS CLOCK (94+dBc @ \( \Delta f = +6MHz \)

FIGURE 3. GSM AT 11MHz, 78MSPS CLOCK (94+dBc @  $\Delta f$  = +6MHz, 3dB PAD)

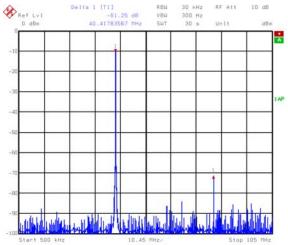

FIGURE 5. FOUR EDGE CARRIERS AT 12.4-15.6MHz, 800kHz SPACING, 78MSPS (75+dBc - 20MHz WINDOW)

FIGURE 2. EDGE AT 11MHz, 78MSPS CLOCK (77dBc -NYQUIST, 6dB PAD)

FIGURE 4. GSM AT 11MHz, 78MSPS CLOCK (79dBc - NYQUIST, 9dB PAD)

FIGURE 6. FOUR GSM CARRIERS AT 12.4-15.6MHz, 78MSPS (75+dBc - 20MHz WINDOW, 6dB PAD)

## **Typical Performance** (+3.3V Supply, Using Figure 13 with $R_{DIFF}$ = $100\Omega$ and $R_{LOAD}$ = $50\Omega$ ) (Continued)

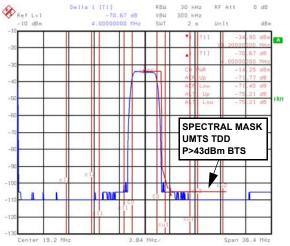

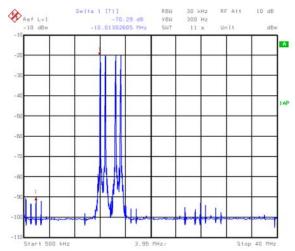

FIGURE 7. UMTS AT 19.2MHz, 76.8MSPS (71dB 1st ACPR, 75dB 2nd ACPR)

FIGURE 9. ONE TONE AT 40.4MHz, 210MSPS CLOCK (61dBc - NYQUIST, 6dB PAD)

FIGURE 11. TWO TONES (CF = 6) AT 8.5MHz, 50MSPS CLOCK, 500kHz SPACING (83dBc - 10MHz WINDOW, 6dB PAD)

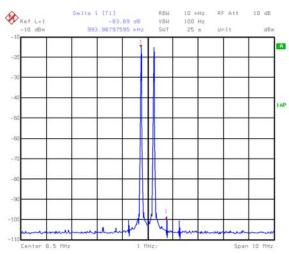

FIGURE 8. ONE TONE AT 10.1MHz, 80MSPS CLOCK (71dBc - NYQUIST, 6dB PAD)

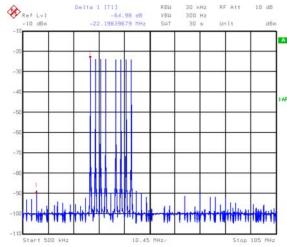

FIGURE 10. EIGHT TONES (CREST FACTOR = 8.9) AT 37MHz, 210MSPS CLOCK, 2.1MHz SPACING (65dBc - NYQUIST)

FIGURE 12. FOUR TONES (CF = 8.1) AT 14MHz, 80MSPS CLOCK, 800kHz SPACING (70dBc - NYQUIST, 6dB PAD)

## **Definition of Specifications**

Adjacent Channel Power Ratio, ACPR, is the ratio of the average power in the adjacent frequency channel (or offset) to the average power in the transmitted frequency channel.

**Differential Linearity Error, DNL**, is the measure of the step size output deviation from code to code. Ideally the step size should be 1 LSB. A DNL specification of 1 LSB or less guarantees monotonicity.

**EDGE, Enhanced Data for Global Evolution,** a TDMA standard for cellular applications which uses 200kHz BW, 8-PSK modulated carriers.

**Full Scale Gain Drift,** is measured by setting the data inputs to be all logic high (all 1s) and measuring the output voltage through a known resistance as the temperature is varied from  $T_{MIN}$  to  $T_{MAX}$ . It is defined as the maximum *deviation* from the *value* measured at room temperature to the *value* measured at either  $T_{MIN}$  or  $T_{MAX}$ . The units are ppm of FSR (full scale range) per °C.

**Full Scale Gain Error**, is the error from an ideal ratio of 32 between the output current and the full scale adjust current (through R<sub>SET</sub>).

**GSM, Global System for Mobile Communication,** a TDMA standard for cellular applications which uses 200kHz BW, GMSK modulated carriers.

**Integral Linearity Error, INL,** is the measure of the worst case point that deviates from a best fit straight line of data values along the transfer curve.

Internal Reference Voltage Drift, is defined as the maximum *deviation* from the *value* measured at room temperature to the *value* measured at either  $T_{MIN}$  or  $T_{MAX}$ . The units are ppm per  $^{\circ}C$ .

**Offset Drift,** is measured by setting the data inputs to all logic low (all 0s) and measuring the output voltage at IOUTA through a known resistance as the temperature is varied from  $T_{MIN}$  to  $T_{MAX}$ . It is defined as the maximum *deviation* from the *value* measured at room temperature to the *value* measured at either  $T_{MIN}$  or  $T_{MAX}$ . The units are ppm of FSR (full scale range) per degree °C.

**Offset Error,** is measured by setting the data inputs to all logic low (all 0s) and measuring the output voltage of IOUTA through a known resistance. Offset error is defined as the maximum *deviation* of the IOUTA output current from a value of 0mA.

**Output Voltage Compliance Range**, is the voltage limit imposed on the output. The output impedance should be chosen such that the voltage developed does not violate the compliance range.

**Power Supply Rejection,** is measured using a single power supply. The nominal supply voltage is varied  $\pm 10\%$  and the change in the DAC full scale output is noted.

Reference Input Multiplying Bandwidth, is defined as the 3dB bandwidth of the voltage reference input. It is measured by using a sinusoidal waveform as the external reference with the digital inputs set to all 1s. The frequency is increased until the amplitude of the output waveform is 0.707 (-3dB) of its original value.

**Spurious Free Dynamic Range, SFDR**, is the amplitude difference from the fundamental signal to the largest harmonically or non-harmonically related spur within the specified frequency window.

**Total Harmonic Distortion, THD,** is the ratio of the RMS value of the fundamental output signal to the RMS sum of the first five harmonic components.

**UMTS, Universal Mobile Telecommunications System,** a W-CDMA standard for cellular applications which uses 3.84MHz modulated carriers.

## **Detailed Description**

The ISL5957 is a 14-bit, current out, CMOS, digital to analog converter. The maximum update rate is at least 260+MSPS and can be powered by a single power supply in the recommended range of +3.0V to +3.6V. It consumes less than 120mW of power when using a +3.3V supply, the maximum 20mA of output current, and the data switching at 210MSPS. The architecture is based on a segmented current source arrangement that reduces glitch by reducing the amount of current switching at any one time. In previous architectures that contained all binary weighted current sources or a binary weighted resistor ladder, the converter might have a substantially larger amount of current turning on and off at certain, worst-case transition points such as midscale and quarter scale transitions. By greatly reducing the amount of current switching at these major transitions, the overall glitch of the converter is dramatically reduced, improving settling time, transient problems, and accuracy.

#### Digital Inputs and Termination

The ISL5957 digital inputs are guaranteed to 3V LVCMOS levels. The internal register is updated on the rising edge of the clock. To minimize reflections, proper termination should be implemented. If the lines driving the clock and the digital inputs are long  $50\Omega$  lines, then  $50\Omega$  termination resistors should be placed as close to the converter inputs as possible connected to the digital ground plane (if separate grounds are used). These termination resistors are not likely needed as long as the digital waveform source is within a few inches of the DAC. For pattern drivers with very high speed edge rates, it is recommended that the user consider series termination  $(50\text{-}200\Omega)$  prior to the DAC's inputs in order to reduce the amount of noise.

#### **Power Supply**

Separate digital and analog power supplies are recommended. The allowable supply range is +2.7V to +3.6V. The recommended supply range is +3.0 to 3.6V

(nominally +3.3V) to maintain optimum SFDR. However, operation down to +2.7V is possible with some degradation in SFDR. Reducing the analog output current can help the SFDR at +2.7V. The SFDR values stated in the table of specifications were obtained with a +3.3V supply.

#### **Ground Planes**

Separate digital and analog ground planes should be used. All of the digital functions of the device and their corresponding components should be located over the digital ground plane and terminated to the digital ground plane. The same is true for the analog components and the analog ground plane.

#### Noise Reduction

To minimize power supply noise,  $0.1\mu F$  capacitors should be placed as close as possible to the converter's power supply pins,  $AV_{DD}$  and  $DV_{DD}$ . Also, the layout should be designed using separate digital and analog ground planes and these capacitors should be terminated to the digital ground for  $DV_{DD}$  and to the analog ground for  $AV_{DD}$ . Additional filtering of the power supplies on the board is recommended.

#### Voltage Reference

The internal voltage reference of the device has a nominal value of  $\pm 1.23 V$  with a  $\pm 40 ppm/\,^{\circ} C$  drift coefficient over the full temperature range of the converter. It is recommended that a  $0.1 \mu F$  capacitor be placed as close as possible to the REFIO pin, connected to the analog ground. The REFLO pin (16) selects the reference. The internal reference can be selected if pin 16 is tied low (ground). If an external reference is desired, then pin 16 should be tied high (the analog supply voltage) and the external reference driven into REFIO, pin 17. The full scale output current of the converter is a function of the voltage reference used and the value of  $R_{SET}.\,I_{OUT}$  should be within the 2mA to 20mA range, though operation below 2mA is possible, with performance degradation.

If the internal reference is used,  $V_{FSADJ}$  will equal approximately 1.2V (pin 18). If an external reference is used,  $V_{FSADJ}$  will equal the external reference. The calculation for  $I_{OUT}$  (Full Scale) is:

$I_{OUT}(Full Scale) = (V_{FSADJ}/R_{SET}) X 32.$

If the full scale output current is set to 20mA by using the internal voltage reference (1.2V) and a 1.91k $\Omega$  R<sub>SET</sub> resistor, then the input coding to output current will resemble the following:

TABLE 1. INPUT CODING vs OUTPUT CURRENT WITH INTERNAL REFERENCE AND RSET = 1.91  $K\Omega$

| INPUT CODE (D13-D0) | IOUTA (mA) | IOUTB (mA) |

|---------------------|------------|------------|

| 1111 11111 11111    | 20         | 0          |

| 1000 00000 00000    | 10         | 10         |

| 0000 00000 00000    | 0          | 20         |

#### Analog Output

IOUTA and IOUTB are complementary current outputs. The sum of the two currents is always equal to the full scale output current minus one LSB. If single ended use is desired, a load resistor can be used to convert the output current to a voltage. It is recommended that the unused output be either grounded or equally terminated. The voltage developed at the output must not violate the output voltage compliance range of -1.0V to 1.25V. R<sub>OUT</sub> (the impedance loading each current output) should be chosen so that the desired output voltage is produced in conjunction with the output full scale current. If a known line impedance is to be driven, then the output load resistor should be chosen to match this impedance. The output voltage equation is:

$$V_{OUT} = I_{OUT} X R_{OUT}$$

The most effective method for reducing the power consumption is to reduce the analog output current, which dominates the supply current. The maximum recommended output current is 20mA.

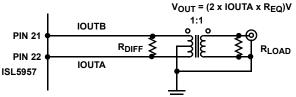

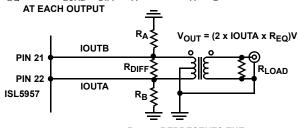

### **Differential Output**

IOUTA and IOUTB can be used in a differential-to-single-ended arrangement to achieve better harmonic rejection. With  $R_{DIFF}$  =  $50\Omega$  and  $R_{LOAD}$  =  $50\Omega$ , the circuit in Figure 13 will provide a 500mV (-2.5dBm) signal at the output of the transformer if the full scale output current of the DAC is set to 20mA (used for the electrical specifications table). Values of  $R_{DIFF}$  =  $100\Omega$  and  $R_{LOAD}$  =  $50\Omega$  were used for the typical performance curves to increase the output power and the dynamic range. The center tap in Figure 13 must be grounded.

In the circuit in Figure 14, the user is left with the option to ground or float the center tap. The DC voltage that will exist at either IOUTA or IOUTB if the center tap is floating is IOUT $_{DC}$  x ( $R_A/\!/R_B$ ) V because  $R_{DIFF}$  is DC shorted by the transformer. If the center tap is grounded, the DC voltage is 0V. Recommended values for the circuit in Figure 14 are  $R_A=R_B=50\Omega,\,R_{DIFF}=100\Omega,$  assuming  $R_{LOAD}=50\Omega.$  The performance of Figure 13 and Figure 14 is basically the same, however leaving the center tap of Figure 14 floating allows the circuit to find a more balanced virtual ground, theoretically improving the even order harmonic rejection, but likely reducing the signal swing available due to the output voltage compliance range limitations.

## R<sub>EQ</sub> = 0.5 x (R<sub>LOAD</sub>//R<sub>DIFF</sub>) AT EACH OUTPUT

R<sub>LOAD</sub> REPRESENTS THE LOAD SEEN BY THE TRANSFORMER

## FIGURE 13. OUTPUT LOADING FOR DATASHEET MEASUREMENTS

$R_{EQ} = 0.5 \text{ x } (R_{LOAD} / R_{DIFF} / R_A), \text{ WHERE } R_A = R_B$

R<sub>LOAD</sub> REPRESENTS THE LOAD SEEN BY THE TRANSFORMER

FIGURE 14. ALTERNATIVE OUTPUT LOADING

#### **Propagation Delay**

The converter requires two clock rising edges for data to be represented at the output. Each rising edge of the clock captures the present data word and outputs the previous data. The propagation delay is therefore 1/CLK, plus <2ns of processing. See Figure 15.

#### **Test Service**

Intersil offers customer-specific testing of converters with a service called Testdrive. To submit a request, fill out the Testdrive form. The form can be found by doing an 'entire site search' at www.intersil.com on the words 'DAC Testdrive'. Or, send a request to the technical support center.

## Timing Diagram

FIGURE 15. PROPAGATION DELAY, SETUP TIME, HOLD TIME AND MINIMUM PULSE WIDTH DIAGRAM

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 29, 2015 | FN6080.2 | Updated the Ordering Information table on page 1.  Added Revision History and About Intersil sections.  Updated POD M28.3 to the latest revision. Changes are as follows:  -Added land pattern  Updated POD M28.173 to the latest revision. Changes are as follows:  -Convert to new POD format by moving dimensions from table onto drawing and adding land pattern. No dimension changes |

#### About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2004-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

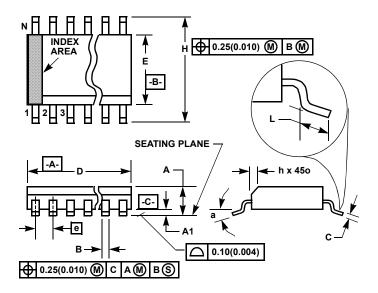

## Small Outline Plastic Packages (SOIC)

M28.3 (JEDEC MS-013-AE ISSUE C)

28 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES |        | MILLIMETERS |       |       |

|--------|--------|--------|-------------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN         | MAX   | NOTES |

| Α      | 0.0926 | 0.1043 | 2.35        | 2.65  | -     |

| A1     | 0.0040 | 0.0118 | 0.10        | 0.30  | -     |

| В      | 0.013  | 0.0200 | 0.33        | 0.51  | 9     |

| С      | 0.0091 | 0.0125 | 0.23        | 0.32  | -     |

| D      | 0.6969 | 0.7125 | 17.70       | 18.10 | 3     |

| Е      | 0.2914 | 0.2992 | 7.40        | 7.60  | 4     |

| е      | 0.05   | BSC    | 1.27 BSC    |       | -     |

| Н      | 0.394  | 0.419  | 10.00       | 10.65 | -     |

| h      | 0.01   | 0.029  | 0.25        | 0.75  | 5     |

| L      | 0.016  | 0.050  | 0.40        | 1.27  | 6     |

| N      | 28     |        | 2           | 28    | 7     |

| α      | 0°     | 8°     | 0°          | 8°    | -     |

Rev. 1, 1/13

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

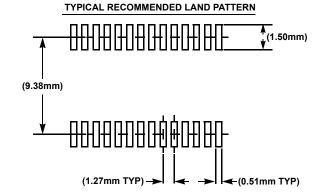

## **Package Outline Drawing**

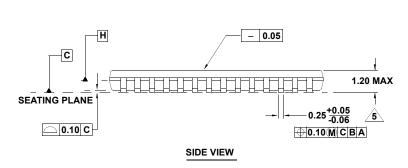

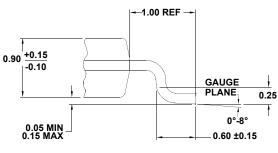

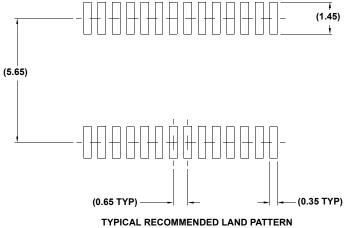

# M28.173 28 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP)

**END VIEW**

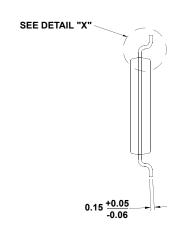

DETAIL "X"

#### NOTES:

- 1. Dimension does not include mold flash, protrusions or gate burrs.

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Dimension does not include dambar protrusion. Allowable protrusion shall be 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153.