#### ISL71441SLH

Radiation Hardened 12V Half-Bridge GaN FET Driver

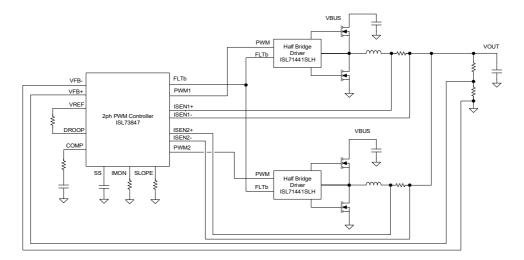

The ISL71441SLH is a Radiation Hardened PWM input 12V Half Bridge GaN FET Driver that drives low  $r_{DS(ON)}$  Gallium Nitride FETs for DC/DC switching regulators. An integrated programmable GaN FET gate drive voltage, high-side bootstrap switch, and strong gate drive current provide a compact and robust GaN FET half-bridge driver.

The ISL71441SLH can interface directly to the ISL73847SLH dual-phase PWM buck controller to create a high-efficiency point-of-load regulator to power many of the latest low voltage high current FPGA and DSP digital core rails.

### **Applications**

- High current DC/DC Point-of-Load (POL) for FPGA and DSP supply rails

- 5V or 12V input to 1V output POL regulation

- GaN FET motor driver

- Combine with ISL73847SLH DC/DC PWM controller and Renesas GaN FETs for a complete DC/DC solution

#### **Features**

- Qualified & Screened to DLA VID V62/25604

- Refer to Renesas Rad Hard Plastic Production and QCI Flow (R34ZZ0006EU)

- All screening and QCI is in accordance with SAE AS6294/1)

- Up to 20V bootstrap voltage half-bridge driver

- Programmable 4.5V to 5.5V gate drive voltage

- Single tri-level PWM input control

- Separate source and sink driver outputs

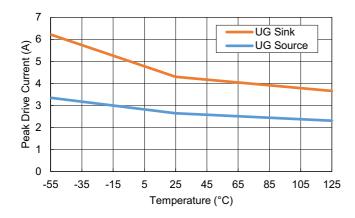

- High-side peak drive: 2A Sourcing, 4A Sinking

- Low-side peak drive: 4A Sourcing, 8A Sinking

- High and low side programmable dead time control

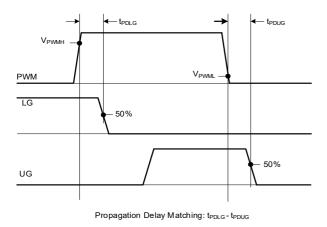

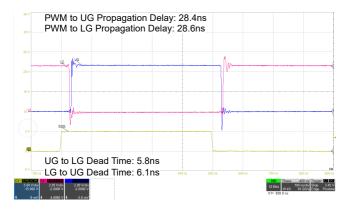

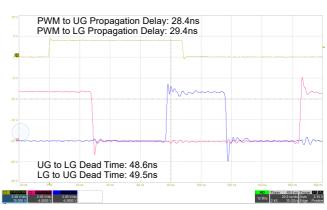

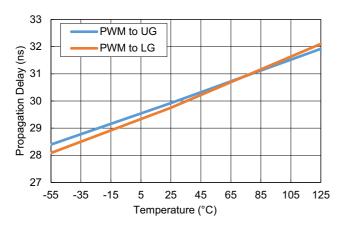

- Highly matched fast propagation delay: 29ns

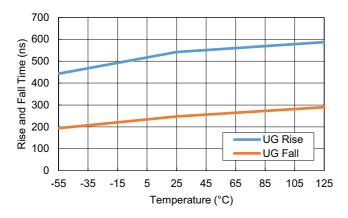

- Full military temperature operation: T<sub>A</sub> = -55°C to 125°C ambient range

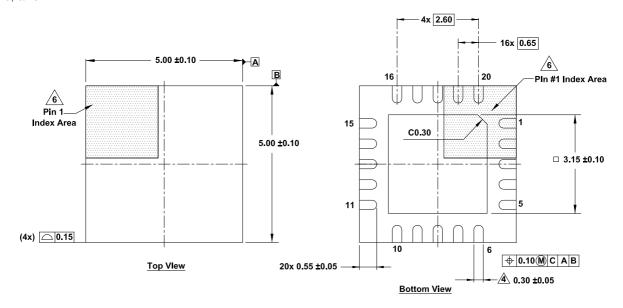

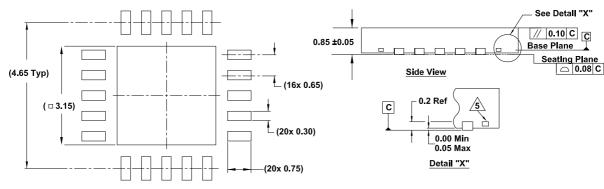

- 20Ld Plastic 5x5mm QFN Package

- TID Rad Hard Assurance (RHA) testing

- LDR (0.01rad(Si)/s): 75krad(Si)

- SEE Characterization

- No DSEE with  $V_{DD}$  = 20V, PHS = 13.5V, PVCC = 6.5V, and AVCC = 6.3V at LET = 86MeV•cm<sup>2</sup>/mg

- SEFI <10µm<sup>2</sup> at LET = 86MeV•cm<sup>2</sup>/mg

- No half-bridge shoot-through SET at LET = 86MeV•cm²/mg

Figure 1. Typical Application Schematic: 2-Phase Controller + Bridge Driver + GaN FETs for 12V Input, 1.0V Output, 50A DC/DC Converter

## **Contents**

| 1.  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 3                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|     | 1.1 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 3                                                                              |

| 2.  | Pin Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 4                                                                              |

|     | 2.1Pin Assignments2.2Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 3.  | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 6                                                                              |

|     | 3.1 Absolute Maximum Ratings 3.2 Outgas Testing 3.3 Thermal Information 3.4 Recommended Operating Conditions 3.5 Electrical Specifications 3.5.1 DC Electrical Specifications 3.5.2 AC Electrical Specifications 3.6 Timing Diagrams                                                                                                                                                                                                                                                                                                                                                     | . 6<br>. 7<br>. 7<br>. 7<br>. 11                                                 |

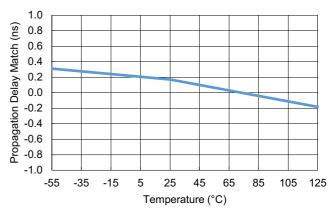

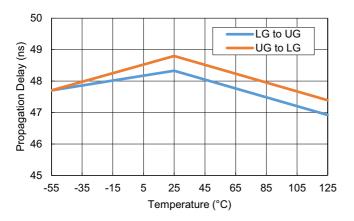

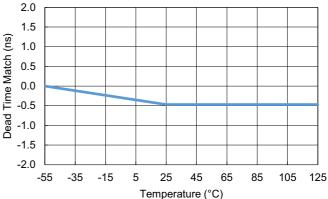

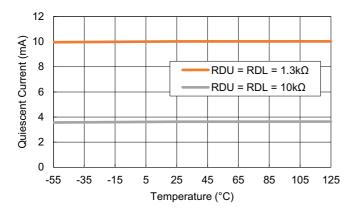

| 4.  | Typical Performance Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 17                                                                             |

| 5.  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                               |

|     | 5.1 Half-Bridge Driver 5.2 GaN/MOS FET Gate Drive Supply 5.3 PWM Input 5.4 Dead Time Control 5.5 Driver Output Architecture 5.6 Integrated BOOT Switch                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23<br>23<br>24<br>24                                                             |

| 6.  | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                                                                               |

|     | 6.1 Power Supply Biasing 6.2 AVCC LDO 6.3 PVCC LDO 6.4 Setting PVCC (Gate Drive) Voltage 6.5 PVCC and BOOT Undervoltage Lockout (UVLO) 6.6 Enable Control 6.7 PWM Operation 6.8 Dead Time Control Resistor Setting 6.9 Bootstrap Capacitor Design 6.10 Bootstrap Voltage Overcharge Protection 6.11 Gate Driver Outputs 6.12 FLTb Pin Fault Indication 6.13 FLTb pin Usage with ISL73847SLH and other ISL71441SLH drivers 6.14 FLTb as Pseudo Enable Pin 6.15 Over-Temperature Protection 6.16 VDD Supply Current 6.17 Power Dissipation 6.18 Dual Complimentary Low-Side GaN FET Driver | 244<br>245<br>255<br>255<br>256<br>277<br>288<br>299<br>299<br>299<br>300<br>300 |

| 7.  | PCB Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|     | 7.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 8.  | Package Outline Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                               |

| 9.  | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                                                               |

| 10. | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                               |

### 1. Overview

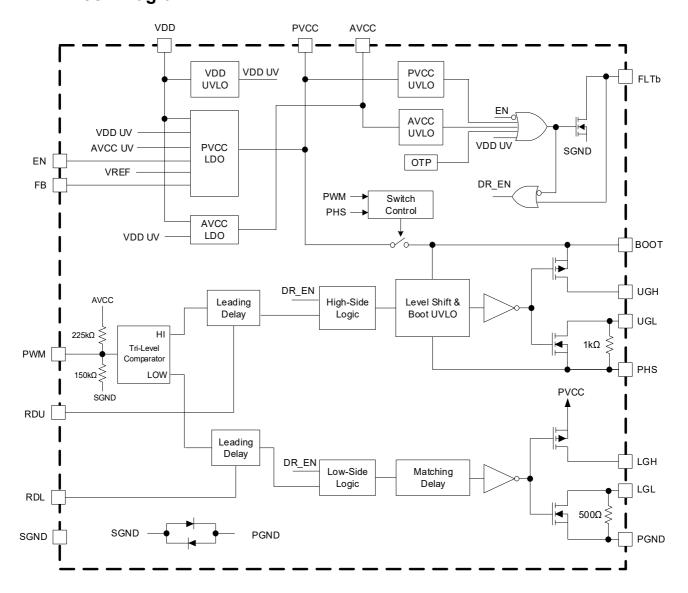

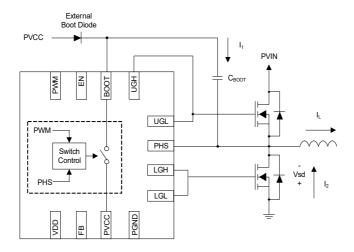

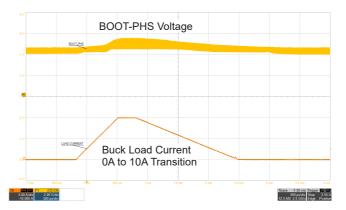

### 1.1 Block Diagram

Figure 2. Circuit Block Diagram

## 2. Pin Information

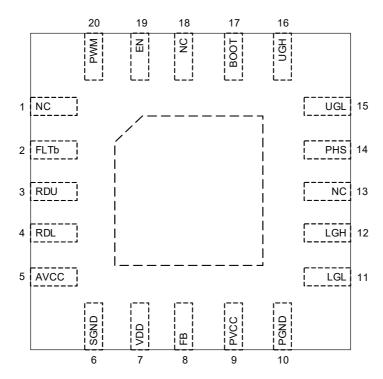

## 2.1 Pin Assignments

Figure 3. Pin Assignments - Top View

Note: Top View - The EPAD is notched on the corner to indicate pin #1 location.

## 2.2 Pin Descriptions

| Pin<br>Number | Pin Name | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                     |

|---------------|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | NC       | -              | No connection.                                                                                                                                                                                                                                                                                                                  |

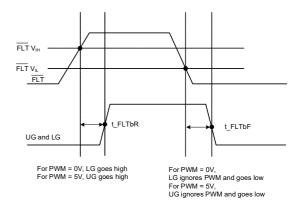

| 2             | FLTb     | 1              | I/O pin. As an open-drain output, FLTb is an active low indicator when EN = 0, AVCC UVLO, PVCC UVLO, or in a over-temperature fault. As a high-impedance input, FLTb disables the driver outputs when driven low. Place a pull-up resistor on the FLTb pin to AVCC. Place a 10pF capacitor from FLTb to GND for SET mitigation. |

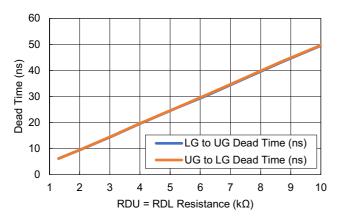

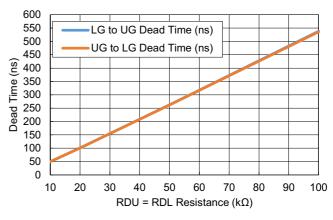

| 3             | RDU      | 1              | Dead time delay control for the high-side turn-on. A $1k\Omega$ - $10k\Omega$ resistor to GND sets the rising edge delay of Upper Gate High (UGH) to the falling edge of Lower Gate Low (LGL) in the range of 6.5ns to 50ns. Connect RDU to SGND for 6.5ns delay.                                                               |

| 4             | RDL      | 1              | Dead time delay control for low-side turn-on. A $1k\Omega$ - $10k\Omega$ resistor to GND sets the rising edge delay of Lower Gate High (LGH) to the falling edge of Upper Gate Low (UGL) in the range of 6.5ns-50ns. Connect RDL to SGND for 6.5ns delay.                                                                       |

| 5             | AVCC     | 1              | Output of the internal 5V LDO regulator for chip bias. Input is VDD. A minimum of 1µF ceramic decoupling capacitor is necessary on AVCC to SGND.                                                                                                                                                                                |

| 6             | SGND     | -              | Analog signal GND pin. Connect to the EPAD and to the ground plane.                                                                                                                                                                                                                                                             |

| 7             | VDD      | 2              | Input supply to chip. Bias range is 4.75V to 18V.                                                                                                                                                                                                                                                                               |

| 8             | FB       | 1              | PVCC LDO error amplifier inverting input. A resistor divider network from FB to PVCC and SGND sets the PVCC LDO output voltage. If FB is connected to PVCC, PVCC output voltage is 4.5V.                                                                                                                                        |

| Pin<br>Number                                                                                                                                                                                     | Pin Name                            | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 9                                                                                                                                                                                                 | PVCC                                | 1              | Output of the LDO for the low-side gate drive voltage. Recommended PVCC range is 4.5V to 5.5V. A minimum $1\mu F$ ceramic decoupling capacitor is necessary on PVCC to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Low-side driver output reference pin. For typical applications, connect PGND to the group plane, EPAD, and SGND. Alternatively, connect PGND directly to the low-side transistor source terminal. |                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 11                                                                                                                                                                                                | LGL                                 | 5              | Low-side sink driver for gate turn-off. Connect this pin to LGH and to the GaN FET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 12                                                                                                                                                                                                | LGH                                 | 4              | Low-side source driver for gate turn-on. Connect this pin to LGL and to the GaN FET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 13                                                                                                                                                                                                | NC                                  | -              | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 14                                                                                                                                                                                                | PHS                                 | 3              | High-side GaN FET source reference. Connect to the phase switching node of the half-bridge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 15                                                                                                                                                                                                | UGL                                 | 7              | High-side sink driver for gate turn-off. Connect this pin to UGH and to the GaN FET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 16                                                                                                                                                                                                | UGH                                 | 6              | High-side source driver for gate turn-on. Connect this pin to UGL and to the GaN FET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 17                                                                                                                                                                                                | воот                                | 3              | High-side bootstrap bias pin. Connect a bootstrap capacitor from this pin to PHS. An internal bootstrap switch refreshes the bootstrap capacitor when PWM = 0 and PHS voltage is within 300mV of PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 18                                                                                                                                                                                                | NC                                  | -              | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

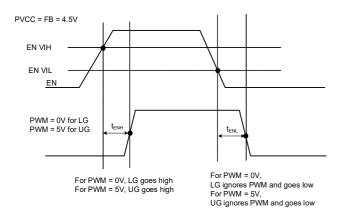

| 19                                                                                                                                                                                                | EN                                  | 2              | Enable input pin. When EN is low, driver outputs are in a high-impedance state and do not respond to PWM inputs. The PVCC LDO is shutdown and the FLTb pin is internally pulled low. When EN is high, the PVCC LDO is enabled and the driver outputs respond to PWM inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 20                                                                                                                                                                                                | PWM                                 | 1              | Tri-Level PWM input pin. Logic high turns on the high-side gate driver. Logic low turns on the low-side gate driver. Mid-Level actively turns off both gate drivers. Internal pull-up and pull-down resistors bias pin to mid-level when not externally driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| EPAD                                                                                                                                                                                              | -                                   | -              | Package bottom thermal pad. The die substrate is connected to EPAD. Connect to SGND and the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                   | ackage<br>Pin<br>PGND □—<br>Circuit | 9.6V<br>Clam   | Package Pin  28.8V Clamp  PGND  PGND  Circuit 2  PGND  Circuit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Pin<br>PGND 1                                                                                                                                                                                     | 0.7<br>A Clar                       | V<br>mp<br>Pa  | Package Pin BOOT 0.7V Clamp Ckage Pin Package Pin Pack |  |  |  |  |

| Cir                                                                                                                                                                                               | cuit 4                              |                | Circuit 5 Circuit 6 Circuit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

## 3. Specifications

### 3.1 Absolute Maximum Ratings

**Caution:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                          | Minimum     | Maximum  | Unit |

|----------------------------------------------------|-------------|----------|------|

| PVCC to PGND; BOOT to PHS                          | -0.3        | +6.5     | V    |

| VDD to SGND                                        | -0.3        | +20      | V    |

| SGND to PGND                                       | -0.3        | +0.3     | V    |

| PHS to PGND                                        | -0.3V DC    | +20      | V    |

| PHS to PGND <sup>[1]</sup>                         | -           | +16.5    | V    |

| PHS to PGND <sup>[2]</sup>                         | -           | +13.5    | V    |

| PHS to PGND (repetitive transient)                 | -5V (100ns) | -        | V    |

| BOOT to PGND                                       | -0.3        | +24      | V    |

| BOOT to PGND <sup>[1]</sup>                        | -           | +21.5    | V    |

| BOOT to PGND <sup>[2]</sup>                        | -           | +18.5    | V    |

| EN to SGND                                         | -0.3        | VDD+0.3  | V    |

| AVCC, FB, PWM, FLTb, RDU, RDL to SGND              | -0.3        | +6.5     | V    |

| UGH, UGL                                           | PHS-0.3     | BOOT+0.3 | V    |

| LGH, LGL                                           | GND-0.3     | PVCC+0.3 | V    |

| Maximum Junction Temperature                       | -           | +150     | °C   |

| Maximum Storage Temperature Range                  | -65         | +150     | °C   |

| Human Body Model (Tested per MIL-STD-883 TM3015.7) | -           | 5        | kV   |

| Charged Device Model (Tested per JS-002-2022)      | -           | 2        | kV   |

| Latch-Up (Tested per JESD78E; Class 2, Level A)    | -           | ±100     | mA   |

<sup>1.</sup> Tested in a heavy ion environment at LET = 67MeV•cm<sup>2</sup>/mg at 125°C.

## 3.2 Outgas Testing

| Specification (Tested per ASTM E595, 1.5)              | Value | Unit |

|--------------------------------------------------------|-------|------|

| Total Mass Lost <sup>[1]</sup>                         | 0.08  | %    |

| Collected Volatile Condensible Material <sup>[1]</sup> | 0.01  | %    |

| Water Vapor Recovered                                  | 0.02  | %    |

<sup>1.</sup> Outgassing results meet NASA requirements of total mass loss <1% and collected volatile condensible material <0.1%.

<sup>2.</sup> Tested in a heavy ion environment at LET = 86MeV•cm<sup>2</sup>/mg at 125°C.

#### 3.3 Thermal Information

| Parameter          | Package                | Symbol              | Conditions           | Typical<br>Value | Unit |

|--------------------|------------------------|---------------------|----------------------|------------------|------|

| Thermal Resistance | 20Ld Plastic 5x5mm QFN | $\theta_{JA}^{[1]}$ | Junction to ambient. | 32               | °C/W |

|                    | Package                | θ <sub>JC</sub> [2] | Junction to case.    | 2                | °C/W |

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features.

See TB379.

### 3.4 Recommended Operating Conditions

| Parameter           | Minimum | Maximum | Unit |

|---------------------|---------|---------|------|

| Ambient Temperature | -55     | +125    | °C   |

| VDD Voltage         | +4.75   | +13.2   | V    |

| PVCC                | +4.5    | +5.5    | V    |

| PHS                 | 0       | +13.2   | V    |

### 3.5 Electrical Specifications

#### 3.5.1 DC Electrical Specifications

| Parameter                     | Symbol              | Test Conditions                                                  | Temp.               | Min   | Typ. <sup>[1]</sup> | Max   | Unit |

|-------------------------------|---------------------|------------------------------------------------------------------|---------------------|-------|---------------------|-------|------|

| VDD Power Supply              |                     |                                                                  |                     | ı     |                     |       | ·    |

| Shutdown Supply Current       | IDD <sub>SHDN</sub> | EN = 0V                                                          | -55 to<br>+125°C    | -     | 850                 | 1200  | μA   |

| Ouisesent Comply Compant      |                     | PWM = Float; RDU = RDL = 1.3kΩ                                   | -55 to              | -     | 9                   | -     | A    |

| Quiescent Supply Current      | I <sub>DDQ</sub>    | PWM = Float; RDU = RDL = 10kΩ                                    | +125°C              | -     | -                   | 6     | - mA |

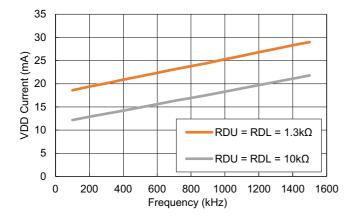

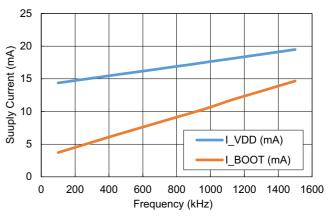

| Unloaded Operating<br>Current | I <sub>DDO1</sub>   | UG and LG unloaded;<br>PWM = 500kHz at 50% 0V to 5V              | -55 to<br>+125°C    | -     | 21                  | 32    | mA   |

| Loaded Operating Current      | I <sub>DDO2</sub>   | 5nF load on UG; 10nF load on LG;<br>PWM = 500kHz at 50% 0V to 5V | -55 to<br>+125°C    | -     | 55                  | 70    | mA   |

| Bootstrap Supply              |                     |                                                                  | •                   | •     |                     |       | •    |

| BOOT Quiescent Current        | I <sub>Q_Boot</sub> | PWM = Float; BOOT-PHS = 4.5V                                     | -55 to<br>+125°C    | -     | 580                 | 650   | μA   |

| PVCC and AVCC LDOs            |                     |                                                                  |                     | •     |                     |       | •    |

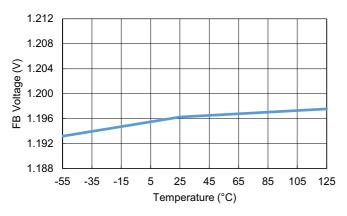

|                               |                     |                                                                  | -55°C               | 1.182 | 1.2                 | 1.206 |      |

|                               |                     |                                                                  | +25°C               | 1.188 | 1.2                 | 1.212 |      |

| PVCC Feedback Voltage         | VFB                 | VFB Internal reference voltage                                   | +125°C              | 1.188 | 1.2                 | 1.212 | V    |

|                               |                     |                                                                  | +25°C<br>(Post Rad) | 1.188 | 1.2                 | 1.212 |      |

<sup>2.</sup> For  $\theta_{\mbox{\scriptsize JC}},$  the case temp location is the center of the package underside.

| Parameter                     | Symbol               | Test Conditions                                                                                       | Temp.               | Min  | Typ. <sup>[1]</sup> | Max  | Unit |

|-------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|------|

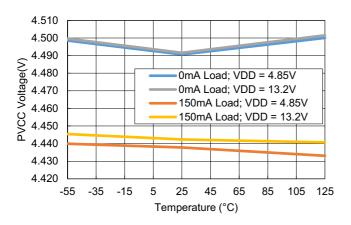

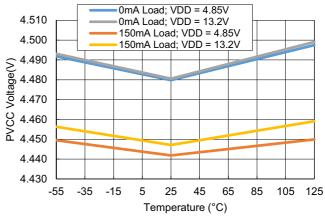

|                               |                      |                                                                                                       | -55°C               | 4.38 | 4.5                 | 4.6  |      |

|                               |                      | PVCC = 4.5V = FB or with external                                                                     | +25°C               | 4.4  | 4.5                 | 4.6  | ]    |

|                               |                      | resistors; I <sub>OUT</sub> from 0mA to 150mA;<br>VDD from 4.85V to 13.2V                             | +125°C              | 4.38 | 4.5                 | 4.6  | V    |

| DV00 0 1 D : V II             | D1/00                | 100 Holli 4.65V to 15.2V                                                                              | +25°C<br>(Post Rad) | 4.39 | 4.5                 | 4.6  | -    |

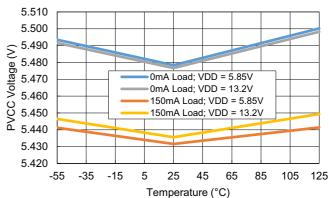

| PVCC Gate Drive Voltage       | PVCC                 |                                                                                                       | -55°C               | 5.38 | 5.5                 | 5.6  |      |

|                               |                      | PVCC = 5.5V with external FB                                                                          | +25°C               | 5.4  | 5.5                 | 5.6  |      |

|                               |                      | resistors; I <sub>OUT</sub> from 0mA to 150mA;<br>VDD from 5.85V to 13.2V                             | +125°C              | 5.38 | 5.5                 | 5.6  | V    |

|                               |                      | VDD IIOII 3.33V to 13.2V                                                                              | +25°C<br>(Post Rad) | 5.39 | 5.5                 | 5.6  |      |

| PVCC in Pass Mode             | -                    | VDD = 4.75V; FB = PVCC;<br>I <sub>OUT</sub> = 150mA                                                   | -55 to<br>+125°C    | 4.34 | 4.44                | -    | V    |

| PVCC Dropout Voltage          | -                    | I <sub>OUT</sub> = 150mA; VDD voltage where<br>PVCC drops 2% below regulation;<br>PVCC = 4.5V to 5.5V | -55 to<br>+125°C    | -    | 190                 | 250  | mV   |

| PVCC Output Current<br>Limit  | I <sub>LIMITP</sub>  | VDD = 4.75V; FB = PVCC;<br>Force PVCC = 4.2V                                                          | -55 to<br>+125°C    | 190  | 250                 | 350  | mA   |

| VDD to PVCC Power             | PVCC <sub>PSRR</sub> | VDD = 6V + 300mVpp AC 1kHz;<br>PVCC = 5.5V; PVCC I <sub>OUT</sub> = 150mA                             | -                   | -    | 70                  | -    | - dB |

| Supply Rejection Ratio        |                      | VDD = 6V + 300mVpp AC 100kHz;<br>PVCC = 5.5V; PVCC I <sub>OUT</sub> = 150mA                           | -                   | -    | 30                  | -    |      |

|                               |                      | VDD = 4.97V; I <sub>OUT</sub> = 20mA                                                                  | FF 1-               | 4.3  | 4.6                 | 4.69 |      |

| Internal LDO voltage          | AVCC                 | VDD = 5.25V to 13.2V; I <sub>OUT</sub> = 0mA to 20mA                                                  | 55 to<br>+125°C     | 4.7  | 5.0                 | 5.4  | V    |

| Dropout Voltage               | -                    | I <sub>OUT</sub> = 20mA; VDD voltage where<br>AVCC drops 2% below regulation                          | -55 to<br>+125°C    | -    | -                   | 250  | mV   |

| AVCC Output Current<br>Limit  | I <sub>LIMITA</sub>  | VDD = 4.75V;<br>Force AVDD = 4.5V                                                                     | -55 to<br>+125°C    | 25   | 49                  | 100  | mA   |

| VDD to AVCC Power             | AV (O.C.             | VDD = 6V + 300mVpp AC 1kHz;<br>AVCC = 5V; AVCC I <sub>OUT</sub> = 20mA                                | -                   | -    | 70                  | -    | -ID  |

| Supply Rejection Ratio        | AVCC <sub>PSRR</sub> | VDD = 6V + 300mVpp AC 100kHz;<br>AVCC = 5V; AVCC I <sub>OUT</sub> = 20mA                              | -                   | -    | 30                  | -    | - dB |

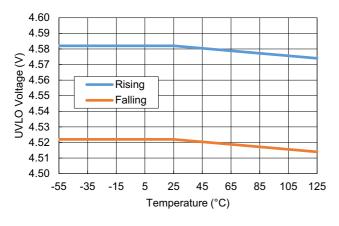

| VDD Undervoltage Locko        | ut (UVLO)            |                                                                                                       | 1                   | •    | ľ                   |      |      |

| VDD UVLO Rising<br>Threshold  | VR <sub>VDD</sub>    | -                                                                                                     | -55 to<br>+125°C    | 4.46 | 4.6                 | 4.74 | V    |

| VDD UVLO Falling<br>Threshold | VF <sub>VDD</sub>    | -                                                                                                     | -55 to<br>+125°C    | 4.41 | 4.55                | 4.68 | V    |

| VDD UVLO Hysteresis           | VH <sub>VDD</sub>    | VR <sub>VDD</sub> - VF <sub>VDD</sub>                                                                 | -55 to<br>+125°C    | 25   | 50                  | 90   | mV   |

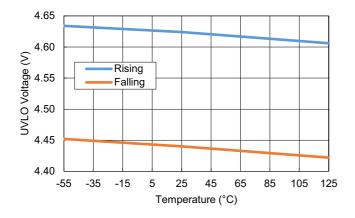

| AVCC Undervoltage Lock        | out (UVLO)           | 1                                                                                                     | 1                   | 1    | ı                   |      |      |

| AVCC UVLO Rising<br>Threshold | VR <sub>AVCC</sub>   | Test by recovering AVCC from constant current limit                                                   | -55 to<br>+125°C    | 4.46 | 4.6                 | 4.74 | V    |

| Parameter                      | Symbol             | Test Conditions                                  | Temp.            | Min  | Typ. <sup>[1]</sup> | Max  | Unit |

|--------------------------------|--------------------|--------------------------------------------------|------------------|------|---------------------|------|------|

| AVCC UVLO Falling<br>Threshold | VF <sub>AVCC</sub> | Test by putting AVCC into constant current limit | -55 to<br>+125°C | 4.28 | 4.41                | 4.52 | V    |

| AVCC UVLO Hysteresis           | VH <sub>AVCC</sub> | VR <sub>AVCC</sub> - VF <sub>AVCC</sub>          | -55 to<br>+125°C | 150  | 183                 | 300  | mV   |

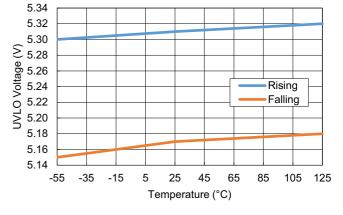

| PVCC Undervoltage Lock         | out (UVLO)         |                                                  |                  |      |                     |      |      |

| PVCC UVLO Rising<br>Threshold  | VR <sub>PVCC</sub> | PVCC = 5.5V with FB resistors <sup>[2]</sup>     | -55 to<br>+125°C | 5.21 | 5.34                | 5.45 | V    |

| PVCC UVLO Falling<br>Threshold | VF <sub>PVCC</sub> | PVCC = 5.5V with FB resistors <sup>[2]</sup>     | -55 to<br>+125°C | 5.07 | 5.17                | 5.27 | V    |

| PVCC UVLO Hysteresis           | VH <sub>PVCC</sub> | VR <sub>PVCC</sub> - VF <sub>PVCC</sub>          | -55 to<br>+125°C | 100  | 150                 | 300  | mV   |

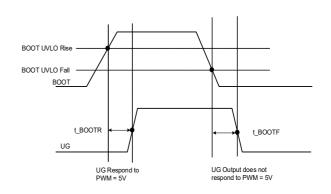

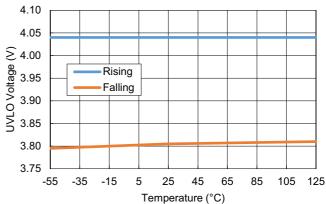

| BOOT Undervoltage Lock         | out (UVLO)         |                                                  |                  |      |                     |      |      |

| BOOT UVLO Rising<br>Threshold  | VR <sub>BOOT</sub> | -                                                | -55 to<br>+125°C | 3.8  | 4.0                 | 4.2  | ٧    |

| BOOT UVLO Falling<br>Threshold | VF <sub>BOOT</sub> | -                                                | -55 to<br>+125°C | 3.6  | 3.8                 | 4.0  | V    |

| BOOT UVLO Hysteresis           | VH <sub>BOOT</sub> | VR <sub>BOOT</sub> - VF <sub>BOOT</sub>          | -55 to<br>+125°C | 100  | 240                 | 400  | mV   |

| PWM and EN Input Pins          |                    |                                                  |                  |      |                     |      |      |

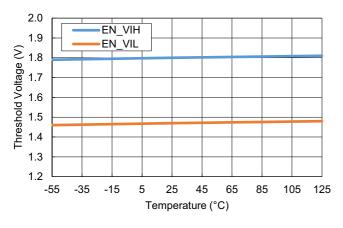

| EN High Level Threshold        | VIH <sub>EN</sub>  | PWM = 0V                                         | -55 to<br>+125°C | -    | 1.8                 | 2.0  | V    |

| EN Low Level Threshold         | VIL <sub>EN</sub>  | PWM = 0V                                         | -55 to<br>+125°C | 1.0  | 1.5                 | -    | V    |

| EN Input Hysteresis            | VHYS <sub>EN</sub> | VIH <sub>EN</sub> - VIL <sub>EN</sub>            | -55 to<br>+125°C | 100  | 325                 | 400  | mV   |

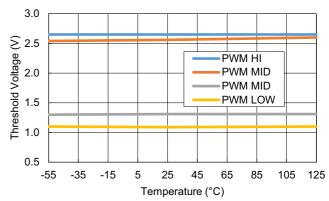

| PWM High Threshold             | V <sub>PWMH</sub>  | VDD = 4.75V to 13.2V                             | -55 to<br>+125°C | -    | 2.7                 | 2.8  | ٧    |

| PWM Middle Level Range         | V <sub>PWMM</sub>  | VDD = 4.75V to 13.2V                             | -55 to<br>+125°C | 1.45 | -                   | 2.4  | ٧    |

| PWM Low Threshold              | V <sub>PWML</sub>  | VDD = 4.75V to 13.2V                             | -55 to<br>+125°C | 0.90 | 1.1                 | -    | V    |

| Mid-High Level Hysteresis      | -                  | VDD = 4.75V to 13.2V                             | -55 to<br>+125°C | -    | 100                 | 200  | mV   |

| Mid-Low Level Hysteresis       | -                  | VDD = 4.75V to 13.2V                             | -55 to<br>+125°C | -    | 200                 | 350  | mV   |

| PWM High Input Current         | I <sub>PWMH</sub>  | PWM = 5V                                         | -55 to<br>+125°C | 10   | 33                  | 50   | μA   |

| PWM Low Input Current          | I <sub>PWML</sub>  | PWM = 0V                                         | -55 to<br>+125°C | -50  | -22                 | -10  | μA   |

| PWM Pin Pull-Up Resistor       | R <sub>PWMU</sub>  | -                                                | -55 to<br>+125°C | 150  | 225                 | 300  | kΩ   |

| PWM Pin Pull-Down<br>Resistor  | R <sub>PWML</sub>  | -                                                | -55 to<br>+125°C | 100  | 150                 | 200  | kΩ   |

| Parameter                                   | Symbol              | Test Conditions                                                               | Temp.            | Min  | Typ. <sup>[1]</sup> | Max   | Unit |

|---------------------------------------------|---------------------|-------------------------------------------------------------------------------|------------------|------|---------------------|-------|------|

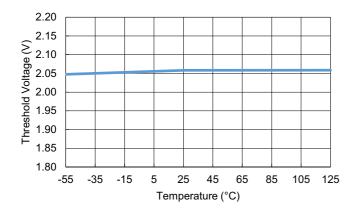

| PWM Pin Floating Voltage                    | $V_{FLOAT}$         | -                                                                             | -55 to<br>+125°C | 1.90 | 2.0                 | 2.135 | V    |

| Bootstrap FET Switch                        |                     |                                                                               |                  | -    |                     |       |      |

| Low Current Voltage                         | $V_{SWL}$           | 100μA through switch                                                          | -55 to<br>+125°C | -    | 1                   | 1.6   | mV   |

| High Current Voltage                        | $V_{SWH}$           | 100mA through switch                                                          | -55 to<br>+125°C | -    | -                   | 145   | mV   |

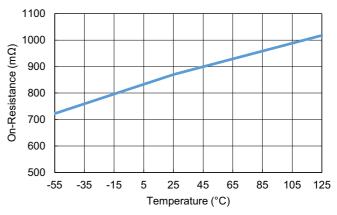

| BOOT Switch Resistance                      | R <sub>SW</sub>     | 100mA through switch                                                          | -55 to<br>+125°C | -    | -                   | 1.45  | Ω    |

| Positive Window Detect<br>Rising Threshold  | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | 160  | 250                 | 400   | mV   |

| Positive Window Detect Falling Threshold    | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | 140  | 220                 | 380   | mV   |

| Negative Window Detect<br>Rising Threshold  | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | -380 | -210                | -140  | mV   |

| Negative Window Detect<br>Falling Threshold | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | -400 | -240                | -160  | mV   |

| Positive Window Detect<br>Hysteresis        | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | 10   | 25                  | 60    | mV   |

| Negative Window Detect<br>Hysteresis        | -                   | PWM = 0V                                                                      | -55 to<br>+125°C | 10   | 20                  | 60    | mV   |

| FLTb Open Drain with Inter                  | rnal Detect         |                                                                               | L                | ı    |                     |       | 1    |

| Input High Leakage<br>Current               | I <sub>LEAK</sub>   | FLTb = AVCC; VDD = 13.2V<br>EN = VDD; No fault condition                      | -55 to<br>+125°C | -1   | -                   | 1     | μA   |

| FLTb Output Low Drive                       | V <sub>OL</sub>     | I <sub>SINK</sub> = 10mA; EN = 0V                                             | -55 to<br>+125°C | -    | 0.18                | 0.4   | V    |

| Fault Detect Input High<br>Threshold        | V <sub>IH</sub>     | VDD = 13.2V; EN = VDD                                                         | -55 to<br>+125°C | 2.0  | 2.4                 | 2.8   | V    |

| Fault Detect Input Low<br>Threshold         | $V_{IL}$            | VDD = 13.2V; EN = VDD                                                         | -55 to<br>+125°C | 1.0  | 1.6                 | 2.0   | V    |

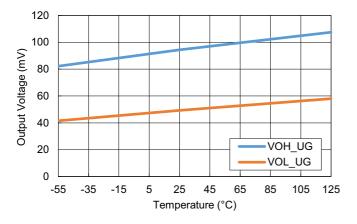

| Upper Gate High Output (U                   | JGH)                |                                                                               | l                | ı    |                     | I     | 1    |

| UGH Peak Source Current                     | IUGH <sub>SRC</sub> | VDD = 4.75V; FB = PVCC;<br>BOOT-PHS = 4.5V;<br>PWM = 5V; 470nF load on UG-PHS | -                | -    | 2                   | -     | А    |

| UGH Output High Voltage                     | VOH <sub>UGH</sub>  | I <sub>SOURCE</sub> = 100mA; Voltage drop<br>below BOOT                       | -55 to<br>+125°C | -    | 90                  | 130   | mV   |

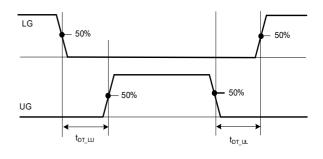

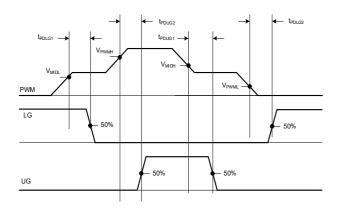

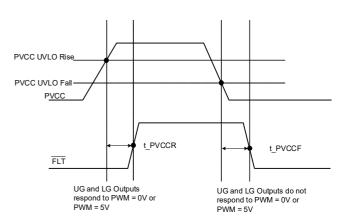

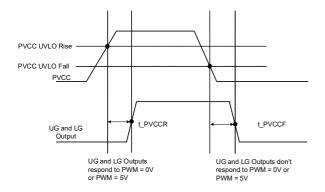

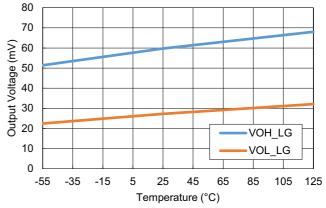

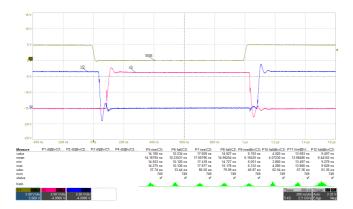

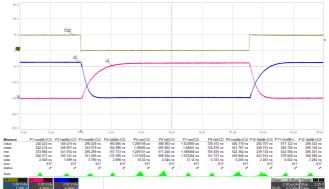

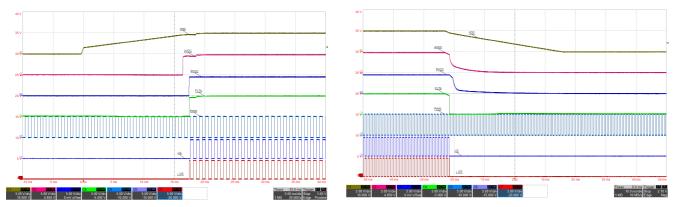

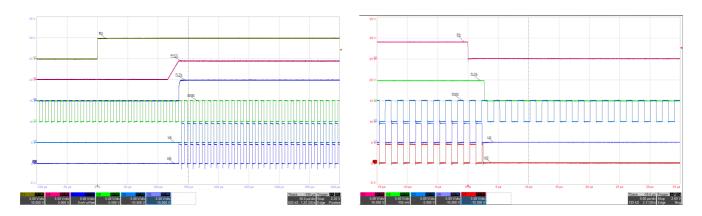

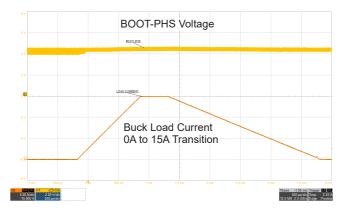

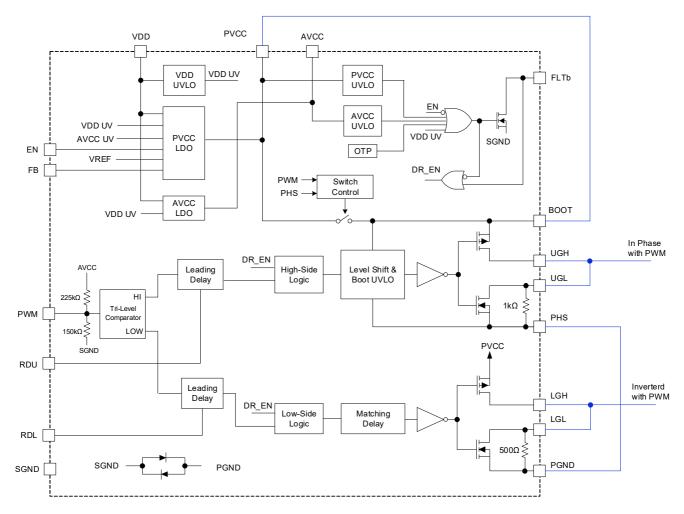

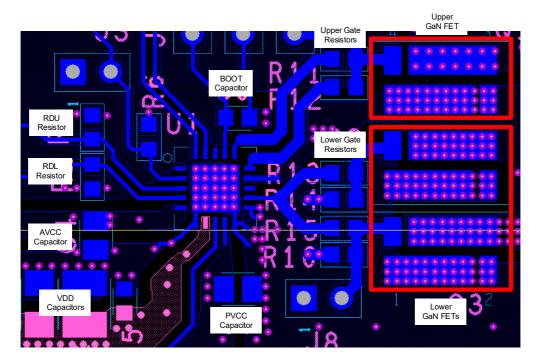

| Lower Gate High Output (L                   | .GH)                | •                                                                             |                  |      |                     |       |      |