# 3.3V LVCMOS-to-LVPECL 1:4 Fanout Buffer MC100ES6535

# PRODUCT DISCONTINUANCE NOTICE - LAST TIME BUY EXPIRES ON (11/18/13)

**DATA SHEET**

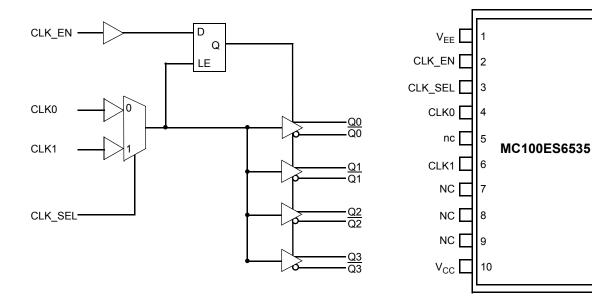

The MC100ES6535 is a low skew, high performance 3.3 V 1-to-4 LVCMOS to LVPECL fanout buffer. The ES6535 has two selectable inputs that allow LVCMOS or LVTTL input levels which translate to LVPECL outputs. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. The ES6535 is ideal for high performance clock distribution applications.

#### **Features**

- 4 differential LVPECL outputs

- 2 selectable LVCMOS/LVTTL inputs

- 1 GHz maximum output frequency

- Translates LVCMOS/LVTTL levels to LVPECL levels

- 30 ps maximum output skew

- 190 ps part-to-part skew

- 3.3 V operating range

- 20-lead TSSOP package

- Ambient temperature range -40°C to +85°C

- 20-lead Pb-free package available

- Use replacement part: ICS8535I-01

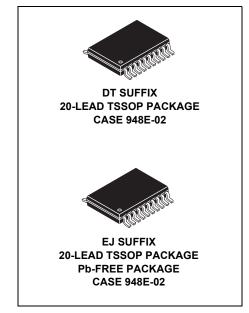

| ORDERING INFORMATION |                    |  |  |  |  |  |  |

|----------------------|--------------------|--|--|--|--|--|--|

| Device               | Package            |  |  |  |  |  |  |

| MC100ES6535DT        | TSSOP-20           |  |  |  |  |  |  |

| MC100ES6535DTR2      | TSSOP-20           |  |  |  |  |  |  |

| MC100ES6535EJ        | TSSOP-20 (Pb-Free) |  |  |  |  |  |  |

| MC100ES6535EJR2      | TSSOP-20 (Pb-Free) |  |  |  |  |  |  |

**Table 1. Pin Description**

| Number     | Name              | Ту     | /pe                     | Description                                                                                                                                                                        |

|------------|-------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>EE</sub>   | Power  |                         | Negative supply pin                                                                                                                                                                |

| 2          | CLK_EN            | Input  | Pullup <sup>(1)</sup>   | Synchronizing clock enable. When HIGH, clock outputs follow clock input. When LOW, Q outputs are forced low, $\overline{Q}$ outputs are forced high. LVCMOS/LVTTL interface levels |

| 3          | CLK_SEL           | Input  | Pulldown <sup>(1)</sup> | Clock select input. When HIGH, selects CLK1 input When LOW, selects CLK0 input. LVCMOS/LVTTL interface levels                                                                      |

| 4          | CLK0              | Input  | Pulldown <sup>(1)</sup> | LVCMOS/LVTTL clock input                                                                                                                                                           |

| 6          | CLK1              | Input  | Pulldown <sup>(1)</sup> | LVCMOS/LVTTL clock input                                                                                                                                                           |

| 5, 7, 8, 9 | NC                | Unused |                         | No connect                                                                                                                                                                         |

| 10, 13, 18 | V <sub>CC</sub>   | Power  |                         | Positive supply pin                                                                                                                                                                |

| 11, 12     | Q3, <del>Q3</del> | Output |                         | LVPECL differential output pair                                                                                                                                                    |

| 14, 15     | Q2, <del>Q2</del> | Output |                         | LVPECL differential output pair                                                                                                                                                    |

| 16, 17     | Q1, Q1            | Output |                         | LVPECL differential output pair                                                                                                                                                    |

| 19, 20     | Q0, Q0            | Output |                         | LVPECL differential output pair                                                                                                                                                    |

<sup>1.</sup> Pullup and Pulldown refer to internal input resistors.

Table 2. Control Input Function Table<sup>(1)</sup>

|        | Inputs  | Outputs         |               |                |

|--------|---------|-----------------|---------------|----------------|

| CLK_EN | CLK_SEL | Selected Source | Q0:Q3         | Q0:Q3          |

| 0      | 0       | CLK0            | Disabled; LOW | Disabled; HIGH |

| 0      | 1       | CLK1            | Disabled; LOW | Disabled; HIGH |

| 1      | 0       | CLK0            | Enabled       | Enabled        |

| 1      | 1       | CLK1            | Enabled       | Enabled        |

<sup>1.</sup> After CLK\_EN switches, the clock outputs are disabled or enabled following a rising and falling input clock edge. In the active mode, the state of the outputs are a function of the CLK0 and CLK1 inputs as described in .

Figure 1. Logic Diagram

Figure 2. 20-Lead Pinout (Top View)

20

19

18

17

16

15

14

13

12

11

Q0

Q0

$V_{CC}$

Q1

Q1

Q2

Q2

$V_{CC}$

Q3

Q3

### . Clock Input Function Table

| Inputs       | Outputs |       |  |  |  |  |

|--------------|---------|-------|--|--|--|--|

| CLK0 or CLK1 | Q0:Q3   | Q0:Q3 |  |  |  |  |

| 0            | LOW     | HIGH  |  |  |  |  |

| 1            | HIGH    | LOW   |  |  |  |  |

### Table 3. General Specifications

| Characteristics                                             | Value                                  |                    |

|-------------------------------------------------------------|----------------------------------------|--------------------|

| Internal Input Pulldown Resistor                            | 75 kΩ                                  |                    |

| Internal Input Pullup Resistor                              | 75 kΩ                                  |                    |

| ESD Protection                                              | Human Body Model<br>Machine Model      | 4000 V<br>200 V    |

| θ <sub>JA</sub> Thermal Resistance<br>(Junction-to-Ambient) | 0 LFPM, 20 TSSOP<br>500 LFPM, 20 TSSOP | 140°C/W<br>100°C/W |

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

# Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol              | Rating                      | Conditions                                           | Rating                                       | Units    |

|---------------------|-----------------------------|------------------------------------------------------|----------------------------------------------|----------|

| V <sub>SUPPLY</sub> | Power Supply Voltage        | Difference between V <sub>CC</sub> & V <sub>EE</sub> | 3.9                                          | V        |

| V <sub>IN</sub>     | Input Voltage               | $V_{CC} - V_{EE} \le 3.6 \text{ V}$                  | V <sub>CC</sub> +0.3<br>V <sub>EE</sub> -0.3 | V<br>V   |

| l <sub>out</sub>    | Output Current              | Continuous<br>Surge                                  | 50<br>100                                    | mA<br>mA |

| T <sub>A</sub>      | Operating Temperature Range |                                                      | -40 to +85                                   | °C       |

| T <sub>store</sub>  | Storage Temperature Range   |                                                      | -65 to +150                                  | °C       |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

# Table 5. DC Characteristics ( $V_{CC}$ = 3.135 V to 3.8 V; $V_{EE}$ = 0 V)

| Symbol                         | Characteristic       |                       | -40°C                 |                       |                       | Unit                  |                       |       |

|--------------------------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|

| Symbol                         | Characteristic       | Min                   | Тур                   | Max                   | Min                   | Тур                   | Max                   | Oilit |

| I <sub>EE</sub>                | Power Supply Current |                       |                       | 35                    |                       |                       | 45                    | mA    |

| V <sub>OH</sub> <sup>(1)</sup> | Output HIGH Voltage  | V <sub>CC</sub> -1150 | V <sub>CC</sub> -1020 | V <sub>CC</sub> -800  | V <sub>CC</sub> -1200 | V <sub>CC</sub> -970  | V <sub>CC</sub> -750  | mV    |

| V <sub>OL</sub>                | Output LOW Voltage   | V <sub>CC</sub> -1950 | V <sub>CC</sub> -1620 | V <sub>CC</sub> -1250 | V <sub>CC</sub> -2000 | V <sub>CC</sub> -1680 | V <sub>CC</sub> -1300 | mV    |

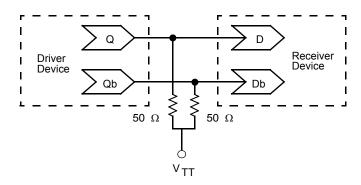

<sup>1.</sup> Outputs are terminated through a  $50\Omega$  resistor to  $V_{\mbox{\footnotesize{CC}}}$  – 2 volts.

# Table 6. LVTTL / LVCMOS Input DC Characteristics ( $V_{CC}$ = 3.135 V to 3.8 V)

| Symbol Characteristic |                     | Condition                         | -40°C |     |                      |     | Unit |                      |    |

|-----------------------|---------------------|-----------------------------------|-------|-----|----------------------|-----|------|----------------------|----|

| Symbol Characteristic | Condition           | Min                               | Тур   | Max | Min                  | Тур | Max  | Uill                 |    |

| I <sub>IN</sub>       | Input Current       | V <sub>IN</sub> = V <sub>CC</sub> |       |     | ±150                 |     |      | ±150                 | μΑ |

| V <sub>IK</sub>       | Input Clamp Voltage | I <sub>IN</sub> = -18 mA          |       |     | -1.2                 |     |      | -1.2                 | V  |

| V <sub>IH</sub>       | Input HIGH Voltage  |                                   | 2.0   |     | V <sub>CC</sub> +0.3 | 2.0 |      | V <sub>CC</sub> +0.3 | V  |

| V <sub>IL</sub>       | Input LOW Voltage   |                                   |       |     | 0.8                  |     |      | 0.8                  | V  |

Table 7. AC Characteristics ( $V_{CC}$  = 3.135 V to 3.8 V,  $V_{EE}$  = 0 V)

| Symbol                         | Symbol Characteristic -                 |                  | −40°C |     | 25°C      |     |     | 85°C      |     |     | Unit      |          |

|--------------------------------|-----------------------------------------|------------------|-------|-----|-----------|-----|-----|-----------|-----|-----|-----------|----------|

| Symbol                         |                                         |                  | Min   | Тур | Max       | Min | Тур | Max       | Min | Тур | Max       | Oille    |

| f <sub>max</sub>               | Maximum Toggle Frequency                |                  |       |     | 1         |     |     | 1         |     |     | 1         | GHz      |

| t <sub>PD</sub>                | Propagation Delay to Output Differentia | 1                | 150   | 350 | 500       | 175 | 360 | 550       | 200 | 380 | 600       | ps       |

| t <sub>SKEW</sub>              | Skew Output-to-0<br>Part-t              | Output<br>o-Part |       | 20  | 30<br>190 |     | 20  | 30<br>190 |     | 20  | 30<br>190 | ps<br>ps |

| t <sub>JITTER</sub>            | Cycle-to-Cycle Jitter RM                | S (1σ)           |       |     | 1         |     |     | 1         |     |     | 1         | ps       |

| V <sub>outPP</sub>             | Output Peak-to-Peak Voltage             | 3                | 350   | 750 |           | 350 | 750 |           | 350 | 750 |           | mV       |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall Time (20%-80% @ 50     | MHz)             | 50    |     | 400       | 50  |     | 400       | 50  |     | 400       | ps       |

Figure 3. Typical Termination for Output Driver and Device Evaluation

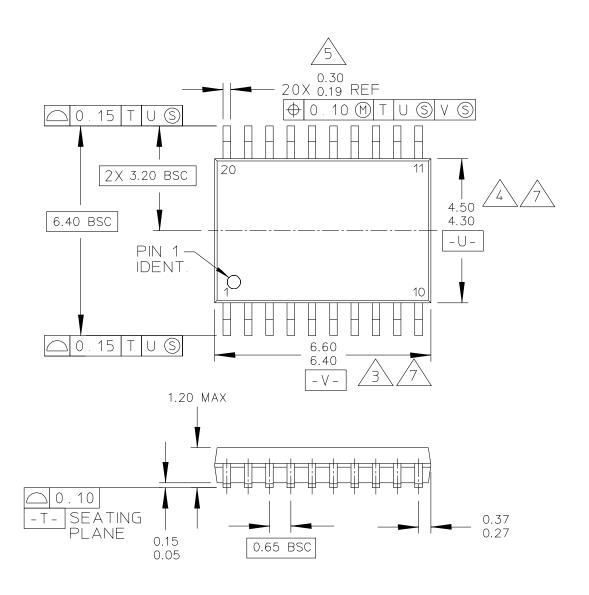

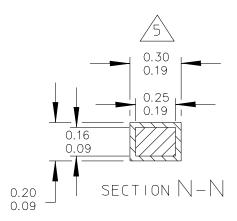

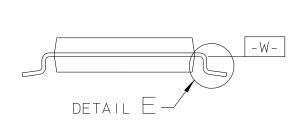

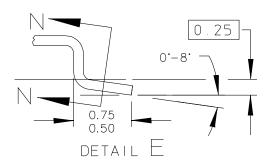

### **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICAL |                           | L OUTLINE    | PRINT VERSION NO | TO SCALE    |

|-------------------------------------------------------------------|---------------------------|--------------|------------------|-------------|

| TITLE:                                                            |                           | DOCUMENT NO  | ): 98ASH70169A   | RE√: C      |

| 20 LD TSSOP, PITCH                                                | 20 LD TSSOP, PITCH 0.65MM |              | 948E-02          | 25 MAY 2005 |

|                                                                   |                           | STANDARD: JE | DEC              |             |

PAGE 1 OF 3

## CASE 948E-02 ISSUE C 20-LEAD TSSOP PACKAGE

## PACKAGE DIMENSIONS

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |                          | L OUTLINE    | PRINT VERSION NO | TO SCALE    |

|------------------------------------------------------------------|--------------------------|--------------|------------------|-------------|

| TITLE:                                                           |                          | DOCUMENT NO  | ]: 98ASH70169A   | REV: C      |

| 20 LD ISSOP. PITCH                                               | 20 ID TSSUD DITCH 0.45MM |              |                  | 25 MAY 2005 |

| 20 23 10001, 111011                                              | 01001111                 | STANDARD: JE | DEC              |             |

PAGE 2 OF 3

CASE 948E-02 ISSUE C 20-LEAD TSSOP PACKAGE

#### PACKAGE DIMENSIONS

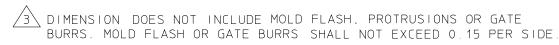

#### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

DIMENSIONS ARE TO BE DETERMINED AT DATUM PLANE -W-

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | L OUTLINE                 | PRINT VERSION NE | TO SCALE       |             |

|------------------------------------------------------|---------------------------|------------------|----------------|-------------|

| TITLE:                                               |                           | DOCUMENT NO      | I: 98ASH70169A | REV: C      |

| 20 ID ISSOP. PITCH 0                                 | 20 I D ISSUP PITCH 0.65MM |                  |                | 25 MAY 2005 |

|                                                      |                           | STANDARD: JE     | DEC            |             |

PAGE 3 OF 3

CASE 948E-02 ISSUE C 20-LEAD TSSOP PACKAGE

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                                                 | Date       |

|-----|-------|------|-------------------------------------------------------------------------------------------------------|------------|

| 4   |       | 1    | Product Discontinuance Notice - Last Time Buy Expires on (11/18/13) Use replacement part: ICS8535I-01 | 12/14/2012 |

|     |       |      |                                                                                                       |            |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.