#### RAA2P4500

Single Coil Inductive Position Sensor IC with Analog, PWM, SENT and I2C Interfaces

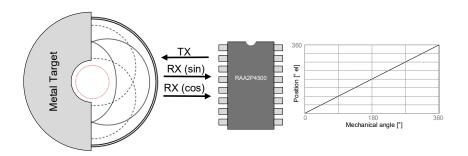

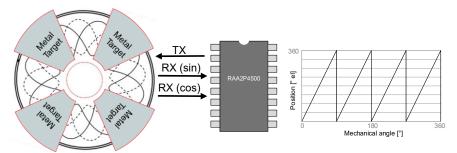

RAA2P4500 is a magnet-free, inductive position sensor ICs that can be used for absolute rotary, linear, or arc position sensing applications in automotive applications. It operates on the principle of eddy currents to detect the position of a simple metallic target that is moving above a set of coils, comprising one transmitter coil and two receiver coils.

These coils are typically copper traces on a printed circuit board (PCB). The transmitter coil induces a secondary voltage in the receiver coils, which varies depending on the position of the metallic target above them.

A signal representative of the target's position relative to the coils is calculated by demodulating and processing the secondary voltages from the receiver coils. The target can be made of various metals, including aluminum, steel, or a PCB with a printed copper layer.

The RAA2P4500 is equipped with:

- 12-bit Analog Output

- 12/14-bit PWM Output

- 12/14-bit SENT interface

- 14-bit I2C interface

- Additional analog voltage input for external devices.

- Digital input for external digital sensors. The information from external analog or digital inputs is available over the I2C interface.

The RAA2P4500 has been developed according to ISO26262 for implementation in safety-relevant systems up to ASIL C. It can also be used in ASIL D system-level requirements according to ASIL Decomposition rules (i.e. ISO 26262:2018, Part 9, Clause 5") or proper risk analysis by the system integrator.

### **Available Support**

Renesas provides application modules that demonstrate RAA2P4500 rotary, arc, and linear position sensing applications.

#### **Features**

- Cost-effective: no magnet required

- Immune to magnetic stray fields: no shielding required

- Suitable for harsh environments and high temperatures

- Analog, PWM, SENT, I2C interfaces

- SENT tick time programmable from 0.02 to 6µs

- Auxiliary 12-bit analog voltage input for external sensors

- Programmable through single wire UART and I2C protocol

- Nonvolatile memory enabling multiple programming options

- Single IC supports on-axis and off-axis rotation, linear motion, and arc motion sensing

- Adaptable to any full-scale angle range through coil design

- High accuracy position ≤0.1% full scale (with ideal coils), enabling sensor solutions up to 11-bit electrical accuracy

- Overvoltage and reverse polarity protection:

±18V on both supply and output pins

- Supply voltage programmable for: 3.3V ±0.3V or 5.0V ±0.5V

- Qualified for automotive application use from -40°C to +160°C ambient temperature

- Compliant to ISO26262 upto ASIL C

- 48 bits nonvolatile user ID memory space

- Small 16-TSSOP package (4.4mm × 5.0mm)

## **Typical Applications**

Linear and Angle position sensing in automotive applications: gas and brake pedals, chassis, valves.

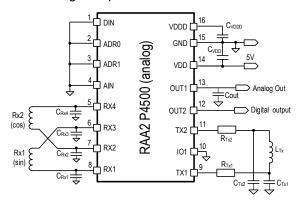

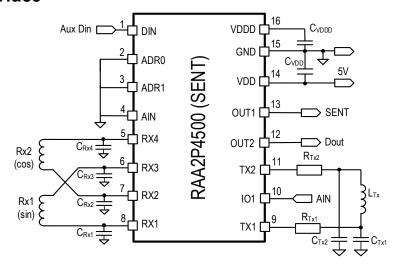

Figure 1. Application Circuit Example

## **Contents**

| 1.  | Pin / | Assignm         | nents and Descriptions                          | 5  |  |  |  |  |

|-----|-------|-----------------|-------------------------------------------------|----|--|--|--|--|

| 2.  | Spec  | cificatio       | n                                               | 6  |  |  |  |  |

|     | 2.1   | Absolu          | ıte Maximum Ratings                             | 6  |  |  |  |  |

|     | 2.2   | ESD R           | Ratings                                         | 7  |  |  |  |  |

|     | 2.3   | Operat          | ting Conditions                                 | 7  |  |  |  |  |

|     | 2.4   | Interfa         | ce Pin Characteristics                          | 10 |  |  |  |  |

| 3.  | Deta  | iled Des        | scription                                       | 13 |  |  |  |  |

|     | 3.1   | Overvi          | iew                                             | 13 |  |  |  |  |

|     | 3.2   | Block [         | Diagram                                         | 14 |  |  |  |  |

|     | 3.3   | LC Os           | cillator                                        |    |  |  |  |  |

|     |       | 3.3.1           | Parallel LC Resonator Calculations              | 15 |  |  |  |  |

|     | 3.4   | Coil De         | esign                                           | 16 |  |  |  |  |

|     |       | 3.4.1           | Multi-periodic Coil Design Application Examples | 17 |  |  |  |  |

|     |       | 3.4.2           | Electrical vs. Mechanical Degrees               | 18 |  |  |  |  |

| 4.  | Line  | arizatio        | n                                               | 19 |  |  |  |  |

| 5.  | Inter | faces           |                                                 | 20 |  |  |  |  |

|     | 5.1   | Analog          | g Interface                                     | 21 |  |  |  |  |

|     | 5.2   | PWM I           | Interface                                       | 22 |  |  |  |  |

|     |       | 5.2.1           | PWM Diagnostics Mode                            | 23 |  |  |  |  |

|     | 5.3   | SENT            | Interface                                       | 25 |  |  |  |  |

|     |       | 5.3.1           | SENT Protocol Frame                             | 25 |  |  |  |  |

|     | 5.4   | SENT            | Load Circuits                                   | 29 |  |  |  |  |

|     | 5.5   | I2C Int         | terface                                         | 30 |  |  |  |  |

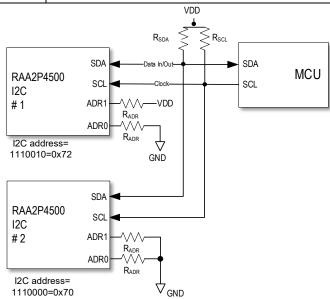

|     |       | 5.5.1           | I2C Addressing                                  | 30 |  |  |  |  |

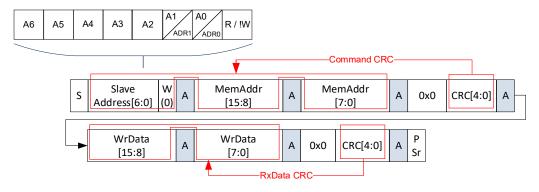

|     |       | 5.5.2           | I2C Register Write                              | 31 |  |  |  |  |

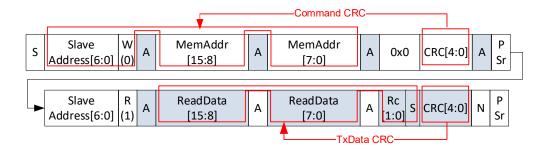

|     |       | 5.5.3           | I2C Register Read                               | 31 |  |  |  |  |

|     |       | 5.5.4           | I2C CRC Check                                   | 32 |  |  |  |  |

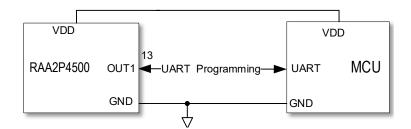

|     |       | 5.5.5           | UART Single Wire Programming Interface          | 32 |  |  |  |  |

| 6.  | Auxi  | iliary Inp      | outs and Outputs                                | 33 |  |  |  |  |

|     |       | 6.1.1           | Digital Input                                   | 33 |  |  |  |  |

|     |       | 6.1.2           | Analog Input                                    | 33 |  |  |  |  |

|     |       | 6.1.3           | Digital Output                                  | 33 |  |  |  |  |

| 7.  | On-0  | Chip Dia        | gnostics (Safety Mechanisms)                    | 34 |  |  |  |  |

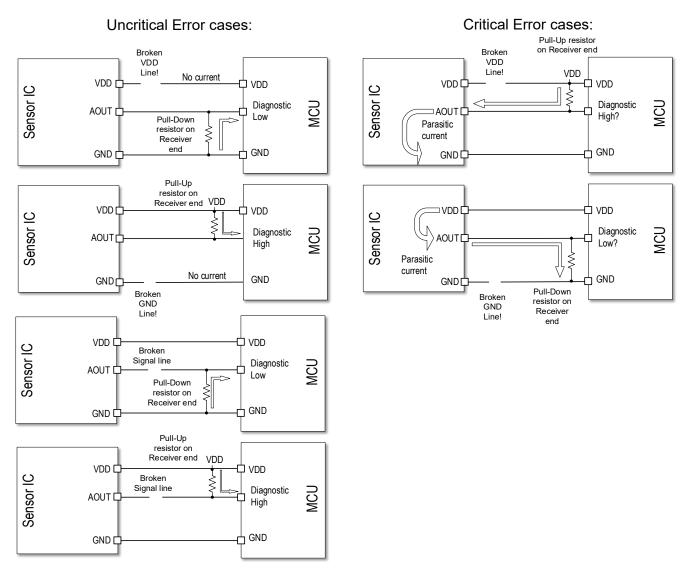

|     | 7.1   | Broker          | n Wires                                         | 36 |  |  |  |  |

| 8.  | Usei  | r Progra        | mming Options                                   | 38 |  |  |  |  |

| 9.  | Rela  | ted Doc         | cuments                                         | 38 |  |  |  |  |

| 10. | 16-T  | SSOP P          | Package Outline Drawings                        | 38 |  |  |  |  |

| 11. | Mark  | king Dia        | gram                                            | 39 |  |  |  |  |

| 12. | Orde  | ering Inf       | -<br>formation                                  | 39 |  |  |  |  |

| 13. | Glos  | -<br>Glossary39 |                                                 |    |  |  |  |  |

| 14. Revision History                                                            | 40      |

|---------------------------------------------------------------------------------|---------|

| Figures                                                                         |         |

| Figure 1. Application Circuit Example                                           | 1       |

| Figure 2. RAA2P4500                                                             |         |

| Figure 3. RAA2P4500 Input/Output Signals                                        |         |

| Figure 4. Block Diagram                                                         |         |

| Figure 5. TX LC Oscillator Connection                                           |         |

| Figure 6. Parallel Resonator Circuit                                            |         |

| Figure 7. Coil Design for a Linear Motion Sensor                                |         |

| Figure 8. Coil Design for a 360° Rotary Sensor                                  |         |

| Figure 9. Coil Design Using Single-Periodic Coil                                |         |

| Figure 10. Coil Design Using 4-Periodic Coil                                    |         |

| Figure 11. Example of 16-Point Linearization                                    |         |

| Figure 12. Linearization Transfer Function Parameters                           |         |

| Figure 13. Analog Interface Input/Output Pins                                   |         |

| Figure 14. Analog Output Transfer Function                                      |         |

| Figure 15. PWM Interfaces (Standard and Differential Mode) Input/Output Pins    |         |

| Figure 16. 12-bit PWM Signal in Normal Operation Mode                           |         |

| Figure 17. 14-bit PWM Signal in Normal Operation Mode                           |         |

| Figure 18. 12-bit PWM Signal in Diagnostics Low Mode                            |         |

| Figure 19. 12-bit PWM Signal in Diagnostics High Mode                           |         |

| Figure 20. 14-bit PWM Signal in Diagnostics Low Mode                            |         |

| Figure 21. 14-bit PWM Signal in Diagnostics High Mode                           |         |

| Figure 22. SENT interface Input/Output Pins                                     |         |

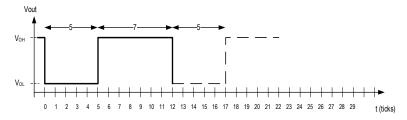

| Figure 23. SENT Nibble Output for Value = 0 <sub>DEC</sub>                      | 25      |

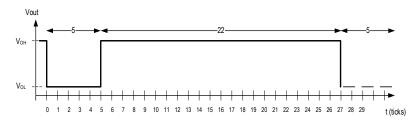

| Figure 24. SENT Nibble Output for Value = 15 <sub>DEC</sub>                     |         |

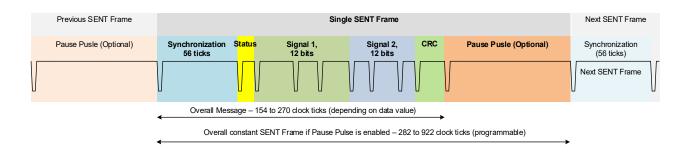

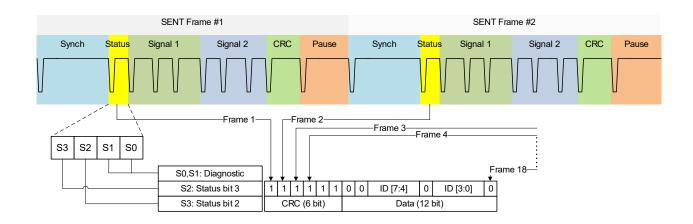

| Figure 25. SENT Typical Frame                                                   | 26      |

| Figure 26. Enhanced Serial Protocol Message Format                              |         |

| Figure 27. Legacy SENT Interface Load Circuit                                   |         |

| Figure 28. Recommended SENT Interface Load Circuit                              |         |

| Figure 29. I2C Interface Input/Output Pins                                      | 30      |

| Figure 30. I2C Interface with Address Select                                    | 31      |

| Figure 31. I2C Register Write Access                                            | 31      |

| Figure 32. I2C Register Read Access                                             | 32      |

| Figure 33. UART Single Wire NVM Programming                                     | 32      |

| Figure 34. Flag Output Configurations                                           | 34      |

| Figure 35. Parasitic Currents on Analog Outputs with Broken VDD or Broken GND I | _ines37 |

| Tables                                                                          |         |

| Table 1. Pin Description, RAA2P4500                                             | 5       |

| Table 2. Absolute Maximum Ratings                                               |         |

| Table 3. ESD Ratings                                                            |         |

| Table 4. Electrical Characteristics, 5V and 3.3V modes                          |         |

| . and and and and and and and                                                   |         |

### RAA2P4500 Datasheet

| Table 5. Position Resolution and Update Rate                             | 8  |

|--------------------------------------------------------------------------|----|

| Table 6. Non-volatile Memory Parameters [1]                              | 8  |

| Table 7. LC Oscillator Specifications                                    | 9  |

| Table 8. Receiver Coils Front-End Specifications                         | 9  |

| Table 9. I2C Specifications                                              | 10 |

| Table 10. Analog Output                                                  | 11 |

| Table 11. PWM Interface Parameters                                       | 11 |

| Table 12. SENT Interface                                                 | 12 |

| Table 13. Linearization Parameters                                       | 19 |

| Table 14. Linearization Parameter Settings                               | 20 |

| Table 15. Interfaces Overview                                            | 20 |

| Table 16. Analog Interface User Programming Options                      | 21 |

| Table 17. PWM Interface User Programming Options                         | 22 |

| Table 18. SENT Interface User Programming Options                        | 25 |

| Table 19. SENT Tick Counts                                               | 26 |

| Table 20. SENT Tick Time Programming Options                             | 26 |

| Table 21. SENT Fast Channel Frame Options                                | 27 |

| Table 22. SENT 12-bit Enhanced Serial Protocol Data (Data Frames 1 - 16) | 28 |

| Table 23. SENT 12-bit Enhanced Serial Protocol Data (Data Frames 17-32)  | 29 |

| Table 24. I2C Interface User Programming Options                         | 30 |

| Table 25. I2C Address Selection Options in NVM                           | 31 |

| Table 26. Auxiliary Inputs and Digital Output Options                    | 33 |

| Table 27. AIN Analog Input Parameters                                    | 33 |

| Table 28. Diagnostic Parameters                                          | 34 |

| Table 29. Safety Mechanisms                                              | 34 |

| Table 30. Diagnostic Levels with Pull-Up Resistors                       | 36 |

| Table 31. Diagnostic Levels with Pull-Down Resistors                     | 36 |

| Table 32. Global Programming Options                                     | 38 |

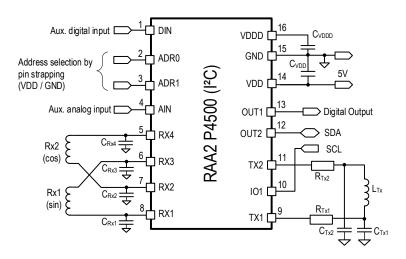

# 1. Pin Assignments and Descriptions

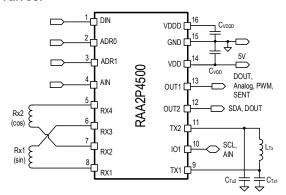

Figure 2. RAA2P4500

Table 1. Pin Description, RAA2P4500

| Pin Number | Name       | Туре                         | Description                                                                                                                                                                                                           |

|------------|------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | DIN        |                              | Auxiliary digital input for static or pulse signals, readable over I2C interface                                                                                                                                      |

| 2 ADR0     |            | Digital Input                | Address selection bit0 input for I2C interface (bit-strapping)                                                                                                                                                        |

| 3          | ADR1       | 1                            | Address selection bit1 input for I2C interface (bit-strapping)                                                                                                                                                        |

| 4          | AIN        | Analog Input                 | Auxiliary analog (12-bit) input for external analog signal, readable over I2C interface                                                                                                                               |

| 5          | RX4        |                              | Receiver coil (COS_N)                                                                                                                                                                                                 |

| 6          | RX3        | 0                            | Receiver coil (SIN_N)                                                                                                                                                                                                 |

| 7          | RX2        | Sensor Input                 | Receiver coil (COS)                                                                                                                                                                                                   |

| 8          | RX1        |                              | Receiver coil (SIN)                                                                                                                                                                                                   |

| 9          | TX1        | Transmitter<br>Output        | Connect the transmitter coil between the TX1 and TX2 pins, using series resistors $R_{Tx1}$ and $R_{Tx2}$ . The resonant frequency is adjusted with capacitors $C_{Tx1}$ and $C_{Tx2}$ from each coil terminal to GND |

|            | IO1 Digita |                              | Analog: Not used                                                                                                                                                                                                      |

| 10         |            | IO1 Digital I/O              | PWM: Not used / PWM inverted                                                                                                                                                                                          |

| 10         |            |                              | SENT: Analog In                                                                                                                                                                                                       |

|            |            |                              | I2C: SCL                                                                                                                                                                                                              |

| 11         | TX2        | Transmitter<br>Output        | Connect the transmitter coil between the TX1 and TX2 pins, using series resistors $R_{Tx1}$ and $R_{Tx2}$ . The resonant frequency is adjusted with capacitors $C_{Tx1}$ and $C_{Tx2}$ from each coil terminal to GND |

| 12         | OUT2       | Digital I/O                  | Analog: Digital output PWM: Digital output / PWM output (differential PWM) SENT: Digital output I2C: SDA                                                                                                              |

| 13         | OUT1       | Analog output<br>Digital I/O | Analog: 12-bit analog ramp output AOUT PWM:12-bit /14-bit PWM output SENT: SENT output I2C: Digital output Single wire programming interface                                                                          |

| 14         | VDD        | Supply                       | External supply voltage (3.3V or 5V)                                                                                                                                                                                  |

| 15         | GND        | Supply                       | Common ground connection                                                                                                                                                                                              |

| 16         | VDDD       | Supply                       | Internally regulated digital supply voltage                                                                                                                                                                           |

## 2. Specification

## 2.1 Absolute Maximum Ratings

The absolute maximum ratings listed in Table 2 are stress ratings only. Exceeding these limits can cause permanent damage to the device. The functional operation of the RAA2P4500 at these maximum ratings is not guaranteed. Exposure to the absolute maximum rating conditions could impact device's reliability. All voltage levels are referenced to GND.

**Table 2. Absolute Maximum Ratings**

| Symbol               | Parameter                                                | Conditions                                                                                   | Minimum | Maximum | Units |

|----------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------|---------|---------|-------|

| $V_{VDDmax}$         | External supply voltage: VDD                             |                                                                                              |         |         |       |

| V <sub>IO1</sub>     | Digital input pin voltage                                |                                                                                              |         |         |       |

| V <sub>OUT2</sub>    | Digital I/O pin voltage                                  | Continuous                                                                                   | -18     | 18      | V     |

| V <sub>OUT1</sub>    | Analog/Digital output pin voltage                        |                                                                                              |         |         |       |

| $V_{RX1}$            | Sensor receiver coil input pin Voltage (RX1)             |                                                                                              |         |         |       |

| $V_{RX2}$            | Sensor receiver coil input pin<br>Voltage (RX2)          |                                                                                              |         |         |       |

| V <sub>RX3</sub>     | Sensor receiver coil input pin<br>Voltage (RX3)          |                                                                                              |         |         |       |

| $V_{RX4}$            | Sensor receiver coil input pin<br>Voltage (RX4)          | Continuous                                                                                   | -12     | 12      | V     |

| $V_{DIN}$            | Digital input pin voltage                                |                                                                                              |         |         |       |

| $V_{ADR0}$           | Digital input pin voltage                                |                                                                                              |         |         |       |

| V <sub>ADR1</sub>    | Digital input pin voltage                                |                                                                                              |         |         |       |

| V <sub>AIN</sub>     | Analog input pin voltage                                 |                                                                                              |         |         |       |

| $V_{Tx1}$            | Transmitter output pin (TX1) voltage                     | Continuous                                                                                   | -0.3    | 5.5     | V     |

| V <sub>Tx2</sub>     | Transmitter output pin (TX2) voltage                     | Continuous                                                                                   | -0.3    | 5.5     | V     |

| $V_{\text{VDDDmax}}$ | Internal digital supply voltage,<br>VDDD                 | VDDD is internally regulated with an external capacitor to GND                               | -0.3    | 2.0     | V     |

| $T_{AMB}$            | Ambient temperature                                      |                                                                                              | -40     | 160     | °C    |

| TJ                   | Junction temperature                                     |                                                                                              | -40     | 170     | °C    |

| T <sub>STOR</sub>    | Storage temperature                                      | Unmounted units must be limited to 10 hours at temperatures above 125°C to prevent pre-aging | -55     | 160     | °C    |

| $R_{THJA}$           | Thermal resistance junction to ambient: 16-TSSOP package | Velocity = 0m/s with 2s2p PCB test<br>board<br>(JEDEC 51-2, JEDEC 51-7)                      |         | 89.5    | K/W   |

| R <sub>THJC</sub>    | Thermal resistance junction to case: 16-TSSOP package    | Junction to top of package                                                                   |         | 38.38   | K/W   |

## 2.2 ESD Ratings

**Table 3. ESD Ratings**

| Symbol                | Parameter                                                                                                                    | Conditions                                   | Maximum | Units |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|-------|

| V <sub>ESD_</sub> OUT | ESD tolerance for pins with potential external cable connection:  OUT1 VDD, VSS Human Body Model: 100pF/1.5kΩ                | According to AEC-Q100-002 classification 3A  | ±4      | kV    |

| V <sub>ESD</sub>      | ESD tolerance for all other pins not listed under $V_{\text{ESD\_OUT}}$ Human Body Model: $100 \text{pF}/1.5 \text{k}\Omega$ | According to AEC-Q100-002 classification 2   | ±2      | kV    |

| V <sub>CDM</sub>      | ESD tolerance for all pins: Charged-<br>Device Model (CDM)                                                                   | According to AEC-Q100-011 classification C2B | ±750    | V     |

## 2.3 Operating Conditions

All minimum/maximum specification limits are guaranteed by design, production testing, and/or statistical characterization. Conditions:  $T_{AMB} = -40$ °C to 160°C unless otherwise specified.  $C_{VDD} = 470$ nF,  $C_{VDDD} = 100$ nF.

Typical values are based on characterization results at default measurement conditions and are informative only.

Table 4. Electrical Characteristics, 5V and 3.3V modes

| Symbol                    | Parameter                               | Description                                                                           | Minimum | Typical | Maximum | Units |

|---------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|---------|---------|---------|-------|

| $V_{VDD5}$                | Supply voltage, 5V mode                 |                                                                                       | 4.5     | 5.0     | 5.5     | V     |

| V5 <sub>UV</sub>          | Undervoltage detection level, 5V mode   | An undervoltage alarm is created if VDD falls below this limit                        | 3.95    | 4.1     | 4.45    | V     |

| V5 <sub>OV</sub>          | Overvoltage detection level, 5V mode    | An overvoltage alarm is created if VDD rises above this limit                         | 5.55    | 6.15    | 6.5     | V     |

| V <sub>VDD3</sub>         | Supply voltage, 3.3V mode               |                                                                                       | 3.0     | 3.3     | 3.6     | V     |

| V3 <sub>UV</sub>          | Undervoltage detection level, 3.3V mode | An undervoltage alarm is created if VDD falls below this limit                        | 2.7     | 2.8     | 2.98    | V     |

| V3 <sub>OV</sub>          | Overvoltage detection level, 3.3V mode  | An overvoltage alarm is created if VDD rises above this limit                         | 3.65    | 3.85    | 4.04    | V     |

| $V_{VDD\_TH\_H}$          | Power-on reset (POR),<br>high threshold | Power-on reset (POR): the device is activated when VDD increases above this threshold |         | 2.61    | 2.7     | ٧     |

| V <sub>VDD_TH_</sub> L    | Power-on reset (POR),<br>low threshold  | The device is deactivated when VDD decreases below this threshold                     | 2.3     | 2.38    |         | ٧     |

| V <sub>VDD POR_HYST</sub> | Power-on reset hysteresis               |                                                                                       | 200     | 250     | 300     | mV    |

| t <sub>stup PE</sub>      | Start up times                          | Power-on reset (POR) to valid output signal, programming enabled                      |         |         | 5       | ms    |

| t <sub>stup PL</sub>      | Start-up times                          | Power-on reset (POR) to valid output signal, programming locked                       |         |         | 3       | ms    |

| t <sub>stup cmd</sub>     | Command timeout time                    | Time to wait before sending first command                                             | 1.5     |         |         | ms    |

| Symbol                  | Parameter                                                   | Description                                                                                                   | Minimum | Typical | Maximum | Units |

|-------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| t <sub>ProgEn</sub>     | Programming window enable time                              | Timeout window after POR, in which a first programming enable command must be sent                            |         |         | 5       | ms    |

| t <sub>ProgUL</sub>     | Programming window unlock time                              | Timeout window after programming enable in which a second unlock command must be completely sent <sup>i</sup> |         |         | 75      | ms    |

| $V_{VDDD}$              | Digital supply voltage                                      | Internally regulated. Connect capacitor C <sub>VDDD</sub> = 100nF from VDDD to GND.                           | 1.75    | 1.8     | 1.85    | V     |

| I <sub>AUXIN</sub>      | Auxiliary Input on<br>VDDD maximum<br>external load current | VDDD must be connected to a capacitor C <sub>VDDD</sub> .                                                     | 0       |         | 4       | mA    |

| I <sub>SHORT VDDD</sub> | VDDD short circuit current limitation                       |                                                                                                               | 18.5    | 27      | 40      | mA    |

| Icc                     | Current consumption                                         | Without coils, no load                                                                                        | 10      | 15      | 20      | mA    |

| $C_{VDDD}$              | Capacitor from VDDD pin to GND                              |                                                                                                               | 100     |         |         | nF    |

| C <sub>VDD</sub>        | Capacitor from VDD pin to GND                               | Nominal value                                                                                                 | 100     | 470     |         | nF    |

### Table 5. Position Resolution and Update Rate

| Symbol              | Parameter                                        | Description                                   | Minimum | Typical | Maximum | Units |

|---------------------|--------------------------------------------------|-----------------------------------------------|---------|---------|---------|-------|

| RES <sub>I2C</sub>  | Position resolution I2C interface                |                                               |         | 14      |         | bit   |

| RES <sub>AOUT</sub> | Position resolution Analog<br>Output interface   |                                               |         | 12      |         | bit   |

| RES <sub>Pwm</sub>  | Position resolution PWM interface                |                                               | 12      |         | 14      | bit   |

| RES <sub>SENT</sub> | Position resolution SENT interface               |                                               | 12      |         | 14      | bit   |

| Acc <sub>sent</sub> | Position accuracy SENT,<br>PWM and I2C interface | Ambient temperature, nominal supply           | -0.1    |         | 0.1     | %FS   |

| PWM I2C             |                                                  | Over temperature and supply range             | -0.2    |         | 0.2     | %FS   |

| A = 0               | Position accuracy Analog<br>Output interface     | Ambient temperature, nominal supply           | -0.5    |         | 0.5     | %FS   |

| Acc <sub>AOUT</sub> |                                                  | Over temperature and supply range             | -0.7    |         | 0.7     | %FS   |

| t <sub>POS</sub>    | Position refresh rate                            | Internal refresh rate of position information | 2       |         | 3       | μs    |

### Table 6. Non-volatile Memory Parameters [1]

| Parameter         | Conditions                              | Minimum                    | Typical                        | Maximum | Units |

|-------------------|-----------------------------------------|----------------------------|--------------------------------|---------|-------|

| Data              | Qualified according to<br>JEDEC 22-A117 | 15 @T <sub>J</sub> = 100°C |                                |         | Years |

| retention         | Over product lifetime                   |                            | >100<br>@T <sub>J</sub> = 25°C |         | Tours |

| Write temperature |                                         | -40                        |                                | 135     | °C    |

| Parameter           | Conditions                                                  | Minimum             | Typical             | Maximum | Units            |

|---------------------|-------------------------------------------------------------|---------------------|---------------------|---------|------------------|

| Read<br>temperature | Allowed ambient temperature range for read and write access | -40                 |                     | 160     | °C               |

| Endurance [2]       | Over product lifetime                                       |                     |                     | 1000    | NVM Write Cycles |

| Read Cycles         | Over product lifetime                                       | 5x 10 <sup>11</sup> | 1x 10 <sup>12</sup> |         | NVM Read events  |

<sup>[1]</sup> Guaranteed by memory supplier

**Table 7. LC Oscillator Specifications**

| Symbol                              | Parameter                                                 | Description                                                           | Minimum | Typical | Maximum              | Units |

|-------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|---------|---------|----------------------|-------|

| f <sub>LC</sub>                     | Excitation frequency                                      | LC oscillator frequency is determined by external components L and C. | 2       |         | 5.5                  | MHz   |

| R <sub>Peq</sub>                    | Equivalent parallel resistance of the LC resonant circuit |                                                                       | 250     |         |                      | Ω     |

| W                                   | LC oscillator amplitude at VDD = 5.0V ±10%                | Peak-to-peak voltage; pins TX1                                        |         |         | 8.8                  | Van   |

| V <sub>TX_PP</sub>                  | LC oscillator amplitude at VDD = 3.3V ±10%                | vs. TX2; all modes. Adjustable by coil current.                       |         |         | 2* V <sub>VDD3</sub> | Vpp   |

| I <sub>LC</sub>                     | Programmable transmitter coil drive current               | T <sub>ambient</sub> = -40 to +160°C                                  | 0       | [1]     | 16                   | mA    |

| R <sub>Tx1</sub> , R <sub>Tx2</sub> | LC oscillator series resistors                            | Depending on coil design and excitation frequency $(f_{LC})$          |         | 10      |                      | Ω     |

<sup>[1]</sup> The required transmitter coil current is determined by the equivalent parallel resistance of the LC circuit, depending on coil design.

**Table 8. Receiver Coils Front-End Specifications**

| Symbol                               | Parameter                             | Description                                                                                    | Minimum | Typical | Maximum | Units     |

|--------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------|---------|---------|---------|-----------|

| $V_{RX}$                             | RX coil amplitude                     | Differential coil input                                                                        | 5       |         | 200     | $mV_{pp}$ |

| A <sub>IN_mm</sub>                   | Maximum amplitude mismatch correction | Programmable gain mismatch correction of RX coil signals (SIN and COS)                         |         | 15      | %       |           |

| Ain_offs_range%                      | Input offset correction range         | Differential input offsets of sine or cosine signal, percentage of transmitter coil amplitude. |         |         | 0.2     | %         |

| Doffset                              | Coil input offset temperature drift   | Over temperature range T <sub>AMB</sub>                                                        | -2.5    |         | 2.5     | %         |

| C <sub>RX1</sub> to C <sub>RX8</sub> | Receiver input filter capacitors      | For improved EMC immunity                                                                      |         | 220     |         | pF        |

| Noise <sub>SP</sub>                  | Signal path noise level               | Digital filtering = OFF<br>V <sub>RX</sub> = 50mV                                              |         |         | 0.1     | ° el. rms |

| INUISESP                             | Olgridi patil Holse level             | Digital filtering = OFF $V_{RX}$ = 5mV                                                         |         |         | 0.5     | ° el. rms |

<sup>[2]</sup> Verified number of program/erase cycles. Qualified with 2000 cycles.

## 2.4 Interface Pin Characteristics

Table 9. I2C Specifications

| Symbol                       | Parameter                                          | Description                                         | Minimum     | Typical | Maximum | Units  |

|------------------------------|----------------------------------------------------|-----------------------------------------------------|-------------|---------|---------|--------|

| f <sub>I2C</sub>             | I2C clock rate                                     |                                                     |             |         | 400     | Kbit/s |

| t <sub>SCL_LOW</sub>         | Low level state of SCL                             | Normal mode                                         | 4.7         |         |         | μs     |

|                              | clock                                              | Fast mode                                           | 1.3         |         |         | μs     |

| t <sub>scl_HIGH</sub>        | High level state of SCL                            | Normal mode                                         | 4.0         |         |         | μs     |

|                              | clock                                              | Fast mode                                           | 0.6         |         |         | μs     |

|                              |                                                    |                                                     |             |         |         |        |

| t <sub>R_SDA_SCL</sub>       | Rise time of SDA/SCL                               | Normal mode                                         |             |         | 1000    | ns     |

|                              | (30%  to  70%)<br>R <sub>SDA/SCL</sub> = 2kΩ       | Fast mode                                           | 20          |         | 300     | ns     |

| t <sub>F_SDA_SCL</sub>       | Fall time of SDA/SCL                               | Normal mode                                         | 20          |         | 300     | ns     |

| F_SDA_SCL                    | (70% to 30%)                                       | Fast mode                                           | 20          |         | 000     | ns     |

|                              | $R_{SDA/SCL} = 2k\Omega$                           | 1 dot mode                                          | 20          |         |         | 110    |

| $V_{IH\_I2C}$                | High level input voltage                           | SCL clock input,                                    | 0.7×VDD     |         | VDD+0.5 | V      |

| V <sub>IL_I2C</sub>          | Low level input voltage                            | SDA data input<br>DIN, ADR0, ADR1                   | -0.5        |         | 0.3×VDD | V      |

| V <sub>I2C_hyst</sub>        | Hysteresis of Schmitt                              | SCL clock input                                     | 0.05 × VDD  |         |         | V      |

| ▼ I2C_nyst                   | trigger input                                      | SDA, DIN, ADR0,                                     | 0.00 ** VDD |         |         | v      |

|                              |                                                    | ADR1                                                |             |         |         |        |

| I <sub>LEAK</sub>            | Input leakage current                              | VDD = 0V to 5.5V                                    | -10         |         | 10      | μΑ     |

| I <sub>SDA lim thr</sub>     | SDA current limitation threshold                   | OUT2 pin 12 (SDA)                                   | 8           |         | 30      | mA     |

| I <sub>SDA sc lim</sub>      | SDA output short current limitation <sup>[1]</sup> | Short to VDD, GND<br>VDD = 3.3V, 5V                 | 14          |         | 26      | mA     |

| V <sub>OL_SDA</sub>          | Output low voltage                                 | 3mA sink current                                    | 0           |         | 0.4     | V      |

| _                            | SDA low level output                               | VDD = 3.0 to 5.5V                                   |             |         |         |        |

|                              | voltage open drain                                 |                                                     |             |         |         |        |

| $I_{OL}$                     | Low level output current                           | $V_{OL} = 0.4V$ ,                                   | 3           |         |         | mA     |

|                              |                                                    | VDD = $5.5V$ ,<br>R <sub>SDA/SCL</sub> = $2k\Omega$ |             |         |         |        |

| t <sub>SP</sub>              | Input spike suppression                            | Spikes shorter than                                 | 400         |         | 426     | ns     |

| <b>L</b> SP                  | iliput spike suppression                           | t <sub>SP</sub> are suppressed                      | 400         |         | 420     | 115    |

| Св                           | External capacitive load                           |                                                     | 1           |         | 400     | pF     |

| _                            | for each bus line                                  |                                                     |             |         |         | ·      |

| R <sub>SDA</sub> ,           | External pull-up resistor at                       | Resistor value and                                  | 1.8         | 3.3     |         | kΩ     |

| $R_{SCL}$                    | pins SDA and SCL                                   | capacitive load on                                  |             |         |         |        |

|                              |                                                    | these pins are                                      |             |         |         |        |

|                              |                                                    | limiting the maximum clock                          |             |         |         |        |

|                              |                                                    | frequency                                           |             |         |         |        |

| R <sub>ADR</sub>             | External resistor at pin                           | Pull-up/pull-down,                                  | 1.8         | 4.7     |         | kΩ     |

|                              | ADR for I2C address                                | depending on I2C                                    |             |         |         |        |

|                              | selection                                          | address setting.                                    |             |         |         |        |

| Inaume                       | DOUT current limitation                            | OUT1 pin 13 in                                      | 35          |         |         | mA     |

| DOUT lim thr I2C             | threshold <sup>[2]</sup>                           | overload condition                                  | ან          |         |         | IIIA   |

| I <sub>DOUT sc lim I2C</sub> | DOUT output short current                          | OUT1 pin 13                                         | 28          |         | 58      | mA     |

| DOG 1 30 III 11 120          | limitation <sup>[2]</sup>                          | - 1                                                 |             |         |         |        |

<sup>[1]</sup> With OUT2 drive strength set to "00" (out2\_io1\_drv = "00")

<sup>[2]</sup> With digital mode configuration (out1\_drv="10")

**Table 10. Analog Output**

| Symbol                        | Parameter                                | Description Minim                                     |     | Typical | Maximum | Units |

|-------------------------------|------------------------------------------|-------------------------------------------------------|-----|---------|---------|-------|

| A <sub>OUT</sub>              | AOUT voltage range                       |                                                       | 5   |         | 95      | %VDD  |

| AOUT lim thr                  | AOUT current limitation threshold [1]    | OUT1 pin 13 in overload condition                     | 19  |         |         | mA    |

| I <sub>AOUT sc lim</sub>      | AOUT output short current limitation     | OUT1 pin 13<br>Short to VDD / GND<br>VDD = 3.3V or 5V | 23  |         | 38      | mA    |

| IDOUT lim thr AOUT            | DOUT current limitation threshold        | OUT2 pin 12 in overload condition                     | 8   |         |         | mA    |

| I <sub>DOUT sc lim</sub> AOUT | DOUT output short current limitation [2] | OUT2 pin 12<br>Short to VDD / GND<br>VDD = 3.3V or 5V | 14  |         | 26      | mA    |

| C <sub>L,AOUT</sub>           | Output buffer Load capacitance           | Capacitor from AOUT to GND                            |     | 47      | 100     | nF    |

| SR_AOUT                       | Output Buffer Slew Rate                  | At maximum load conditions                            | 0.1 |         |         | V/µs  |

<sup>[1]</sup> With Analog Out configuration (out1\_drv="01")

**Table 11. PWM Interface Parameters**

| Symbol                            | Parameter                                             | Description                                                              | Minimum                                       | Typical | Maximum | Units |

|-----------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|---------|---------|-------|

| I <sub>OUT1 lim thr PWM</sub>     | PWM Out limitation threshold [1]                      | Pin 13 (OUT1) PWM SE<br>In overload condition                            | 35                                            |         |         | mA    |

| OUT1 sc lim PWM                   | PWM output short current limitation [1]               | Pin 13 (OUT1) PWM SE<br>Short to VDD / GND<br>VDD = 3.3V,5V              | 28                                            |         | 58      | mA    |

| I <sub>OUT2</sub> IO1 lim_thr PWM | OUT2 and IO1 current limitation threshold             | Pin 12 (OUT2)<br>Pin 10 (IO1) in overload<br>condition                   | 6                                             |         |         | mA    |

| I <sub>OUT2</sub> IO1 sc lim PWM  | Output short current limitation <sup>[2]</sup>        | Pin 12 (OUT2) Pin 10 (IO1) Short to VDD / GND VDD = 3.3V,5V              | Pin 12 (OUT2) Pin 10 (IO1) Short to VDD / GND |         | 70      | mA    |

|                                   | Output high voltage                                   | VDD= 3.3V                                                                | 2.64                                          |         |         | V     |

| V <sub>OH_OUT2_PWM</sub>          | Push-pull mode<br>Pin 12 (OUT2)                       | VDD= 5V                                                                  | 4                                             |         |         | ٧     |

| V <sub>OL_OUT2_PWM</sub>          | Output low voltage<br>Push-pull mode<br>Pin 12 (OUT2) | VDD= 3.3V, 5V                                                            |                                               |         | 0.4     | V     |

| DC <sub>PWM</sub>                 | PWM duty cycle                                        | Normal operation                                                         | 5.56                                          |         | 94.44   | %     |

| DC <sub>PWM_DHI</sub>             | PWM duty cycle                                        | Diagnostic low mode                                                      |                                               | 2.78    |         | %     |

| DC <sub>PWM_DLO</sub>             | PWM duty cycle                                        | Diagnostic high mode                                                     |                                               | 97.24   |         | %     |

| ft <sub>PWM</sub>                 | PWM frequency tolerance                               |                                                                          | -5                                            |         | 5       | %     |

| t <sub>PWM_r</sub>                | PWM output rising edge, push-pull mode.               | Load capacitance 4.7nF Output voltage rising from 10% to 90% @ 5V        |                                               |         | 5       | us    |

| t <sub>PWM_f</sub>                | PWM output falling edge, push-pull mode               | Load capacitance 4.7nF<br>Output voltage falling from 90%<br>to 10% @ 5V |                                               |         | 5       | us    |

| R <sub>PULL-UP</sub>              | Output Pull-up<br>Resistance                          |                                                                          | 1                                             | 2       | 10      | kΩ    |

<sup>[1]</sup> With digital mode configuration (out1\_drv="10")

<sup>[2]</sup> With OUT2 slow configuration (out2\_io1\_drv="00")

<sup>[2]</sup> With OUT2 fast configuration (out2\_io1\_drv="11")

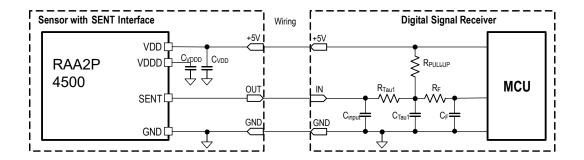

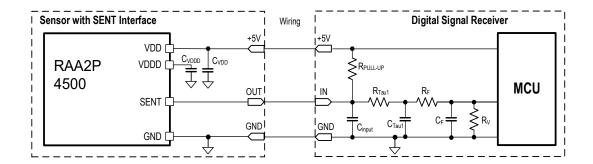

**Table 12. SENT Interface**

| Symbol                                | Parameter                                                                                               | Description                                                             | Minimum | Typical | Maximum | Units |

|---------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------|---------|---------|-------|

| $V_{\text{OL\_SENT}^{[3]}}$           | Output low voltage                                                                                      | 3mA sink current, VDD = 4.5 to 5.5V                                     | 0       |         | 0.5     | V     |

| V <sub>OH_SENT</sub> <sup>[3]</sup>   | Output high voltage                                                                                     | OUT1 pin 13  3mA source current, VDD = 4.5 to 5.5V  OUT1 pin 13         | 4.1     |         | 5.5     | V     |

| I <sub>OUT1 lim thr</sub>             | OUT1 current limitation threshold <sup>[1]</sup>                                                        | OUT1 pin 13  OUT1 pin 13 in overload condition                          | 55      |         |         | mA    |

| I <sub>OUT1 sc lim</sub>              | OUT1 output short current limitation <sup>[1]</sup>                                                     | OUT1 pin 13<br>Short to VDD, GND<br>VDD = 4.5 to 5.5V<br>Push-pull mode | 40      |         | 91      | mA    |

| t <sub>OVL</sub>                      | Overload shutdown debounce time                                                                         | Duration of overload condition, before output is shut off               |         | 2       |         | ms    |

| I <sub>DOUT lim thr</sub>             | DOUT current limitation threshold <sup>[2]</sup>                                                        | OUT2 pin 12 in overload condition                                       | 8       |         |         | mA    |

| I <sub>DOUT lim thr</sub>             | DOUT output short current limitation [2]                                                                | OUT2 pin 12                                                             | 33      |         | 70      | mA    |

| $C_{input}$                           | Parasitic input capacitance from ESD protection                                                         |                                                                         |         |         | 0.1     | nF    |

| I <sub>SUP<sup>[3]</sup></sub>        | Average current consumption from Receiver 5V supply over one message                                    |                                                                         |         |         | 50      | mA    |

| I <sub>GND</sub> <sup>[3]</sup>       | Average current through Ground line over one message                                                    |                                                                         |         |         | 50      | mA    |

| I <sub>SUP RIPPLE<sup>[3]</sup></sub> | Peak-to-peak variation in supply<br>current consumption over one<br>message at frequencies up 30<br>kHz |                                                                         |         |         | 9       | mA    |

| T <sub>Fall</sub> <sup>[3]</sup>      | Falling time, tick time = 3 μs                                                                          | I <sub>SUP</sub> ≤ 20 mA                                                |         |         | 6.5     | μs    |

| I Fall <sup>[0]</sup>                 | From $V_{TH} = 3.8V$ to $V_{TL} = 1.1V$                                                                 | 20 mA ≤ I <sub>SUP</sub> < 50 mA                                        |         |         | 5       | μs    |

| $T_{Rise}^{[3]}$                      | Rising time, tick time = 3 $\mu$ s<br>From V <sub>TL</sub> = 1.1V to V <sub>TH</sub> = 3.8V             |                                                                         |         |         | 18      | μs    |

| $\Delta T_{Fall}^{[3]}$               | Edge to Edge Jitter with static environment for any pulse period tick time = 3 µs                       |                                                                         |         |         | 0.1     | μs    |

| $R_{Tau1}$                            | Input filter resistor (1st stage)                                                                       |                                                                         | 448     | 560     | 672     | Ω     |

| $C_{Tau1}$                            | Input filter capacitor (1st stage)                                                                      |                                                                         | 1.54    | 2.2     | 2.86    | nF    |

| Tau₁                                  | Input filter time 1st stage time constant defined by RTau1 and CTau1                                    |                                                                         | 0.74    |         | 1.73    | μs    |

| R <sub>PULL-UP</sub>                  | Input Pull-up resistor                                                                                  |                                                                         | 10      |         | 55      | kΩ    |

| $R_{F}$                               | Input filter resistor (2nd stage)                                                                       |                                                                         | 4       |         |         | kΩ    |

| C <sub>F</sub>                        | Input filter capacitor (2nd stage)                                                                      | Determined by TAU2 requirement                                          |         |         |         | nF    |

| $R_V$                                 | Voltage divider, adjusting SENT output level to MCU input level                                         | Optional, depends on MCU input level                                    |         |         |         | kΩ    |

| Tau <sub>2</sub>                      | Input filter time 2nd stage time constant defined by RV,RF and CF                                       |                                                                         | 0.6     |         | 1.4     | μs    |

<sup>[1]</sup> With SENT mode configuration (out1\_drv=""11")

<sup>[2]</sup> With out2\_io1\_drv = "11"

<sup>[3]</sup> Refer to SENT Standard SAE J2716 Standard (Rev. April 2016)

## 3. Detailed Description

#### 3.1 Overview

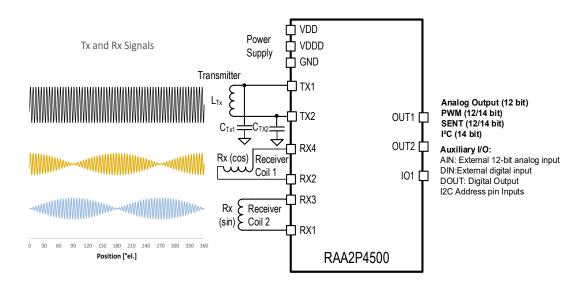

The RAA2P4500 sensor IC is designed to drive a single transmitter coil and receive signals from one pair of receiver coils, typically created as traces on a printed circuit board. The receiver coils consist of two wire loops connected in anti-serial fashion, with the "sine" and "cosine" coils shifted by 90 electrical degrees. A metal target is placed above this coil arrangement.

When the IC drives an AC current into the transmitter coil, it generates an alternating magnetic field. This magnetic field induces secondary voltages in the receiver coils. Without a target, the induced voltages in the loops of the receiver coils cancel each other out, resulting in a net receiver voltage of zero.

When a metal target is placed above the coils, the magnetic field generates eddy currents on its surface. These eddy currents create a counter magnetic field, reducing the total flux density underneath. This leads to a reduction in the voltage induced in the receiver coil areas underneath the target, creating an imbalance in the anti-serial coil segment voltages.

The IC demodulates, offsets and corrects the amplitude of the signals from the two receiver coils with a 90° electrical phase shift design, which generates sine and cosine shaped voltages as the target is moving.

The RAA2P4500 IC amplifies, rectifies, and filters the receiver voltages, converting them into digital representation with an ADC. The digital sine and cosine signals are converted into a 0°to 360° absolute position. The signal accuracy can be further enhanced through a 2-dimentional,16-point linearization process.

The absolute position can be read over Analog, PWM, SENT and I2C interfaces.

Figure 3. RAA2P4500 Input/Output Signals

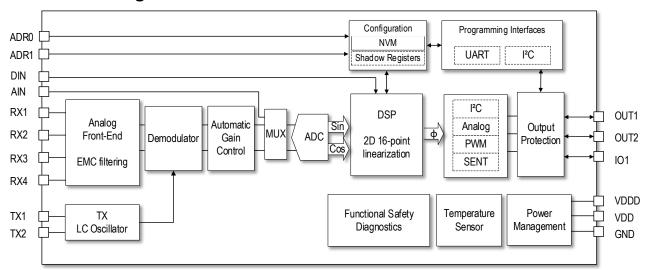

## 3.2 Block Diagram

Figure 4. Block Diagram

The main building blocks include:

- Analog front-end: Input EMC filter, offset, and gain control for the receiver signals.

- Demodulator: Converting RF modulated position signals to LF demodulated raw sine and cosine signals.

- Automatic Gain Control: Automatically adjusts the raw sine and cosine signal levels.

- High Speed ADC: Converts raw signals into digital format for further processing.

- Digital signal processing: Converts digital sine and cosine raw signals into synchronized absolute position information.

- 2D 16-point linearization: Supports up to 16 two-dimensional linearization points with freely programmable Xand Y- coordinates for each point (X= Position input, Y= Position output).

- Analog, PWM SENT, I2C: Carries out post processing, clamping, signal integrity checks, and decodes channel information and other diagnostics information into the selected output format.

- TX Oscillator: Generates the transmitter coil signal.

- Temperature sensor: Internal temperature sensor used for chip diagnostics.

- Protection: All outputs are fully protected against overvoltage, reverse polarity and short circuit, enabling direct cable connection to these outputs and eliminating the need for additional line driver ICs.

- Power Management: Operates with supply voltages ranging from 3.0V to 5.5V. External capacitors are required for the supply voltage VDD, and for the digital power supply, VDDD.

- Programming interface: Accessible via one-wire UART interface or I2C interface.

- Configuration, NVM: Stores non-volatile storage for factory and user-programmable settings. User configuration parameters can be programmed multiple times.

- On-chip failure diagnostics: Performs internal diagnosis of critical blocks.

- ADR: Selects the address input for the I2C interface, see Table 26.

- Auxiliary I/O including DIN (Digital input), AIN (12-bit analog input for external analog signals), DOUT (Diagnostic Output) accessible over I2C interface.

- Functional Safety Diagnostics: Internal diagnostics of critical blocks to ensure functional safety up to ASIL-C on chip level.

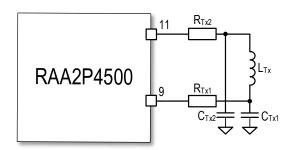

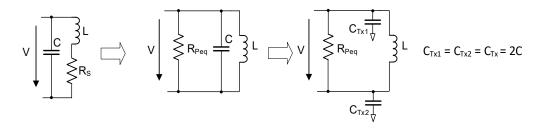

#### 3.3 LC Oscillator

The transmitter circuit of the RAA2P4500 generates the required RF magnetic field for operating the sensor as determined by an external parallel LC circuit, see Figure 5. To ensure low emission of harmonics, the capacitive part of the LC circuit is split into two equal-value capacitors:  $C_{Tx1}$  and  $C_{Tx2}$ . Additionally, two series resistors  $R_{Tx1}$  and  $R_{Tx2}$  are added as shown Figure 5.

Figure 5. TX LC Oscillator Connection

### 3.3.1 Parallel LC Resonator Calculations

A resonator, comprising an inductor (L) and a capacitor (C) in parallel, is essential for generating specific frequencies in RF applications. Accurate calculations of the equivalent parallel resistance (R-Peq) ensure proper resonator function. In the RAA2P4500 transmitter circuit, this resonator minimizes harmonic emissions.

Figure 6. Parallel Resonator Circuit

Equivalent parallel resistance from Coil series resistance:

$$R_{Peq} = \frac{1}{R_S} \times \frac{L}{C}$$

Equation 1

For

$$C_{Tx1} = C_{Tx2} = C_{Tx} = 2C$$

:

$$R_{Peq} = \frac{1}{R_S} \times \frac{2 \times L}{C_{Tr}}$$

**Equation 2**

Equivalent parallel resistance from Quality factor Q:

$$R_{Peq} = Q \times \sqrt{\frac{L}{C}} = Q \times \sqrt{\frac{2L}{C_{Tx}}}$$

Equation 3

Ideal LC Oscillator frequency with split Tx capacitors

$$C_{Tx}$$

$$f_{TX} = \frac{1}{2\pi \sqrt{L\frac{C_{TX}}{2}}}$$

**Equation 4**

Oscillator frequency with split Tx capacitor  $C_{\text{Tx}}$  and coil series resistor  $R_s$

$$f_{TX} = \frac{1}{2\pi} \sqrt{\frac{2}{LC_{Tx}} - \left(\frac{R_S}{L}\right)^2}$$

**Equation 5**

Oscillator frequency with split Tx capacitor  $C_{\text{Tx}}$  and equivalent parallel resistor  $R_{\text{Peq}}$

$$f_{TX} = \frac{1}{2\pi} \sqrt{\frac{2}{LC_{TX}} - \left(\frac{2}{R_{Peq}C_{TX}}\right)^2}$$

**Equation 6**

$$Q = R_{Peq} \sqrt{\frac{C}{L}} = \frac{1}{R_S} \sqrt{\frac{L}{C}}$$

**Equation 7**

Coil quality factor

$$Q = \omega \frac{L}{R_s} = 2\pi f_{TX} \frac{L}{R_s}$$

**Equation 8**

Where:

R<sub>Peq</sub> Equivalent parallel resistance of the LC circuit at the transmitter frequency in Ohms

Rs Serial resistance of the transmitter coil at the transmitter frequency in Ohms

$f_{Tx}$  Resonant circuit frequency in Hertz, 1/s

L Resonant circuit coil impedance in Henry

C Resonant circuit capacitance in Farad

C<sub>Tx1</sub>, C<sub>Tx2</sub> Capacitance of the split capacitors in Farad

Q Resonant circuit quality factor (unitless)  $\omega \qquad \qquad \text{Angular frequency } 2^*\pi^*f_{Tx} \text{ in Hertz, 1/s}$

## 3.4 Coil Design

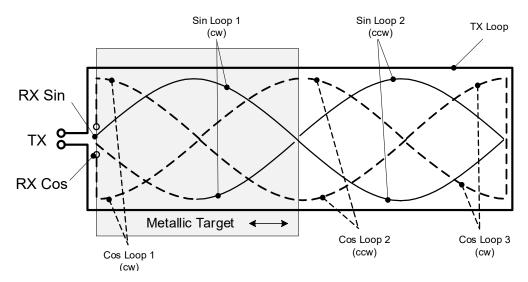

Figure 7 shows an example of a linear motion sensor with one transmitter coil (transmitter loop) and two receiver coils (Sin loop and Cos loop). Due to the alternating clockwise and counterclockwise winding direction of each segment in a loop (for example RxCos = clockwise Cos Loop1 + counterclockwise Cos Loop2), the induced voltages in each segment have alternating opposite polarity.

**Equation 9**

$V_{\text{Cos Loop1}} = -V_{\text{Cos Loop2}}$

In the absence of a target, the secondary voltages balance out as follows:

$$V_{Cos} = V_{Cos Loop1} - V_{Cos Loop2} = 0V$$

**Equation 10**

With a target placed above the coils, the secondary voltage induced in the covered area decreases compared to the secondary voltage when no target is present above it.

$V_{Cos\ Loop1} \neq -V_{Cos\ Loop2}$

**Equation 11**

This creates an imbalance of the secondary voltage segments, and thus, a secondary voltage ≠ 0V is generated, depending on the location of the target.

$V_{\text{Cos}} = V_{\text{Cos Loop1}} - V_{\text{Cos Loop2}} \neq 0V$

**Equation 12**

Figure 7. Coil Design for a Linear Motion Sensor

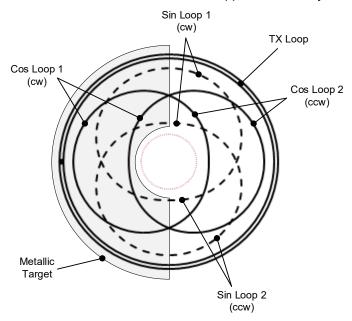

The same principles shown for the linear motion sensor can be applied to a rotary sensor as shown in Figure 8.

Figure 8. Coil Design for a 360° Rotary Sensor

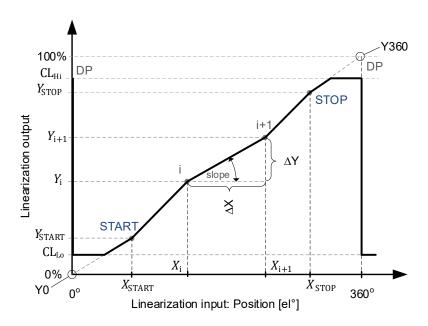

### 3.4.1 Multi-periodic Coil Design Application Examples

Applying the same fundamental design principles, coils with multiple periods per turn can be designed. Multiperiodic designs improve mechanical accuracy compared to single-periodic coil designs. For example, a 4periodic coil design (4 × 90°) improves mechanical accuracy by a factor of 4. Consequently, for angular designs, requiring < 360° movement range, coil designs with multiple periods are recommended.

#### 3.4.2 Electrical vs. Mechanical Degrees

RAA2P4500 converts the movement of a target across a single period of the receiver coil into a precise electrical signal. This conversion spans the full angular range from 0°to 360°, producing a digital output ranging from 0 to (2<sup>N</sup>-1) LSBs. The position output is thus absolute over a full turn of 360 mechanical degrees.

As illustrated in Figure 9, the single-periodic coil design establishes a direct 1:1 relationship between electrical and mechanical domains as the following:

Coil Period: 360° electrical

Mechanical Range: 360° mechanical

Conversion Factor: 1:1 (1°el. = 1° mechanical)

Figure 9. Coil Design Using Single-Periodic Coil

As illustrated in Figure 10, a coil design with four receiver coil periods within a single full mechanical turn, results in four electrical rotations for every complete mechanical turn and provides the following advantages in accuracy and resolution:

Higher Resolution: Position output resolution increases proportionally with period count by Mechanical Resolution = Sensors\_Periods \* Electrical Resolution

In this configuration one electrical degree (°el) equals 0.25 mechanical degrees (°). The provided output resolution is four times higher compared to the single-periodic design

Improved accuracy: Mechanical error is reduced by the period factor

$$Mechanical\ Error = \frac{Electrical\ Error}{Sensor\ Periods}$$

This configuration is particularly well-suited for:

- · Multi-pole motors requiring precise commutation

- Limited-range applications (<180° mechanical travel)</li>

- · Systems demanding high-resolution incremental feedback

Select the number of periods based on application requirements to optimize measurement performance. Proper period selection is critical for achieving maximum system accuracy.

Figure 10. Coil Design Using 4-Periodic Coil

### 4. Linearization

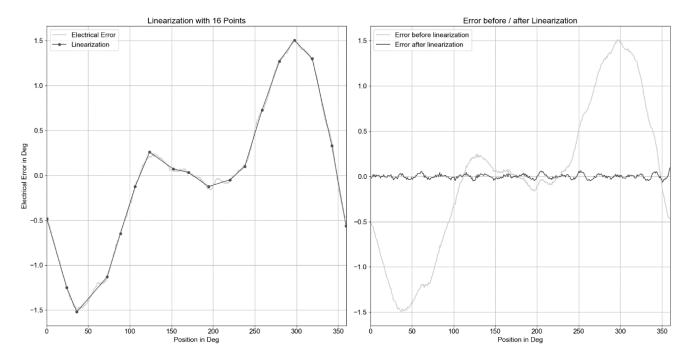

The RAA2P4500 offers a very flexible linearization feature to enhance sensor accuracy. The linearization algorithm is applied digitally after an angle calculation. The linearization is performed with 12-bits resolution over a 360° electrical range (el.). Up to 16 programmable linearization points can be positioned within a grid of 0.088° in both X (position) and Y (expected output) directions.

Figure 11 illustrates an example of the impact of linearization, showing that the total error is significantly reduced.

Figure 11. Example of 16-Point Linearization

**Table 13. Linearization Parameters**

| Symbol              | Parameter                                     | Conditions          | Minimum | Typical | Maximum | Units |

|---------------------|-----------------------------------------------|---------------------|---------|---------|---------|-------|

| $N_{P\_Lin}$        | Number of linearization points                |                     | 16      |         |         |       |

| Grid <sub>LIN</sub> | Placement grid of linearization points        | In X and Y          |         | 0.088   |         | °el   |

| Res <sub>Lin</sub>  | Resolution of linearization transfer function | X and Y coordinates |         | 12      |         | bits  |

Note: The slope of each segment ( $\Delta Y / \Delta X$ ) is automatically calculated from the X and Y parameters of adjacent linearization points. If two adjacent points are positioned with a slope outside the specified range (see Table 13), the slope is reset to 0 to prevent an overflow of the calculated slope value.

Figure 12. Linearization Transfer Function Parameters

**Table 14. Linearization Parameter Settings**

| Parameter          | Description                                                                        | Programming Options | Resolution           |  |

|--------------------|------------------------------------------------------------------------------------|---------------------|----------------------|--|

| P <sub>Lin</sub>   | Number of linearization options                                                    | 0,2,4,6,8,16        |                      |  |

| D <sub>P</sub>     | Discontinuity point, Zero position transition from 0°/360°                         |                     |                      |  |

| X <sub>Start</sub> | Mechanical start position, first linearization point                               |                     |                      |  |

| Y <sub>Start</sub> | Expected output at XStart, first linearization point                               |                     |                      |  |

| X <sub>i</sub>     | Mechanical position of linearization point (i = 1 to 16, including start and stop) | 0° to <360° el.     | 0.088°el. per LSB    |  |

| Yi                 | Expected output at linearization point (i = 1 to 16 including start and stop)      |                     |                      |  |

| X <sub>Stop</sub>  | Mechanical end position, last linearization point                                  |                     |                      |  |

| Y <sub>Stop</sub>  | Expected output at XStop, last linearization point                                 |                     |                      |  |

| CL <sub>Hi</sub>   | Output Clamping level, high                                                        | 0% to 100% VDD      | 12 bits              |  |

| CL <sub>Lo</sub>   | Output Clamping level, low                                                         | 0% (0 100% VDD      | (VDD / 4096) per LSB |  |

| Y0                 | Position at DP, start value at X = 0°                                              | 0° / 360° el.       |                      |  |

| Y360               | Position at DP, stop value at X = 360°                                             | 0° / 360° el.       |                      |  |

## 5. Interfaces

The RAA2P4500 offers an Analog Output, a PWM, a SENT and an I2C. A summary is shown in Table 15.

**Table 15. Interfaces Overview**

| Interfaces    | Number of I/f<br>Wires | Resolution  | Features                                                                       | Other options                                           |

|---------------|------------------------|-------------|--------------------------------------------------------------------------------|---------------------------------------------------------|

| Analog Output | 1                      | 12 bit      | Analog out Position update rate: 20 KHz                                        | Digital Output (pin 12)                                 |

| PWM           | 1/2                    | 12 / 14 bit | PWM output (push-pull or open drain) PWM frequency: 109 Hz to 4376 Hz          | Digital Output (pin 12)                                 |

| SENT          | 1                      | 12 / 14 bit | Programmable tick time: 0.02 to 6 µs<br>Fast Channel / Enhanced Serial Message | Auxiliary Analog input (pin 10) Digital Output (pin 12) |

| I2C           | 2                      | 14 bit      | Interface speed: 400KHz Fastest position update rate 5.4 KHz                   | Digital Output (pin 13)                                 |

### 5.1 Analog Interface

An analog interface is included to accommodate legacy applications that utilize potentiometers or position sensors with linear ramp output, such as magnetic position sensors.

Figure 13. Analog Interface Input/Output Pins

The analog output is generated by converting the digitally processed angle data into an analog voltage through a 12-bit DAC and an analog output buffer. This buffer is protected against overvoltage, reverse polarity, overcurrent, and short circuits to GND and positive supply voltage.

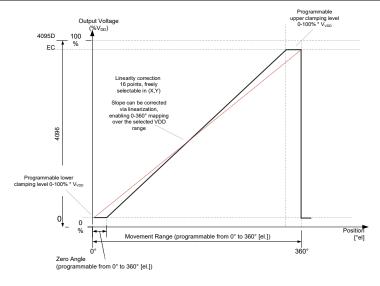

The full electrical 360° range is operational, with programmable clamping levels from 5%VDD to 95%VDD, see Figure 14 and Table 16). The analog position is indicated as a linear ramp between these clamping levels, and the output voltage is ratiometric to the supply voltage VDD, ensuring stability against supply voltage changes.

Adjusting the clamping level limits allows for full range mapping (0° to 360°) over a 5 to 95 VDD% voltage range. Diagnostic mode is indicated by a high-ohmic tri-state mode, detectable as an out-of-range voltage level with external pull-up or pull-down resistors. Broken ground or broken supply condition can also be detected this way.

A separate digital output pin (pin 12) indicates additional information, such as an out-of-range position or out-of-range magnitude or magnitude value (PWM).

Analog Interface Programming Parameter

Number of Options

Programming Option

Output high clamp level

4096

0% to 100% VDD in 12-bit steps

Output low clamp level

4096

0% to 100% VDD in 12-bit steps

**Table 16. Analog Interface User Programming Options**

Figure 14. Analog Output Transfer Function

#### 5.2 PWM Interface

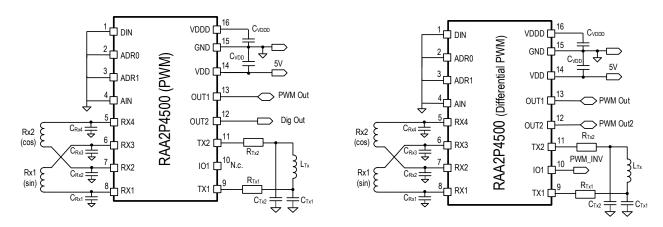

The PWM interface can be configured for single wire PWM interface with push-pull or open drain output, as well as a dual wire differential PWM interface with push-pull outputs. In differential mode, an inverted signal is provided on pin 10 as shown in Figure 15.

Figure 15. PWM Interfaces (Standard and Differential Mode) Input/Output Pins

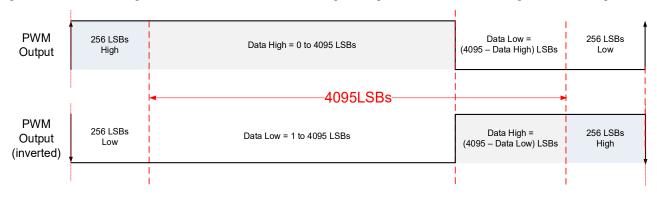

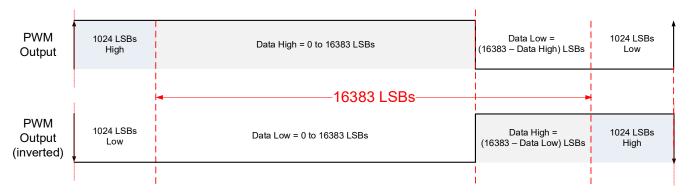

| PWM<br>Programming Parameter            | Number of Options | Programming Option                                                                                  |

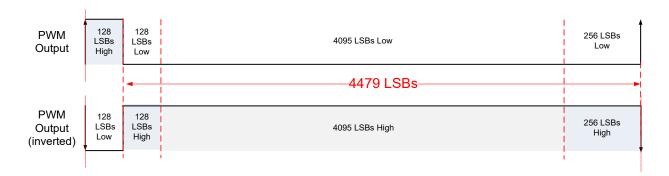

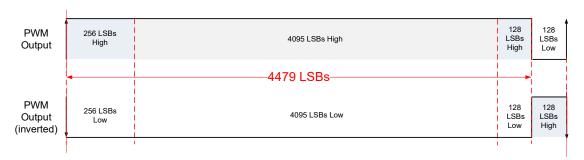

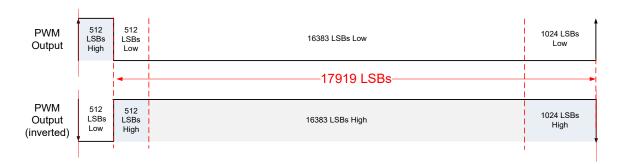

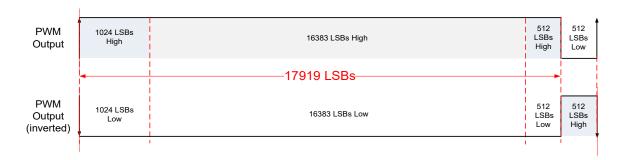

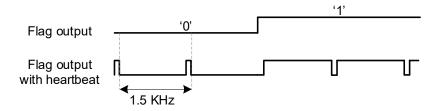

|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|