#### RAA489300

3-Level Buck Controller with Pass-Through Mode

### Description

The RAA489300 is a high-performance buck controller designed for a 3-level buck topology. This topology delivers exceptional efficiency and significantly reduces the required inductance for regulating the output voltage. Its innovative design minimizes power loss and reduces system size, making it ideal for compact, high-performance applications. In addition, the controller ensures a seamless switching mode transition across the entire output voltage range.

The advanced Renesas R3™ Technology enhances performance by enabling highly efficient light-load operation, fast transient response, and seamless transitions between discontinuous conduction mode (DCM) and continuous conduction mode (CCM).

The RAA489300 is an ideal choice for applications requiring versatile input sources, such as high-power barrel adapters and USB Power Delivery (USB PD) adapters. For USB PD applications, it complies with PD specifications and supports Programmable Power Supply (PPS) and Adjustable Voltage Supply (AVS) operation. Independent control loops for input and output voltages and currents ensure precision, safety, and flexibility.

The device features pass-through mode (PTM) in both forward and reverse directions, maximizing efficiency when the input and output voltages are identical. This makes it especially suitable for applications demanding high efficiency and low power loss.

Beyond its core functionality, the RAA489300 incorporates system-level features such as isolation MOSFET control and an adjustable output voltage. Its robust protection mechanisms, including overcurrent protection (OCP), overvoltage protection (OVP), undervoltage protection (UVP), and over-temperature protection (OTP), ensure reliable and safe operation under all conditions.

The controller also supports serial communication through SMBus/I<sup>2</sup>C to allow the programing of critical parameters for tailored performance. Customizable parameters include minimum input voltage, maximum output voltage, input current limits, and output current

limits, offering flexibility and adaptability for diverse applications.

#### **Features**

- Single inductor 3-level buck controller

- Patented modulator for flying capacitor balancing and smooth mode transition

- Wide input voltage range: 4.5V to 57.6V

- Wide output voltage range: 3V to 54.912V

- Programmable switching frequency: up to 400kHz (800kHz at switching node effectively)

- EXT5V pin to generate 5V or 10V gate drive voltage through internal charge pump

- Low shutdown current: 25µA

- Pass through mode (PTM) in both directions

- Support pre-biased output with soft-start

- Input and output current monitor

- Protection features: OCP, OVP, UVP, and OTP

- SMBus and I<sup>2</sup>C compatible

- 32 Ld 4x4 TQFN package

#### **Applications**

- USB PD 3.0/3.1 systems

- Docking stations

- Battery powered mobile devices

- Renewable energy systems

- Robots and drones

- Security surveillance

- Medical equipment

## **Contents**

| 1.  | Overv  | riew                                     | . 4 |

|-----|--------|------------------------------------------|-----|

|     | 1.1    | Block Diagram                            |     |

|     | 1.2    | Typical Applications                     |     |

| 2.  | Pin In | formation                                | . 7 |

|     | 2.1    | Pin Assignments                          | . 7 |

|     | 2.2    | Pin Descriptions                         | . 7 |

| 3.  | Speci  | fications                                | . 9 |

|     | 3.1    | Absolute Maximum Ratings                 | . 9 |

|     | 3.2    | Recommended Operating Conditions         | . 9 |

|     | 3.3    | Thermal Specifications                   | . 9 |

|     | 3.4    | Electrical Specifications                | 10  |

|     | 3.5    | SMBus Timing Specifications              | 14  |

| 4.  | Typic  | al Performance Graphs                    | 14  |

| 5.  | Gene   | ral SMBus Architecture                   | 16  |

|     | 5.1    | Data Validity                            |     |

|     | 5.2    | START and STOP Conditions                |     |

|     | 5.3    | Acknowledge                              |     |

|     | 5.4    | SMBus Transactions                       |     |

|     | 5.5    | Byte Format                              |     |

|     | 5.6    | SMBus and I <sup>2</sup> C Compatibility |     |

| 6.  | RAA4   | 89300 SMBus Commands                     |     |

| •   | 6.1    | Setting Input Current Limit              |     |

|     | 6.2    | Setting Output Current Limit             |     |

|     | 6.3    | Setting Output Voltage                   |     |

|     | 6.4    | Setting VINOK Reference                  |     |

|     | 6.5    | Setting Minimum Input Voltage            |     |

|     | 6.6    | Setting Reverse PTM Voltage              |     |

|     | 6.7    | Control Registers                        |     |

|     | 6.8    | Information Register                     |     |

|     | 6.9    | ADC register                             |     |

| 7.  | Modu   | lator Information                        |     |

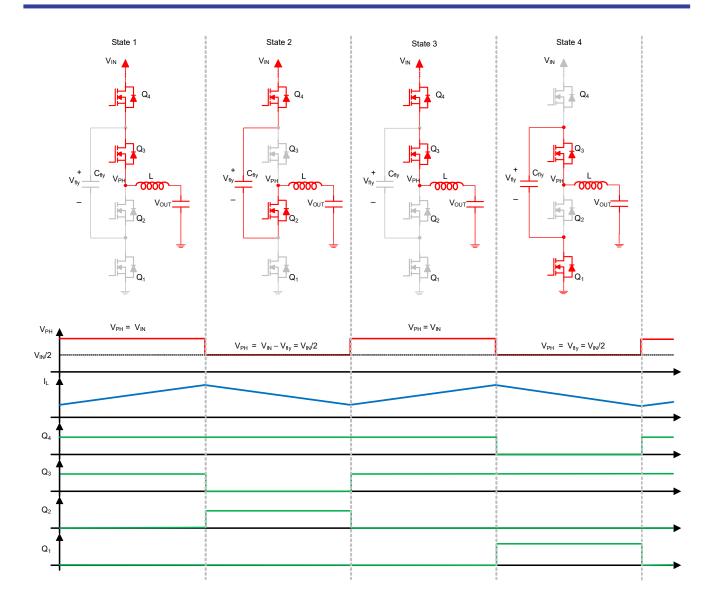

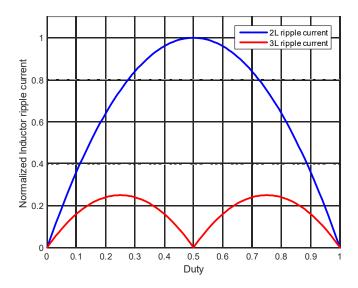

| • • | 7.1    | 3-Level Buck Converter Operation         |     |

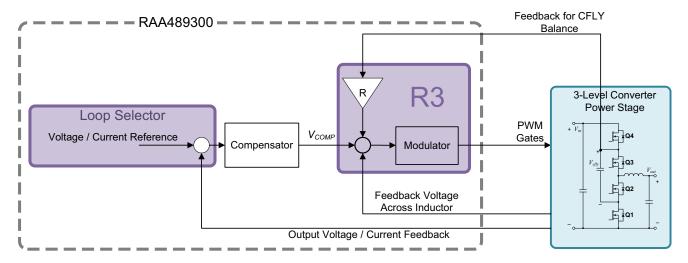

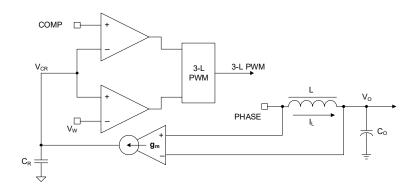

|     | 7.2    | Modulator                                |     |

| 8.  |        | cation Information                       |     |

| ٥.  | 8.1    | Soft-Start                               |     |

|     | 8.2    | PROG Pin Option                          |     |

|     | 8.3    | EXT5V and Gate Voltage                   |     |

|     | 8.4    | Pass-Through Mode                        |     |

|     | 8.5    | Cfly Balance                             |     |

|     | 8.6    | PGOOD                                    |     |

|     | 8.7    | IGATE Control                            |     |

|     | 8.8    | General-Purpose Comparator               |     |

|     | 8.9    | Current Alert                            |     |

|     | 8.10   | Current Monitoring (IMON)                |     |

|     | 8.11   | Analog-to-Digital Converter              |     |

|     | 8.12   | Auto Discharge                           |     |

|     | 8.13   | Output Short-Circuit Protection          |     |

|     | 8.14   | Phase Comparator                         |     |

|     | 8.15   | Faults, Interrupts, and Alerts           |     |

| 9.  |        | cation Design Guidelines                 |     |

| ٠.  | Appin  |                                          | 55  |

### RAA489300 Datasheet

| 10. | -      | t Guidelines                 |    |

|-----|--------|------------------------------|----|

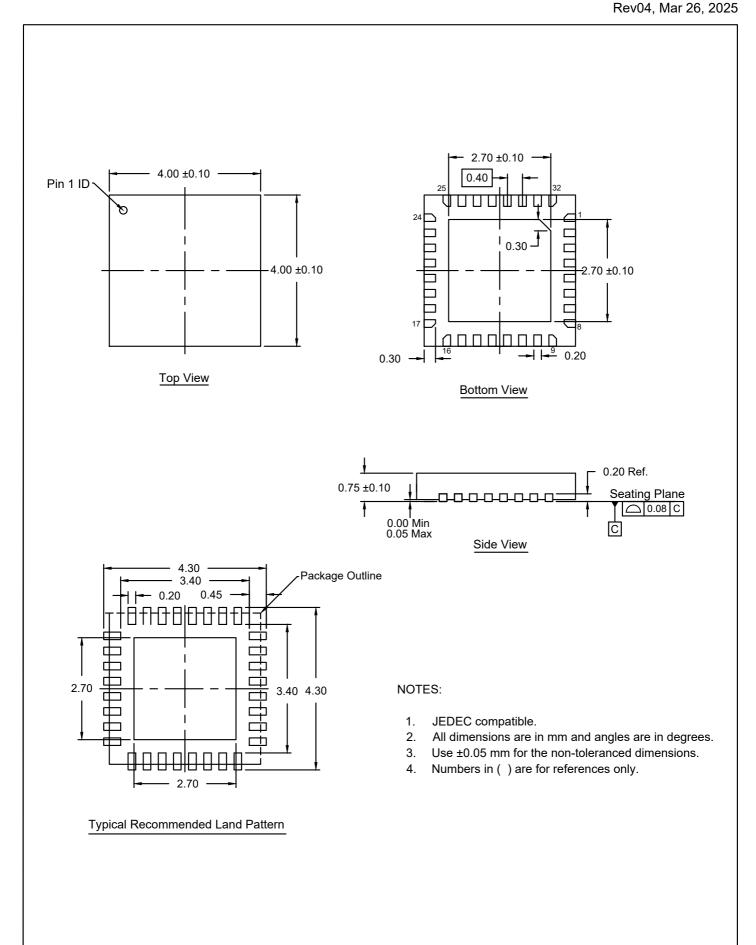

| 11. | Packa  | ge Outline Drawings          | 65 |

| 12. | Orderi | ng Information               | 65 |

| 13. | Revisi | on History                   | 65 |

| A.  | ECAD   | Design Information           | 66 |

|     | A.1    | Part Number Indexing         | 66 |

|     | A.2    | Symbol Pin Information       | 66 |

|     | A.3    | Symbol Parameters            | 67 |

|     | A.4    | Footprint Design Information | 68 |

### 1. Overview

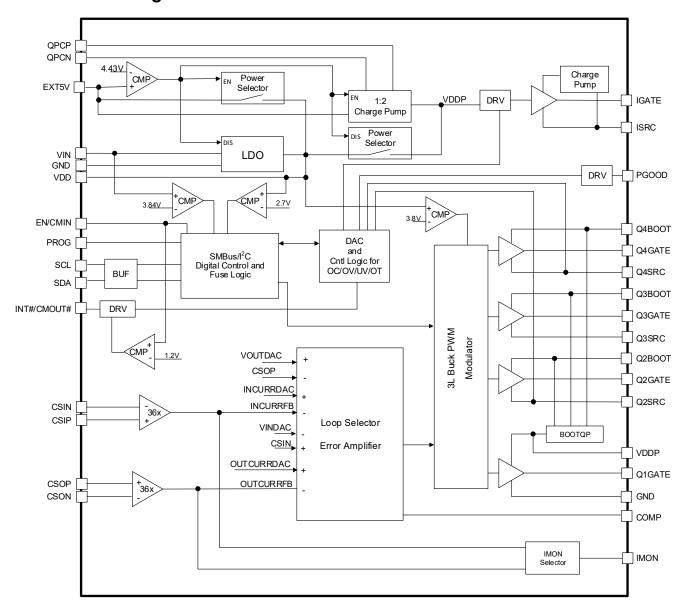

# 1.1 Block Diagram

Figure 1. Block Diagram

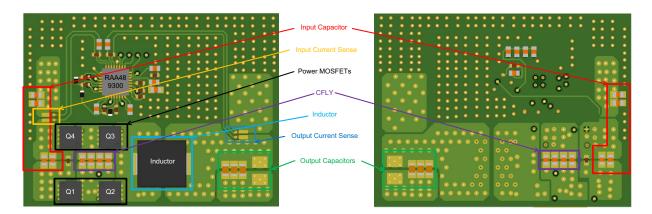

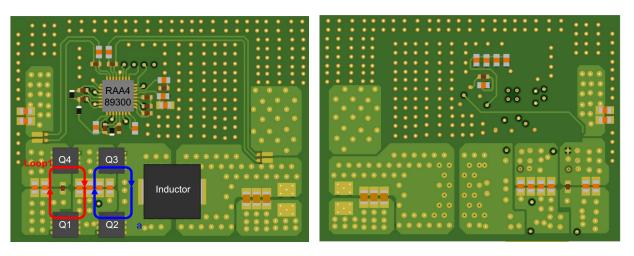

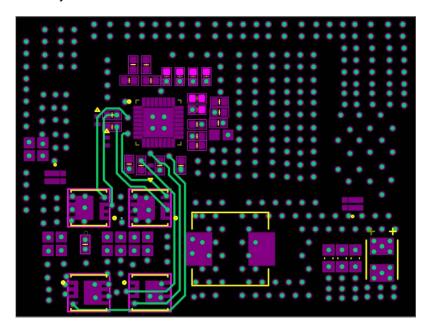

## 1.2 Typical Applications

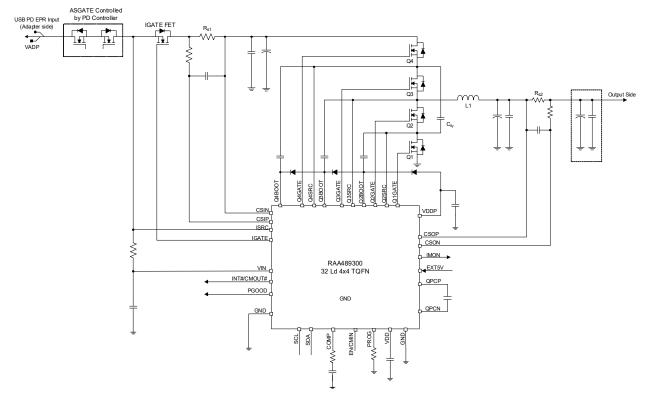

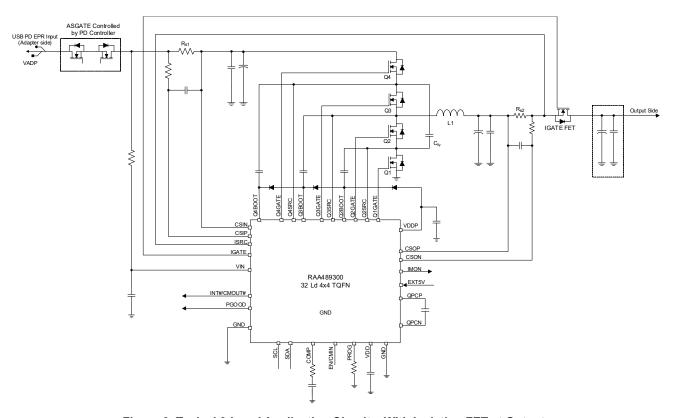

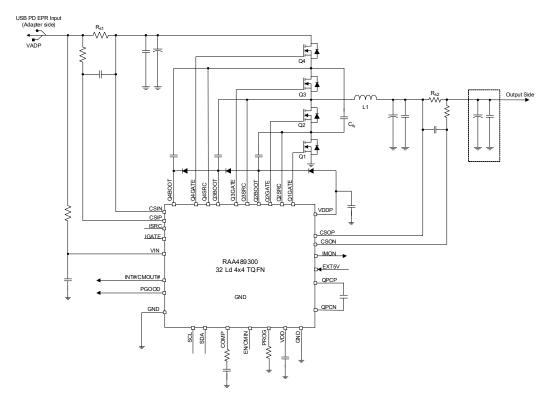

### 1.2.1 3-Level Configurations

Figure 2. Typical 3-Level Application Circuit – With Isolation FET at Input

Figure 3. Typical 3-Level Application Circuit – With Isolation FET at Output

Figure 4. Typical 3-Level Application Circuit – Without Isolation FET

## 2. Pin Information

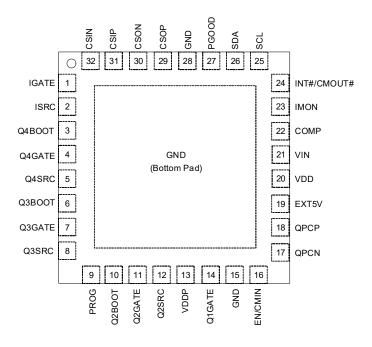

## 2.1 Pin Assignments

Figure 5. Pin Assignments - Top View

## 2.2 Pin Descriptions

| Pin<br>Number | Pin Name | Description                                                                                                                                                                                    |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | IGATE    | Output of the gate driver for an isolation FET (N-Channel). The use of an isolation FET is optional. Leave this pin floating if there is no isolation FET.                                     |

| 2             | ISRC     | Source terminal of the IGATE FET.                                                                                                                                                              |

| 3             | Q4BOOT   | Q4 MOSFET gate driver supply. Between Q4BOOT and Q4SRC, connect an MLCC that has an effective capacitance of at least 50 times the Cg of the Q4 MOSFET and is not less than 200nF at 10V.      |

| 4             | Q4GATE   | Q4 MOSFET gate driver output.                                                                                                                                                                  |

| 5             | Q4SRC    | Current return path for the Q4 MOSFET gate drive. Connect this pin to the node consisting of the Q4 MOSFET source, the Q3 MOSFET drain, and the positive input terminal of flying capacitor.   |

| 6             | Q3BOOT   | Q3 MOSFET gate driver supply. Between Q3BOOT and Q3SRC, connect an MLCC that has an effective capacitance of at least 50 times the Cg of the Q3 MOSFET and is no less than 200nF at 10V.       |

| 7             | Q3GATE   | Q3 MOSFET gate driver output.                                                                                                                                                                  |

| 8             | Q3SRC    | Current return path for Q3 MOSFET gate drive. Connect this pin to the node consisting of the Q3 MOSFET source, the Q2 MOSFET drain, and the input terminal of the inductor.                    |

| 9             | PROG     | Connect a resistor to GND. Configures default address, default operation, and default input current limit.                                                                                     |

| 10            | Q2BOOT   | Q2 MOSFET gate driver supply. Between Q2BOOT and Q2SRC, connect an MLCC that has an effective capacitance of at least 50 times the Cg of the Q2 MOSFET, and that is no less than 200nF at 10V. |

| 11            | Q2GATE   | Q2 MOSFET gate driver output.                                                                                                                                                                  |

| 12            | Q2SRC    | Current return path for the Q2 MOSFET gate drive. Connect this pin to the node consisting of the Q2 MOSFET source, the Q1 MOSFET drain, and the negative input terminal of flying capacitor.   |

| 13            | VDDP     | Power supply for the gate drivers. Between VDDP and GND, connect an MLCC that has an effective capacitance of at least 50 times the Cg of the Q1 MOSFET and is no less than 200nF at 10V.      |

| 14            | Q1GATE   | Q1 MOSFET gate driver output.                                                                                                                                                                  |

### RAA489300 Datasheet

| Pin<br>Number | Pin Name    | Description                                                                                                                                                                                                                                                                                             |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | GND         | Connect to GND.                                                                                                                                                                                                                                                                                         |

| 16            | EN/CMIN     | Input pin. It can be configured as enable switching or general-purpose comparator input based on Control0 register Bit[3].                                                                                                                                                                              |

| 17            | QPCN        | Internal charge pump capacitor negative input. Connect an MLCC capacitor across the QPCP pin and the QPCN pin.                                                                                                                                                                                          |

| 18            | QPCP        | Internal charge pump capacitor positive input. Connect an MLCC capacitor across the QPCP pin and the QPCN pin.                                                                                                                                                                                          |

| 19            | EXT5V       | Input from external 5V supply or external 5V rail.                                                                                                                                                                                                                                                      |

| 20            | VDD         | Internal LDO output that provides the bias power for the internal analog and digital circuit. Connect an MLCC between VDD and GND. MLCC should have an effective capacitance of 1µF at 5V.                                                                                                              |

| 21            | VIN         | Input voltage sense. The input voltage is valid if the VIN pin voltage is greater than 3.84V when the VIN voltage is rising. The VIN pin can be one of the internal LDO inputs. The LDO provides power to the IC. Connect an MLCC having an effective capacitance of at least 200nF at 48V.             |

| 22            | COMP        | Error amplifier output. Connect a compensation network externally from COMP to GND.                                                                                                                                                                                                                     |

| 23            | IMON        | Input or output current monitor output. The default is output current monitor.                                                                                                                                                                                                                          |

| 24            | INT#/CMOUT# | Open-drain output. This output is driven from the active-low interrupt function or the general-purpose comparator. When configured as an interrupt, this pin indicates abnormal events such as WOC, OV, UV, OTP, CFLY UV OV, and others. The interrupt status register must be read to clear the latch. |

| 25            | SCL         | SMBus clock I/O. Connect to the clock line from the host controller or smart battery. Connect a 10k pull-up resistor according to the SMBus specification.                                                                                                                                              |

| 26            | SDA         | SMBus data I/O. Connect to the data line from the host controller or smart battery. Connect a 10k pull-up resistor according to the SMBus specification.                                                                                                                                                |

| 27            | PGOOD       | Open-drain output. This indicates if the output voltage is within the value set by PGOOD register.                                                                                                                                                                                                      |

| 28            | GND         | Connect to GND.                                                                                                                                                                                                                                                                                         |

| 29            | CSOP        | Output current sense positive input. Place a 4.7µF MLCC between CSOP and CSON to provide differential mode filtering.                                                                                                                                                                                   |

| 30            | CSON        | Output current sense negative input. Place a 4.7µF MLCC between CSOP and CSON to provide differential mode filtering.                                                                                                                                                                                   |

| 31            | CSIP        | Input current sense positive input. Place a 10µF MLCC between CSIP and CSIN to provide differential mode filtering.                                                                                                                                                                                     |

| 32            | CSIN        | Input current sense negative input. Place a 10µF MLCC between CSIP and CSIN to provide differential mode filtering.                                                                                                                                                                                     |

## 3. Specifications

## 3.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                                                                        | Minimum          | Maximum      | Unit |

|------------------------------------------------------------------------------------------------------------------|------------------|--------------|------|

| Q4BOOT, Q3BOOT                                                                                                   | -0.3             | 73           | V    |

| CSIP, CSIN, CSOP, CSON, ISRC, VIN, Q2BOOT, Q4SRC                                                                 | -0.3             | 63           | V    |

| Q2SRC, Q3SRC                                                                                                     | -1, -3.5 (<10ns) | 63           | V    |

| CSIP-CSIN, CSOP-CSON                                                                                             | -0.3             | 0.3          | V    |

| VDDP                                                                                                             | -0.3             | 12           | V    |

| Q2BOOT-Q2SRC, Q3BOOT-Q3SRC, Q4BOOT-Q4SRC                                                                         | -0.3             | 14           | V    |

| Q1GATE                                                                                                           | GND - 0.3        | VDDP + 0.3   | V    |

| Q2GATE                                                                                                           | Q2SRC - 0.3      | Q2BOOT + 0.3 | V    |

| Q3GATE                                                                                                           | Q3SRC - 0.3      | Q3BOOT + 0.3 | V    |

| Q4GATE                                                                                                           | Q4SRC - 0.3      | Q4BOOT + 0.3 | V    |

| IGATE-ISRC, VDDP-EXT5V, VDDP-VDD, QPCP-QPCN, VDD, VDD-EXT5V, EXT5V, EN/CMIN, VINOK, INT#/CMOUT#, SCL, SDA, PGOOD | -0.3             | 6.5          | V    |

| QPCP                                                                                                             | EXT5V-0.3        | VDDP + 0.3   | V    |

| QPCN                                                                                                             | -0.3             | EXT5V + 0.3  | V    |

| IMON, COMP, PROG                                                                                                 | -0.3             | VDD + 0.3    | V    |

| Human Body Model (Tested per JS-001-2023)                                                                        | -                | 2            | kV   |

| Charged Device Model (Tested per JS-002-2022)                                                                    | -                | 750          | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A)                                                                  | -                | 100          | mA   |

## 3.2 Recommended Operating Conditions

| Parameter           | Minimum | Maximum | Unit |    |

|---------------------|---------|---------|------|----|

| Ambient Temperature | ARGNP   | -10     | +100 | °C |

| Ambient Temperature | A3GNP   | -40     | +105 |    |

## 3.3 Thermal Specifications

| Parameter          | Package                 | Symbol                         | Conditions        | Typical<br>Value | Unit |

|--------------------|-------------------------|--------------------------------|-------------------|------------------|------|

| Thermal Resistance | 32 Ld 4x4 TQFN Package  | θ <sub>JA</sub> [1]            | Junction to air.  | 37               | °C/W |

| Thermal Nesistance | 32 Lu 4x4 TQTTVT ackage | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case. | 2                | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured with the component mounted on a low-effective thermal conductivity test board in free air. See TB379 for details.

<sup>2.</sup> For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

## 3.4 Electrical Specifications

Limits apply across the junction temperature range, -40°C to +125°C unless otherwise specified.

| Parameter                                | Symbol             | Test Conditions                                      | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit |

|------------------------------------------|--------------------|------------------------------------------------------|--------------------|------|--------------------|------|

| UVLO/ACOK                                | 1                  | 1                                                    |                    |      | 1                  | l .  |

| VIN UVLO Rising                          | VIN_UVLO_r         | -                                                    | 3.50               | 3.84 | 4.20               | V    |

| VIN UVLO Hysteresis                      | VIN_UVLO_h         | -                                                    | -                  | 240  | -                  | mV   |

| VDD 3P8 Rising                           | VDD_3P8_r          | -                                                    | 3.45               | 3.8  | 4.25               | V    |

| VDD 3P8 Hysteresis                       | VDD_3P8_h          | -                                                    | -                  | 150  | -                  | mV   |

| EXT5V Rising                             | EXT5V_r            | -                                                    | 4.30               | 4.7  | 4.95               | V    |

| EXT5V Hysteresis                         | EXT5V_h            | -                                                    | -                  | 400  | -                  | mV   |

| EN Threshold                             | EN_r               | -                                                    | 0.50               | 0.7  | 1.10               | V    |

| Bias Current                             |                    |                                                      |                    |      |                    |      |

| VIN Supply Current                       | I_VIN_SLEEP        | EXT5V = 0V, VIN = 5V, SLEEP state                    | -                  | 25   | -                  | μA   |

| EXT5V Supply Current                     | I_EXT5V_READY      | VIN ≥ 5V, EXT5V = 5V, READY state                    | -                  | 2.6  | -                  | mA   |

| Forward Supply Current,<br>Enable State  | I_EXT5V_<br>SWITCH | VIN ≥ 5V, EXT5V = 5V, SWITCHING state                | -                  | 2.9  | -                  | mA   |

| Linear Regulator                         | •                  |                                                      |                    |      |                    |      |

| VDD Output Voltage                       | VDD                | VIN = 6V to 57.6V, EXT5V = 0V                        | 4.7                | 5    | 5.6                | V    |

| VDD Dropout Voltage                      | VDD_dp             | VIN = 4.5V, I <sub>VDD</sub> = 10mA                  | 75                 | 130  | 170                | mV   |

| VDD Overcurrent Threshold                | VDD_OC_<br>READY   | VIN = 6V, V <sub>VDD</sub> = 4.0V, READY state       | 40                 | 100  | 150                | mA   |

|                                          | VDD_OC_<br>SLEEP   | VIN = 6V, V <sub>VDD</sub> = 4.0V, SLEEP state       | 18                 | 33   | 50                 | mA   |

| Input Current Regulation, Re             | s1 = 10mΩ          |                                                      |                    |      |                    |      |

|                                          |                    | VCSIP - VCSIN = 60mV (6A),<br>CSIP = 4.5V to 57.6V   | -3                 | -    | 3                  |      |

|                                          |                    | VCSIP - VCSIN = 25mV (2.5A),<br>CSIP = 4.5V to 57.6V | -4                 | -    | 4                  | -    |

| Input Current Accuracy                   | Accuracy CSIx_acc  | VCSIP - VCSIN = 15mV (1.5A),<br>CSIP = 4.5V to 57.6V | -6                 | -    | 6                  | %    |

|                                          |                    | VCSIP - VCSIN = 10mV (1A),<br>CSIP = 4.5V to 57.6V   | -9                 | -    | 9                  |      |

|                                          |                    | VCSIP - VCSIN = 5mV (0.5A),<br>CSIP = 4.5V to 57.6V  | -15                | -    | 15                 | -    |

| Voltage Regulation                       |                    |                                                      |                    |      |                    |      |

| Output Voltage Accuracy,<br>Forward Mode | VCSOP_acc          | 20V output case                                      | -1                 | -    | 1                  | 0/2  |

| Input Voltage Regulation Accuracy        | VCSIN_acc          | Min VIN DAC = 10.034V                                | -3                 | -    | 3                  | %    |

| Output Current Regulation,               | Rs2 = 5mΩ          |                                                      | · ·                |      | •                  |      |

|                                          |                    | VCSOP- VCSON = 60mV (12A)                            | -3                 | -    | 3                  |      |

|                                          |                    | VCSOP- VCSON = 25mV (5A)                             | -4                 | -    | 4                  | 1    |

| Output Current Accuracy                  | CSOx_acc           | VCSOP- VCSON = 15mV (3A)                             | -9                 | -    | 9                  | %    |

|                                          |                    | VCSOP- VCSON = 10mV (2A)                             | -16                | •    | 16                 |      |

|                                          |                    | VCSOP- VCSON = 5mV (1A)                              | -25                | -    | 25                 | 1    |

Limits apply across the junction temperature range, -40  $^{\circ}$ C to +125  $^{\circ}$ C unless otherwise specified.

| IMON                                                                |                   |                                                    |          |      |      |     |

|---------------------------------------------------------------------|-------------------|----------------------------------------------------|----------|------|------|-----|

| Input Current Sense Amplific                                        | er, Rs1 = 10mΩ    |                                                    |          |      |      |     |

| Forward IMON_IN Gain                                                | IMON_IN_gain      | -                                                  | -        | 36   | -    | V/V |

|                                                                     |                   | VCSIP - VCSIN = 60mV (6A),<br>CSIP = 5V to 57.6V   | -3       | -    | 3    |     |

|                                                                     |                   | VCSIP - VCSIN = 25mV (2.5A),<br>CSIP = 5V to 57.6V | -6       | -    | 6    |     |

| Forward IMON_IN Accuracy VIMON_IN = IMON_IN gain x (CSIP - CSIN)    | IMON_IN_acc       | VCSIP - VCSIN = 15mV (1.5A),<br>CSIP = 5V to 57.6V | -12      | -    | 12   | %   |

| (CSIF - CSIN)                                                       |                   | VCSIP - VCSIN = 10mV (1A),<br>CSIP = 5V to 57.6V   | -20      | -    | 20   |     |

|                                                                     |                   | VCSIP - VCSIN = 5mV (0.5A),<br>CSIP = 5V to 57.6V  | -40      | -    | 40   |     |

| Output Current Sense Ampli                                          | fier, Rs2 = 5mΩ   |                                                    | <u> </u> |      | 1    |     |

| Forward IMON_OUT Gain                                               | IMON_OUT_<br>gain | -                                                  | -        | 36   | -    | V/V |

|                                                                     |                   | VCSOP - VCSON = 60mV (12A),<br>VCSON = 20V         | -3       | -    | 3    |     |

|                                                                     |                   | VCSOP - VCSON = 25mV (5A),<br>VCSON = 20V          | -6       | -    | 6    | %   |

| IMON_OUT Accuracy<br>VIMON_OUT = IMON_OUT<br>Gain x (VCSOP - VCSON) |                   | VCSOP - VCSON = 15mV (3A),<br>VCSON = 20V          | -12      | -    | 12   |     |

| Cam X (VCCC) VCCCIV)                                                |                   | VCSOP - VCSON = 10mV (2A),<br>VCSON = 20V          | -20      | -    | 20   |     |

|                                                                     |                   | VCSOP - VCSON = 5mV (1A),<br>VCSON = 20V           | -40      | -    | 40   |     |

| INT#/CMOUT#                                                         |                   |                                                    | '        |      | l    |     |

| INT#, Input Leakage Current                                         |                   | -                                                  | -        | -    | 1    | μA  |

| INT#, Output Current Sink                                           | -                 | VINT# = 0.4V                                       | 4        | -    | -    | mA  |

| General-Purpose Comparato                                           | or                |                                                    | <u> </u> |      | I    |     |

| General-Purpose                                                     | ороомр            | Reference = 1.2V                                   | 1.14     | 1.2  | 1.32 | V   |

| Comparator Rising Threshold                                         | GPCOMP_r          | Reference = 2V                                     | 1.98     | 2    | 2.02 | V   |

| General-Purpose                                                     | 000010            | Reference = 1.2V                                   | -        | 45   | -    | mV  |

| Comparator Hysteresis                                               | GPCOMP_h          | Reference = 2V                                     | -        | 45   | -    | mV  |

| Protection                                                          | I                 |                                                    |          |      |      |     |

| V <sub>IN</sub> Absolute Overvoltage<br>Rising Threshold            | VIN_ABS_OV_r      | -                                                  | 57.1     | 57.8 | 58.5 | V   |

| V <sub>IN</sub> Absolute Overvoltage<br>Hysteresis                  | VIN_ABS_OV_h      | -                                                  | -        | 730  | -    | mV  |

|                                                                     |                   | Control1 register Bit[3:2] = 00                    | 23.4     | 24   | 24.6 |     |

| V <sub>OUT</sub> Absolute Overvoltage                               | VOLIT ADD ON      | Control1 register Bit[3:2] = 01                    | 32.9     | 33.6 | 34.3 | 1   |

| Rising Threshold                                                    | VOUT_ABS_OV_r     | Control1 register Bit[3:2] = 10                    | 44.8     | 45.6 | 44.4 | V   |

|                                                                     |                   | Control1 register Bit[3:2] = 11                    | 56.7     | 57.6 | 58.5 | -   |

| V <sub>OUT</sub> Absolute Overvoltage<br>Hysteresis                 | VOUT_ABS_OV_h     | -                                                  | -        | 800  | -    | mV  |

Limits apply across the junction temperature range, -40  $^{\circ}$ C to +125  $^{\circ}$ C unless otherwise specified.

|                                                     |                    | Control2 register Bit[9:8] = 00 from V <sub>OUT</sub>                                      |      |       |     |     |

|-----------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------|------|-------|-----|-----|

|                                                     |                    | DAC                                                                                        | -    | 5     | -   |     |

| PGOOD Window                                        | EDCOOD WIN         | Control2 register Bit[9:8] = 01 from V <sub>OUT</sub><br>DAC                               | -    | 10    | -   | - % |

| PGOOD WINDOW                                        | FPGOOD_WIN         | Control2 register Bit[9:8] = 10 from V <sub>OUT</sub> DAC                                  | -    | 15    | -   | - % |

|                                                     |                    | Control2 register Bit[9:8] = 11 from V <sub>OUT</sub> DAC                                  | -    | 20    | -   |     |

|                                                     |                    | Control2 register Bit[9:8] = 00 from V <sub>OUT</sub> DAC                                  | -    | 2.5   | -   |     |

|                                                     | FPGOOD             | Control2 register Bit[9:8] = 01 from V <sub>OUT</sub> DAC                                  | -    | 5     | -   |     |

| PGOOD Window Hysteresis                             | WIN_h              | Control2 register Bit[9:8] = 10 from V <sub>OUT</sub> DAC                                  | -    | 5     | -   | - % |

|                                                     |                    | Control2 register Bit[9:8] = 11 from V <sub>OUT</sub> DAC                                  | -    | 5     | -   |     |

| V <sub>OUT</sub> OK Threshold                       | VOUT_OK_th         | -                                                                                          | -    | 0.6   | -   | V   |

| V <sub>OUT</sub> OK Source Current                  | VOUT_OK_lsr        | -                                                                                          | -    | 10    | -   | mA  |

| Input Way Overcurrent Rising Threshold              | WOCP_IN_r          | Rs1 = 10mΩ, Control1 register Bit[7] = 0                                                   | 15.6 | 16.8  | 18  | А   |

| Output Way Overcurrent<br>Rising Threshold          | WOCP_OUT_r         | Rs2 = 5mΩ. Control1 register Bit[7] = 0                                                    | 31.2 | 33.6  | 36  | А   |

|                                                     |                    | Control2 register Bit[9:8] = 00 from<br>Reverse PTM Voltage DAC                            | -    | 5     | -   | - % |

| Reverse PTM PGOOD                                   |                    | Control2 register Bit[9:8] = 01 from<br>Reverse PTM Voltage DAC                            | -    | 10    | -   |     |

| Window <sup>[1]</sup>                               | RPGOOD_WIN         | Control2 register Bit[9:8] = 10 from<br>Reverse PTM Voltage DAC                            | -    | 15    | -   |     |

|                                                     |                    | Control2 register Bit[9:8] = 11 from<br>Reverse PTM Voltage DAC                            | -    | 20    | -   |     |

|                                                     |                    | Control2 register Bit[9:8] = 00 from<br>Reverse PTM Voltage DAC                            | -    | 2.5   | -   |     |

| Reverse PTM PGOOD                                   | RPGOOD             | Control2 register Bit[9:8] = 01 from<br>Reverse PTM Voltage DAC                            | -    | 5     | -   |     |

| Hysteresis <sup>[1]</sup>                           | WIN_h              | Control2 register Bit[9:8] = 10 from<br>Reverse PTM Voltage DAC                            | -    | 5     | -   | V   |

|                                                     |                    | Control2 register Bit[9:8] = 11 from<br>Reverse PTM Voltage DAC                            | -    | 5     | -   |     |

|                                                     |                    | Control3 Bit[10:9] = 00,<br>VCFLY_OV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2       | -    | 1.5   | -   |     |

| CFLY Switching Overvoltage Ratio <sup>[1]</sup>     | VCFLY_OV_<br>ratio | Control3 Bit[10:9] = 01 or 11,<br>VCFLY_OV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2 | -    | 1.25  | -   | N/A |

|                                                     |                    | Control3 Bit[10:9] = 10,<br>VCFLY_OV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2       | -    | 1.125 | -   |     |

|                                                     |                    | Control3 Bit[10:9] = 00,<br>VCFLY_UV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2       | -    | 0.5   | -   |     |

| CFLY Switching<br>Undervoltage Ratio <sup>[1]</sup> | VCFLY_UV_<br>ratio | Control3 Bit[10:9] = 01 or 11,<br>VCFLY_UV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2 | -    | 0.25  | -   | N/A |

|                                                     |                    | Control3 Bit[10:9] = 10,<br>VCFLY_UV_ratio = V <sub>CFLY</sub> / V <sub>IN</sub> / 2       | -    | 0.125 | -   |     |

| Over-Temperature Threshold                          | OT_th              | -                                                                                          | 140  | 150   | 160 | °C  |

Limits apply across the junction temperature range, -40  $^{\circ}$ C to +125  $^{\circ}$ C unless otherwise specified.

| Oscillator                                 |                         | 1                                           |      |       |          | 1        |

|--------------------------------------------|-------------------------|---------------------------------------------|------|-------|----------|----------|

| Oscillator Frequency, Digital<br>Core Only | -                       | -                                           | 0.85 | 1     | 1.15     | MHz      |

| Digital Debounce Time<br>Accuracy          | -                       | -                                           | -15  | -     | 15       | %        |

| Miscellaneous                              |                         |                                             |      |       |          |          |

| Switching Frequency<br>Accuracy            | SW_Freq_acc             | VCOMP > 1.7V and not in period stretching   | -15  | -     | 15       | %        |

| CSIN Discharge Current                     | CSIN_I_dc               | Control2 register Bit[13] = 0               | -    | 20    | -        | mA       |

| CSOP Discharge Current                     | CSOP_I_dc               | Control2 register Bit[12] = 0               | -    | 20    | 1        | mA       |

| Gate Driver                                |                         |                                             |      |       |          |          |

| Q1GATE Pull-Up Resistance                  | Q1GRPU                  | 10V gate drive at 100mA source current      | -    | 1.275 | 2.50     | Ω        |

| Q1GATE Source Current                      | Q1GSRC                  | VQ1BOOT – VQ1GATE = 2.5V                    | -    | 2.346 | 1        | А        |

| Q1GATE Pull-Down<br>Resistance             | Q1GRPD                  | 10V gate drive at 100mA source current      | -    | 1.029 | 1.50     | Ω        |

| Q1GATE Sink Current                        | Q1GSNK                  | VQ1BOOT - VQ1SRC = 2.5V                     | -    | 1.692 | -        | А        |

| Q2GATE Pull-Up Resistance                  | Q2GRPU                  | 10V gate drive at 100mA source current      | -    | 1.275 | 2.50     | Ω        |

| Q2GATE Source Current                      | Q2GSRC                  | VQ2BOOT – VQ2GATE = 2.5V                    | -    | 2.346 | -        | А        |

| Q2GATE Pull-Down<br>Resistance             | Q2GRPD                  | 10V gate drive at 100mA source current      | -    | 1.029 | 1.50     | Ω        |

| Q2GATE Sink Current                        | Q2GSNK                  | VQ2BOOT – VQ2SRC = 2.5V                     | -    | 1.692 | -        | Α        |

| Q3GATE Pull-Up Resistance                  | Q3GRPU                  | 10V gate drive at 100mA source current      | -    | 1.275 | 2.50     | Ω        |

| Q3GATE Source Current                      | Q3GSRC                  | VQ3BOOT – VQ3GATE = 2.5V                    | -    | 2.346 | -        | А        |

| Q3GATE Pull-Down<br>Resistance             | Q3GRPD                  | 10V gate drive at 100mA source current      | -    | 1.029 | 1.50     | Ω        |

| Q3GATE Sink Current                        | Q3GSNK                  | VQ3BOOT – VQ3SRC = 2.5V                     | -    | 1.692 | -        | Α        |

| Q4GATE Pull-Up Resistance                  | Q4GRPU                  | 10V gate drive at 100mA source current      | -    | 1.275 | 2.50     | Ω        |

| Q4GATE Source Current                      | Q4GSRC                  | VQ3BOOT – VQ3GATE = 2.5V                    | -    | 2.346 | -        | А        |

| Q4GATE Pull-Down<br>Resistance             | Q4GRPD                  | 10V gate drive at 100mA source current      | -    | 1.029 | 1.50     | Ω        |

| Q4GATE Sink Current                        | Q4GSNK                  | VQ3BOOT – VQ3SRC = 2.5V                     | -    | 1.692 | -        | А        |

| Q1GATE1 to Q4GATE1<br>Dead Time            | t <sub>Q1GQ4GDEAD</sub> | -                                           | -    | 20    | -        | ns       |

| Q4GATE1 to Q1GATE1<br>Dead Time            | t <sub>Q4GQ1GDEAD</sub> | -                                           | -    | 20    | -        | ns       |

| Q2GATE1 to Q3GATE1<br>Dead Time            | t <sub>Q2GQ3GDEAD</sub> | -                                           | -    | 20    | -        | ns       |

| Q3GATE1 to Q2GATE1<br>Dead Time            | t <sub>Q3GQ2GDEAD</sub> | -                                           | -    | 20    | -        | ns       |

| Charge Pump Gate Drivers                   |                         | 1                                           | ц    | I     |          | 1        |

| IGATE Gate Drive Current (Sink)            | IG_GD_I_sink            | V <sub>IGATE</sub> - V <sub>ISRC</sub> = 2V | -    | 190   | -        | μА       |

| IGATE Gate Drive Current (Source)          | IG_GD_I_src             | V <sub>IGATE</sub> - V <sub>ISRC</sub> = 2V | -    | 50    | -        | μА       |

| SMBus                                      |                         | 1                                           | ı    | 1     | <u> </u> | 1        |

| SDA/SC Input Low Voltage                   | -                       | -                                           | -    | -     | 0.6      | V        |

| SDA/SCL Input High Voltage                 | -                       | -                                           | 1.3  | -     | -        | V        |

| SDA/SCL Input Bias Current                 | -                       | -                                           | -    | -     | 1        | μA       |

| *                                          |                         | 1                                           | I    |       |          | <u> </u> |

Limits apply across the junction temperature range, -40°C to +125°C unless otherwise specified.

| SDA, Output Sink Current | -                | VSDA_B = 0.4V, on | 4  | - | -   | mA  |

|--------------------------|------------------|-------------------|----|---|-----|-----|

| SMBus Frequency          | f <sub>SMB</sub> | -                 | 10 | - | 400 | kHz |

<sup>1.</sup> Limits established by characterization and are not production tested.

## 3.5 SMBus Timing Specifications

| Parameters                           | Symbol              | Test Conditions                        | Min <sup>[1]</sup> | Тур | Max <sup>[1]</sup> | Unit |

|--------------------------------------|---------------------|----------------------------------------|--------------------|-----|--------------------|------|

| SMBUS Frequency                      |                     | (Supports Standard-Mode and Fast-mode) | 10                 | -   | -                  | kHz  |

| Bus Free Time                        | t <sub>BUF</sub>    | -                                      | 4.7                | -   | -                  | μs   |

| Start Condition Hold Time from SCL   | t <sub>HD:STA</sub> | -                                      | 4                  | -   | -                  | μs   |

| Start Condition Set-Up Time from SCL | t <sub>SU:STA</sub> | -                                      | 4.7                | -   | -                  | μs   |

| Stop Condition Set-Up Time from SCL  | t <sub>SU:STO</sub> | -                                      | 4                  | -   | -                  | μs   |

| SDA Hold Time from SCL               | t <sub>HD:DAT</sub> | -                                      | 300                | -   | -                  | μs   |

| SDA Set-Up Time from SCL             | t <sub>SU:DAT</sub> | -                                      | 250                | -   | -                  | μs   |

| SCL Low Period                       | t <sub>LOW</sub>    | For SMBus Standard-mode                | 4.7                | -   | -                  | μs   |

| SCL High Period                      | t <sub>HIGH</sub>   | For SMBus Standard-mode                | 4                  | -   | -                  | μs   |

<sup>1.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

# 4. Typical Performance Graphs

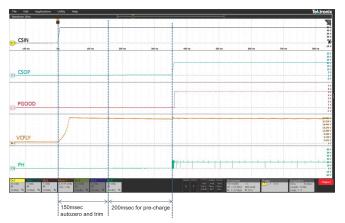

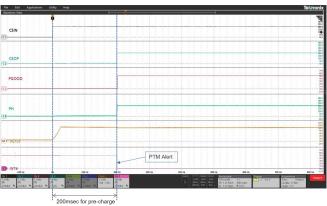

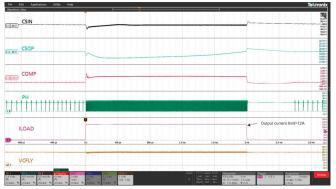

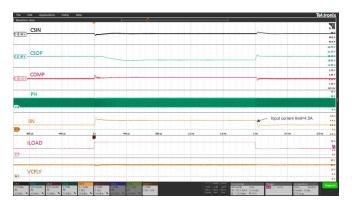

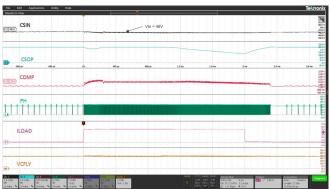

Figure 6. Startup without EXT5V,  $V_{IN} = 48V$ ,  $V_{OUT} = 20V$ , No Load

Figure 7. Startup with EXT5V, V<sub>IN</sub> = 48V, V<sub>OUT</sub> = 20V, No Load, Control0 Bits[14:13] = 0b01 (Pre-Charge Wait Time = 150ms)

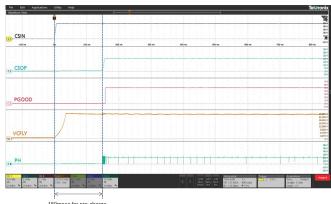

Figure 8. PTM Startup without EXT5V,  $V_{IN}$  = 20V,  $V_{OUT}$  = 20V, No Load (PROG Pin Resistrance = 7.5k $\Omega$ )

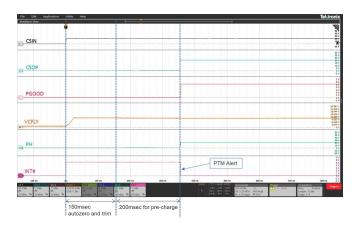

Figure 9. PTM Startup with EXT5V, V<sub>IN</sub> = 20V, V<sub>OUT</sub> = 20V, No Load

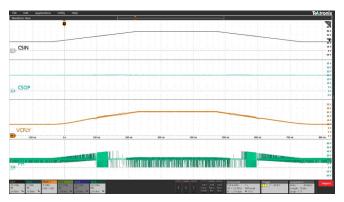

Figure 10. Flying Cap Voltage Regulation During  $V_{IN}$  Transition,  $V_{IN}$  = 22V to 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 10mA,  $V_{IN}$  slew rate = 0.1mV/ $\mu$ s

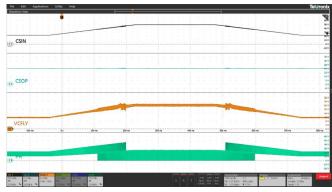

Figure 11. Flying Cap Voltage Regulation During  $V_{IN}$  Transition,  $V_{IN}$  = 22V to 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 12A,  $V_{IN}$  slew rate = 0.1mV/ $\mu$ s

Figure 12. Voltage Regulation During Load Transients,  $V_{IN}$  = 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 5A to 12A (Load Slew = 2.5A/ $\mu$ s, 5A\_Time = 12A\_Time = 2ms)

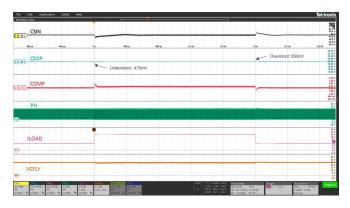

Figure 13. Output Current Regulation During Load Transients,  $V_{IN}$  = 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 0.1A to 12A (Load Slew = 2.5A/ $\mu$ s, 5A\_Time = 12A\_Time = 2ms, Output Current Limit = 12A)

Figure 14. Input Current Regulation During Load Transients,  $V_{IN}$  = 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 5A to 11A (Load Slew = 2.5A/µs, 11A time = 5A time = 2ms, Input Current Limit = 4.5A)

Figure 15. Input Voltage Regulation,  $V_{IN}$  = 48V,  $V_{OUT}$  = 20V,  $I_{OUT}$  = 0.1A to 5A (Load Slew = 2.5A/ $\mu$ s, 0.1A time = 5A time = 2ms, Min Input Voltage Limit = 46.053V, Input Power Supply Current Limit = 1A)

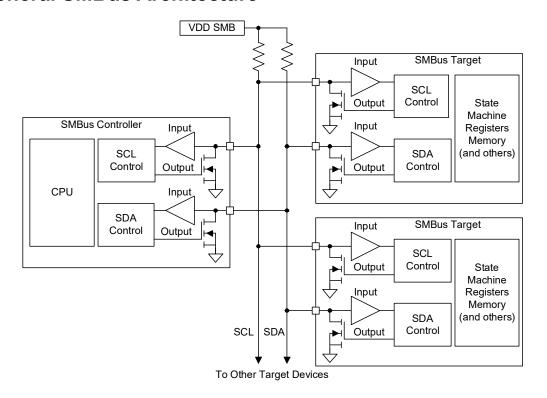

### 5. General SMBus Architecture

Figure 16. General SMBus

## 5.1 Data Validity

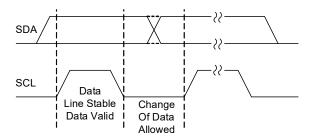

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can change only when the clock signal on the SCL line is LOW. See Figure 17.

Figure 17. Data Validity

#### 5.2 START and STOP Conditions

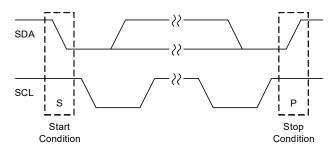

Figure 18 shows that the START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH.

Figure 18. Start and Stop Waveforms

### 5.3 Acknowledge

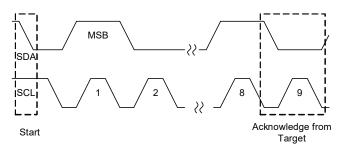

Each address and data transmission uses nine clock pulses. The ninth pulse is the Acknowledge bit (ACK). After the start condition, the controller sends seven target address bits and a R/W bit during the next eight clock pulses. During the ninth clock pulse, the device that recognizes its own address holds the data line low to acknowledge (see Figure 19). Both the controller and the target use the ACK bit to acknowledge receipt of register addresses and data.

Figure 19. Acknowledge on the SMBus

#### 5.4 SMBus Transactions

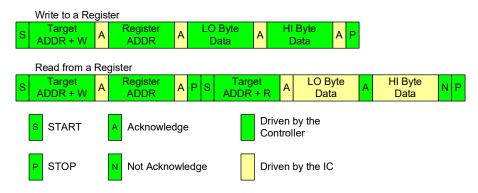

All transactions start with a control byte sent from the SMBus controller device. The control byte begins with a Start condition followed by seven bits of target address (0001001) and the R/W bit. The R/W bit is 0 for a WRITE or 1 for a READ. If any target device on the SMBus bus recognizes its address, it acknowledges by pulling the Serial Data (SDA) line low for the last clock cycle in the control byte. If no target exists at that address or it is not ready to communicate, the data line is 1 indicating a not acknowledge condition.

After the control byte is sent and the RAA489300 acknowledges it, the second byte sent by the controller must be a register address byte such as 0x14 for the ChargeCurrent register. The register address byte tells the RAA489300 which register the controller writes or reads. When the RAA489300 receives a register address byte, it responds with an acknowledge.

### 5.5 Byte Format

Every byte put on the SDA line must be eight bits long and must be followed by an ACK bit. Data is transferred with the Most Significant Bit (MSB) first and the Least Significant Bit (LSB) last. The LO Byte data is transferred before the HI Byte data. For example, when writing 0x41A0, 0xA0 is written first and 0x41 is written second.

Figure 20. SMBus Read and Write Protocol

## 5.6 SMBus and I<sup>2</sup>C Compatibility

The RAA489300 SMBus minimum input logic high voltage is 1.3V, so it is compatible with I<sup>2</sup>C with pull-up power supplies higher than 1.3V.

The RAA489300 SMBus registers are 16 bits, so it is compatible with 16-bit  $I^2C$  or 8-bit  $I^2C$  with auto-increment capability.

#### 6. RAA489300 SMBus Commands

The RAA489300 receives control inputs from the SMBus interface after Power-On Reset (POR). The serial interface complies with the System Management Bus Specification. The RAA489300 uses the SMBus Read-word and Write-word protocols, as shown in Figure 20, to communicate with the host system The RAA489300 is an SMBus target device and does not initiate communication on the bus. The RAA489300 offers two device address options, and the address is selected by programming through the PROG pin resistor. The two 7-bit device addresses are as follows:

Read addresses = 0b10010101(0x95)

Write addresses = 0b10010100(0x94)

Read addresses = 0b10010111(0x97)

Write addresses = 0b10010110(0x96)

The data (SDA) and clock (SCL) pins have Schmitt-trigger inputs that can accommodate slow edges. Choose pull-up resistors for SDA and SCL to achieve rise times according to the SMBus specifications.

The information in this datasheet is based on current sensing resistors Rs1 =  $10m\Omega$  and Rs2 =  $5m\Omega$ , unless otherwise specified.

The control inputs and control information of the RAA489300 received or provided can be done by writing or reading registers in Table 1 using the Write-word protocol shown in Figure 20.

**Table 1. Register Summary**

| Register Names                       | Register<br>Address | Read/<br>Write | Number of<br>Bits | Description                                                                                            | Default          |

|--------------------------------------|---------------------|----------------|-------------------|--------------------------------------------------------------------------------------------------------|------------------|

| Output Current Limit                 | 0x14                | R/W            | 11                | [13:3] 11-bit, LSB size 8mA, total range 12156mA with Rs2 = $10m\Omega$                                | 0x00BC<br>1500mA |

| Output Voltage                       | 0x15                | R/W            | 13                | [15:3] 13-bit, LSB size 12mV for PPS and 24mV for AVS, total range 24564mV for PPS and 54912mV for AVS | Set by PROG      |

| Control0                             | 0x39                | R/W            | 16                | Configures various options. See Table 11.                                                              | 0x0000           |

| Information1                         | 0x3A                | R              | 16                | Indicates various options. See Table 18.                                                               | 0x0000           |

| Control1                             | 0x3C                | R/W            | 16                | Configures various options. See Table 12.                                                              | 0x0000           |

| Control2                             | 0x3D                | R/W            | 16                | Configures various options. See Table 13.                                                              | 0x0000           |

| Input Current Limit                  | 0x3F                | R/W            | 11                | [12:2] 11-bit, LSB size 4mA (default) or 8mA, total range 6078mA (default) or 12156mA                  | Set by PROG      |

| VINOK Reference                      | 0x40                | R/W            | 8                 | [15:8] 8-bit, LSB size 257.28mV, total range 46310.4mV                                                 | 0mV              |

| Control6                             | 0x43                | R/W            | 16                | Configures various options. See Table 17.                                                              | 0x0000           |

| Reverse PTM Voltage <sup>[1]</sup>   | 0x49                | R/W            | 12                | [15:4] 12-bit, LSB size 12mV, total range 32784mV                                                      | 0mV              |

| Minimum Input Voltage <sup>[2]</sup> | 0x4B                | R/W            | 8                 | [15:8] 8-bit, LSB size 257.28mV, total range 46310.4mV                                                 | 0mV              |

| Control3                             | 0x4C                | R/W            | 16                | Configures various options. See Table 14.                                                              | 0x0000           |

| Information2                         | 0x4D                | R              | 5                 | Indicates various options. See Table 19.                                                               | 0x0000           |

| Control4                             | 0x4E                | R/W            | 2                 | Configures various options. See Table 15.                                                              | 0x0000           |

| Control5                             | 0x4F                | R/W            | 16                | Configures various options. See Table 16.                                                              | 0x0000           |

| Information3                         | 0x90                | R              | 16                | Indicates various options. See Table 20.                                                               | 0x0000           |

| Information4                         | 0x91                | R              | 16                | Indicates various options. See Table 21.                                                               | 0x0000           |

| Manufacturer ID                      | 0xFE                | R              | 8                 | Manufacturer ID register – 0x49. Read only                                                             | 0x0049           |

| Device ID                            | 0xFF                | R              | 8                 | Device ID register. Read only                                                                          | 0x0016           |

<sup>1.</sup> Although the register accepts values up to 32784mV, values should be lower than Absolute Input Overvoltage Threshold.

### 6.1 Setting Input Current Limit

To set the input current limit, write the 16-bit Input Current Limit register (0x3F) using the Write-word protocol shown in Figure 20.

The RAA489300 limits the input current based on the differential voltage across the CSIP and CSIN pins. The gain of the input current feedback signal can be set by Control1 Bit[7]. With the recommended current sense resistor value Rs1 =  $10 \text{ m}\Omega$ , the LSB of the Input Current Limit register according to Control1 Bit[7] is:

- Control1 Bit[7] = 0 (default): LSB of the Input Current Limit register is 4mA

- Control1 Bit[7] = 1: LSB of the Input Current Limit register is 8mA

The Input Current Limit register accepts any value, but only the valid bits are written to the register. The maximum input current limit, with Rs1 =  $10m\Omega$ , is clamped at 6078mA for Control1 Bit[7] = 0 or 12156mA for Control1 Bit[7] = 1.

After POR, the Input Current Limit register is reset to the value programmed through the PROG pin resistor. The Input Current Limit register can be read back to verify its value.

<sup>2.</sup> Although the register accepts values up to 46310mV, values should be lower than Absolute Input Overvoltage Threshold.

RAA489300 can limit the slew rate of the input current limit by setting Control3 Bit[15]. If Control3 Bit[15] is enabled, the input current limit DAC reference increases by 1LSB per 1µsec.

Table 2 and Table 3 show the data format of the input current limit with Rs1 =  $10m\Omega$  when Control1 Bit[7] = 0 and Control1 Bit[7] = 1, respectively.

Table 2. Input Current Limit Register 0x3F (11-bit, 4mA Step, 10mΩ Sense Resistor, Control1 Bit[7] = 0)

| Bit     | Description                                                                   |  |  |

|---------|-------------------------------------------------------------------------------|--|--|

| [1:0]   | Not used                                                                      |  |  |

| [2]     | 0 = Add 0mA of input current limit.<br>1 = Add 4mA of input current limit.    |  |  |

| [3]     | 0 = Add 0mA of input current limit.<br>1 = Add 8mA of input current limit.    |  |  |

| [4]     | 0 = Add 0mA of input current limit.<br>1 = Add 16mA of input current limit.   |  |  |

| [5]     | 0 = Add 0mA of input current limit.<br>1 = Add 32mA of input current limit.   |  |  |

| [6]     | 0 = Add 0mA of input current limit.<br>1 = Add 64mA of input current limit.   |  |  |

| [7]     | 0 = Add 0mA of input current limit.<br>1 = Add 128mA of input current limit.  |  |  |

| [8]     | 0 = Add 0mA of input current limit.<br>1 = Add 256mA of input current limit.  |  |  |

| [9]     | 0 = Add 0mA of input current limit.<br>1 = Add 512mA of input current limit.  |  |  |

| [10]    | 0 = Add 0mA of input current limit.<br>1 = Add 1024mA of input current limit. |  |  |

| [11]    | 0 = Add 0mA of input current limit.<br>1 = Add 2048mA of input current limit. |  |  |

| [12]    | 0 = Add 0mA of input current limit.<br>1 = Add 4096mA of input current limit. |  |  |

| [13:15] | Not used                                                                      |  |  |

| Maximum | [12:2] = 101 1111 0000: 6078mA                                                |  |  |

Table 3. Input Current Limit Register 0x3F (11-bit, 8mA Step, 10mΩ Sense Resistor, Control1 Bit[7] = 1)

| Bit     | Description                                                                   |

|---------|-------------------------------------------------------------------------------|

| [1:0]   | Not used                                                                      |

| [2]     | 0 = Add 0mA of input current limit. 1 = Add 8mA of input current limit.       |

| [3]     | 0 = Add 0mA of input current limit. 1 = Add 16mA of input current limit.      |

| [4]     | 0 = Add 0mA of input current limit.<br>1 = Add 32mA of input current limit.   |

| [5]     | 0 = Add 0mA of input current limit.<br>1 = Add 64mA of input current limit.   |

| [6]     | 0 = Add 0mA of input current limit. 1 = Add 128mA of input current limit.     |

| [7]     | 0 = Add 0mA of input current limit.<br>1 = Add 256mA of input current limit.  |

| [8]     | 0 = Add 0mA of input current limit.<br>1 = Add 512mA of input current limit.  |

| [9]     | 0 = Add 0mA of input current limit. 1 = Add 1024mA of input current limit.    |

| [10]    | 0 = Add 0mA of input current limit.<br>1 = Add 2048mA of input current limit. |

| [11]    | 0 = Add 0mA of input current limit.<br>1 = Add 4096mA of input current limit. |

| [12]    | 0 = Add 0mA of input current limit.<br>1 = Add 8192mA of input current limit. |

| [13:15] | Not used                                                                      |

| Maximum | [13:3] = 101111110000: 12160mA                                                |

## 6.2 Setting Output Current Limit

To set the output current limit, write the 16-bit Output Current Limit register (0x14) using the Write-word protocol shown in Figure 20.

The RAA489300 limits the output current based on the differential voltage across the CSOP and CSON pins. The gain of the output current feedback signal can be set by Control1 Bit[7]. With the recommended current sense resistor value Rs2 = 5 m $\Omega$ , the LSB of the Output Current Limit register according to Control1 Bit[7] is:

- Control1 Bit[7] = 0 (default): LSB of the Output Current Limit register = 8mA

- Control1 Bit[7] = 1: LSB of the Output Current Limit register = 16mA

The Output Current Limit register accepts any value, but only the valid bits are written to the register. The maximum output current limit, with Rs2 =  $5m\Omega$ , is clamped at 12156mA for Control Bit[7] = 0 or 24311mA for Control Bit[7] = 1.

After POR, the Output Current Limit register is reset to 0x00BC (1.5A). The Output Current Limit register can be read back to verify its value.

Table 4 and Table 5 show the data format of the output current limit, with Rs2 =5m $\Omega$ , when Control1 Bit[7] = 0 and 1, respectively.

Table 4. Output Current Limit Register 0x14 (11-bit, 8mA Step,  $5m\Omega$  Sense Resistor, Control1 Bit[7] = 0)

| Bit     | Description                                                                  |  |  |

|---------|------------------------------------------------------------------------------|--|--|

| [2:0]   | Not used                                                                     |  |  |

| [3]     | 0 = Add 0mA of output current limit. 1 = Add 8mA of output current limit.    |  |  |

| [4]     | 0 = Add 0mA of output current limit. 1 = Add 16mA of output current limit.   |  |  |

| [5]     | 0 = Add 0mA of output current limit. 1 = Add 32mA of output current limit.   |  |  |

| [6]     | 0 = Add 0mA of output current limit. 1 = Add 64mA of output current limit.   |  |  |

| [7]     | 0 = Add 0mA of output current limit. 1 = Add 128mA of output current limit.  |  |  |

| [8]     | 0 = Add 0mA of output current limit. 1 = Add 256mA of charge current limit.  |  |  |

| [9]     | 0 = Add 0mA of output current limit. 1 = Add 512mA of output current limit.  |  |  |

| [10]    | 0 = Add 0mA of output current limit. 1 = Add 1024mA of output current limit. |  |  |

| [11]    | 0 = Add 0mA of output current limit. 1 = Add 2048mA of output current limit. |  |  |

| [12]    | 0 = Add 0mA of output current limit. 1 = Add 4096mA of output current limit. |  |  |

| [13]    | 0 = Add 0mA of output current limit. 1 = Add 8192mA of output current limit. |  |  |

| [14:15] | Not used                                                                     |  |  |

| Maximum | [13:3] = 101111110000: 12156mA                                               |  |  |

Table 5. Output Current Limit Register 0x14 (11-bit, 6mA Step, 5mΩ Sense Resistor, Control1 Bit[7] = 1)

| Bit     | Description                                                                      |

|---------|----------------------------------------------------------------------------------|

| [2:0]   | Not used                                                                         |

| [3]     | 0 = Add 0mA of output current limit. 1 = Add 16mA of output current limit.       |

| [4]     | 0 = Add 0mA of output current limit.<br>1 = Add 32mA of output current limit.    |

| [5]     | 0 = Add 0mA of output current limit.<br>1 = Add 64mA of output current limit.    |

| [6]     | 0 = Add 0mA of output current limit.<br>1 = Add 128mA of output current limit.   |

| [7]     | 0 = Add 0mA of output current limit.<br>1 = Add 256mA of output current limit.   |

| [8]     | 0 = Add 0mA of output current limit.<br>1 = Add 512mA of output current limit.   |

| [9]     | 0 = Add 0mA of output current limit.<br>1 = Add 1024mA of output current limit.  |

| [10]    | 0 = Add 0mA of output current limit.<br>1 = Add 2048mA of output current limit.  |

| [11]    | 0 = Add 0mA of output current limit.<br>1 = Add 4096mA of output current limit.  |

| [12]    | 0 = Add 0mA of output current limit.<br>1 = Add 8192mA of output current limit.  |

| [13]    | 0 = Add 0mA of output current limit.<br>1 = Add 16384mA of output current limit. |

| [14:15] | Not used                                                                         |

| Maximum | [13:3] = 101111110000: 24320mA                                                   |

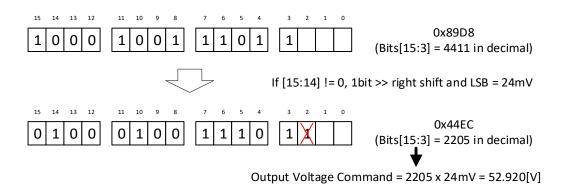

### 6.3 Setting Output Voltage

To set the regulated output voltage, write a 16-bit value to the Output Voltage register (0x15) using the Write-word protocol shown in Figure 20. Thirteen bits, [15:3], are allocated for the Output Voltage register. The RAA489300 supports Programmable Power Supply (PPS) and Adjustable Voltage Supply (AVS) modes. The RAA489300 can be configured to regulate the output voltage in PPS mode or AVS mode based on Bits[15:14] of the Output Voltage register. If those bits are 0, PPS mode is engaged and, otherwise, AVS mode is engaged. When supporting PPS mode, 11 bits are used and the LSB is 12mV. When AVS is supported, 12 bits are used and the LSB is 24mV. For example, when a user writes 0x89D8 (4411 in decimal) to the Output Voltage register, the Output Voltage register value is expressed as follows and AVS is supported:

However, when a user writes 0x1978 (815 in decimal) to the Output Voltage register, the Output Voltage register value is expressed as follows and PPS is supported:

RAA489300 can apply the slew rate to the output voltage DAC reference by setting Control3 Bit[14]. When Control3 Bit[14] is enabled, the slew rate is limited to 3mV/μs or 0.75mV/μs, as selected according to the Control3 Bit[13] value (see Table 14).

Table 6 and Table 7 show the data format of the Output Voltage register in PPS mode and AVS mode, respectively.

Table 6. Output Voltage Command Register 0x15 in PPS mode (13-bit, 12mV Step) - Bits[15:14] = 0

| Bit     | Description                                                          |

|---------|----------------------------------------------------------------------|

| [2:0]   | Not used                                                             |

| [3]     | 0 = Add 0mV of output voltage.<br>1 = Add 12mV of output voltage.    |

| [4]     | 0 = Add 0mV of output voltage.<br>1 = Add 24mV of output voltage.    |

| [5]     | 0 = Add 0mV of output voltage.<br>1 = Add 48mV of output voltage.    |

| [6]     | 0 = Add 0mV of output voltage.<br>1 = Add 96mV of output voltage.    |

| [7]     | 0 = Add 0mV of output voltage.<br>1 = Add 192mV of output voltage.   |

| [8]     | 0 = Add 0mV of output voltage.<br>1 = Add 384mV of output voltage.   |

| [9]     | 0 = Add 0mV of output voltage.<br>1 = Add 768mV of output voltage.   |

| [10]    | 0 = Add 0mV of output voltage.<br>1 = Add 1536mV of output voltage.  |

| [11]    | 0 = Add 0mV of output voltage.<br>1 = Add 3072mV of output voltage.  |

| [12]    | 0 = Add 0mV of output voltage.<br>1 = Add 6144mV of output voltage.  |

| [13]    | 0 = Add 0mV of output voltage.<br>1 = Add 12288mV of output voltage. |

| [14]    | 0 = Add 0mV of output voltage.                                       |

| [15]    | 0 = Add 0mV of output voltage.                                       |

| Maximum | [15:3] = 0011111111111: 24564mV                                      |

Table 7. Output Voltage Command Register 0x15 in AVS mode (13-Bit, 24mV Step) – Bits[15:14] = nonzero

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [2:0]   | Not used                                                             |  |

| [3]     | 0 = Add 0mV of output voltage. (no impact)                           |  |

| [4]     | 0 = Add 0mV of output voltage.<br>1 = Add 24mV of output voltage.    |  |

| [5]     | 0 = Add 0mV of output voltage.<br>1 = Add 48mV of output voltage.    |  |

| [6]     | 0 = Add 0mV of output voltage.<br>1 = Add 96mV of output voltage.    |  |

| [7]     | 0 = Add 0mV of output voltage.<br>1 = Add 192mV of output voltage.   |  |

| [8]     | 0 = Add 0mV of output voltage.<br>1 = Add 384mV of output voltage.   |  |

| [9]     | 0 = Add 0mV of output voltage.<br>1 = Add 768mV of output voltage.   |  |

| [10]    | 0 = Add 0mV of output voltage.<br>1 = Add 1536mV of output voltage.  |  |

| [11]    | 0 = Add 0mV of output voltage.<br>1 = Add 3072mV of output voltage.  |  |

| [12]    | 0 = Add 0mV of output voltage.<br>1 = Add 6144mV of output voltage.  |  |

| [13]    | 0 = Add 0mV of output voltage.<br>1 = Add 12288mV of output voltage. |  |

| [14]    | 0 = Add 0mV of output voltage.<br>1 = Add 24576mV of output voltage. |  |

| [15]    | 0 = Add 0mV of output voltage.<br>1 = Add 49152mV of output voltage. |  |

| Maximum | [15:3] = 1000111100000: 54912mV                                      |  |

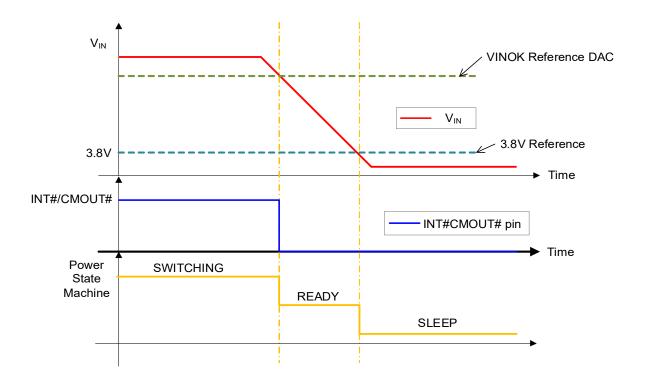

## 6.4 Setting VINOK Reference

RAA489300 starts switching when the input voltage is higher than the voltage setting of the VINOK Reference register. To set the VINOK reference, write a 16-bit value to the VINOK Reference register (0x40) using the Write-word protocol shown in Figure 20.

Table 8. VINOK Reference Register 0x40 (8-bit, 257.28mV Step)

| Bit     | Description                                                               |

|---------|---------------------------------------------------------------------------|

| [7:0]   | Not used                                                                  |

| [8]     | 0 = Add 0mV of VINOK reference.<br>1 = Add 257.28mV of VINOK reference.   |

| [9]     | 0 = Add 0mV of VINOK reference.<br>1 = Add 514.56mV of VINOK reference.   |

| [10]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 1029.12mV of VINOK reference.  |

| [11]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 2058.24mV of VINOK reference.  |

| [12]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 4116.48mV of VINOK reference.  |

| [13]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 8232.96mV of VINOK reference.  |

| [14]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 16465.92mV of VINOK reference. |

| [15]    | 0 = Add 0mV of VINOK reference.<br>1 = Add 32931.84mV of VINOK reference. |

| Maximum | [15:8] = 10110100: 46310.4 mV                                             |

## 6.5 Setting Minimum Input Voltage

The Minimum Input Voltage register (0x4B) contains an SMBus readable and writable minimum input voltage. The default is 3.8592V. This register accepts any value, but only the valid register bits are written. The maximum value is clamped at 46.3104V.

Table 9. Minimum Input Voltage Register 0x4B (11-bit, 257.29mV Step)

| Bit     | Description                                                                           |  |

|---------|---------------------------------------------------------------------------------------|--|

| [7:0]   | Not used                                                                              |  |

| [8]     | 0 = Add 0mV of minimum input voltage.<br>1 = Add 257.28mV of minimum input voltage.   |  |

| [9]     | 0 = Add 0mv of minimum input voltage. 1 = Add 514.56mV of minimum input voltage.      |  |

| [10]    | 0 = Add 0mV of minimum input voltage.<br>1 = Add 1029.12mV of minimum input voltage.  |  |

| [11]    | 0 = Add 0mV of minimum input voltage.<br>1 = Add 2058.24mV of minimum input voltage.  |  |

| [12]    | 0 = Add 0mV of minimum input voltage. 1 = Add 4116.48mV of minimum input voltage.     |  |

| [13]    | 0 = Add 0mV of minimum input voltage.<br>1 = Add 8232.96mV of minimum input voltage.  |  |

| [14]    | 0 = Add 0mV of minimum input voltage.<br>1 = Add 16465.92mV of minimum input voltage. |  |

| [15]    | 0 = Add 0mV of minimum input voltage.<br>1 = Add 32931.84mV of minimum input voltage. |  |

| Maximum | [15:8] = 10110100: 46310.4mV                                                          |  |

## 6.6 Setting Reverse PTM Voltage

RAA489300 provides Reverse Pass-Through Mode (PTM). To switch to Reverse PTM, the CSOP voltage must be matched with the reverse PTM voltage reference. To set the reverse PTM voltage reference, write a 16-bit value to the Reverse PTM Voltage register (0x49) using the Write-word protocol shown in Figure 20.

Table 10. Reverse PTM Voltage Register 0x49 (12-bit, 12mA Step)

| Bit     | Description                                                                    |  |

|---------|--------------------------------------------------------------------------------|--|

| [3:0]   | Not used                                                                       |  |

| [4]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 12mV of reverse PTM voltage.    |  |

| [5]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 24mV of reverse PTM voltage.    |  |

| [6]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 48mV of reverse PTM voltage.    |  |

| [7]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 96mV of reverse PTM voltage.    |  |

| [8]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 192mV of reverse PTM voltage.   |  |

| [9]     | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 384mV of reverse PTM voltage.   |  |

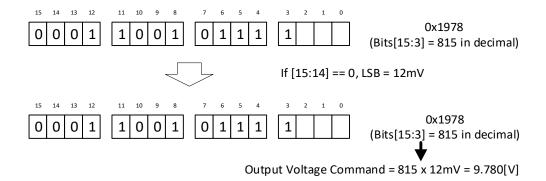

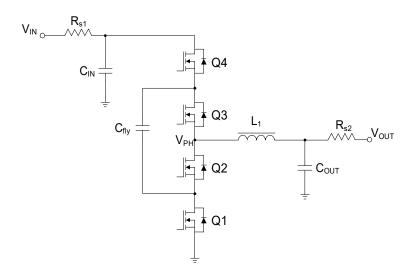

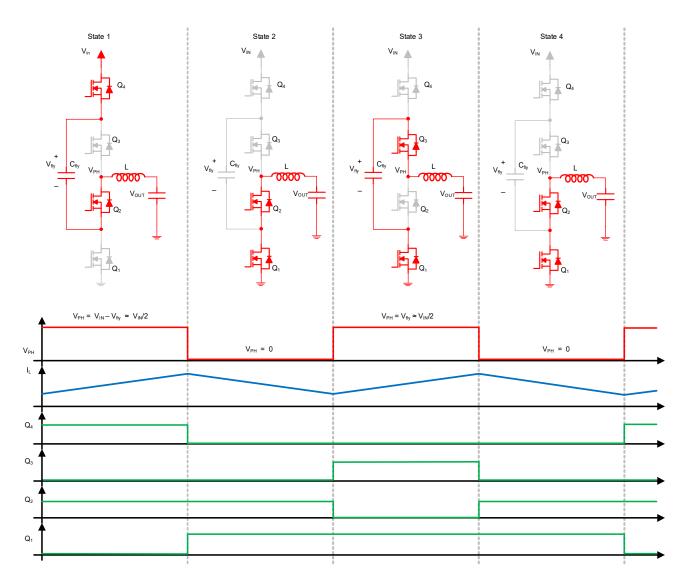

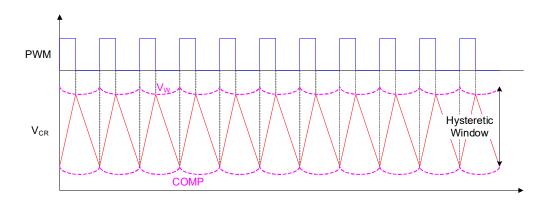

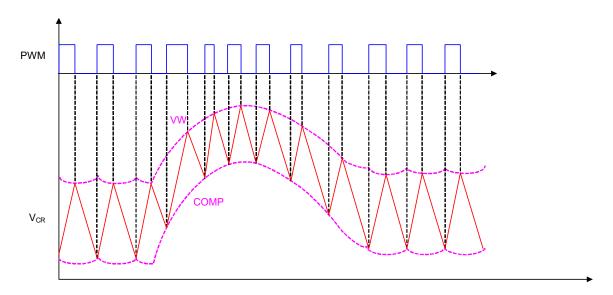

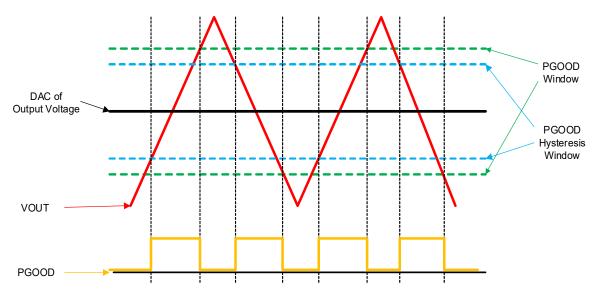

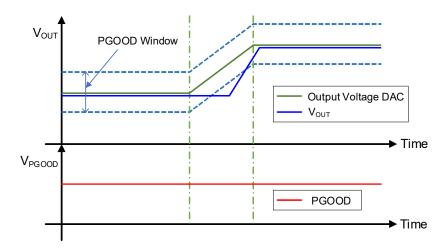

| [10]    | 0 = Add 0mV of reverse PTM voltage.<br>1 = Add 768mV of reverse PTM voltage.   |  |