### RC32312, RC32308

FemtoClock™ 3 Jitter Attenuator and Multi-Frequency Clock Synthesizer

### **Description**

The RC32312/RC32308 is an ultra-low phase noise jitter attenuator, multi-frequency synthesizer, synchronous Ethernet synchronizer, and digitally controlled oscillator (DCO). This flexible, low-power device outputs clocks with 25fs RMS jitter supporting 112Gbps and 224Gbps SerDes.

### **Applications**

- Jitter attenuation for:

- · 112Gbps and 224Gbps SerDes

- 100 / 200 / 400 / 800 / 1600 Gbps Ethernet PHYs

- Synchronous Ethernet timing cards and line cards

- Switches and routers

- Medical imaging

- Test and measurement

#### **Features**

- Jitter 25fs RMS, 12kHz to 20MHz with 4MHz HPF

- Output frequency range:

- 4kHz to 1GHz for differential outputs

- · 4kHz to 250MHz for single-ended outputs

- Up to 12 HCSL (AC-LVPECL) or LVDS outputs with independent integer dividers; differential outputs can be configured as two single-ended outputs

- Up to four clock inputs that can each be configured as differential or as two single-ended inputs

- Input frequency range:

- 1kHz to 1GHz for differential inputs

- · 1kHz to 250MHz for single-ended inputs

- Compliant to ITU-T G.8262 and G.8262.1

- · Hitless reference switching, manual or automatic

- DPLL input-to-output phase variation ≤ 500ps

- DCO frequency resolution < 10<sup>-13</sup>

- Factory programmable internal OTP

- RC32312

- · 4 inputs and 12 outputs

- 9 × 9 mm, 64-VFQFPN

- RC32308

- · 3 inputs and 8 outputs

- 7 × 7 mm. 48-VFQFPN

- Operating voltage: 1.8V

- Serial ports support 1.8V or 3.3V

- Operating temperature:

- · -40°C to 85°C ambient

- -40°C to 105°C board

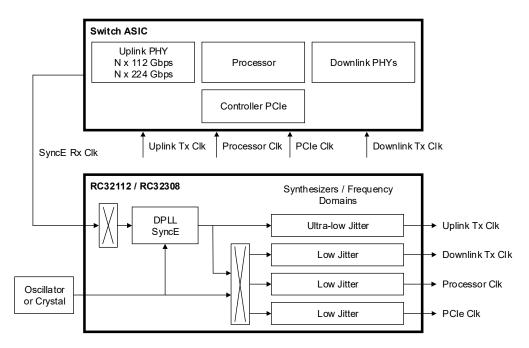

Figure 1. Typical Wireline Infrastructure Use Case

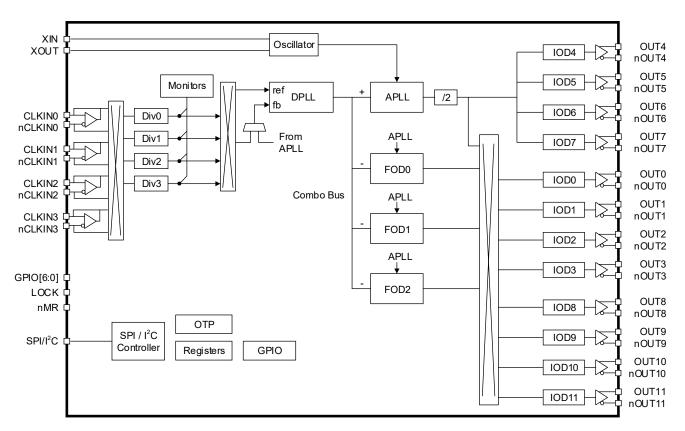

Figure 2. RC32312 Block Diagram

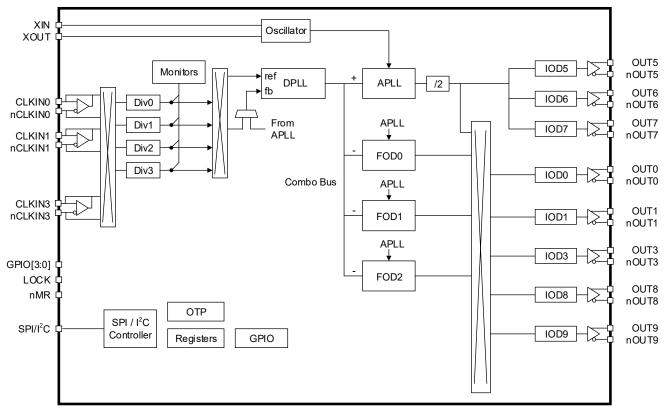

Figure 3. RC32308 Block Diagram

# **Contents**

| 1. | Pin Ir     | formation                                                           | . 7      |

|----|------------|---------------------------------------------------------------------|----------|

|    | 1.1        | Pin Assignments                                                     | . 7      |

|    | 1.2        | Pin Descriptions                                                    | . 7      |

| 2. | Spec       | ifications                                                          | 10       |

|    | 2.1        | Absolute Maximum Ratings                                            |          |

|    | 2.2        | Thermal Resistance                                                  |          |

|    | 2.3        | Recommended Operating Conditions                                    |          |

|    | 2.4        | APLL Phase Jitter                                                   |          |

|    | 2.5        | FOD Phase Jitter                                                    |          |

|    | 2.6        | Power Supply Noise Rejection                                        |          |

|    | 2.7        | Crystal Oscillator Input and APLL AC/DC Electrical Characteristics. |          |

|    | 2.8        | Recommended Crystal Characteristics                                 |          |

|    | 2.9        | Clock Input (CLKIN/nCLKIN) AC/DC Characteristics                    |          |

|    | 2.10       | Output Frequencies and Start-Up Time                                |          |

|    | 2.11       | Phase and Frequency Uncertainty                                     |          |

|    | 2.12       | Output-to-Output and Input-to-Output Skew.                          |          |

|    | 2.13       | LVCMOS Output AC/DC Characteristics                                 |          |

|    | 2.14       | LVDS Output AC/DC Characteristics                                   |          |

|    | 2.15       | HCSL Output AC/DC Characteristics                                   |          |

|    | 2.16       | Power Supply Current                                                |          |

|    | 2.17       | GPIO and Serial Port DC Electrical Characteristics.                 |          |

|    | 2.18       | CMOS GPIO and Serial Port Common Electrical Characteristics         |          |

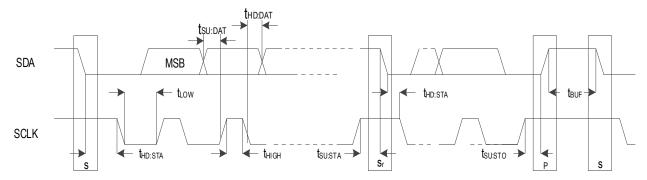

|    | 2.19       | I <sup>2</sup> C Bus Target Timing Diagram                          |          |

|    | 2.20       | I <sup>2</sup> C Bus Target Timing Characteristics                  |          |

|    | 2.21       | I <sup>2</sup> C Bus AC/DC Electrical Characteristics               |          |

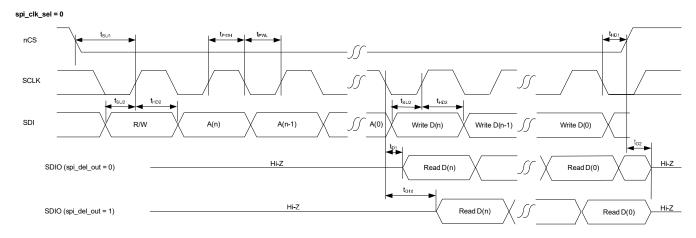

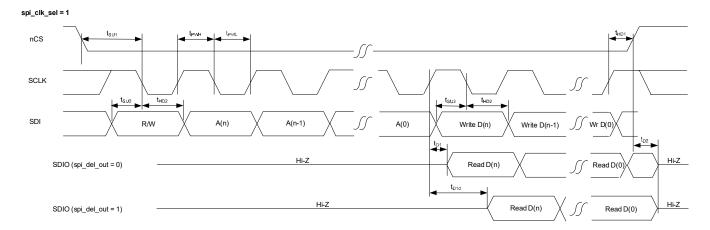

|    | 2.22       | SPI Target Timing Diagrams                                          |          |

|    |            | SPI Target Timing Characteristics                                   |          |

| 3. |            | tional Description                                                  |          |

| J. |            | •                                                                   |          |

|    | 3.1<br>3.2 | Overview                                                            |          |

|    |            | ·                                                                   |          |

|    | 3.3        | Analog PLL                                                          |          |

|    | 3.4        | Integer Output Dividers.                                            |          |

|    | 3.5        | Fractional Output Dividers                                          |          |

|    | 3.6        | Divider Synchronization                                             |          |

|    | 3.7        | Digital PLL                                                         |          |

|    |            |                                                                     |          |

|    |            | 3.7.2 DPLL Acquire State                                            |          |

|    |            | 3.7.3 DPLL Normal State                                             |          |

|    |            | 3.7.4 DPLL Holdover State                                           |          |

|    | 2.0        | 3.7.5 DPLL Hitless Switch State                                     |          |

|    | 3.8        | DPLL External Feedback                                              |          |

|    | 3.9        | DPLL Reference Switching.                                           |          |

|    |            | 3.9.1 Hitless Reference Switching                                   |          |

|    | 2.40       | 3.9.2 Aligned Reference Switching                                   |          |

|    | 3.10       | Clock Output Enable.                                                |          |

|    | 3.11       | Reference Monitors                                                  |          |

|    | 3.12       | Status and Control                                                  |          |

| 4. | Appli      | cations Information                                                 |          |

|    |            |                                                                     |          |

|    | 4.1        | Power Considerations                                                |          |

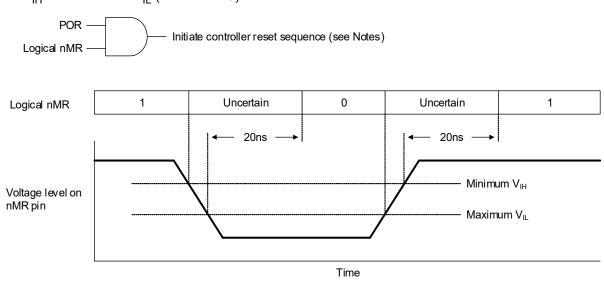

|    | 4.2        | Power-On Reset and Reset Controller                                 | 25       |

|    |            |                                                                     | 25<br>26 |

# RC32312, RC32308 Datasheet

|    |      | 4.3.2     | LVCMOS Control Pins                       | 26             |

|----|------|-----------|-------------------------------------------|----------------|

|    |      | 4.3.2     | LVCMOS Output Pins                        |                |

|    |      |           | •                                         |                |

|    |      | 4.3.4     | Differential Output Pins                  | 26             |

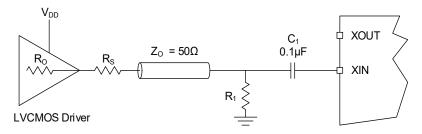

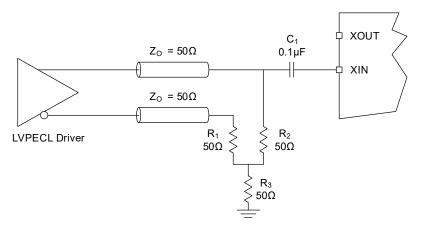

|    | 4.4  | Overdr    | riving the Crystal Interface              | 26             |

|    | 4.5  | Differe   | ential Output Termination                 | 27             |

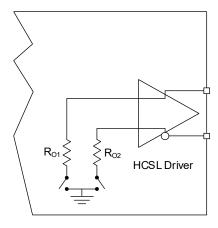

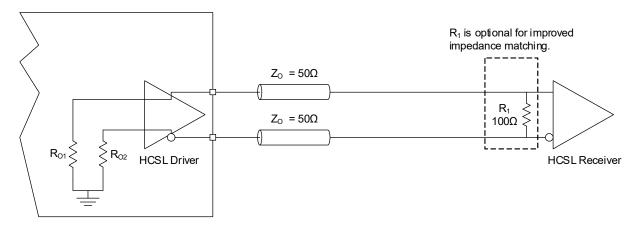

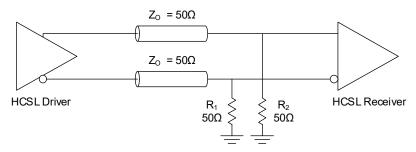

|    |      | 4.5.1     | Direct-Coupled HCSL Terminations          | 27             |

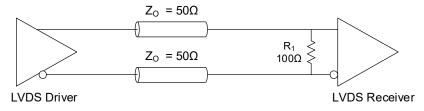

|    |      | 4.5.2     | Direct-Coupled LVDS Termination           | 28             |

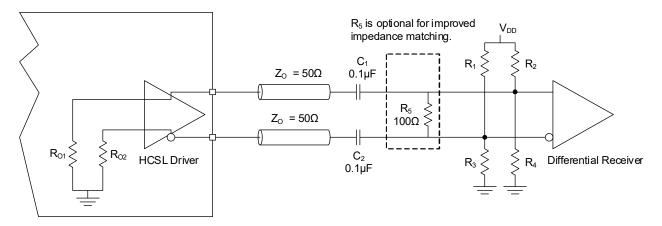

|    |      | 4.5.3     | AC-Coupled Differential Termination       | 29             |

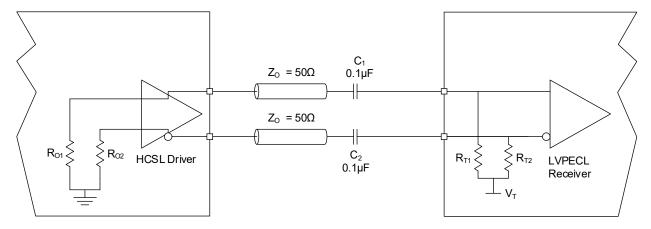

|    |      | 4.5.4     | AC-Coupled LVPECL (AC-LVPECL) Termination | 29             |

| 5. | Pack | age Out   | tline Drawings                            | 30             |

| 6. | Devi | ce ID Re  | egister                                   | 30             |

| 7. | Mark | ing Diaເ  | gram                                      | 30             |

| 8. | Orde | ring Info | -<br>formation                            | 30             |

| 9. | Revi | sion His  | story                                     | 3 <sup>4</sup> |

# **Figures**

| Figure 1. Typical Wireline Infrastructure Use Case                                                   | 1  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 2. RC32312 Block Diagram                                                                      | 2  |

| Figure 3. RC32308 Block Diagram                                                                      | 2  |

| Figure 4. I <sup>2</sup> C Bus Target Timing Diagram                                                 | 19 |

| Figure 5. SPI Target Timing Diagrams                                                                 |    |

| Figure 6. Controller Reset Sequence Initiation                                                       | 25 |

| Figure 7. LVCMOS Driver to Crystal Input Interface                                                   | 26 |

| Figure 8. LVPECL Driver to Crystal Input Interface                                                   | 27 |

| Figure 9. Internal Termination Resistors for Differential Drivers                                    | 27 |

| Figure 10. HCSL Internal Termination                                                                 | 28 |

| Figure 11. HCSL External Termination                                                                 | 28 |

| Figure 12. LVDS Termination                                                                          | 28 |

| Figure 13. AC-Coupled Differential Termination                                                       | 29 |

| Figure 14. AC-LVPECL Termination for LVPECL Receiver with Internal Termination Resistors and Biasing | 29 |

# **Tables**

| Table 1. Pin Descriptions                                              | . 7  |

|------------------------------------------------------------------------|------|

| Table 2. Input Characteristics                                         | . 9  |

| Table 3. Absolute Maximum Ratings                                      | . 10 |

| Table 4. Thermal Resistance                                            | . 10 |

| Table 5. Recommended Operating Conditions                              | . 11 |

| Table 6. APLL Phase Jitter                                             | . 11 |

| Table 7. FOD Phase Jitter                                              | . 11 |

| Table 8. Power Supply Noise Rejection                                  | . 12 |

| Table 9. Crystal Oscillator Input and Analog PLL AC/DC Characteristics | . 12 |

| Table 10. Recommended Crystal Characteristics                          | . 13 |

| Table 11. Clock Input (CLKIN/nCLKIN) AC/DC Characteristics             | . 13 |

| Table 12. Output Frequencies and Start-Up Time                         | . 14 |

| Table 13. Phase and Frequency Uncertainty                              | . 14 |

| Table 14. Output-to-Output and Input-to-Output Skew                    | . 15 |

| Table 15. LVCMOS Output AC/DC Characteristics                          | . 15 |

| Table 16. LVDS Output AC/DC Characteristics                            | . 16 |

| Table 17. HCSL Output AC/DC Characteristics                            |      |

| Table 18. Power Supply Current                                         |      |

| Table 19. GPIO and Serial Port DC Electrical Characteristics           |      |

| Table 20. CMOS GPIO Common Electrical Characteristics                  |      |

| Table 21. I <sup>2</sup> C Bus Target Timing Characteristics           |      |

| Table 22. I <sup>2</sup> C Bus AC/DC Electrical Characteristics        |      |

| Table 23. SPI Target Timing Characteristics                            |      |

| Table 24. Recommended Free-Running Freguency Accuracy by Application   | . 22 |

### 1. Pin Information

# 1.1 Pin Assignments

(9 × 9 mm, 0.5mm lead pitch) nOUT0 nOUT2 OUT0 noUT1 OUT1 OUT2 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 V<sub>DD04</sub>  $V_{DD\_VCO}$ 1 47 OUT4 LOCK 2 46 nOUT4 V<sub>DDXO\_DCD</sub> 3 45 GPI06 XIN 4 44 V<sub>DDO5</sub> XOUT 5 43 OUT5 nCS A0 6 42 nOUT5 SDO A1 7 41 GPIO1 V<sub>DD D33\_SERIAL</sub> 8 RC32312 (V<sub>SS</sub> ePAD) 40 GPIO2 9 V<sub>DDD33 DIA</sub> 10 39 nOUT6 V<sub>DD</sub> CLK CLKIN2 11 38 OUT6 37 nCLKIN2 12  $V_{DDO6}$ 36 GPIO3 CLKIN1 13 35 nOUT7 nCLKIN1 14 CLKIN0 15 34 OUT7 nCLKIN0 16 33 V<sub>DDO7</sub>

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

OUT10 OUT11 nOUT 10 nouT9 OUT9 nOUT8 OUT8 nCLKIN3 V<sub>DD009</sub>

Top View

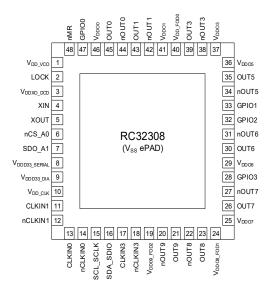

Top View (7 × 7 mm, 0.5mm lead pitch)

## 1.2 Pin Descriptions

**Table 1. Pin Descriptions**

| Pin Name | Pin N   | umber   | Time | Description                                                                                                                                     |

|----------|---------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | RC32312 | RC32308 | Туре | Description                                                                                                                                     |

| XIN      | 4       | 4       | 1    | Crystal oscillator / xCXO input.                                                                                                                |

| XOUT     | 5       | 5       | 0    | Crystal oscillator output.                                                                                                                      |

| CLKIN0   | 15      | 13      | 1    |                                                                                                                                                 |

| nCLKIN0  | 16      | 14      | 1    |                                                                                                                                                 |

| CLKIN1   | 13      | 11      | 1    |                                                                                                                                                 |

| nCLKIN1  | 14      | 12      | 1    | Clock reference input, differential pair / single-ended.                                                                                        |

| CLKIN2   | 11      | -       | 1    | <ul> <li>CLKINx indicates the positive pin of a differential pair.</li> <li>nCLKINx indicates the negative pin of differential pair.</li> </ul> |

| nCLKIN2  | 12      | -       | 1    |                                                                                                                                                 |

| CLKIN3   | 19      | 17      | 1    |                                                                                                                                                 |

| nCLKIN3  | 20      | 18      | 1    |                                                                                                                                                 |

| OUT0     | 60      | 45      | 0    |                                                                                                                                                 |

| nOUT0    | 59      | 44      | 0    |                                                                                                                                                 |

| OUT1     | 58      | 43      | 0    |                                                                                                                                                 |

| nOUT1    | 57      | 42      | 0    | Clock output, differential pair / single ended. LVDS, HCSL, or LVCMOS.                                                                          |

| OUT2     | 54      | -       | 0    | OUTx indicates the positive pin of a differential pair.  nOUTx indicates the negative pin of a differential pair.                               |

| nOUT2    | 53      | -       | 0    |                                                                                                                                                 |

| OUT3     | 52      | 39      | 0    |                                                                                                                                                 |

| nOUT3    | 51      | 38      | 0    |                                                                                                                                                 |

Table 1. Pin Descriptions (Cont.)

| Pin Name                  | Pin N   | umber   | Tuna  | Description                                                                                                                                                                      |  |  |  |

|---------------------------|---------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                  | RC32312 | RC32308 | Туре  | Description                                                                                                                                                                      |  |  |  |

| OUT4                      | 47      | -       | 0     |                                                                                                                                                                                  |  |  |  |

| nOUT4                     | 46      | -       | 0     |                                                                                                                                                                                  |  |  |  |

| OUT5                      | 43      | 35      | 0     |                                                                                                                                                                                  |  |  |  |

| nOUT5                     | 42      | 34      | 0     | Clock output, differential pair / single ended. LVDS, HCSL, or LVCMO OUTx indicates the positive pin of a differential pair.                                                     |  |  |  |

| OUT6                      | 38      | 30      | 0     | nOUTx indicates the positive pin of a differential pair.                                                                                                                         |  |  |  |

| nOUT6                     | 39      | 31      | 0     |                                                                                                                                                                                  |  |  |  |

| OUT7                      | 34      | 26      | 0     |                                                                                                                                                                                  |  |  |  |

| nOUT7                     | 35      | 27      | 0     |                                                                                                                                                                                  |  |  |  |

| OUT8                      | 31      | 23      | 0     |                                                                                                                                                                                  |  |  |  |

| nOUT8                     | 30      | 22      | 0     |                                                                                                                                                                                  |  |  |  |

| OUT9                      | 29      | 21      | 0     | Clock output, differential pair / single ended TVDS, HCSL or TVC                                                                                                                 |  |  |  |

| nOUT9                     | 28      | 20      | 0     | Clock output, differential pair / single ended. LVDS, HCSL, or LVCMO:  OUTx indicates the positive pin of a differential pair.                                                   |  |  |  |

| OUT10                     | 25      | -       | 0     | nOUTx indicates the positive pin of a differential pair.                                                                                                                         |  |  |  |

| nOUT10                    | 24      | -       | 0     |                                                                                                                                                                                  |  |  |  |

| OUT11                     | 23      | -       | 0     |                                                                                                                                                                                  |  |  |  |

| nOUT11                    | 22      | -       | 0     |                                                                                                                                                                                  |  |  |  |

| nMR                       | 64      | 48      | I     | Active-low controller (master) reset. The V <sub>DDO0</sub> pin must be powered t ensure proper operation.                                                                       |  |  |  |

| nCS_A0                    | 6       | 6       | I     | I2C mode: address bit 0. SPI mode: active-low chip select.                                                                                                                       |  |  |  |

| SCL_SCLK                  | 17      | 15      | I/O   | I <sup>2</sup> C Mode: I <sup>2</sup> C interface bi-directional clock. SPI Mode: serial clock.                                                                                  |  |  |  |

| SDA_SDIO                  | 18      | 16      | I/O   | I <sup>2</sup> C mode: I <sup>2</sup> C interface bi-directional serial data. SPI 3-wire mode: bi-directional serial data. SPI 4-wire mode: input serial data.                   |  |  |  |

| SDO_A1                    | 7       | 7       | I/O   | I <sup>2</sup> C mode: address bit 1. SPI 3-wire mode: unused. SPI 4-wire mode: output serial data.                                                                              |  |  |  |

| GPIO0                     | 62      | 47      | I/O   |                                                                                                                                                                                  |  |  |  |

| GPIO1                     | 41      | 33      | I/O   |                                                                                                                                                                                  |  |  |  |

| GPIO2                     | 40      | 32      | I/O   |                                                                                                                                                                                  |  |  |  |

| GPIO3                     | 36      | 28      | I/O   | General purpose input/output.                                                                                                                                                    |  |  |  |

| GPIO4                     | 63      | -       | I/O   |                                                                                                                                                                                  |  |  |  |

| GPIO5                     | 49      | -       | I/O   |                                                                                                                                                                                  |  |  |  |

| GPIO6                     | 45      | -       | I/O   |                                                                                                                                                                                  |  |  |  |

| LOCK                      | 2       | 2       | 0     | Lock indicator. This pin is GPIO8 with gpio_func default = 0x1B (APLI lock).                                                                                                     |  |  |  |

| V <sub>DD_CLK</sub>       | 10      | 10      | Power | Power supply for CLKINx buffers, dividers, muxes, and the TDC. 1.8\ is supported.                                                                                                |  |  |  |

| V <sub>DD_VCO</sub>       | 1       | 1       | Power | Power supply for the VCO. 1.8V is supported.                                                                                                                                     |  |  |  |

| V <sub>DDD33_DIA</sub>    | 9       | 9       | Power | Power supply for digital core, digital in FODs, and digital in the APLL. 1.8V and 3.3V are supported.  1.8V is recommended for lowest power consumption during normal operation. |  |  |  |

| V <sub>DDD33_SERIAL</sub> | 8       | 8       | Power | Power supply for serial port. 1.8V and 3.3V are supported.                                                                                                                       |  |  |  |

| V <sub>DDO0</sub>         | 61      | 46      | Power | Power supply for OUT0/nOUT0, IOD0, GPIO0, GPIO4, and nMR. 1.8 is supported.                                                                                                      |  |  |  |

| V <sub>DDO1_FOD0</sub>    | 56      | -       | Power | Power supply for OUT1/nOUT1, IOD1, and FOD0. 1.8V is supported.                                                                                                                  |  |  |  |

| V <sub>DDO1</sub>         | -       | 41      | Power | Power supply for OUT1/nOUT1 and IOD1. 1.8V is supported.                                                                                                                         |  |  |  |

| V <sub>DD_FOD0</sub>      | _       | 40      | Power | Power supply for FOD0. 1.8V is supported.                                                                                                                                        |  |  |  |

Table 1. Pin Descriptions (Cont.)

| Pin Name                | Pin Number |         | Time                                                             | Description                                                                                                                                                                          |  |  |

|-------------------------|------------|---------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                | RC32312    | RC32308 | Туре                                                             | Description                                                                                                                                                                          |  |  |

| $V_{DDO2}$              | 55         | -       | Power                                                            | Power supply for OUT2/nOUT2 and IOD2. 1.8V is supported.                                                                                                                             |  |  |

| V <sub>DDO3</sub>       |            |         | Power supply for OUT3/nOUT3, IOD3, and GPIO5. 1.8V is supported. |                                                                                                                                                                                      |  |  |

| V <sub>DDO4</sub>       | 48         | -       | Power                                                            | Power supply for OUT4/nOUT4, IOD4, and GPIO6. 1.8V is supported.                                                                                                                     |  |  |

| V <sub>DDO5</sub>       | 44         | 36      | Power                                                            | Power supply for OUT5/nOUT5, IOD5 and GPIO1. 1.8V is supported.                                                                                                                      |  |  |

| V <sub>DDO6</sub>       | 37         | 29      | Power                                                            | Power supply for OUT6/nOUT6, IOD6, and GPIO2. 1.8V is supported.                                                                                                                     |  |  |

| V <sub>DDO7</sub>       | 33         | 25      | Power                                                            | Power supply for OUT7/nOUT7, IOD7, and GPIO3. 1.8V is supported.                                                                                                                     |  |  |

| V <sub>DDO8_FOD1</sub>  | 32         | 24      | Power                                                            | Power supply for OUT8/nOUT8, IOD8, and FOD1. 1.8V is supported.                                                                                                                      |  |  |

| V <sub>DDO9</sub>       | 27         | -       | Power                                                            | Power supply for OUT9/nOUT9 and IOD9. 1.8V is supported.                                                                                                                             |  |  |

| V <sub>DDO9_</sub> FOD2 | -          | 19      | Power                                                            | Power supply for OUT9/nOUT9, IOD9, FOD2, and FOD calibration. For the RC32308, the V <sub>DDO9_FOD2</sub> pin must be powered if "any" of the FODs are used.  1.8V is supported.     |  |  |

| V <sub>DDO10_FOD2</sub> | 26         | -       | Power                                                            | Power supply for OUT10/nOUT10, IOD10, FOD2, and FOD calibration. For the RC32312, the V <sub>DDO10_FOD2</sub> pin must be powered if "any" of the FODs are used.  1.8V is supported. |  |  |

| V <sub>DDO11</sub>      | 21         | -       | Power                                                            | Power supply for OUT11/nOUT11 and IOD11. 1.8V is supported.                                                                                                                          |  |  |

| V <sub>DDXO_DCD</sub>   | 3          | 3       | Power                                                            | Power supply for the analog reference and the LOCK output.  1.8V is supported.                                                                                                       |  |  |

| V <sub>SS</sub>         | ePad       | ePad    | Power                                                            | Device ePad. Must be connected to ground.                                                                                                                                            |  |  |

**Table 2. Input Characteristics**

| Symbol                | Pa                       | Condition                                            | Minimum | Typical | Maximum | Unit |    |

|-----------------------|--------------------------|------------------------------------------------------|---------|---------|---------|------|----|

|                       |                          | CLKIN/nCLKIN                                         | -       | -       | 3       | -    |    |

| C <sub>IN</sub>       | Input capacitance        | nMR, nCS_A0, SDO_A1,<br>GPIOx, SCL_SCLK,<br>SDA_SDIO | -       | -       | 4       | -    | pF |

|                       |                          | nMR                                                  | -       | -       | 98      | -    |    |

| R <sub>PULLUP</sub>   | Input pull-up resistor   | nCS_A0, SDO_A1,<br>GPIOx                             | -       | -       | 53      | -    | kΩ |

| R <sub>PULLDOWN</sub> | Input pull-down resistor | nCS_A0, SDO_A1,<br>GPIOx                             | -       | -       | 53      | -    | kΩ |

# 2. Specifications

# 2.1 Absolute Maximum Ratings

**Table 3. Absolute Maximum Ratings**

| Symbol            | Parameter                                                         | Condition                                                                                                                                       | Minimum            | Maximum                   | Unit |

|-------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|------|

| V <sub>DD33</sub> | Supply Voltage with Respect to Ground                             | V <sub>DDD33_Serial</sub> , V <sub>DDD33_DIA</sub>                                                                                              | -0.5               | 3.63                      | ٧    |

| V <sub>DD18</sub> | Supply Voltage with Respect to Ground                             | V <sub>DD_CLK</sub> , V <sub>DDXO_DCD</sub> , V <sub>DD_VCO</sub> ,<br>V <sub>DD05_FOD0</sub> , V <sub>DD06_FOD1</sub> , V <sub>DD09_FOD2</sub> | -0.5               | 1.89                      | V    |

|                   |                                                                   | XIN [1]                                                                                                                                         | -0.5               | 1.32                      |      |

| $V_{IN}$          |                                                                   | GPIOx used as inputs, nMR <sup>[2]</sup>                                                                                                        | -0.5               | V <sub>DDOx</sub> + 0.3   |      |

|                   | Input Voltage                                                     | CLKINX                                                                                                                                          | -0.5               | V <sub>DD_CLK</sub> + 0.3 | V    |

|                   |                                                                   | nCS_A0, SDO_A1, SCL_SCLK, SDA_SDIO                                                                                                              | -0.5               | 3.63                      |      |

|                   |                                                                   | GPIOx used as inputs, nMR                                                                                                                       | -                  | ±25                       |      |

| I <sub>IN</sub>   | Input Current                                                     | CLKINx                                                                                                                                          | -                  | ±50                       | mA   |

| ·IIV              |                                                                   | nCS_A0, SDO_A1, SCL_SCLK, SDA_SDIO                                                                                                              |                    | ±25                       |      |

|                   | Output Current - Continuous                                       | OUTx, nOUTx                                                                                                                                     | -                  | 30                        |      |

|                   |                                                                   | LOCK, SDO_A1, SCL_SCLK, SDA_SDIO                                                                                                                | -                  | 25                        | mA   |

|                   |                                                                   | GPIOx used as outputs                                                                                                                           | -                  | 25                        |      |

| I <sub>OUT</sub>  |                                                                   | OUTx, nOUTx                                                                                                                                     | -                  | 60                        |      |

|                   | Output Current - Surge                                            | LOCK, SDO_A1, SCL_SCLK, SDA_SDIO                                                                                                                | -                  | 50                        | mA   |

|                   |                                                                   | GPIOx used as outputs                                                                                                                           | ed as outputs - 50 |                           | †    |

| TJ                | Maximum Junction Temperature                                      | -                                                                                                                                               | -                  | 150                       | °C   |

| T <sub>S</sub>    | Storage Temperature                                               | Storage Temperature                                                                                                                             | -65                | 150                       | °C   |

| -                 | Human Body Model (Tested per JESD22-A114 (JS-001) Classification) | -                                                                                                                                               | -                  | 2000                      | ٧    |

| -                 | Charged Device Model (Tested per JESD22-C101 Classification)      | -                                                                                                                                               | -                  | 250                       | ٧    |

<sup>1.</sup> This limit only applies when XIN is overdriven by an external oscillator. No limit is implied when connected directly to a crystal.

# 2.2 Thermal Resistance

**Table 4. Thermal Resistance**

| Package | Symbol           | Conditions [1]             | Typical Value | Unit |

|---------|------------------|----------------------------|---------------|------|

|         | Θ <sub>JC</sub>  | Junction to case           | 17.5          |      |

| NDG48   | Θ <sub>JB</sub>  | Junction to base           | 1.0           | °C/W |

|         | Θ <sub>JA0</sub> | Junction to air, still air | 20.0          |      |

|         | Θ <sub>JC</sub>  | Junction to case           | 13.1          |      |

| NDG64   | Θ <sub>JB</sub>  | Junction to base           | 1.0           | °C/W |

|         | Θ <sub>JA0</sub> | Junction to air, still air | 20.0          |      |

<sup>1.</sup> ePad soldered to board.

<sup>2.</sup>  $V_{DDOx}$  refers to the supply powering the GPIO or nMR. For  $V_{DD}$  pin mapping, see Pin Assignments.

# 2.3 Recommended Operating Conditions

Table 5. Recommended Operating Conditions [1][2]

| Symbol           | Parameter                                                                | Condition                             | Minimum | Typical | Maximum | Unit |

|------------------|--------------------------------------------------------------------------|---------------------------------------|---------|---------|---------|------|

| TJ               | Maximum Junction Temperature                                             | -                                     | -       | -       | 125     | °C   |

| T <sub>A</sub>   | Ambient Operating Temperature                                            | -                                     | -40     | -       | 85      | °C   |

| V                | Supply Voltage with Respect to Ground                                    | V <sub>DD</sub> pins with 1.8V supply | 1.71    | 1.8     | 1.89    | V    |

| V <sub>DDx</sub> |                                                                          | V <sub>DD</sub> pins with 3.3V supply | 3.135   | 3.3     | 3.465   | V    |

| t <sub>PU</sub>  | Power up time for all V <sub>DD</sub> to reach minimum specified voltage | Power ramps must be monotonic         | -       | -       | 10      | ms   |

<sup>1.</sup> All electrical characteristics are specified over Recommended Operating Conditions unless noted otherwise.

#### 2.4 APLL Phase Jitter

Table 6. APLL Phase Jitter [1][2][3][4]

| Symbol               | Parameter                                                                                                                                      | Condition | Minimum | Typical | Maximum | Unit      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|---------|---------|-----------|

| t <sub>JIT</sub> (Φ) | Random Phase Jitter (12kHz to 20MHz), OUT[11:0] differential, APLL configured as synthesizer, XIN = 62.5MHz, VCO = 10.625GHz                   | 156.25MHz | -       | 51      | 60      | fs RMS    |

| JIT(4)               |                                                                                                                                                | 312.5MHz  | -       | 47      | 56      |           |

| t <sub>JIT</sub> (Φ) | Random Phase Jitter (12kHz to 20MHz), OUT[11:0] differential, APLL steered by DPLL, BW = 25Hz, CLKIN = 25MHz, XIN = 63MHz, VCO = 10.625GHz [5] | 156.25MHz | -       | 63      | 85      | fs RMS    |

| JII(4)               |                                                                                                                                                | 312.5MHz  | -       | 60      | 93      | 10 T (WIO |

<sup>1.</sup> The device will meet specifications after thermal equilibrium has been reached.

### 2.5 FOD Phase Jitter

Table 7. FOD Phase Jitter [1][2][3][4]

| Symbol               | Parameter                                                                                                                  | Condition | Minimum | Typical | Maximum | Unit     |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|---------|---------|---------|----------|

|                      |                                                                                                                            | 106.25MHz | -       | 100     | 165     |          |

|                      | Random Phase Jitter (12kHz to 20MHz),                                                                                      | 212.5MHz  | -       | 82      | 97      |          |

| t (Φ)                | OUT[3:0] and OUT[11:8] differential, APLL configured as a synthesizer, XIN = 60MHz, VCO = 10.86GHz                         | 425MHz    | -       | 75      | 101     | fs RMS   |

| ·JIT(Ψ)              |                                                                                                                            | 156.25MHz | -       | 100     | 165     | IS KIVIS |

|                      |                                                                                                                            | 312.5MHz  | -       | 79      | 115     |          |

|                      |                                                                                                                            | 625MHz    | -       | 68      | 97      |          |

|                      | Random Phase Jitter (12kHz to 20MHz), OUT[3:0] and OUT[11:8] differential, APLL steered by DPLL, BW = 25Hz, CLKIN = 25MHz, | 156.25MHz | -       | 89      | 105     |          |

| t <sub>JIT</sub> (Φ) |                                                                                                                            | 312.5MHz  | -       | 78      | 97      | fs RMS   |

|                      | FOD configured as synthesizer / DCO,<br>XIN = 60MHz, VCO = 10.15625GHz <sup>[5]</sup>                                      | 625MHz    | -       | 73      | 89      |          |

<sup>2.</sup> All conditions in this table must be met to guarantee device functionality and performance.

<sup>2.</sup> Characterized using a Rohde and Schwarz SMA100 overdriving the crystal interface.

<sup>3.</sup> Measured after the APLL has locked and settled.

<sup>4.</sup> All outputs enabled and generating clocks with the same frequency sourced from the APLL via integer output dividers.

<sup>5.</sup> Measured after the DPLL has locked and settled using a jitter free and wander-free reference to the DPLL.

- 1. The device will meet specifications after thermal equilibrium has been reached.

- 2. Characterized using a Rohde and Schwarz SMA100 overdriving the crystal interface.

- 3. Measured after the APLL has locked and settled.

- 4. All outputs enabled and generating clocks with the same frequency sourced from the same FOD.

- 5. Measured after the DPLL has locked and settled using a jitter free and wander-free reference to the DPLL.

## 2.6 Power Supply Noise Rejection

Table 8. Power Supply Noise Rejection [1]

| Symbol | Parameter                                                                 | Condition                   | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------------------------------------------|-----------------------------|---------|---------|---------|------|

|        |                                                                           | f <sub>NOISE</sub> = 10kHz  | -       | -125    | -       |      |

|        |                                                                           | f <sub>NOISE</sub> = 25kHz  | -       | -127    | -       |      |

|        | Power supply rejection ratio V <sub>DDx</sub> = 1.8V <sup>[2][3][4]</sup> | f <sub>NOISE</sub> = 50kHz  | -       | -117    | -       |      |

| PSNR   |                                                                           | f <sub>NOISE</sub> = 100kHz | -       | -99     | -       | dBc  |

|        |                                                                           | f <sub>NOISE</sub> = 250kHz | -       | -92     | -       |      |

|        |                                                                           | f <sub>NOISE</sub> = 500kHz | -       | -80     | -       |      |

|        |                                                                           | f <sub>NOISE</sub> = 1MHz   | -       | -81     | -       |      |

- 1. The device will meet specifications after thermal equilibrium is reached.

- 2. 100mV peak-to-peak sine wave applied to any  $V_{DDO}$ , excluding  $V_{DDO}$  of the output being measured and excluding  $V_{DD\_VCO}$ .

- 3. Relative to 156.25MHz carrier frequency.

- 4. Measured on any differential output.

# 2.7 Crystal Oscillator Input and APLL AC/DC Electrical Characteristics

Table 9. Crystal Oscillator Input and Analog PLL AC/DC Characteristics

| Symbol            | Parameter                          | Condition                                                                | Minimum | Typical             | Maximum | Unit   |

|-------------------|------------------------------------|--------------------------------------------------------------------------|---------|---------------------|---------|--------|

| -                 | Mode of oscillation                | -                                                                        |         | Fundamental         | •       | -      |

|                   |                                    | Using a crystal with APLL in Integer mode [1]                            | 25      | -                   | 80      | MHz    |

|                   | Input Frequency                    | Over-driving crystal interface, with APLL in Integer mode <sup>[1]</sup> | 25      | -                   | 150     | IVII   |

| f <sub>IN</sub>   |                                    | Using a crystal, with APLL not in Integer mode [2]                       | 25      |                     | 73      |        |

|                   |                                    | Over-driving crystal interface,<br>with APLL not in Integer mode<br>[2]  | 25      |                     | 63      |        |

| V <sub>BIAS</sub> | Bias point for XIN                 | Over-driving XIN input                                                   | -       | 0.6                 | -       | V      |

| V <sub>IVS</sub>  | Input voltage swing for XIN        | Over-driving XIN input                                                   | 0.6     | -                   | 1.2     | V      |

|                   | Internal crystal oscillator tuning | xobuf_digicap_x1 = 0x0<br>xobuf_digcap_x2 = 0x0                          | -       | 8                   | -       | 5<br>E |

| C <sub>T</sub>    | capacitance                        | xobuf_digicap_x1 = 0xF<br>xobuf_digcap_x2 = 0xF                          | -       | 11.5 <sup>[3]</sup> | -       | pF     |

| f <sub>VCO</sub>  | Analog PLL VCO Operating Frequency |                                                                          | 9.7     | -                   | 10.75   | GHz    |

| F <sub>TOL</sub>  | Frequency Tolerance [4][5][6][7]   | -40°C to 85°C                                                            | -450    | -                   | 450     | PPM    |

- 1. APLL configured with integer\_mode = 0x1. Note this configuration does not permit the APLL to be steered by the DPLL/DCO.

- 2. APLL configured with integer\_mode = 0x0, apll\_fb\_div\_frac  $\neq 0x0$ .

- 3. Capacitance increases by 0.25pF for each step of both xobuf\_digicap\_x1 and xobuf\_digicap\_x2.

- 4. F<sub>TOL</sub> refers to the frequency accuracy of the Device Frequency Reference, either a crystal connected between XIN and XOUT, or an oscillator connected to XIN and overdriving the crystal interface. The APLL can reliably lock to a frequency reference that meets the F<sub>TOL</sub> limits.

- 5. Inclusive of initial tolerance at 25°C, temperature stability, and aging.

- 6. The APLL frequency steering range (±F<sub>STEER</sub>) available for a DPLL or DCO to digitally steer the APLL is determined by the following expression: F<sub>STEER</sub> = |F<sub>TOL</sub>| |F<sub>ACC</sub>|; where F<sub>ACC</sub> is the frequency accuracy of the device frequency reference. For example, if the frequency accuracy of the Device Frequency Reference is ±100PPM. then the APLL frequency steering range will be ±350PPM.

- 7. The frequency accuracy of the device frequency reference should be chosen to meet the free-running frequency requirements of the application, and to allow sufficient frequency steering range for a DPLL or DCO to lock the APLL to its reference and to track reference noise. For more information, see Device Frequency Reference.

# 2.8 Recommended Crystal Characteristics

**Table 10. Recommended Crystal Characteristics**

| Symbol           | Parameter <sup>[1]</sup>     | Condition                   | Minimum                                                           | Typical | Maximum | Unit |

|------------------|------------------------------|-----------------------------|-------------------------------------------------------------------|---------|---------|------|

| ESR              | Equivalent Series Resistance | 8pF ≤ C <sub>L</sub> ≤ 12pF | -                                                                 | -       | 50      | Ω    |

| Co               | Shunt Capacitance            | -                           | -                                                                 | -       | 4       | pF   |

| C <sub>L</sub>   | Load Capacitance             | -                           | -                                                                 | 8       | 12      | pF   |

| Drive            | Drive Level [2]              | C <sub>L</sub> = 8pF        | -                                                                 | -       | 160     | μW   |

| Dilve            | Dive Level ( )               | C <sub>L</sub> = 12pF       | -                                                                 | -       | 290     | μνν  |

| F <sub>TOL</sub> | Frequency Tolerance          | -                           | See F <sub>TOL</sub> in Table 9 and Device<br>Frequency Reference |         |         | -    |

- 1. Specified by the crystal manufacturer.

- 2. Refers to power delivered by the oscillator circuit and dissipated in the crystal. The crystal must tolerate this drive level.

# 2.9 Clock Input (CLKIN/nCLKIN) AC/DC Characteristics

Table 11. Clock Input (CLKIN/nCLKIN) AC/DC Characteristics

| Symbol           | Parameter                                   | Condition                                       | Minimum                       | Typical   | Maximum                                  | Unit   |

|------------------|---------------------------------------------|-------------------------------------------------|-------------------------------|-----------|------------------------------------------|--------|

| V <sub>IPP</sub> | Differential input peak-to-peak voltage [1] | -                                               | 0.15                          | -         | 1.20                                     | V      |

| V                | Differential input common mode voltage [2]  | PMOS buffer (HCSL) input                        | V <sub>I(PP)</sub> / 2        | 0.35      | V <sub>DD_CLK</sub> - 1.2                | V      |

| $V_{CMR}$        | Differential input common mode voltage ( )  | NMOS buffer (LVDS) input                        | 0.7                           | -         | V <sub>DD_CLK</sub> - V <sub>I(PP)</sub> | V      |

| E                | Input frequency                             | Differential input                              | -                             | -         | 1000                                     | MHz    |

| F <sub>IN</sub>  | Input frequency                             | Single-ended input                              | -                             | -         | 150                                      | IVITIZ |

| F <sub>PD</sub>  | DPLL phase detector frequency [3]           | -                                               | 0.001                         | 0.001 -   |                                          | MHz    |

| 1                | Differential input high current, CLKIN      | \/ -\/                                          | -                             | -         | 5                                        |        |

| I <sub>IH</sub>  | Differential input high current, nCLKIN     | $V_{IN} = V_{DD\_CLK (max)}$                    | -                             | -         | 5                                        | μΑ     |

| ı                | Differential input low current, CLKIN       | \/ - 0\/                                        | -5                            | -         | -                                        |        |

| I <sub>IL</sub>  | Differential input low current, nCLKIN      | V <sub>IN</sub> = 0V                            | -5                            | -         | -                                        | μΑ     |

| V <sub>IH</sub>  | Input high voltage                          | V <sub>DD_CLK</sub> = V <sub>DD_CLK (max)</sub> | 0.65 ×<br>V <sub>DD_CLK</sub> | · · · · · |                                          | V      |

| V <sub>IL</sub>  | Input low voltage                           | V <sub>DD_CLK</sub> = V <sub>DD_CLK (max)</sub> | -0.3                          | -         | 0.35 ×<br>V <sub>DD_CLK</sub>            | V      |

| I <sub>IH</sub>  | Input high current                          | V <sub>IN</sub> = V <sub>DD_CLK (max)</sub>     | -                             | -         | 5                                        | μΑ     |

| I <sub>IL</sub>  | Input low current                           | V <sub>IN</sub> = 0V                            | -5                            | -         | -                                        | μΑ     |

- 1. Single-ended value.

- 2. Common mode is defined as the cross-point.

- 3. Internal input dividers can be used to reduce the CLKIN/nCLKIN frequency to be within the valid range.

# 2.10 Output Frequencies and Start-Up Time

Table 12. Output Frequencies and Start-Up Time

| Symbol                | Parameter                                                          | Condition                 | Minimum | Typical | Maximum | Unit   |

|-----------------------|--------------------------------------------------------------------|---------------------------|---------|---------|---------|--------|

| f                     | f <sub>OUT</sub> Output Frequency for Clocks Sourced from the APLL | Differential Output       | 0.004   | -       | 1000    | MHz    |

| OUT                   |                                                                    | LVCMOS Output             | 0.004   | -       | 250     | IVITIZ |

| Δf <sub>OUT</sub>     | Output frequency tuning resolution                                 | Fractional Output Divider | -       | -       | 0.1     | PPT    |

| t <sub>Start-up</sub> | Start-up time [1][2]                                               | Synthesizer mode          | -       | -       | 9.9     | ms     |

<sup>1.</sup> Measured from when all power supplies have reached > 90% of nominal voltage to the first stable clock edge on the output. A stable clock is defined as one generated from a locked PLL (as appropriate for the configuration listed) with no further perturbations in frequency expected. Includes time needed to load a configuration from internal OTP.

# 2.11 Phase and Frequency Uncertainty

Table 13. Phase and Frequency Uncertainty [1][2]

| Symbol                                                                | Parameter                                               | Condition Minimum                                                                    |     | Typical | Maximum | Unit |

|-----------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|-----|---------|---------|------|

| $\Delta t_{HS}$ Output phase change using hitless reference switching | Output phase change using hitless                       | DPLL reference frequency = 25MHz, DPLL bandwidth = 0.1Hz                             | -   | 15      | 65      | no   |

|                                                                       | DPLL reference frequency = 8kHz, DPLL bandwidth = 0.1Hz |                                                                                      | 150 | 910     | ps      |      |

| $\Delta f_{HO}$                                                       | Initial frequency offset entering holdover              | Using holdover filter with<br>1mHz bandwidth and allowing<br>settling time of 1 hour | -   | 0.2     | 0.7     | PPB  |

| Δt <sub>HO</sub>                                                      | Initial Phase Shift entering Holdover                   | Using LOS monitor to disqualify                                                      | -   | 6       | 30      | ps   |

<sup>1.</sup> The device will meet specifications after thermal equilibrium has been reached.

<sup>2.</sup> Start-up time will depend on the actual configuration used. For more information, please contact Renesas Technical Support.

<sup>2.</sup> Measured after the DPLL has locked and settled using a jitter free and wander-free reference.

# 2.12 Output-to-Output and Input-to-Output Skew

Table 14. Output-to-Output and Input-to-Output Skew [1][2][3]

| Symbol           | Parameter                                                                 | Condition                                                                              | Minimum | Typical | Maximum | Unit  |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                  |                                                                           | Any two outputs within the same output bank                                            | -       | 20      | 50      | ps    |

|                  | Output-to-output skew differential outputs [4][5]                         | Any two outputs across all output banks from the same APLL or FOD source               | -       | 40      | 70      | ps    |

|                  |                                                                           | Any two outputs across all output banks from different APLL or FOD sources             | -       | 50      | 80      | ps    |

| t <sub>sk</sub>  |                                                                           | Any two outputs within the same output bank                                            | -       | 40 70   | ps      |       |

|                  | Output-to-output skew LVCMOS outputs [4][5]                               | Any two outputs across all output banks from the same APLL or FOD source               | -       | 60      | 90      | ps    |

|                  |                                                                           | Any two outputs across all output banks from different APLL or FOD sources             | -       | 80      | 100     | ps    |

| ۸+               | Output-to-output skew temperature variation [4]                           | Single device, at a fixed voltage, over temperature                                    | -       | 0.30    | 2       | ps/°C |

| ∆t <sub>SK</sub> | Output-to-output skew variation outputs [4]                               | put skew variation outputs  Single device, over process, temperature, and voltage  2 4 | 4       | ps      |         |       |

| t <sub>PD</sub>  | Input-to-output delay differential inputs and differential outputs [6][7] | DPLL path to any output                                                                | 1.15    | 1.35    | 1.55    | ns    |

| Δt <sub>PD</sub> | Input-to-output delay variation [6][7]                                    | Fixed voltage, over temperature                                                        | -       | 1.2     | 2.0     | ps/°C |

- 1. The device will meet specifications after thermal equilibrium has been reached.

- 2. Output bank 1 refers to OUT[3:0], output bank 2 refers to OUT[7:4], and output bank 3 refers to OUT[11:8].

- 3. Measured across the full operating temperature range.

- 4. Defined as the time between the rising edges of two outputs of the same frequency, configuration, loading, and supply voltage.

- 5. This parameter is defined in accordance with JEDEC Standard 65.

- 6. Input-to-output delay is defined as the time between the rising edge of a reference clock at CLKINx and the associated rising edge of an output clock at OUTx that is locked to the reference by the DPLL. The reference clock and the output clock must have the same frequency and the reference input dividers must be bypassed.

- 7. Measured after the DPLL has locked and settled using a jitter free and wander-free reference to the DPLL.

## 2.13 LVCMOS Output AC/DC Characteristics

Table 15. LVCMOS Output AC/DC Characteristics [1]

| Symbol                         | Parameter                    | Condition                | Minimum                    | Typical | Maximum | Unit |

|--------------------------------|------------------------------|--------------------------|----------------------------|---------|---------|------|

| V <sub>OH</sub>                | Output high voltage [2]      | I <sub>OH</sub> = -2mA   | V <sub>DDO</sub> -<br>0.45 | -       | -       | V    |

| V <sub>OL</sub>                | Output low voltage [2]       | I <sub>OL</sub> = 2mA    | -                          | -       | 0.45    | V    |

| V <sub>OH</sub>                | Output high voltage [2]      | I <sub>OH</sub> = -100μA | V <sub>DDO</sub> - 0.2     | -       | -       | V    |

| V <sub>OL</sub>                | Output low voltage [2]       | I <sub>OL</sub> = 100μA  | -                          | -       | 0.2     | V    |

| I <sub>OZ</sub>                | Output leakage current       | Outputs tri-stated       | -5                         | -       | 5       | μA   |

| Z <sub>OUTDC</sub>             | DC output impedance          | At 25°C                  | -                          | 46      | -       | Ω    |

| t <sub>R</sub> /t <sub>F</sub> | Rise/Fall time<br>20% to 80% | -                        | 133                        | 200     | 310     | ps   |

| t <sub>DC</sub>                | Output duty cycle            | -                        | 45                         | 50      | 55      | %    |

- 1. Measured with outputs terminated with  $50\Omega$  to  $V_{DDO}/2$ .

- 2. These values are compliant with JESD8-7A.

# 2.14 LVDS Output AC/DC Characteristics

Table 16. LVDS Output AC/DC Characteristics [1]

| Symbol           | Parameter                                                     | Condition                 | Minimum | Typical | Maximum | Unit |

|------------------|---------------------------------------------------------------|---------------------------|---------|---------|---------|------|

|                  | Output valtage swing [2]                                      | out_cnf_lvds_amp = 0x0    | 156     | 377     | 526     | mV   |

| $V_{OD}$         | Output voltage swing [2]                                      | out_cnf_lvds_amp = 0x1    | 336     | 456     | 594     | mV   |

|                  | Offset voltage                                                | out_lvds_cm_voltage = 0x1 | 775     | 900     | 1025    |      |

| $V_{OS}$         |                                                               | out_lvds_cm_voltage = 0x2 | 875     | 1000    | 1125    | mV   |

|                  |                                                               | out_lvds_cm_voltage = 0x3 | 975     | 1100    | 1225    |      |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between complimentary output states | -                         | 5       | 20      | 50      | mV   |

| + /+             | Rise/fall time                                                | out_cnf_lvds_amp = 0x0    | 73      | 125     | 190     | 20   |

| $t_R/t_F$        | 20% to 80%                                                    | out_cnf_lvds_amp = 0x1    | 80      | 135     | 200     | ps   |

| t <sub>DC</sub>  | Output duty cycle                                             | -                         | 45      | 50      | 55      | %    |

<sup>1.</sup> Outputs terminated with  $100\Omega$  across OUTx and nOUTx.

# 2.15 HCSL Output AC/DC Characteristics

Table 17. HCSL Output AC/DC Characteristics [1]

| Symbol                          | Р                            | arameter                           | Condition                | Minimum | Typical | Maximum | Unit |

|---------------------------------|------------------------------|------------------------------------|--------------------------|---------|---------|---------|------|

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x0 | 172     | 213     | 272     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x1 | 227     | 266     | 326     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x2 | 267     | 321     | 393     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x3 | 313     | 374     | 466     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x4 | 360     | 430     | 540     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x5 | 398     | 482     | 640     | mV   |

|                                 |                              | HCSL Mode<br>(Amplitude boost off) | out_cnf_hcsl_swing = 0x6 | 402     | 537     | 709     | mV   |

| V [2]                           | Output voltage swing         |                                    | out_cnf_hcsl_swing = 0x7 | 454     | 589     | 764     | mV   |

| V <sub>OVS</sub> <sup>[2]</sup> |                              |                                    | out_cnf_hcsl_swing = 0x8 | 508     | 641     | 815     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0x9 | 560     | 692     | 864     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xA | 619     | 742     | 901     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xB | 662     | 789     | 940     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xC | 700     | 834     | 981     | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xD | 725     | 875     | 1026    | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xE | 745     | 913     | 1068    | mV   |

|                                 |                              |                                    | out_cnf_hcsl_swing = 0xF | 789     | 946     | 1102    | mV   |

|                                 |                              | HCSL Mode<br>(Amplitude boost on)  | out_cnf_hcsl_swing = 0xF | 812     | 1085    | 1359    | mV   |

| t <sub>R</sub> /t <sub>F</sub>  | Rise/fall time<br>20% to 80% | out_cnf_hcsl_swing = A             | out_cnf_hcsl_swing = Any |         | 161     | 225     | ps   |

| t <sub>DC</sub>                 | Output duty cycle            |                                    |                          | 47      | 50      | 52      | %    |

<sup>1.</sup> Outputs terminated with  $50\Omega$  to GND on each OUTx and nOUTx pin.

<sup>2.</sup> Single-ended measurement.

<sup>2.</sup> Peak-to-peak output voltage swing on each OUTx and nOUTx pin.

# 2.16 Power Supply Current

Table 18. Power Supply Current [1]

| Symbol                    | Parameter                                                                 |                                                                                   | Condition                        | Typical | Maximum | Unit |

|---------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|---------|---------|------|

|                           |                                                                           | Dividers, muxes                                                                   | s and TDC                        | 13      | 19      |      |

| I <sub>DD_CLK</sub>       | Supply current for V <sub>DD_CLK</sub>                                    | Per single-ende                                                                   | ed input                         | 1       | 2       | mA   |

|                           |                                                                           | Per differential input                                                            |                                  | 2       | 4       |      |

| I <sub>DDD33_SERIAL</sub> | Supply current for V <sub>DDD33_SERIAL</sub>                              |                                                                                   | -                                | 0.5     | 1       | mA   |

| I <sub>DDXO_DCD</sub>     | Supply current for V <sub>DDXO_DCO</sub>                                  | V <sub>DDXO_DCD</sub> = 1                                                         | $V_{DDXO\_DCD} = 1.89V$          |         | 86      | mA   |

| I <sub>DD_VCO</sub>       | Supply current for V <sub>DD_VCO</sub>                                    | V <sub>DD_VCO</sub> = 1.89V                                                       |                                  | 230     | 260     | mA   |

|                           |                                                                           | V <sub>DDD33_DIA</sub> = 1.89V or 3.465V<br>All FODs off                          |                                  | 52      | 69      |      |

|                           |                                                                           | I <sub>DD_FODDIGBASI</sub>                                                        |                                  |         |         |      |

| I <sub>DDD33_DIA</sub>    | Supply current for V <sub>DDD33_DIA</sub>                                 |                                                                                   | or one FOD at 120MHz             | 7       | 11      | mA   |

|                           |                                                                           | IDD_PERFODDIG                                                                     |                                  |         |         |      |

|                           |                                                                           | V <sub>DDD33_DIA</sub> = 1<br>Current adder f<br>120MHz                           | or one FOD per 100MHz over       | 1       | 2       |      |

|                           |                                                                           | I <sub>DD_FODDIGPERI</sub>                                                        | MHZ                              |         |         |      |

|                           |                                                                           | V <sub>DDOx_FODx</sub> = 1                                                        |                                  | 0.02    | 0.1     |      |

|                           |                                                                           | I <sub>DD_FODBASE</sub>                                                           |                                  |         |         |      |

| DD_FODxADD <sup>[2]</sup> | Supply current adder for VDD01_FOD0, VDD_FOD0,                            | V <sub>DDOx_FODx</sub> = 1.89V<br>Current adder with FOD at 120MHz.               |                                  | 34      | 38      |      |

|                           | $V_{DDO8\_FOD1}, V_{DDO9\_FOD2},$                                         | I <sub>DD_PERFOD</sub>                                                            |                                  |         |         |      |

|                           | V <sub>DDO10_FOD2</sub>                                                   | V <sub>DDOx_FODx</sub> = 1<br>Current adder f<br>120MHz.                          | 1.89V<br>for FOD per 100MHz over | 0.9     | 1.3     | mA   |