# RENESAS

# RC32514A

FemtoClock<sup>®</sup>2 Sub-100fs Universal Frequency Translator

# Description

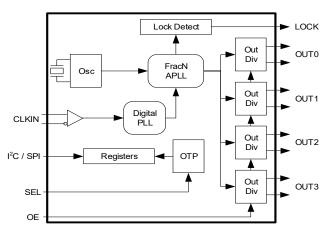

The RC32514A is a small, low-power timing component designed to be placed immediately adjacent to a PHY, switch, ASIC or FPGA that requires several reference clocks with jitter performance less than 100fs. The RC32514A can act as a frequency synthesizer to locally generate the reference clock, a jitter attenuator to perform local clean-up and/or frequency translation of a centrallysupplied reference or as a DCO for frequency margining or OTN clock applications.

The device is a member of Renesas' highperformance FemtoClock2 family.

# Applications

- Reference clock generator for 100Gbps / 400Gbps

PHYs or switches

- Adjustable OTN clock reference for OTU3 / OTU4 mappers

- Reference clock for programmable FiberOptic Modules

### Features

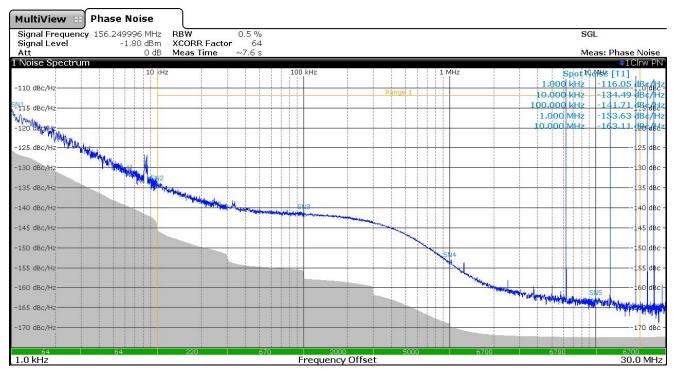

- Jitter below 100fs RMS maximum (10kHz to 20MHz)

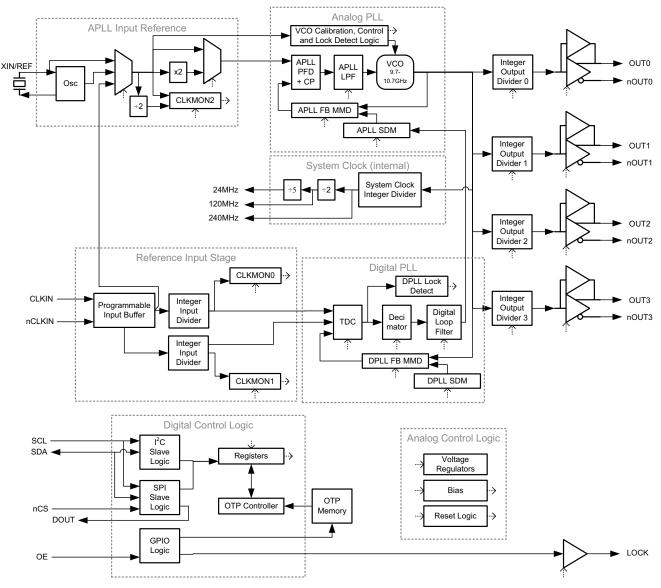

- PLL core consists of fractional-feedback Analog PLL (APLL) which can optionally be steered by a Digital PLL (DPLL)

- $\circ$  Operates from an integrated 60MHz crystal

- APLL frequency independent of input / crystal frequency

- Operates as a frequency synthesizer, jitter attenuator, or Digitally Controlled Oscillator (DCO)

- DPLL loop filter programmable from 10Hz to 12kHz

- $\circ$  DCO has tuning granularity of < 1ppb

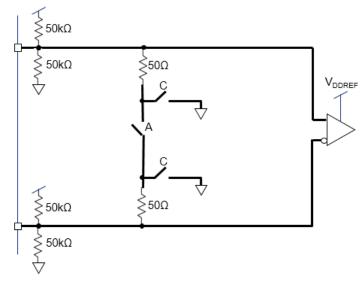

- Programmable input buffer supports HCSL, LVDS, or two LVCMOS with no external terminations needed

- $\circ\,$  Input frequencies: 1MHz to 800MHz (250MHz for LVCMOS)

- Reference monitor qualifies/disqualifies input clock

- Programmable status output

- 4 differential / 8 LVCMOS outputs

- $\circ\,$  Any frequency from 10MHz to 1GHz (180MHz for LVCMOS)

- Programmable output buffer supports HCSL (DCcoupled), LVDS/LVPECL/CML (AC-coupled) or two LVCMOS

- $\circ\,$  Differential output swing is selectable: 400mV to 800mV

- $\circ$  Output Enable input with programmable effect

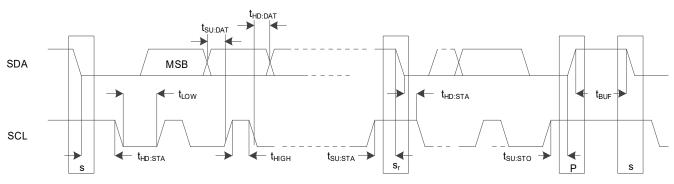

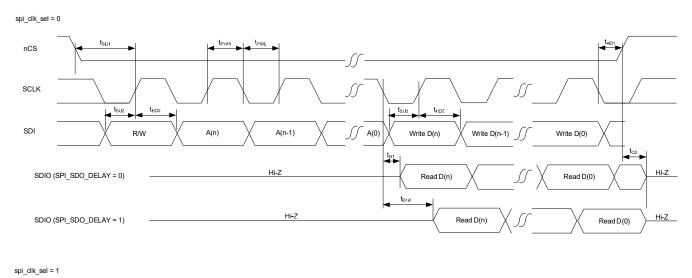

- Supports up to 1MHz I<sup>2</sup>C or up to 20MHz SPI serial processor port

- Can configure itself automatically after reset via internal customer-definable One-Time Programmable (OTP) memory with up to four different configurations

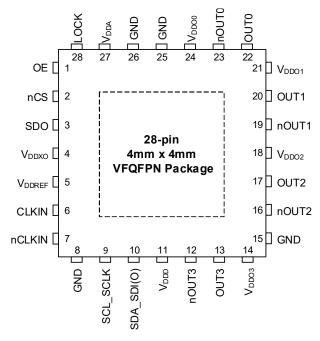

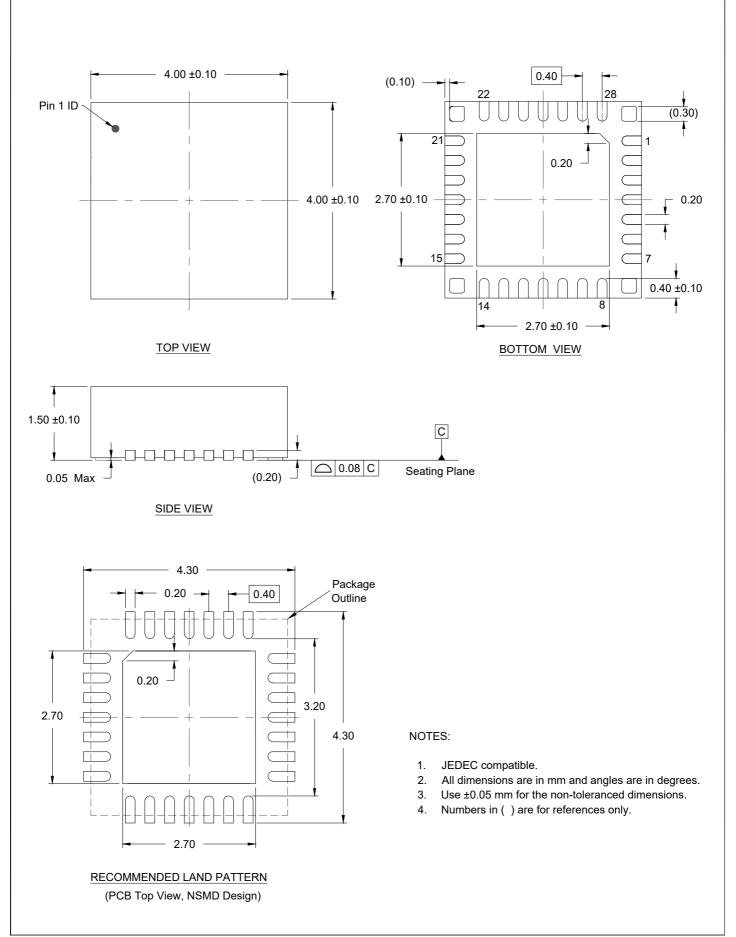

- 4 × 4 mm 28-QFN package

# **Block Diagram**

# Contents

| 1. | Abou   | It this Document                                                  | 8 |

|----|--------|-------------------------------------------------------------------|---|

|    | 1.1    | Document Conventions                                              | 8 |

|    |        | 1.1.1 Signal Notation                                             | 8 |

|    |        | 1.1.2 Object Size Notation                                        |   |

|    |        | 1.1.3 Numeric Notation                                            |   |

|    |        | 1.1.4 Endianness                                                  | 8 |

| 2. | Din Ir | nformation                                                        | ٩ |

| 2. | 2.1    | Pin Assignments                                                   |   |

|    | 2.1    | Pin Descriptions                                                  |   |

|    |        |                                                                   |   |

| 3. | -      | ifications                                                        |   |

|    | 3.1    | Absolute Maximum Ratings                                          |   |

|    | 3.2    | Recommended Operating Conditions                                  |   |

|    | 3.3    | Reference Clock Phase Jitter and Phase Noise    1                 |   |

|    | 3.4    | AC Electrical Characteristics                                     |   |

|    | 3.5    | DC Electrical Characteristics                                     | 8 |

| 4. | Appli  | ications Information                                              | 5 |

|    | 4.1    | Power Considerations                                              | 5 |

|    | 4.2    | Recommendations for Unused Input and Output Pins 2                | 5 |

|    |        | 4.2.1 CLKIN/nCLKIN Input                                          | 5 |

|    |        | 4.2.2 LVCMOS Control Pins                                         | 5 |

|    |        | 4.2.3 LVCMOS Outputs                                              | 5 |

|    |        | 4.2.4 Differential Outputs                                        | 5 |

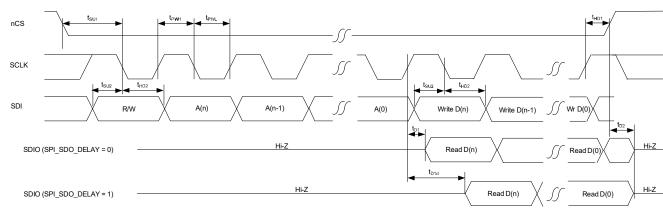

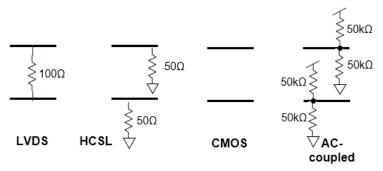

|    | 4.3    | Clock Input Interface                                             | 5 |

|    | 4.4    | Differential Output Termination                                   | 6 |

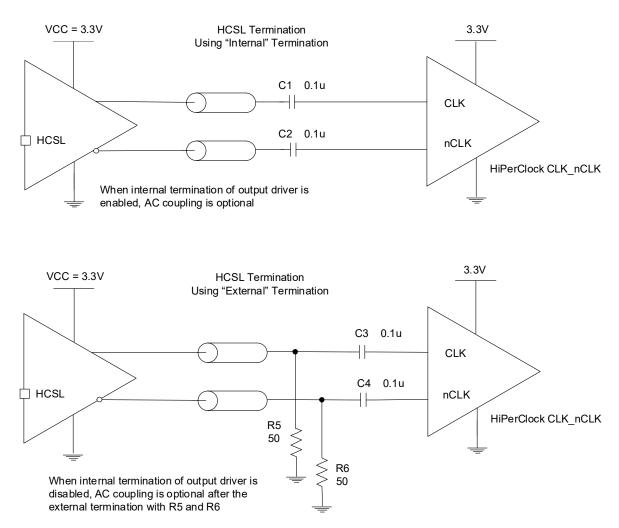

|    |        | 4.4.1 Direct-Coupled HCSL Termination                             | 6 |

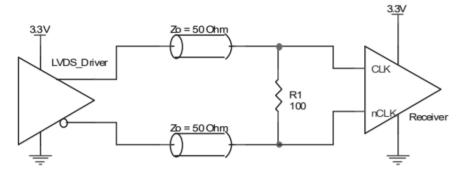

|    |        | 4.4.2 Direct-Coupled LVDS Termination                             | 7 |

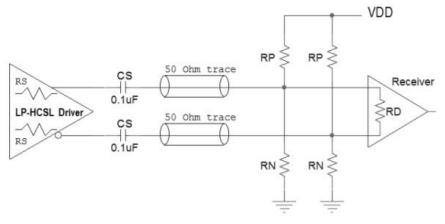

|    |        | 4.4.3 AC-Coupled Differential Termination 2                       | 8 |

| 5. | Archi  | itecture                                                          | 9 |

|    | 5.1    | Modes of Operation                                                |   |

|    | ••••   | 5.1.1 Frequency Synthesizer/Digitally Controlled Oscillator (DCO) |   |

|    |        | 5.1.2 Jitter Attenuator                                           |   |

| 6. | Block  | ks 3                                                              | 1 |

| 0. | 6.1    | Device Reset Logic                                                |   |

|    | 0.1    | 6.1.1 Bias Calibration                                            |   |

|    | 6.2    | Crystal Oscillator                                                |   |

|    | 6.3    | Reference Clock Input                                             |   |

|    | 6.4    | Analog Phase Lock Loop                                            |   |

|    | 0.4    | 6.4.1 Frequency Doubler                                           |   |

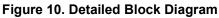

|    |        | 6.4.2 APLL Loop Filter (LPF)                                      |   |

|    |        | 6.4.3 Voltage-Controlled Oscillator (VCO)                         |   |

|    |        | 6.4.4 APLL Feedback Divider                                       |   |

|    |        | 6.4.5 APLL Lock Detector                                          |   |

|    |        | 6.4.6 Direct DCO Control                                          |   |

|    | 6.5    | Reference Clock Outputs                                           |   |

|    | 0.0    | 6.5.1 Integer Output Divider (IOD)                                |   |

|    |        | 6.5.2 Clock Output Driver                                         |   |

|    |        |                                                                   |   |

|    |                     | 6.5.3                                                                                                                                                                                                                     | Output Enable Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

|----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

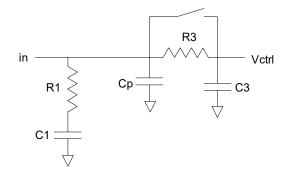

|    | 6.6                 | DPLL.                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    |                     | 6.6.1                                                                                                                                                                                                                     | Reference Clock Input Buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|    |                     | 6.6.2                                                                                                                                                                                                                     | Input Dividers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

|    |                     | 6.6.3                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

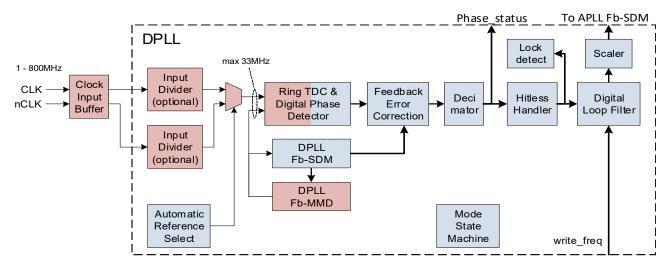

|    |                     | 6.6.4                                                                                                                                                                                                                     | Digital Loop Filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

|    |                     | 6.6.5                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    |                     | 6.6.6                                                                                                                                                                                                                     | DPLL Feedback Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

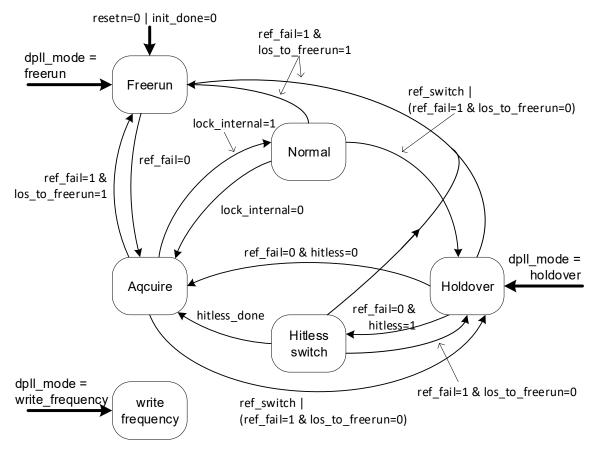

|    | 67                  | 6.6.7                                                                                                                                                                                                                     | DPLL State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|    | 6.7                 | 6.7.1                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    |                     |                                                                                                                                                                                                                           | Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

|    | 6.0                 | 6.7.2                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

|    | 6.8                 |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    | 6.9                 |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

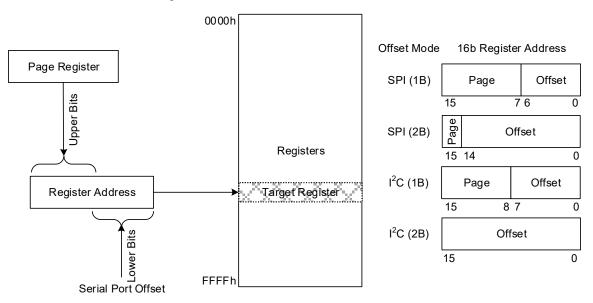

|    |                     | 6.9.1                                                                                                                                                                                                                     | Paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |

|    |                     | 6.9.2                                                                                                                                                                                                                     | I <sup>2</sup> C Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |

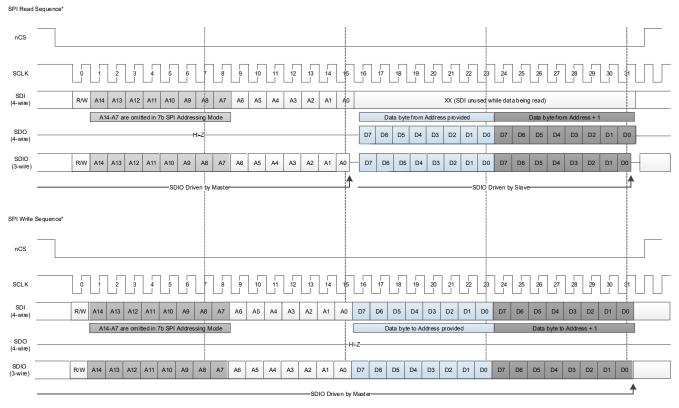

|    |                     | 6.9.3                                                                                                                                                                                                                     | SPI Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

|    | 6.10                |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    |                     | 6.10.1                                                                                                                                                                                                                    | Lock Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|    |                     | 6.10.2                                                                                                                                                                                                                    | Serial Data Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|    |                     | 6.10.3                                                                                                                                                                                                                    | Output Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|    | 6.11                |                                                                                                                                                                                                                           | up Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|    |                     | 6.11.1                                                                                                                                                                                                                    | Configuration Select Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

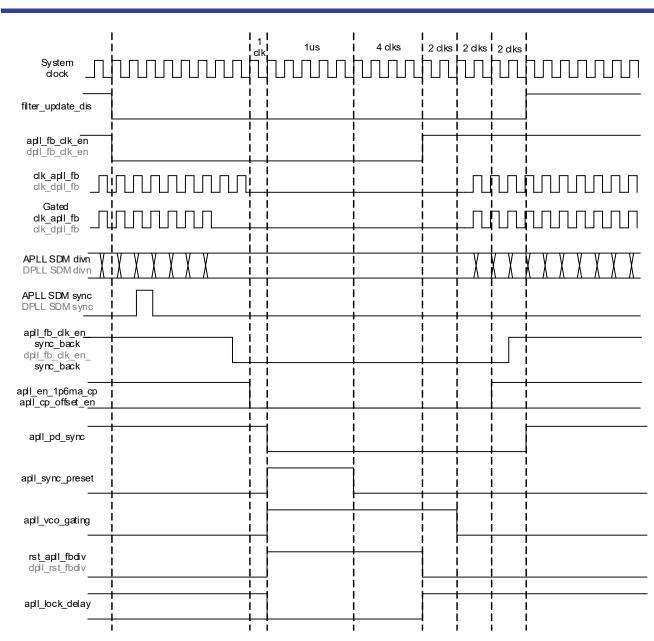

|    |                     | 6.11.2                                                                                                                                                                                                                    | Divider Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

|    |                     | 6.11.3                                                                                                                                                                                                                    | Maximum PLL Lock Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                                                                                                                               |

|    |                     |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

| 7. | Regis               | •                                                                                                                                                                                                                         | nization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |