#### RRP63175

5V, 7.2A Source, 5.3A Sink, High Frequency GaN/MOSFET Single Low-Side Driver

### **Description**

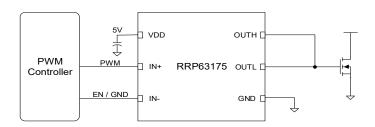

The RRP63175 is a 5V, 7.2A source, 5.3A sink high frequency enhance mode GaN or logic level gate MOSFET single low-side driver. The RRP63175 accepts 3.3V/5V logic level PWM inputs.

The driver features a fast 5ns typical propagation delay, making it optimal for high-frequency switching applications. The RRP63175 can operate up to 30MHz.

The RRP63175 has split-gate outputs, providing flexibility to adjust the turn-on and turn-off strength independently.

The driver features VDD UVLO that protects against undervoltage operation and over-temperature protection (OTP) in the event of overload and fault condition.

The RRP63175 is offered in a SCTDFN-6L (2mm×2mm) package with wettable flanks.

#### **Features**

- Accepts 3.3V/5V logic level PWM inputs

- 7.2A source and 5.3A sink driver for GaN/MOSFET

- Separately adjusts turn-on and turn-off speed

- Supports positive, negative PWM or EN input logic

- Fast propagation delay: 5ns typical delay

- 7ns minimum input pulse width

- 4ns typical rise and fall time

- 5V power supply

- V<sub>DD</sub> undervoltage lockout (UVLO) and over-temperature protection (OTP)

- Small package with low parasitic inductance supporting up to 30MHz switching frequency application

- Low power consumption

- 2mm×2mm SCTDFN package

#### **Applications**

- GaN/MOSFET synchronous rectifier

- Power modules

- DC/DC converter

Figure 1. Low-Side Driver Typical Application

## **Contents**

| 1.  | Over                   | Overview                          |    |  |  |  |  |  |

|-----|------------------------|-----------------------------------|----|--|--|--|--|--|

|     | 1.1                    | Block Diagram                     | 3  |  |  |  |  |  |

| 2.  | Pin Ir                 | formation                         | 4  |  |  |  |  |  |

|     | 2.1                    | Pin Assignments                   |    |  |  |  |  |  |

|     | 2.2                    | Pin Descriptions                  | 4  |  |  |  |  |  |

| 3.  | Spec                   | ifications                        | 5  |  |  |  |  |  |

|     | 3.1                    | Absolute Maximum Ratings          | 5  |  |  |  |  |  |

|     | 3.2                    | Recommended Operating Conditions  | 5  |  |  |  |  |  |

|     | 3.3                    | Thermal Specifications            |    |  |  |  |  |  |

|     | 3.4                    | Electrical Specifications         | 6  |  |  |  |  |  |

|     | 3.5                    | Switching Specifications          | 7  |  |  |  |  |  |

|     | 3.6                    | Timing Diagrams                   | 7  |  |  |  |  |  |

| 4.  | Typic                  | al Performance Curves             | 8  |  |  |  |  |  |

| 5.  | Functional Description |                                   |    |  |  |  |  |  |

|     | 5.1                    | Overview                          |    |  |  |  |  |  |

|     | 5.2                    | Input Stage                       | 9  |  |  |  |  |  |

|     | 5.3                    | Output Stage                      | 10 |  |  |  |  |  |

|     | 5.4                    | Undervoltage Lockout (UVLO)       | 10 |  |  |  |  |  |

|     | 5.5                    | Over-Temperature Protection (OTP) | 10 |  |  |  |  |  |

| 6.  | Appli                  | cations Information               | 10 |  |  |  |  |  |

|     | 6.1                    | Output Damping                    | 10 |  |  |  |  |  |

|     | 6.2                    | VDD                               | 10 |  |  |  |  |  |

|     | 6.3                    | Application Curves                | 10 |  |  |  |  |  |

| 7.  | РСВ                    | Layout Guidelines                 | 11 |  |  |  |  |  |

| 8.  | Pack                   | age Outline Drawings              | 13 |  |  |  |  |  |

| 9.  |                        | ring Information                  |    |  |  |  |  |  |

| 10. |                        | sion History                      |    |  |  |  |  |  |

| ۸   |                        | •                                 | 11 |  |  |  |  |  |

## 1. Overview

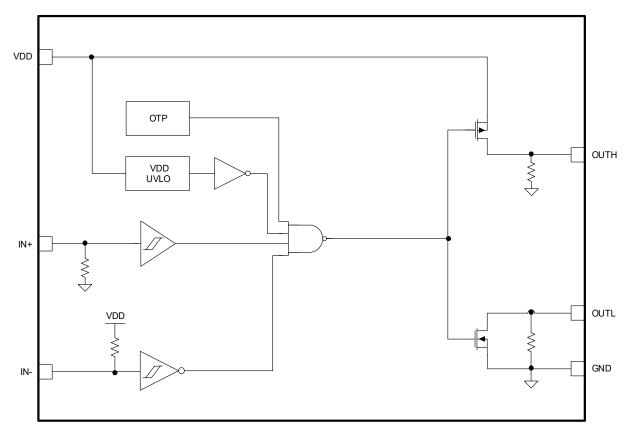

# 1.1 Block Diagram

Figure 2. Block Diagram

## 2. Pin Information

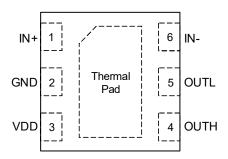

# 2.1 Pin Assignments

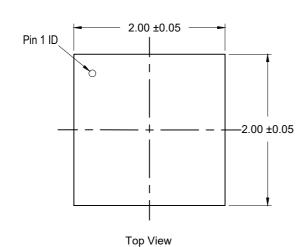

Figure 3. Pin Assignments - Top View

## 2.2 Pin Descriptions

| Pin<br>Name | Pin Number | Description                                                                                             |

|-------------|------------|---------------------------------------------------------------------------------------------------------|

| VDD         | 3          | Supply voltage is 5V. Decouple through a small size, low inductance capacitor to GND.                   |

| OUTH        | 4          | Pull-up gate drive output. Connect through an optional resistor to the gate of the target transistor.   |

| GND         | 2          | Analog ground. Provides the ground return path for driver circuitry and internal reference.             |

| OUTL        | 5          | Pull-down gate drive output. Connect through an optional resistor to the gate of the target transistor. |

| IN+         | 1          | Positive logic-level input                                                                              |

| IN-         | 6          | Negative logic-level input. The pin could be used as negative logic EN function.                        |

| Thermal Pad | -          | Internally connected to the ground plane through substrate.                                             |

## 3. Specifications

### 3.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter <sup>[1]</sup>                        | Minimum | Maximum | Unit |

|-------------------------------------------------|---------|---------|------|

| Supply Voltage, VDD                             | -0.3    | 6.0     | V    |

| Output Voltage, OUTH, OUTL                      | -0.3    | 6.0     | V    |

| Input voltage, IN+, IN-                         | -0.3    | 6.0     | V    |

| Maximum Junction Temperature                    | -40     | 150     | °C   |

| Maximum Storage Temperature Range               | -65     | 150     | °C   |

| Human Body Model (Tested per JS-001-2023)       | -2000   | 2000    | V    |

| Charged Device Model (Tested per JS-002-2022)   | -750    | 750     | V    |

| Latch-Up (Tested per JESD78F; Class 2, Level A) | -100    | 100     | mA   |

<sup>1.</sup> All voltages referenced to GND (AGND and PGND are connected together as GND) unless otherwise specified.

### 3.2 Recommended Operating Conditions

| Parameter <sup>[1][2]</sup> | Minimum | Typical | Maximum | Units |

|-----------------------------|---------|---------|---------|-------|

| Supply Voltage, VDD         | 4.5     | 5.0     | 5.5     | V     |

| Output Voltage, OUTH, OUTL  | 0.0     | -       | 5.5     | V     |

| Input Voltage, IN+, IN-     | 0.0     | 3.3/5   | 5.5     | V     |

| Operating Temperature       | -40     | -       | 125     | °C    |

<sup>1.</sup> All voltages referenced to GND (AGND and PGND are connected together as GND) unless otherwise specified.

## 3.3 Thermal Specifications

| Parameter             | Package     | Symbol                         | Conditions                                                                                                | Typical<br>Value | Unit |

|-----------------------|-------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|------|

| Thermal Resistance    |             | θ <sub>JA</sub> [1]            | Junction to ambient (on JEDEC high effective thermal conductivity test board with direct attach features) | 68               | °C/W |

|                       | 6 Ld SCTDFN | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case (at bottom)                                                                              | 11               |      |

|                       |             | $\theta_{JB}$                  | Junction to board                                                                                         | 31               |      |

| Max Power Dissipation |             | P <sub>D</sub>                 | For T <sub>J</sub> (MAX) of 150°C in free air at 25°C                                                     | 1.83             | W    |

<sup>1.</sup>  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board with direct attach features in free air. See TB379.

<sup>2.</sup> Assured by design.

<sup>2.</sup> For  $\theta_{\text{JC}}$ , the case temperature location is the center of the package underside.

### 3.4 Electrical Specifications

Typical Values at 25°C,  $V_{DD}$  = 5V; GND = 0V. Limits apply across the operating temperature range, -40°C to +125°C.

| Parameters                                                                | Symbol                                   | Test Conditions                                                                                     | Min <sup>[1]</sup> | Тур                 | Max <sup>[1]</sup> | Unit |

|---------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------|---------------------|--------------------|------|

| Power Supply                                                              | '                                        |                                                                                                     |                    | -                   |                    | -    |

| V <sub>DD</sub> Quiescent Current                                         | IQ                                       | V <sub>DD</sub> = 5V; IN+ = IN- = 0V                                                                | -                  | 48                  | -                  | μA   |

| V <sub>DD</sub> Operating Current                                         | I <sub>O</sub>                           | $V_{DD}$ = 5V; $f_{SW}$ = 1000kHz<br>PWMx = 50% square wave, EN = $V_{DD}$ ,<br>$C_{LOAD}$ = 1000pF | -                  | 5.9                 | -                  | mA   |

| VDD UV Rising Threshold                                                   | VIN <sub>UV_Rise</sub>                   | -                                                                                                   | 3.9                | 4.2                 | 4.5                | V    |

| VDD UV Threshold Hysteresis                                               | -                                        | -                                                                                                   | -                  | 0.2                 | -                  | V    |

| PWMx INPUT                                                                | '                                        |                                                                                                     |                    | <u>'</u>            |                    |      |

| Low Level Input Voltage<br>Threshold                                      | VIN <sub>x_L</sub>                       | -                                                                                                   | 1.0                | 1.4                 | 1.8                | V    |

| High Level<br>Input Voltage Threshold                                     | VIN <sub>x_H</sub>                       | -                                                                                                   | 1.6                | 2.1                 | 2.7                | V    |

| Input Voltage Hysteresis                                                  | VHys                                     | -                                                                                                   | -                  | 0.7                 | -                  | V    |

| Input Pull-Down IN+                                                       | RIN+                                     | PWMx = V <sub>DD</sub> . Measure I.Calculate R.<br>Pull down                                        | 100                | 200                 | 300                | kΩ   |

| Input Pull-UP IN-                                                         | RIN-                                     | -                                                                                                   | 100                | 200                 | 300                | kΩ   |

| Minimum Input Pulse Width for<br>Response at Output to Reach<br>90% Value | T <sub>MIN</sub>                         | C <sub>LOAD</sub> = 1nF                                                                             | -                  | 7.0 <sup>[2]</sup>  | -                  | ns   |

| Output                                                                    | !                                        |                                                                                                     |                    |                     |                    | !    |

| Peak Source Current                                                       | ISRC                                     | V <sub>DD</sub> = 5V, CV <sub>DD</sub> = 20.1μF,<br>CL = 0.256μF, f = 10Hz                          | -                  | 7.2 <sup>[2]</sup>  | -                  | А    |

| Pull-Up Resistance                                                        | ROH                                      | V <sub>DD</sub> = 5V, IOUT = 100mA                                                                  | -                  | 0.30[2]             | -                  | Ω    |

| Peak Sink Current                                                         | ISNK                                     | V <sub>DD</sub> = 5V, CV <sub>DD</sub> = 20.1μF,<br>CL = 0.256μF, f = 10Hz                          | -                  | 5.3[2]              | -                  | А    |

| Pull-Down Resistance                                                      | ROL                                      | V <sub>DD</sub> = 5V, IOUT = 100mA                                                                  | -                  | 0.25 <sup>[2]</sup> | -                  | Ω    |

| OUTH, OUTL Pull Down<br>Resistance                                        | Rout <sub>L</sub> ,<br>Rout <sub>H</sub> | -                                                                                                   | -                  | 400                 | -                  | kΩ   |

| Thermal Shutdown                                                          | 1                                        |                                                                                                     |                    |                     |                    | 1    |

| Thermal Shutdown                                                          | ОТ                                       | -                                                                                                   | -                  | 160                 | -                  | °C   |

| Thermal Hysteresis                                                        | -                                        | -                                                                                                   | -                  | 20                  | -                  | °C   |

<sup>1.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

<sup>2.</sup> Characterized by engineering samples, not fully tested.

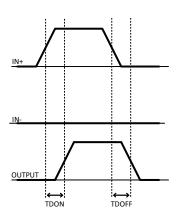

## 3.5 Switching Specifications

Typical Values at 25°C,  $V_{DD}$  = 5V; GND = 0V. Limits apply across the operating temperature range, -40°C to +125°C.

| Parameters                                     | Symbol | Test Conditions                                                                                                                    | Min | Тур                | Max | Unit |

|------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| Turn ON Propagation Delay (50% IN to 50% OUT)  | TDON   | C <sub>LOAD</sub> = 1nF, 50% of the input rise to 50% of output rise, V <sub>DD</sub> = 5V, f <sub>SW</sub> = 1MHz, 50% duty cycle | -   | 5[1]               | -   | ns   |

| Turn OFF Propagation Delay (50% IN to 50% OUT) | TDOFF  | C <sub>LOAD</sub> = 1nF, 50% of the input fall to 50% of output fall, V <sub>CC</sub> = 5V, f <sub>SW</sub> = 1MHz, 50% duty cycle | -   | 5[1]               | -   | ns   |

| Pulse Positive Distortion (∆tpd)               | -      | C <sub>LOAD</sub> = 1000pF                                                                                                         | -   | 150 <sup>[1]</sup> | -   | ps   |

| Output Rise Time (10% to 90%)                  | TRx    | C <sub>LOAD</sub> = 1nF, V <sub>DD</sub> = 5V, f <sub>SW</sub> = 1MHz,<br>50% duty cycle                                           | -   | 4[1]               | -   | ns   |

| Output Fall Time<br>(90% to 10%)               | TFx    | C <sub>LOAD</sub> = 1nF, V <sub>DD</sub> = 5V, f <sub>SW</sub> = 1MHz, 50% duty cycle                                              | -   | 4[1]               | -   | ns   |

<sup>1.</sup> Characterized by engineering samples, not fully tested.

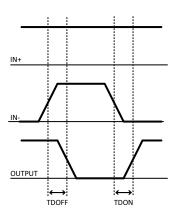

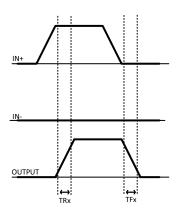

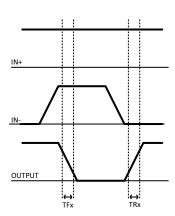

## 3.6 Timing Diagrams

Figure 4. Propagation Delay Timing Diagram

Figure 5. Output Rise and Fall Time

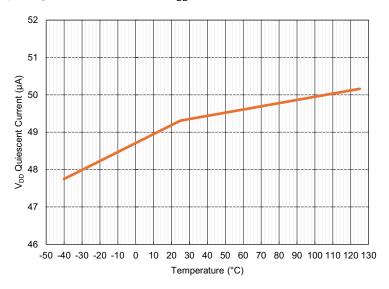

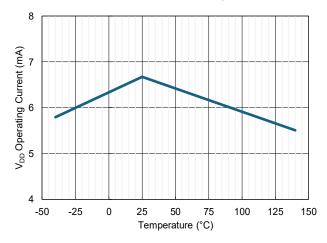

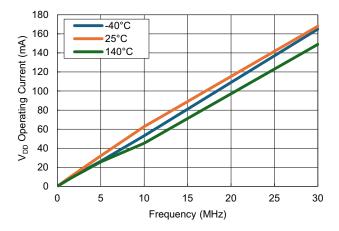

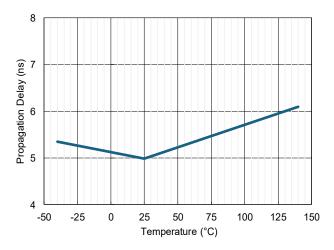

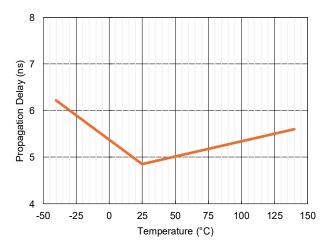

# 4. Typical Performance Curves

Unless otherwise specified, operating conditions at: T = +25 $^{\circ}$ C; V<sub>DD</sub> 5V;

Figure 6. Quiescent Current vs Temperature

Figure 7. Operating Current vs Temperature, 1nF Load, 1MHz Frequency

Figure 8. Operating Current vs Frequency, 1nF Load

Unless otherwise specified, operating conditions at: T = +25°C; V<sub>DD</sub> 5V;

Figure 9. Propagation Delay vs Temperature, 1nF Load, Rising Edge

Figure 10. Propagation Delay vs Temperature, 1nF Load, Falling Edge

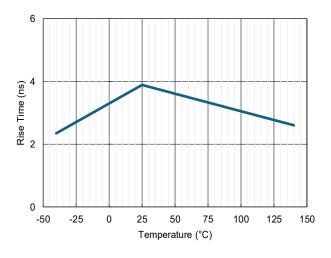

Figure 11. Rise Time vs Temperature, 1nF Load

Figure 12. Fall Time vs Temperature, 1nF Load

## 5. Functional Description

#### 5.1 Overview

The RRP63175 is an advanced gate driver engineered for GaN and silicon FETs in low-side configurations. This driver accommodates both 3.3V and 5V logic level PWM inputs and offers adjustable turn-on and turn-off strengths. The RRP63175 is optimized to deliver high peak current to the power transistor. Housed in a compact 2mm×2mm SCTDFN package with wettable flanks, this design is intended for high-density applications and mitigates the influence of parasitic inductance, which improves ringing performance across various conditions.

### 5.2 Input Stage

The input stage's IN+ and IN- pins are connected to an AND gate. When the IN+ signal exceeds the high-level input voltage threshold while the IN- signal remains below the low-level input voltage threshold, the output registers a high state. Conversely, the output transitions to a low state when both IN+ and IN- exceed the high-level input voltage threshold. Additional conditions resulting in a low output are detailed in the truth table (see Table 1). IN+ is connected to a pull-down resistor, and IN- is connected to a pull-up resistor to reduce the risk of erroneous behavior. The input pins are connected with two Schmitt triggers to minimize noise and mitigate the

impact of parasitic inductance on the performance of RRP63175. The IN- pin can be used as a negative logic EN pin.

**OUTH OUTL** IN-Low Low Open Low High High Open Low High Low Open Low High High Open Low

**Table 1. Functional Mode Table**

### 5.3 Output Stage

The output stage, comprising OUTH and OUTL, is designed with a split configuration, allowing for independent resistor connections to the gate. The output ringing and slew rate can be adjusted by using these two resistors. The RRP63175 features a peak drive current capability of 7.2 A for sourcing and 5.3 A for sinking. This current drive capability allows the driver to drive a 256nF load with a 1V output voltage difference time of 39ns for sourcing and 54ns for sinking.

#### 5.4 Undervoltage Lockout (UVLO)

RRP63175 is equipped with an internal undervoltage lockout (UVLO) mechanism to protect against fault conditions. The UVLO threshold is set between 3.9V and 4.5V, with a large hysteresis of 0.2V. During UVLO conditions, the OUTL pin is pulled down to ground.

### 5.5 Over-Temperature Protection (OTP)

The RRP63175 over-temperature protection feature activates with a rising edge trigger point at approximately 160°C of junction temperature. The device exhibits a hysteresis of 20°C, allowing it to resume operation when the junction temperature falls below 140°C.

## 6. Applications Information

### 6.1 Output Damping

High-speed applications often encounter ringing issues. Reducing parasitic inductance by shortening printed circuit board traces is crucial. Additionally, adding a gate resistor in series with the output helps mitigate ringing, though it might slightly increase the rise and fall times. Employing bypassing techniques is also effective in preventing ringing.

#### 6.2 VDD

Controlling overshoot voltage during switching is important to prevent the voltage from exceeding the absolute maximum limit. The RRP63175 supports typical supply voltages of 5V and a maximum of 6V. Reducing parasitic inductance in the layout is essential to mitigate ringing, which can contribute to VDD overshoot voltage.

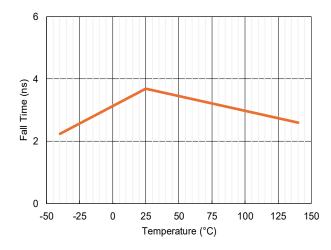

### 6.3 Application Curves

The waveforms were recorded using an RRP63175 IC evaluation board. Figure 13 through Figure 16 illustrate the short propagation delays observed on both the IN+ and IN– pins with no load on the output. This propagation delay performance is critical for high-frequency applications.

Figure 13. Propagation Delay (IN+ Rising Edge)

Figure 14. Propagation Delay (IN+ Falling Edge)

Figure 15. Propagation Delay (IN- Rising Edge)

Figure 16. Propagation Delay (IN- Falling Edge)

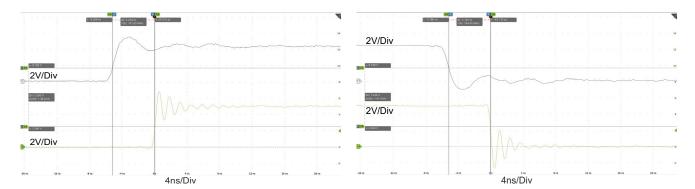

## 7. PCB Layout Guidelines

The AC performance of the RRP63175 depends significantly on the design of the PCB. The following layout design guidelines are recommended to achieve optimum switching performance:

- Connect the driver thermal pad to a low thermal impedance ground plane.

- Use as many vias as possible to connect the top layer PCB thermal land to the ground planes on other PCB layers.

- Place the driver as close as possible to the driven power FET.

- Keep power loops as short as possible by routing the source and return traces on adjacent layers, directly above and beneath each other.

- It might be necessary to add resistance to dampen resonating parasitic circuits. PCB designs with long trace lengths on the outputs may require series gate resistors on the FETs to dampen the oscillations.

- Use low inductance components such as SMD chip resistors and chip capacitors with low Equivalent Series Inductance (ESL). The 0201 package is highly recommended.

- Bypass capacitors are strongly recommended for the VDD power terminal. It is essential to ensure the shortest

possible lead lengths to the IC. Additionally, capacitors with a temperature coefficient of X7R or better are

advisable.

- Use planes where practical; they are usually more effective than parallel traces. A four or more layer PCB design is recommended.

- Understand where the switching power currents flow. The high-amplitude di/dt currents of the driven power FET induce significant voltage transients on the associated traces.

- Avoid having a signal ground plane under a high-amplitude dv/dt circuit, which injects di/dt currents into the signal ground paths.

- Complete the power dissipation and voltage drop calculations for the power traces. Many PCB/CAD programs

have built in tools for calculation of trace resistance.

- Large power components (such as power FETs, Electrolytic caps, power resistors) have internal parasitic inductance, which cannot be eliminated. This must be accounted for in the PCB layout and circuit design.

- If simulating the circuits is required, consider including parasitic components.

Figure 17. Typical RRP63175 Layout with GaN FET

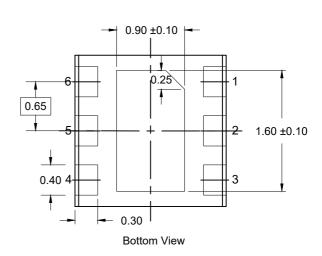

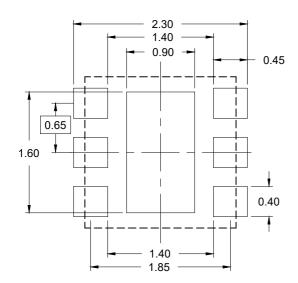

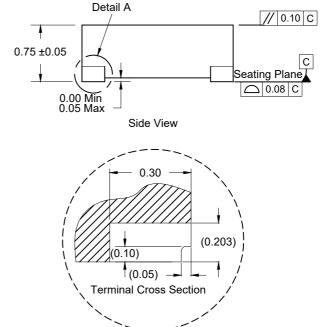

#### **Package Outline Drawings** 8.

The package outline drawings are located at the end of this document and are accessible from the Renesas website. The package information is the most current data available and is subject to change without revision of this document.

#### 9. **Ordering Information**

| Part Number <sup>[1]</sup> [2] | Part Marking | Package<br>Description <sup>[3]</sup><br>(RoHS Compliant) | Pkg. Dwg. # | Carrier Type <sup>[4]</sup> | Temp. Range   |

|--------------------------------|--------------|-----------------------------------------------------------|-------------|-----------------------------|---------------|

| RRP63175-NH0                   | 175          | 6LD SC-TDFN                                               | L6.2x2A     | Reel, 6k                    | -40 to +125°C |

| RRP63175-NM0                   | 173          | OLD SC-TDFN                                               | LU.ZXZA     | Reel, 1k                    | -40 to +125 C |

<sup>1.</sup> These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 2. For Moisture Sensitivity Level (MSL), refer to the RRP63175 product information pages. For more information about MSL, refer to TB363.

- 3. For the Pb-Free Reflow Profile, see TB493.

- 4. Refer to TB347 for details about reel specifications.

## 10. Revision History

| Revision | Date                                                          | Description                                                        |  |  |

|----------|---------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| 1.02     | 1.02 Apr 21, 2025 Updated POD. Added ECAD Design Information. |                                                                    |  |  |

| 1.01     | Jan 17, 2025                                                  | Updated Features. Updated Figures 7 and 9-12. Updated section 5.1. |  |  |

| 1.00     | Nov 21, 2024                                                  | Initial release.                                                   |  |  |

# A. ECAD Design Information

This information supports the development of the PCB ECAD model for this device. It is intended to be used by PCB designers.

# A.1 Part Number Indexing

| Orderable Part Number | Orderable Part Number Number of Pins |        | Package Code/POD Number |

|-----------------------|--------------------------------------|--------|-------------------------|

| RRP63175-NH0          | 6                                    | SCTDFN | L6.2x2A                 |

| RRP63175-NM0          | 6                                    | SCTDFN | L6.2x2A                 |

## A.2 Symbol Pin Information

### A.2.1 6-SCTDFN

| Pin Number | Primary Pin Name | Primary Electrical Type | Alternate Pin Name(s) |

|------------|------------------|-------------------------|-----------------------|

| 1          | IN+              | Input                   | -                     |

| 2          | GND              | Power                   | -                     |

| 3          | VDD              | Power                   | -                     |

| 4          | OUTH             | Output                  | -                     |

| 5          | OUTL             | Output                  | -                     |

| 6          | 6 IN-            |                         | -                     |

| EPAD7      | GND              | Power                   | -                     |

# A.3 Symbol Parameters

| Orderable Part Number | Qualification | Mounting Type | Peak Source<br>Current | Peak Sink<br>Current | Min Supply<br>Voltage | Max Supply<br>Voltage | RoHS      | Min Operating<br>Temperature | Max Operating<br>Temperature | Max Switching<br>Frequency |

|-----------------------|---------------|---------------|------------------------|----------------------|-----------------------|-----------------------|-----------|------------------------------|------------------------------|----------------------------|

| RRP63175-NH0          | Industrial    | SMD           | 7.2 A                  | 5.3 A                | 4.5 V                 | 5.5 V                 | Compliant | -40 °C                       | 125 °C                       | 30 MHz                     |

| RRP63175-NM0          | Industrial    | SMD           | 7.2 A                  | 5.3 A                | 4.5 V                 | 5.5 V                 | Compliant | -40 °C                       | 125 °C                       | 30 MHz                     |

# A.4 Footprint Design Information

### A.4.1 6-SCTDFN

| IPC Footprint Type |     | Package Code/ POD Number | Number of Pins |  |

|--------------------|-----|--------------------------|----------------|--|

|                    | DFN | L6.2x2A/DW0006AA         | 6              |  |

| Description                                          | Dimension | Value (mm) | Diagram            |

|------------------------------------------------------|-----------|------------|--------------------|

| Minimum body span (vertical side)                    | Dmin      | 1.95       | 1                  |

| Maximum body span (vertical side)                    | Dmax      | 2.05       | [ <del></del>      |

| Minimum body span (horizontal side)                  | Emin      | 1.95       | 11                 |

| Maximum body span (horizontal side)                  | Emax      | 2.05       | n   17             |

| Minimum Lead Width                                   | Bmin      | 0.35       | n-1 2              |

| Maximum Lead Width                                   | Bmax      | 0.45       | <u>+</u> □ □ □ □ □ |

| Minimum Lead Width                                   | Lmin      | 0.25       | Pitch              |

| Maximum Lead Width                                   | Lmax      | 0.35       | * - I              |

| Maximum Height                                       | Amax      | 0.80       |                    |

| Minimum Standoff Height                              | A1min     | 0.00       | \$B                |

| Minimum Lead Thickness                               | cmin      | 0.153      | —E2—→              |

| Maximum Lead Thickness                               | cmax      | 0.253      | Bottom View        |

| Number of pins                                       | PinCount  | 6          |                    |

| Distance between the center of any two adjacent pins | Pitch     | 0.65       | <b>↑</b>           |

| Minimum thermal pad size (vertical side)             | D2min     | 1.50       | <b>1</b> ★         |

| Maximum thermal pad size (vertical side)             | D2max     | 1.70       | 7 ↓ <u>↓</u>       |

| Minimum thermal pad size (vertical side)             | E2min     | 0.80       |                    |

| Maximum thermal pad size (vertical side)             | E2max     | 1.00       | Side View          |

| Recommended Land Pattern                            |           |            |                            |  |  |

|-----------------------------------------------------|-----------|------------|----------------------------|--|--|

| Description                                         | Dimension | Value (mm) | Diagram                    |  |  |

| Row spacing. Distance between pad centers.          | С         | 1.85       | <u></u> Z——→               |  |  |

| Distance between pads. Measured from outside edges. | Z         | 2.30       | C T                        |  |  |

| Distance between pads. Measured from inside edges.  | G         | 1.40       |                            |  |  |

| Pad Width                                           | Х         | 0.40       |                            |  |  |

| Pad Length                                          | Y         | 0.45       | Pitch  Pitch  PCB Top View |  |  |

## **Package Outline Drawing**

L6.2x2A DW0006AA

$6\text{-SCTDFN}\ 2.0\ x\ 2.0\ x\ 0.8\ mm\ Body,\ 0.65\ mm\ Pitch$ Rev 02, Feb 18, 2025

### Recommended Land Pattern

#### Notes:

- JEDEC compatible. 1.

- All dimensions are in mm and angles are in degrees.

- Use ±0.05 mm for the non-toleranced dimensions.

- Numbers in ( ) are for references only.

Detail A: Wettable Flank

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.