## SLG47912 Datasheet

1K Configurable Digital Array

### Description

The SLG47912 is a small size, low-power devices for common FPGA applications. The user creates their circuit design by programming the One Time Programmable (OTP) Non-Volatile Memory (NVM) or providing bitstream through SPI Interface to configure the FPGA Core, the IO pins, and the macrocells of the chip. This highly versatile device allows a wide variety of FPGA applications to be implemented.

### Features

- Dense Array of Configurable Logic

- 1120 5-bit LUTs

- 1120 DFFs

- 5 kb Distributed Memory

- 32 kb BRAM

- Power Supply Domains

- Two separate domains (20 GPIOs per domain)

- $V_{DDIO0}$  and  $V_{DDIO1}$ : 1.71 V to 3.465 V

- $V_{DDC}$ : 1.1 V  $\pm$  5 %

- Clocking

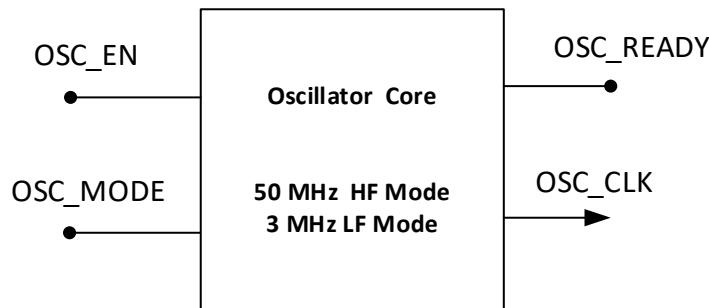

- High-frequency Oscillator

- 50 MHz High-frequency Oscillator

- 3 MHz Low-frequency Mode

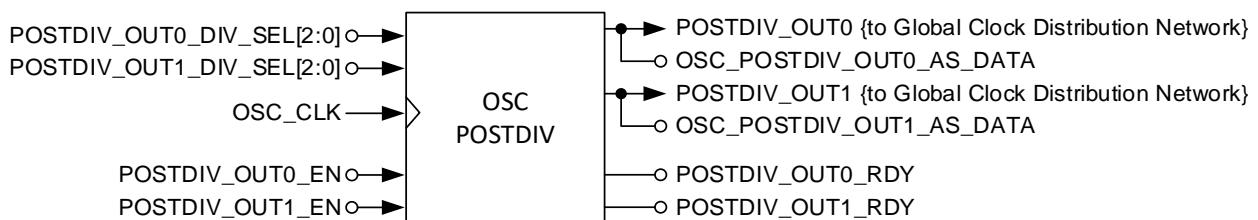

- Oscillator Post divider

- Divide Oscillator clock by a power of 2 (range 1 to 128)

- Two independent outputs

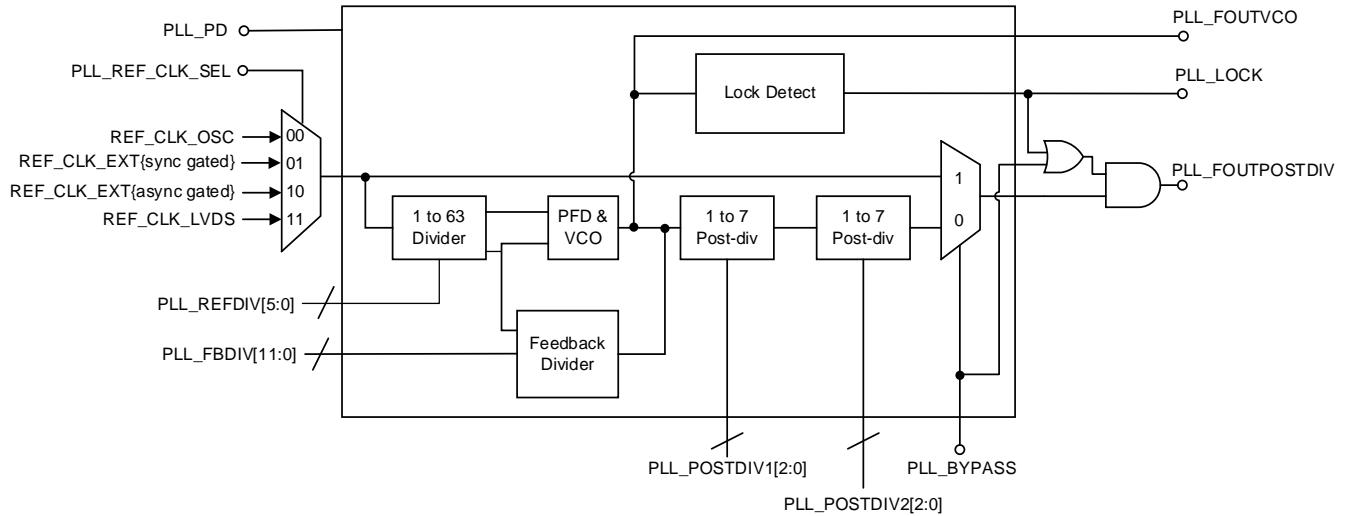

- Phase-locked Loop (PLL)

- Input from external source, internal oscillator or LVDS Differential clock

- Power-on Reset (POR)

- Flexible power-consumption control:

- FPGA Core power control

- Clock sources power control

- BRAM deep-sleep/power-gated modes

- General Purpose IOs

- 40 GPIOs

- Flexible configuration options:

- Selectable drive strength (4/8/12 mA)

- Optional pull-up – 1x or 2x

- Optional pull-up control from FPGA Core

- Optional Schmitt Trigger input

- Six LVDS Capable GPIOs (three true-LVDS pairs up to 100 Mbps)

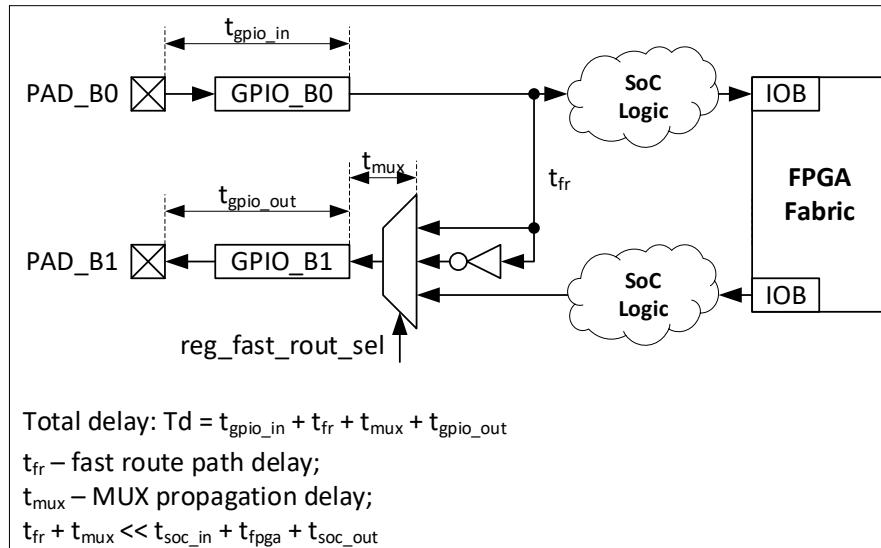

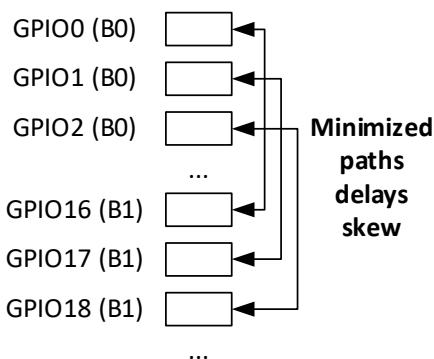

- Fast Routing capability between pairs of GPIO located in different IO voltage domains

- Bitstream security features:

- CRC Integrity Check

- AES Decryption

- Configuration Options

- OTP Mode – load from built-in OTP memory

- SPI Controller (Master) Mode – load from external Flash memory

- SPI Target (Slave) Mode – load from external source (MCU host)

- Boot control logic: can address up to 16 different bitstreams from external memory

- Two idle low-power modes:

- Sleep mode when configuration is being retained and no device re-configuration is needed

- Reset mode when device re-configuration is required after exit from this mode

- Possibility to retain GPIOs and BRAM states in both low power modes

- Low power consumption in both modes (<85  $\mu$ A)

- Operating Temperature Range: -40 °C to 85 °C

- RoHS Compliant/Halogen-Free

- Available Package

- 48-pin QFN: 6.0 mm x 6.0 mm, 0.4 mm pitch

- 48-pin WLCSP: 3.24 mm x 2.57 mm, 0.35 mm pitch

### Applications

- Consumer Electronics

- Data Communications Equipment

- Handheld and Portable Electronics

- Notebooks and Tablet PCs

- Industrial Instrumentation and Control

## Contents

|                                                                                    |           |

|------------------------------------------------------------------------------------|-----------|

| <b>1. Overview .....</b>                                                           | <b>7</b>  |

| 1.1    Block Diagram.....                                                          | 7         |

| 1.2    Block Description.....                                                      | 8         |

| <b>2. Pin Information .....</b>                                                    | <b>10</b> |

| 2.1    Pin Assignments - LQFN-48 .....                                             | 10        |

| 2.2    Pin Assignments - WLCSP-48 .....                                            | 13        |

| 2.3    Pin Descriptions .....                                                      | 16        |

| <b>3. Specifications.....</b>                                                      | <b>19</b> |

| 3.1    Absolute Maximum Ratings .....                                              | 19        |

| 3.2    ESD Ratings.....                                                            | 19        |

| 3.3    Recommended Operating Conditions .....                                      | 20        |

| 3.4    Thermal Specifications .....                                                | 20        |

| 3.5    Electrical Specifications .....                                             | 20        |

| 3.5.1    PLL Specifications .....                                                  | 20        |

| 3.5.2    GPIOs Specifications .....                                                | 21        |

| 3.5.3    GPIO Pull-Up Resistance Specifications .....                              | 27        |

| 3.5.4    Oscillator Specifications.....                                            | 27        |

| 3.5.5    LVDS Specifications .....                                                 | 28        |

| 3.5.6    Power-On Reset Specifications.....                                        | 30        |

| 3.5.7    Estimated Current Consumption of Internal Blocks.....                     | 31        |

| 3.5.8    Timing Specifications .....                                               | 31        |

| 3.5.9    Supply Current.....                                                       | 32        |

| 3.5.10    BRAM Characteristics.....                                                | 33        |

| 3.5.11    nRST (PWR) and nSLEEP (EN) Specifications .....                          | 33        |

| <b>4. General Purpose Input (GPIO) Buffers .....</b>                               | <b>35</b> |

| 4.1    CMOS GPIO with Configurable Drive Strength.....                             | 35        |

| 4.2    GPIO with LVDS Capability .....                                             | 37        |

| 4.3    GPIO Paths to/from the FPGA Core.....                                       | 41        |

| 4.4    Fast Routing between $V_{DDIO}$ Banks .....                                 | 41        |

| 4.5    Typical IO Behavior During Power-up .....                                   | 44        |

| 4.6    Supported Standards .....                                                   | 44        |

| <b>5. FPGA Core.....</b>                                                           | <b>45</b> |

| 5.1    Introduction .....                                                          | 46        |

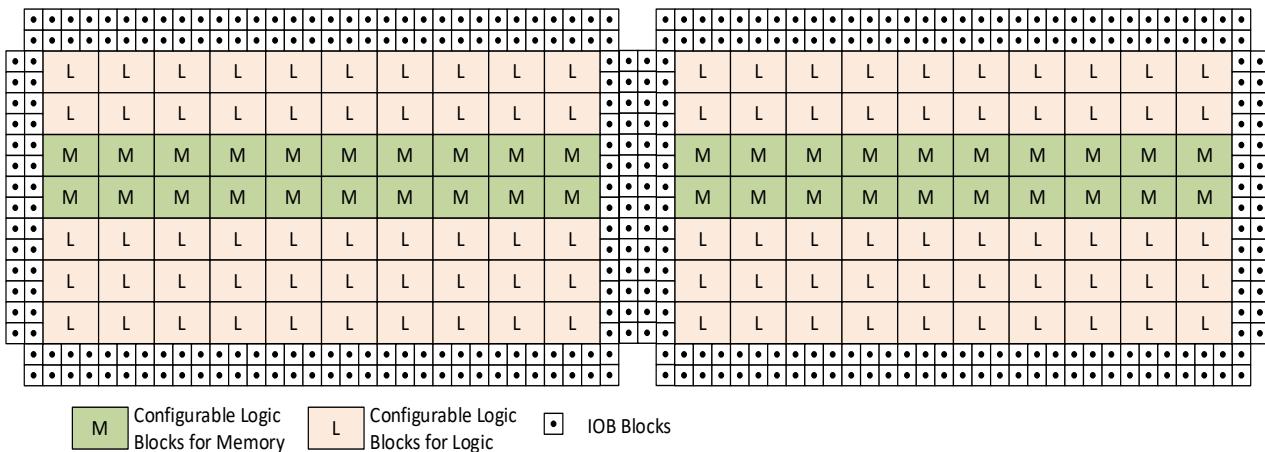

| 5.2    FPGA Core Composition .....                                                 | 46        |

| 5.3    Configurable Logic Blocks .....                                             | 46        |

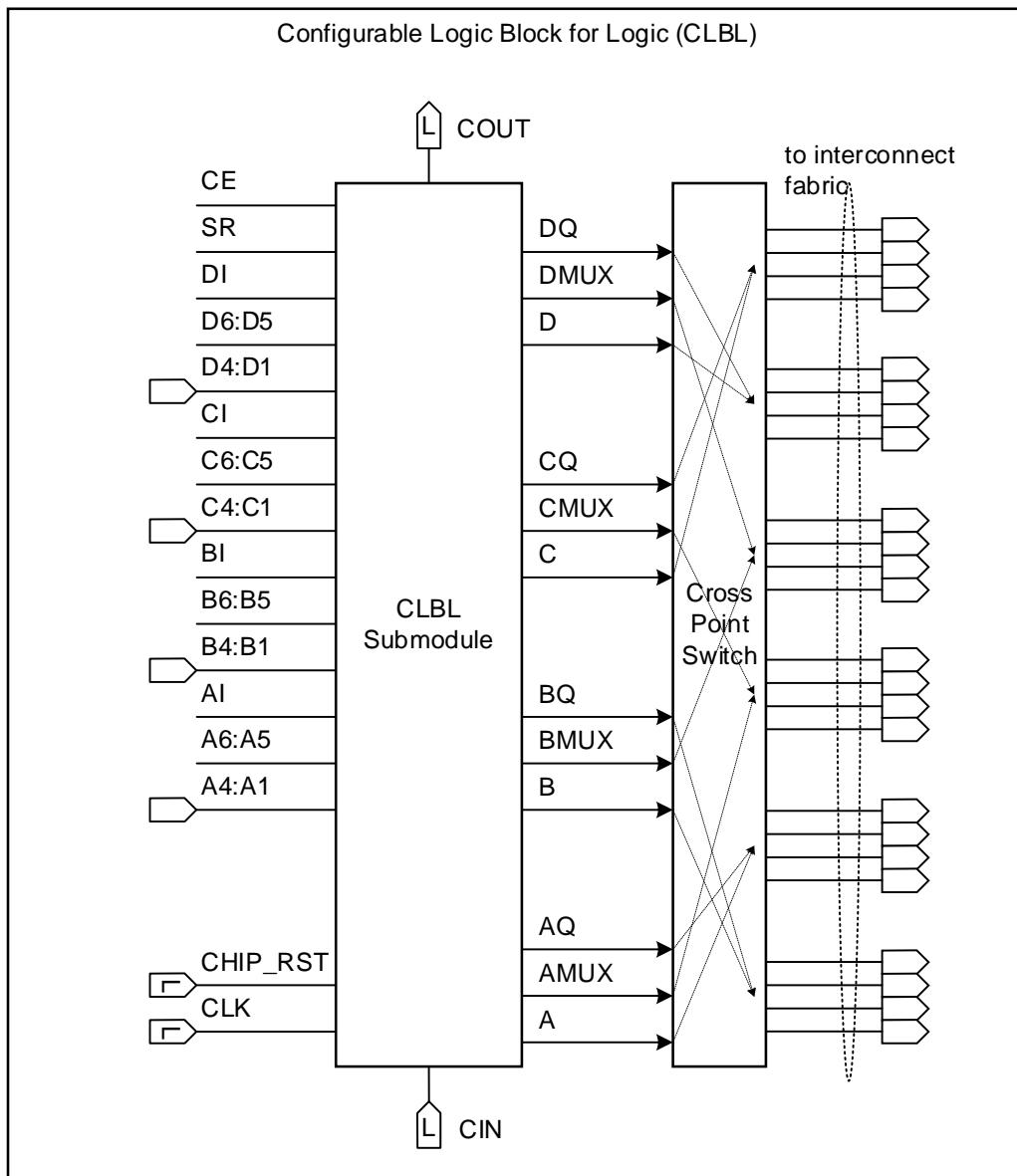

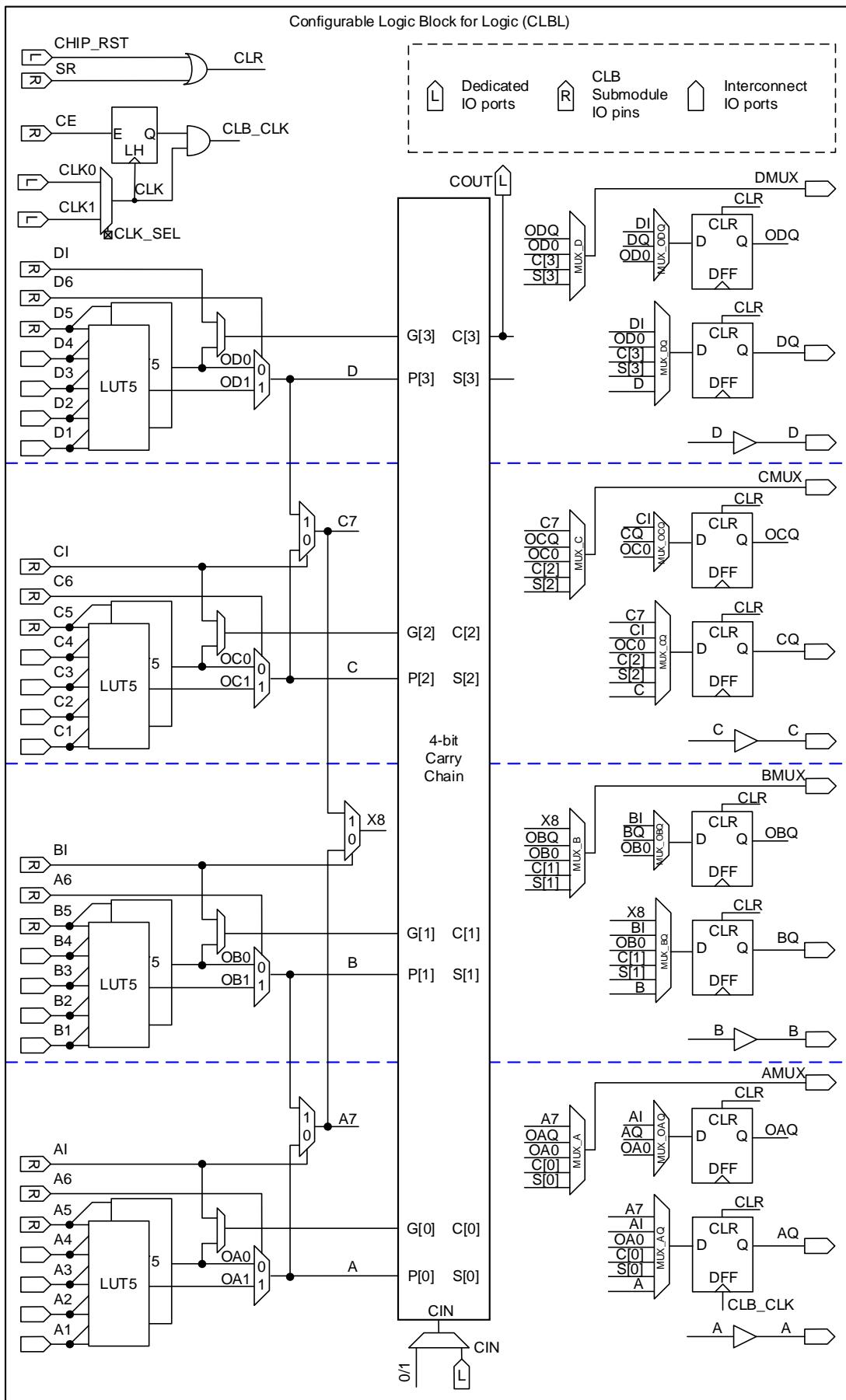

| 5.3.1    Configurable Logic Blocks for Logic.....                                  | 47        |

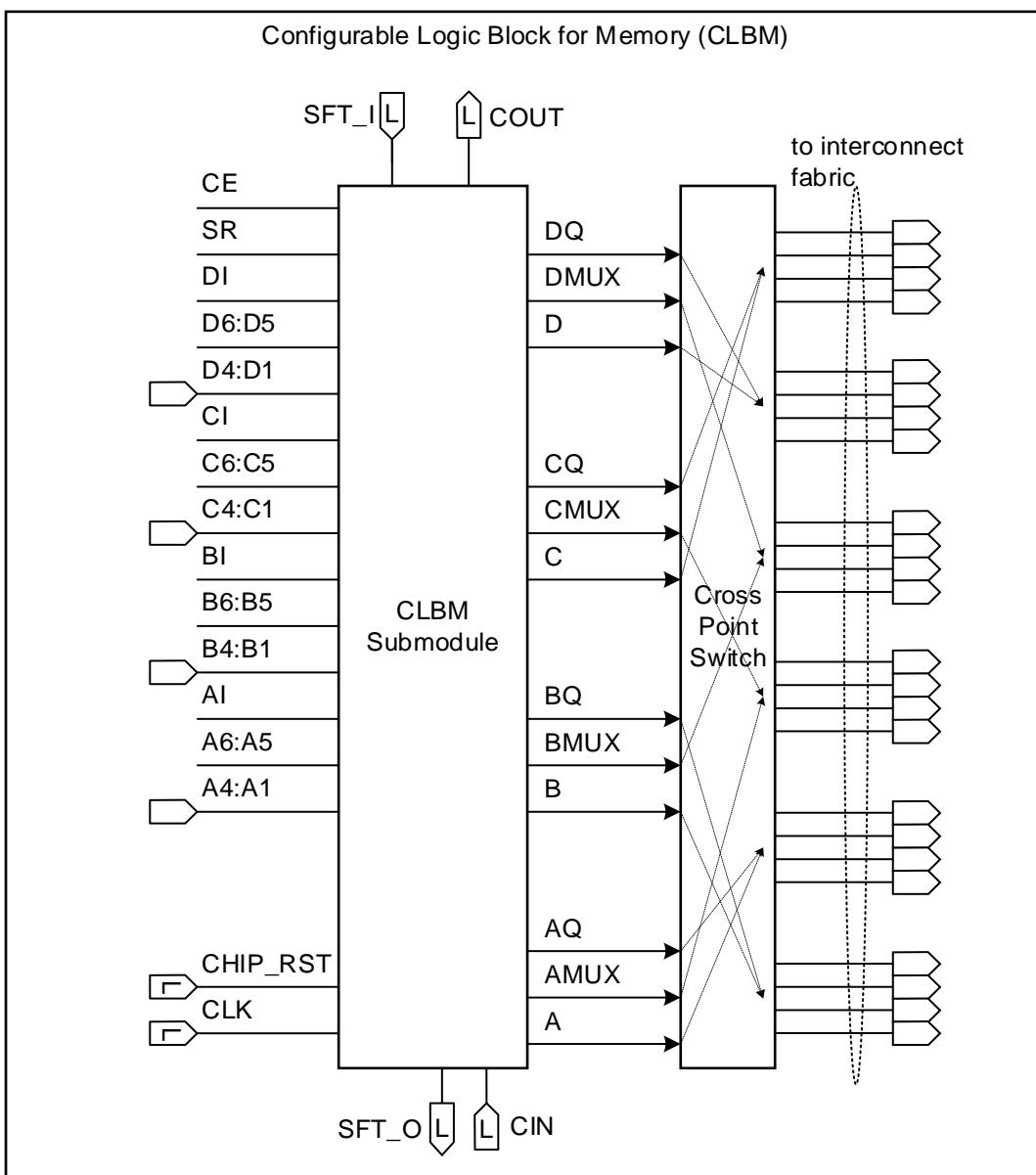

| 5.3.2    Configurable Logic Blocks for Memory .....                                | 49        |

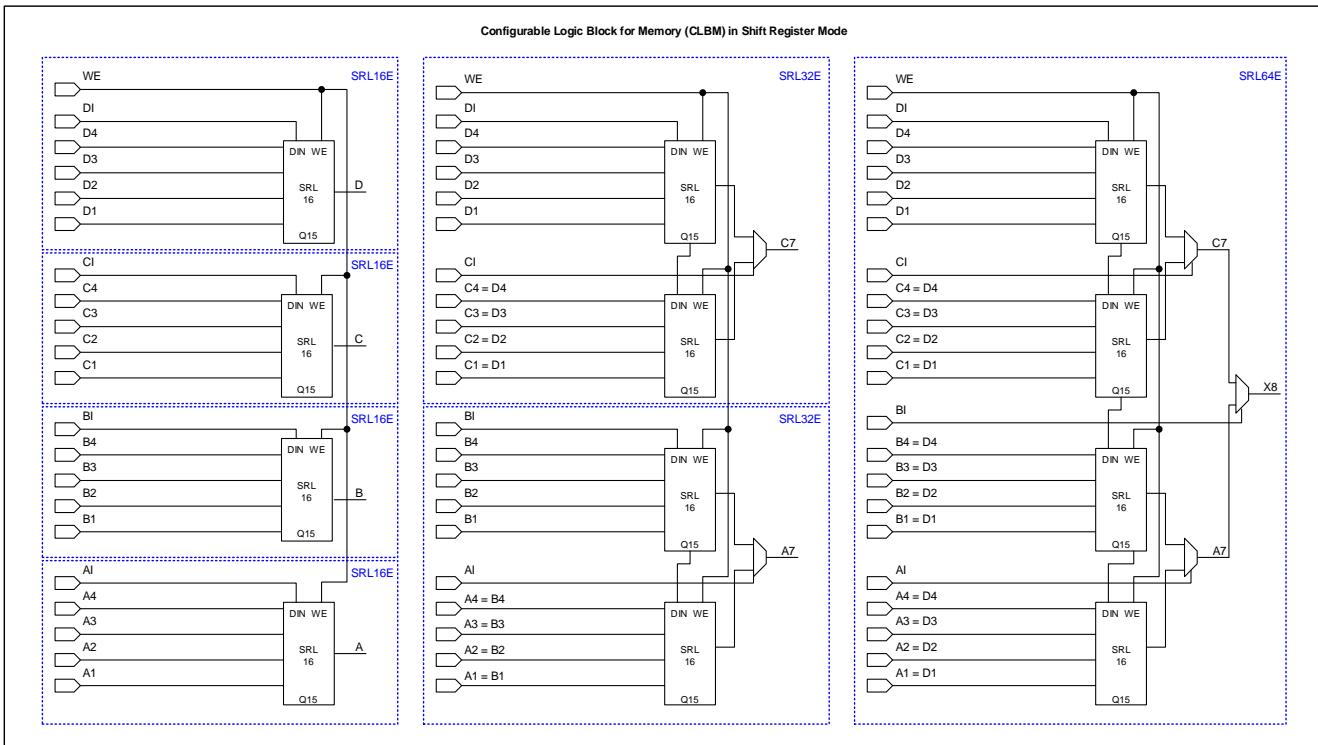

| 5.3.2.1    Configurable Logic Block for Memory Used in Shift Register Mode .....   | 50        |

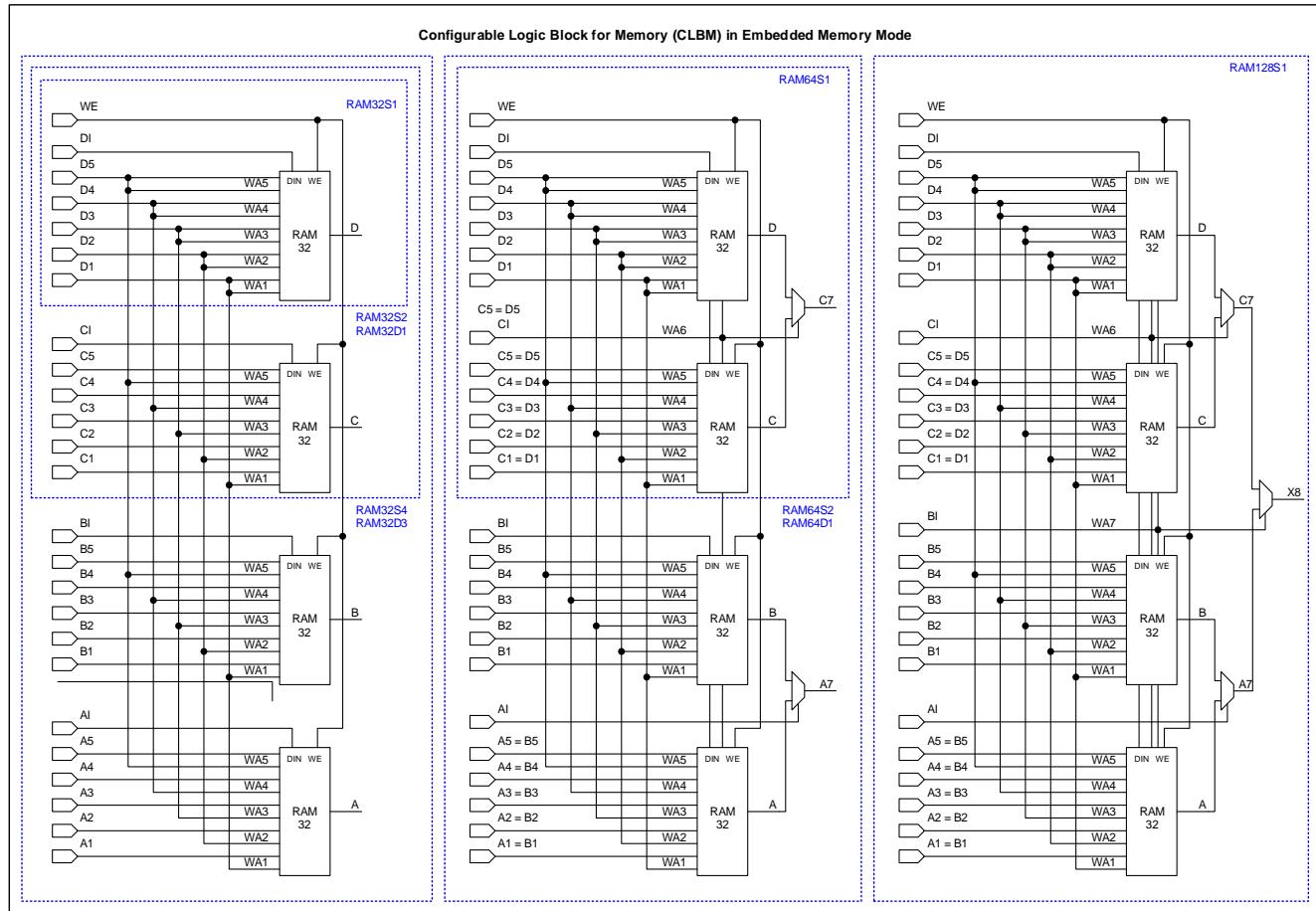

| 5.3.2.2    Configurable Logic Blocks for Memory used in Embedded Memory Mode ..... | 51        |

| 5.4    Core IO Buffers (IOBs).....                                                 | 52        |

| 5.5    Power Management and Operating Modes .....                                  | 56        |

| 5.5.1    FPGA Core Power-On Reset .....                                            | 56        |

| 5.5.2    Configuration Mode .....                                                  | 56        |

| 5.5.3    Functional Mode .....                                                     | 56        |

| 5.5.4    nSLEEP: Sleep (Retention) Mode .....                                      | 56        |

| 5.5.5    nRST: Reset Mode .....                                                    | 56        |

| 5.6    Typical Building Block Performance .....                                    | 57        |

| 5.7    OTP User Area Access.....                                                   | 57        |

| <b>6. Clocking.....</b>                                                            | <b>59</b> |

---

|                              |                                                        |           |

|------------------------------|--------------------------------------------------------|-----------|

| 6.1                          | Clock Network .....                                    | 59        |

| 6.2                          | On-Chip Oscillator .....                               | 60        |

| 6.2.1                        | Overview .....                                         | 60        |

| 6.2.2                        | Signal Descriptions .....                              | 61        |

| 6.2.3                        | Oscillator Post Divider.....                           | 61        |

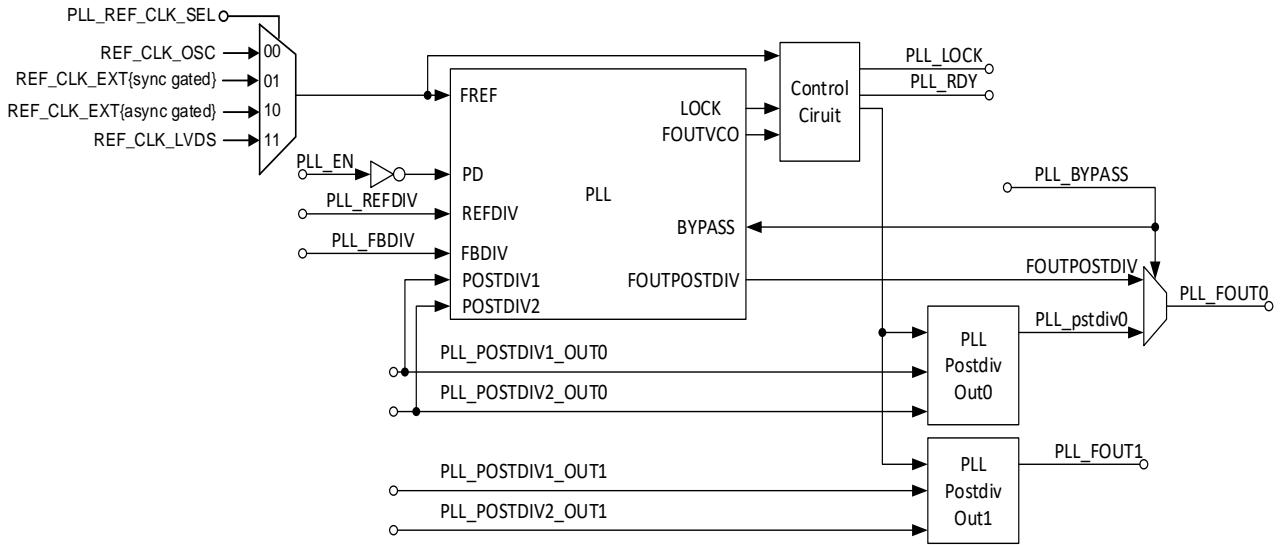

| 6.3                          | Phase-Locked Loop.....                                 | 62        |

| 6.3.1                        | Overview .....                                         | 62        |

| 6.3.2                        | PLL with External Post Dividers .....                  | 63        |

| 6.3.2.1                      | Signal Descriptions .....                              | 64        |

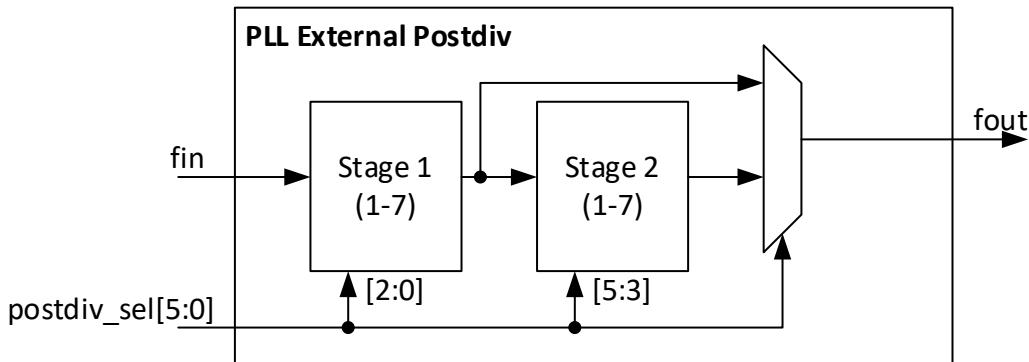

| 6.3.2.2                      | External POSTDIV Architecture .....                    | 65        |

| 6.3.2.3                      | External Post Divider Clock Phase Shift.....           | 65        |

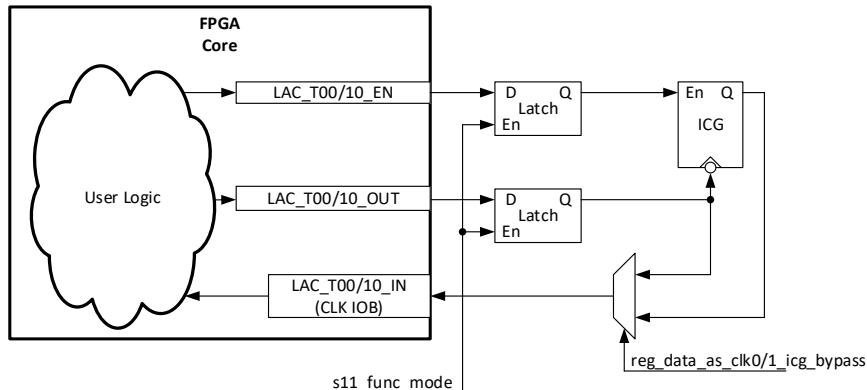

| 6.4                          | Logic-As-Clock .....                                   | 67        |

| <b>7.</b>                    | <b>Power Operating Modes.....</b>                      | <b>68</b> |

| 7.1                          | nRST Control Pin .....                                 | 68        |

| 7.2                          | nSLEEP control pin .....                               | 68        |

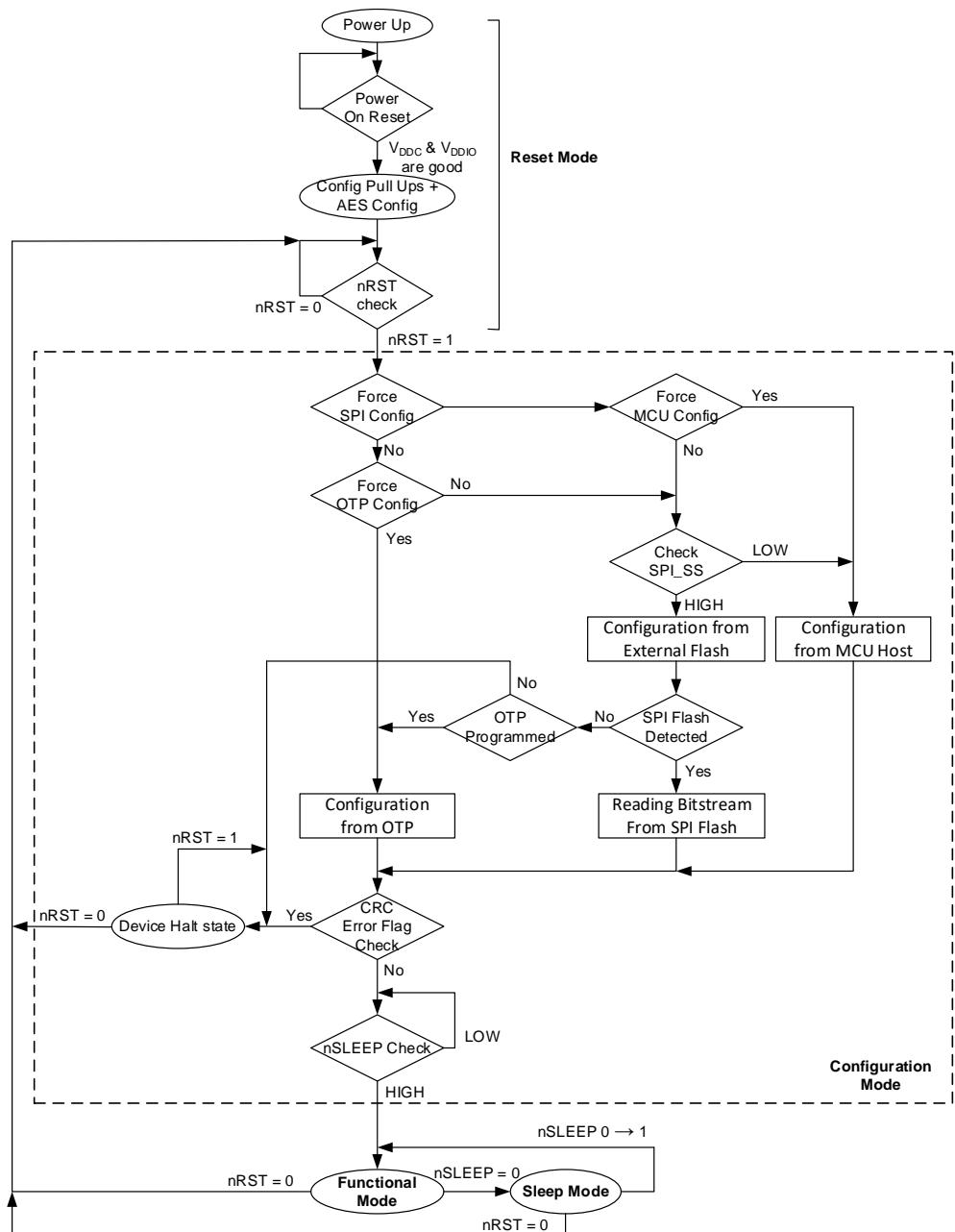

| 7.3                          | Power-up and Configuration Sequence.....               | 68        |

| <b>8.</b>                    | <b>LVDS Support.....</b>                               | <b>73</b> |

| 8.1                          | LVDS Input Paths.....                                  | 73        |

| 8.2                          | LVDS Output Paths .....                                | 74        |

| 8.3                          | LVDS Use Cases .....                                   | 75        |

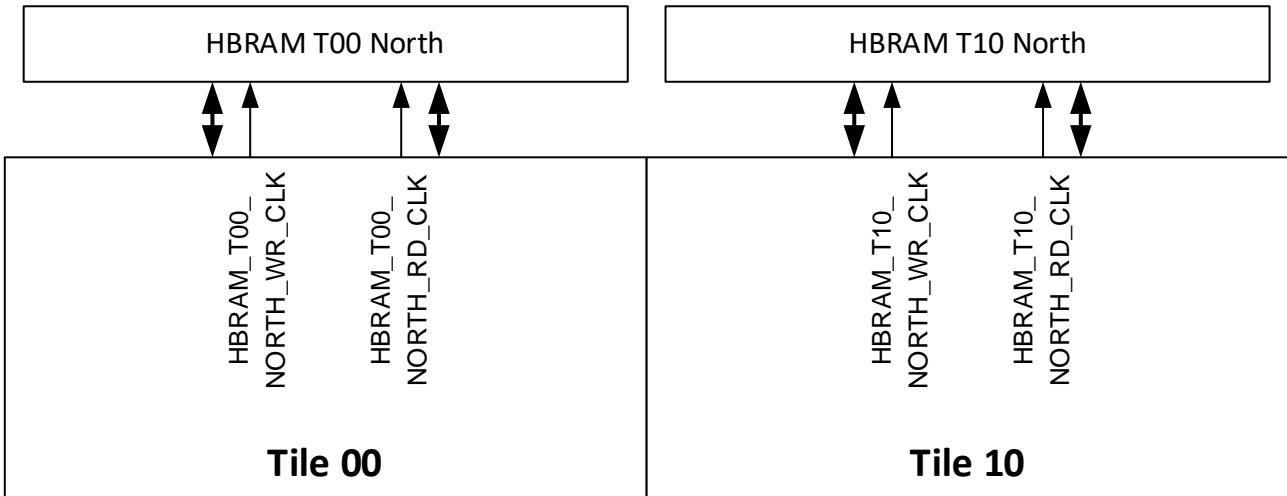

| <b>9.</b>                    | <b>Block RAM (BRAM).....</b>                           | <b>76</b> |

| 9.1                          | BRAM Instance .....                                    | 77        |

| 9.2                          | BRAM Considerations .....                              | 79        |

| 9.3                          | Address Extension.....                                 | 79        |

| 9.3.1                        | Write Operations for BRAM.....                         | 80        |

| 9.3.2                        | Read Operation for BRAM .....                          | 81        |

| 9.4                          | BRAM Initialization .....                              | 81        |

| <b>10.</b>                   | <b>Configuration Modes.....</b>                        | <b>83</b> |

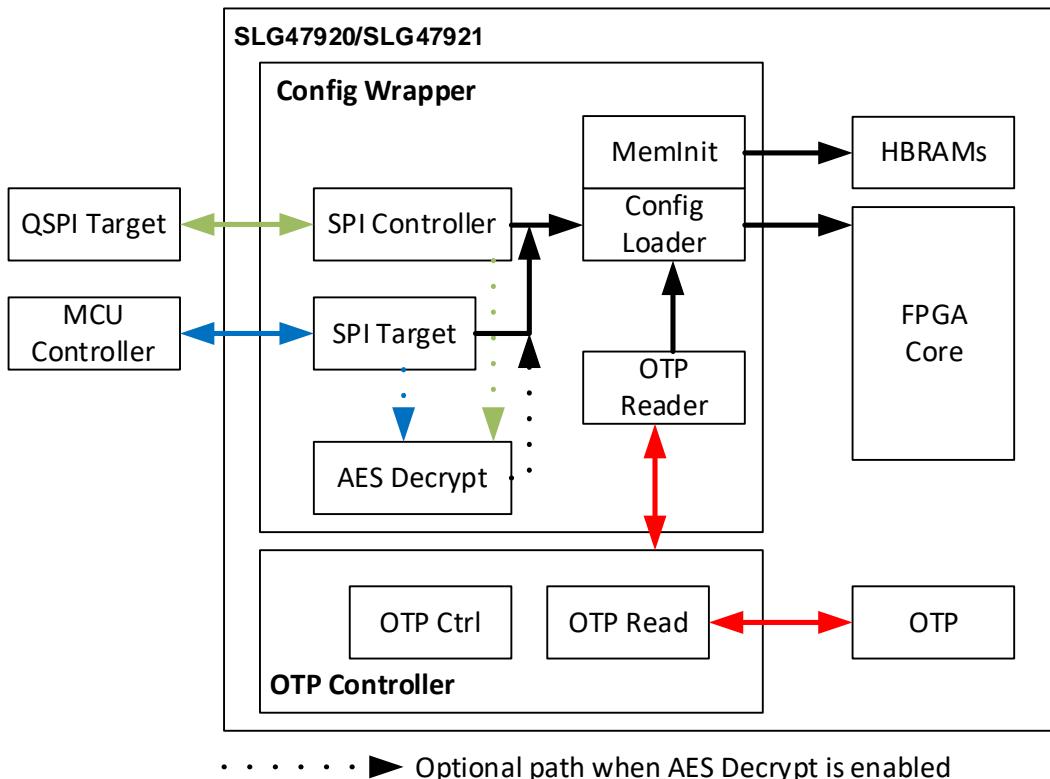

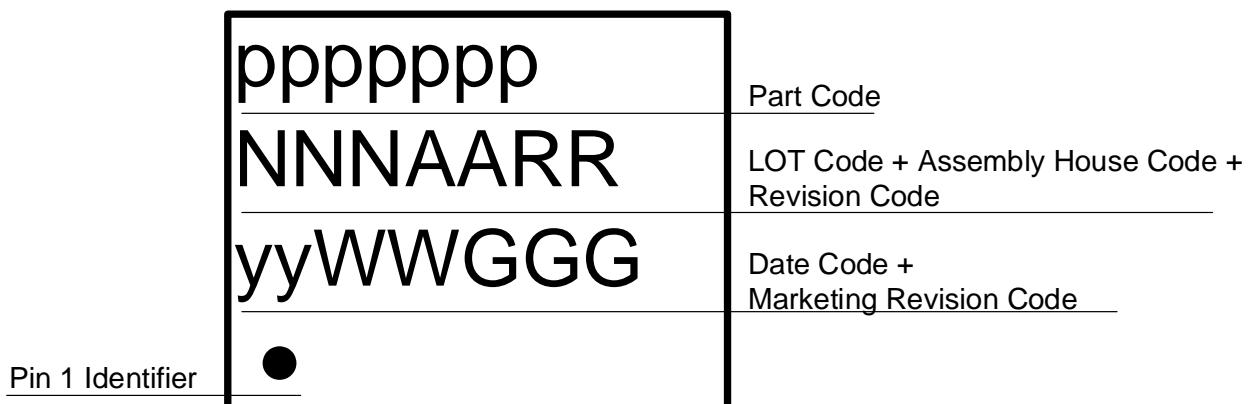

| <b>11.</b>                   | <b>Package Information.....</b>                        | <b>86</b> |

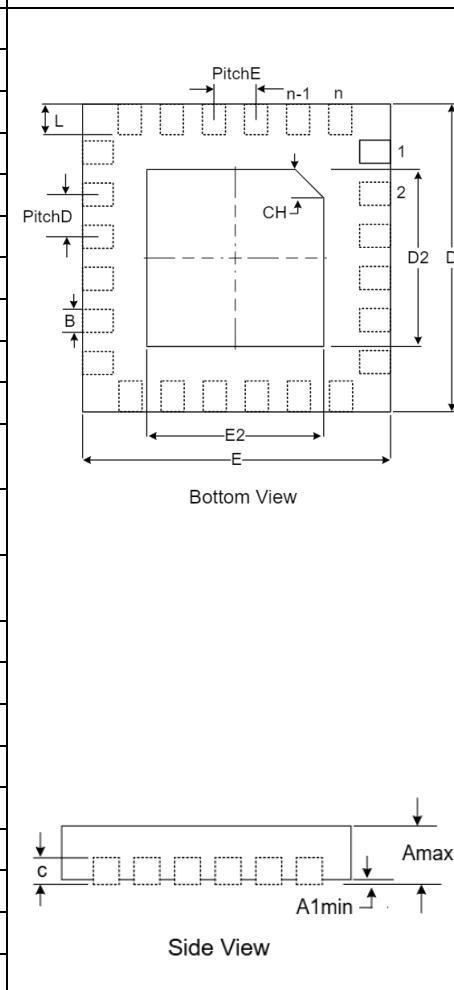

| 11.1                         | Package Outline Drawings.....                          | 86        |

| 11.1.1                       | LQFN 48L (6.0 mm x 6.0 mm x 0.85 mm, 0.4P) WB .....    | 86        |

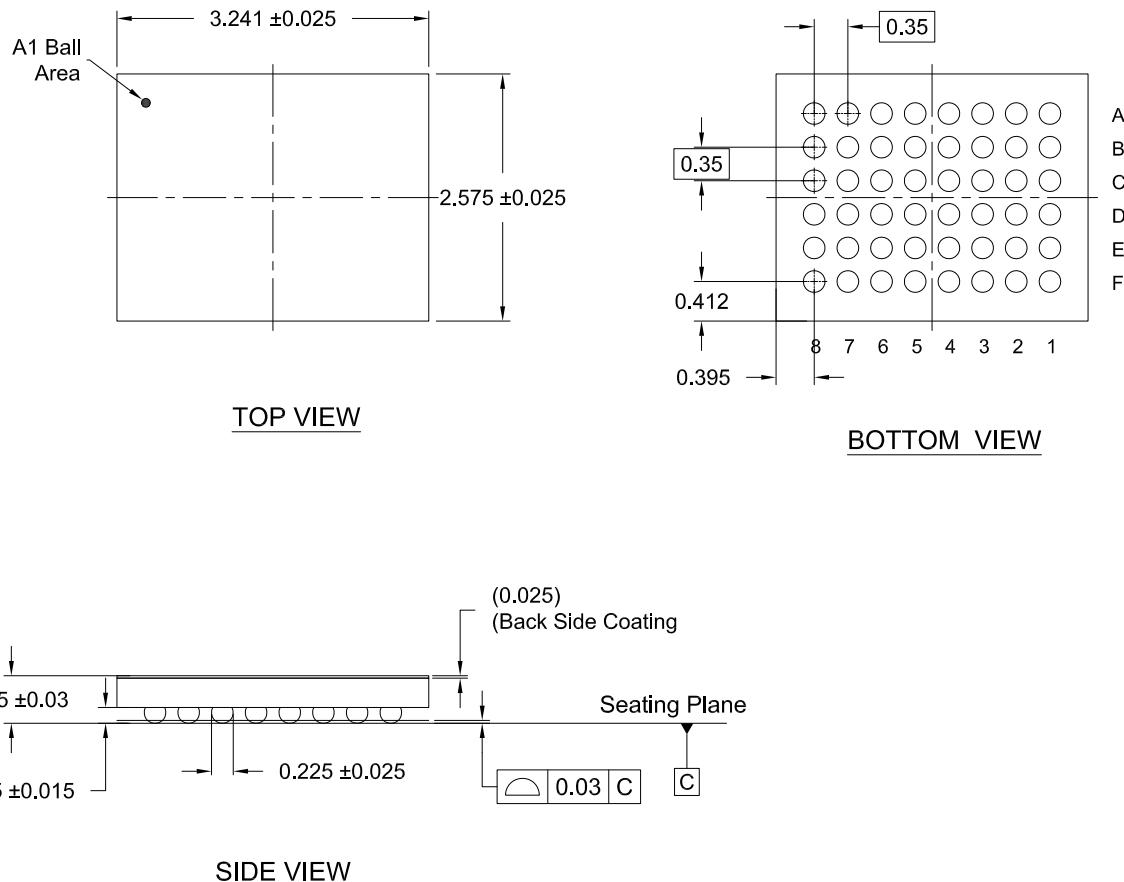

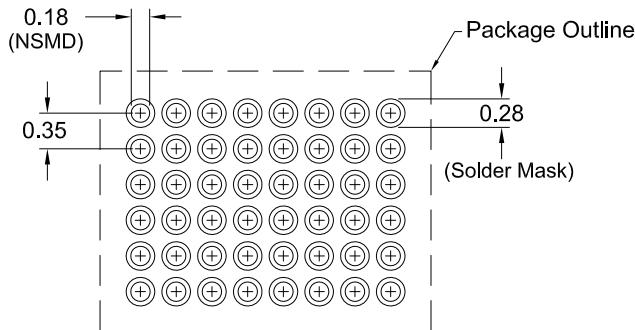

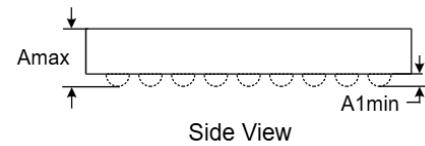

| 11.1.2                       | WLCSP 48L (3.241 mm x 2.575 mm x 0.495 mm, 0.35P)..... | 87        |

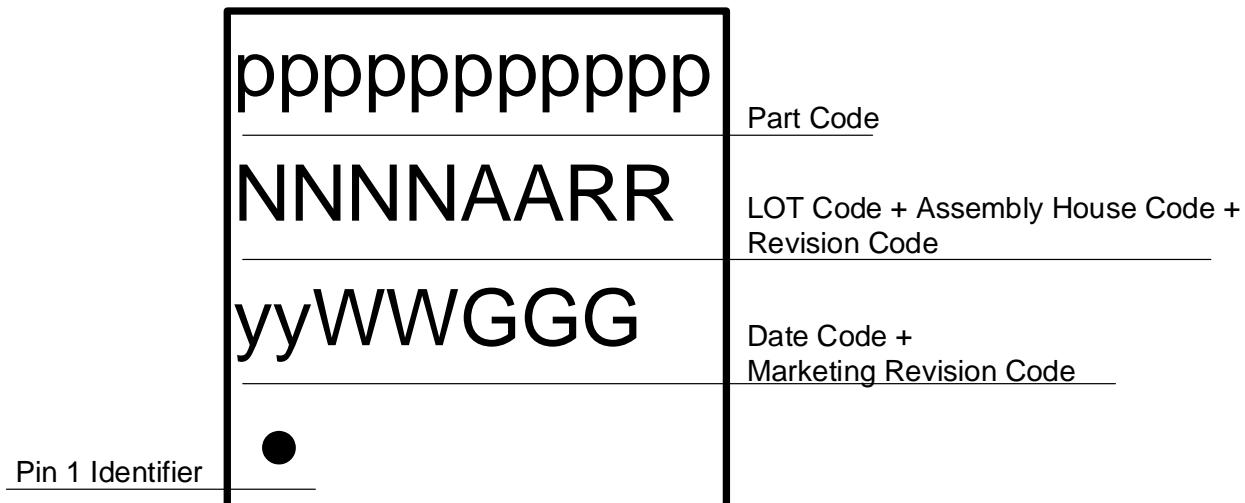

| 11.2                         | Package Top Marking.....                               | 88        |

| 11.2.1                       | LQFN 48L (6.0 mm x 6.0 mm x 0.85 mm, 0.4P) WB .....    | 88        |

| 11.2.2                       | WLCSP 48L (3.241 mm x 2.575 mm x 0.495 mm, 0.35P)..... | 88        |

| 11.3                         | Moisture Sensitivity Level.....                        | 88        |

| 11.4                         | Handling.....                                          | 89        |

| 11.5                         | Soldering Information.....                             | 89        |

| <b>12.</b>                   | <b>Thermal Guidelines .....</b>                        | <b>89</b> |

| <b>13.</b>                   | <b>Layout Guidelines.....</b>                          | <b>90</b> |

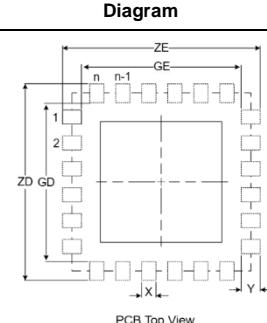

| 13.1                         | LQFN 48L (6.0 mm x 6.0 mm x 0.85 mm, 0.4P) WB.....     | 90        |

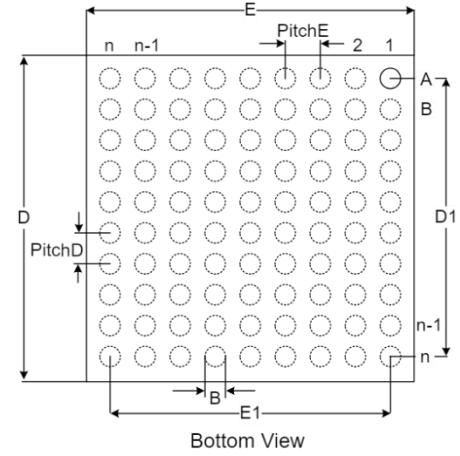

| 13.2                         | WLCSP 48L (3.241 mm x 2.575 mm x 0.495 mm, 0.35P)..... | 90        |

| <b>14.</b>                   | <b>Ordering Information.....</b>                       | <b>91</b> |

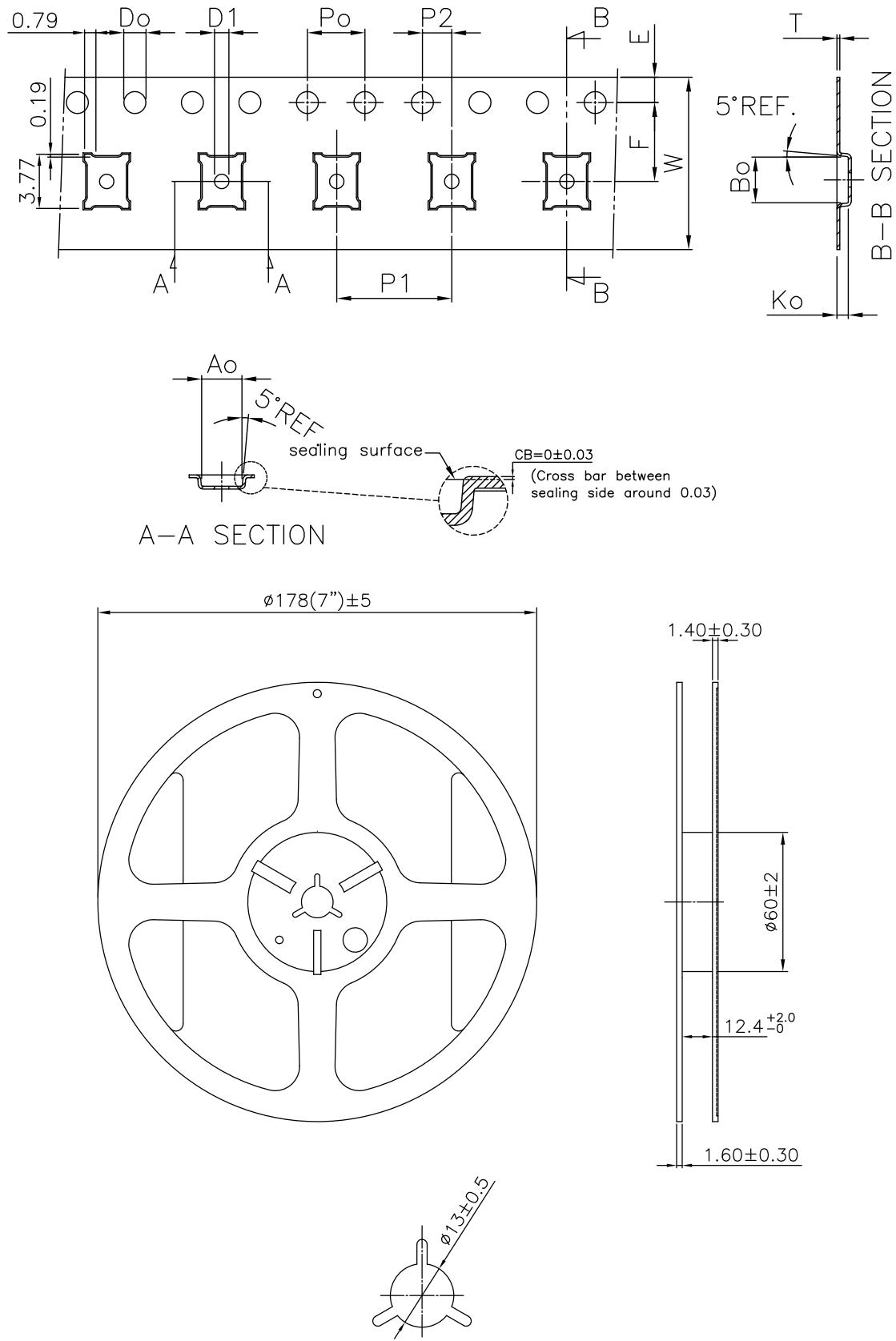

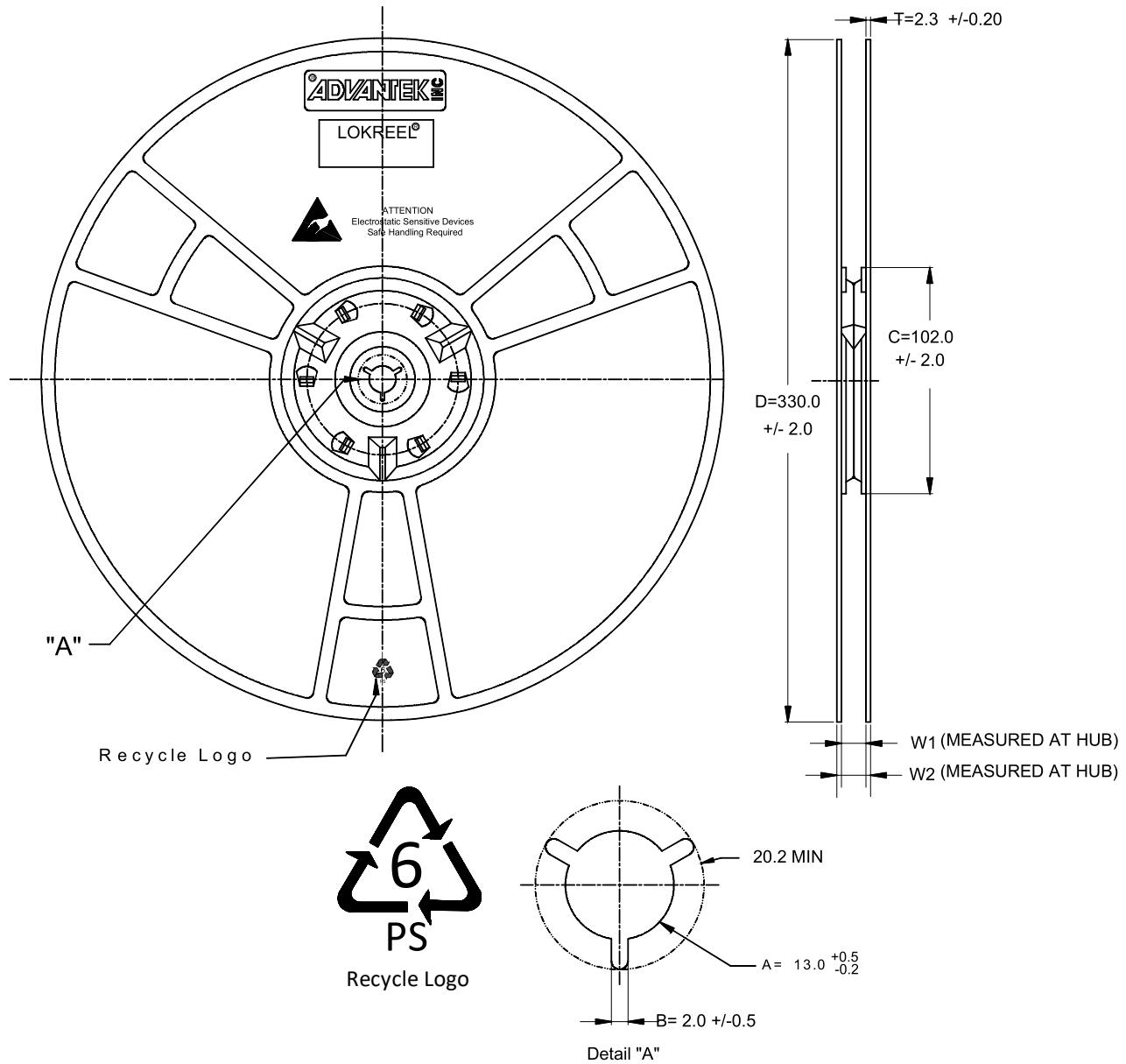

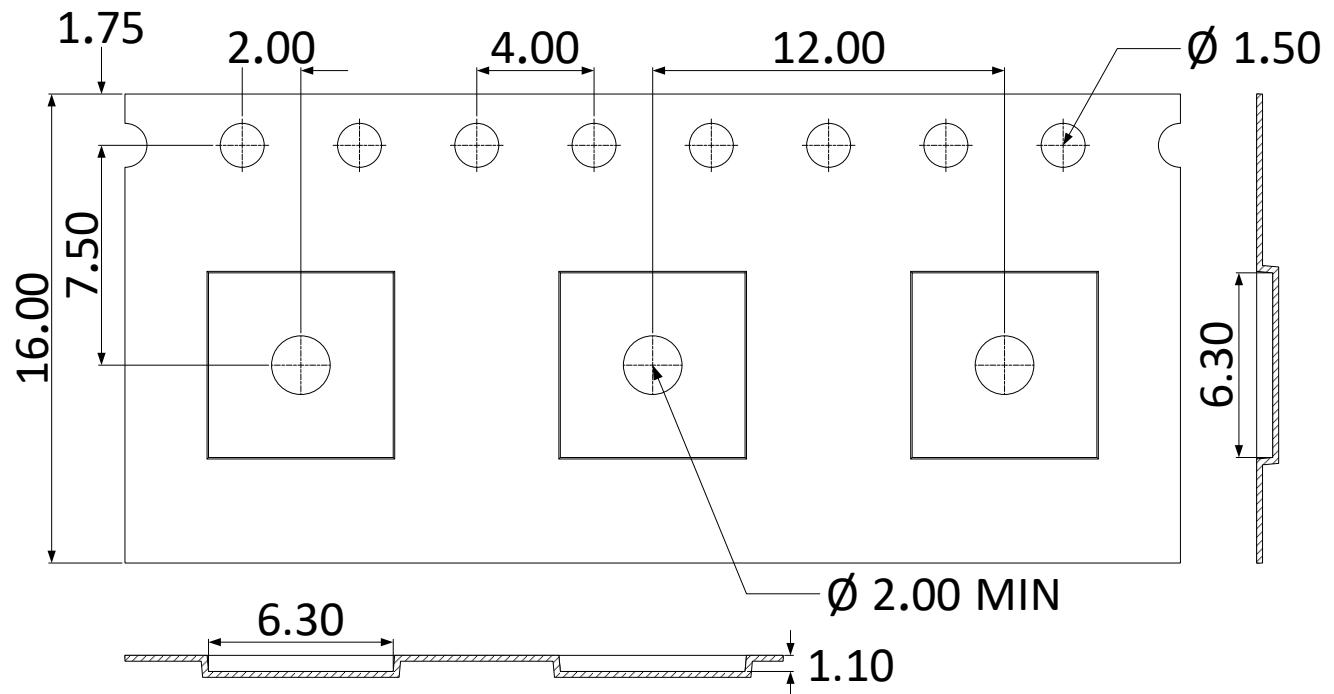

| 14.1                         | Tape and Reel Specifications .....                     | 91        |

| 14.2                         | Carrier Tape Drawing and Dimensions.....               | 91        |

| <b>Glossary .....</b>        |                                                        | <b>95</b> |

| <b>Revision History.....</b> |                                                        | <b>97</b> |

| <b>A.</b>                    | <b>ECAD Design Information .....</b>                   | <b>98</b> |

| A.1                          | Part Number Indexing.....                              | 98        |

| A.2                          | Symbol Pin Information.....                            | 98        |

---

|       |                                    |     |

|-------|------------------------------------|-----|

| A.2.1 | 48-LQFN .....                      | 98  |

| A.2.2 | 48-WLCSP .....                     | 99  |

| A.3   | Symbol Parameters .....            | 101 |

| A.4   | Footprint Design Information ..... | 102 |

| A.4.1 | 48-LQFN .....                      | 102 |

| A.4.2 | 48-WLCSP .....                     | 103 |

## Figures

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| Figure 1. Block Diagram .....                                                      | 7  |

| Figure 2. Pinout for 48-pin LQFN Package .....                                     | 10 |

| Figure 3. Pinout for 48-pin WLCSP Package (Top View).....                          | 13 |

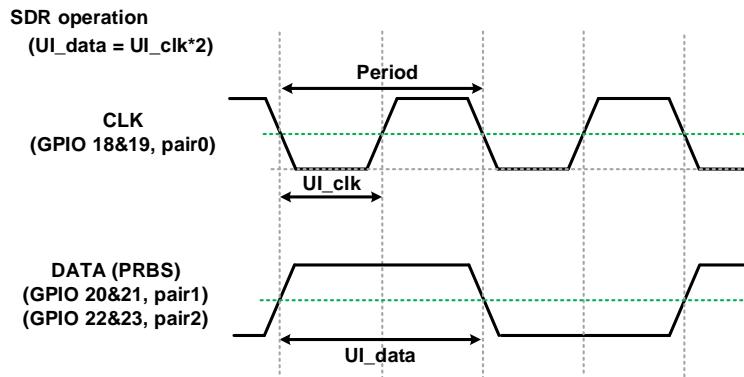

| Figure 4. SDR Data and Clock Rates .....                                           | 30 |

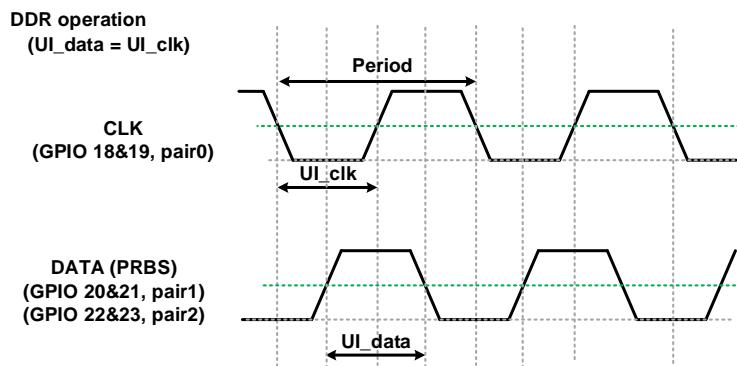

| Figure 5. DDR Data and Clock Rates .....                                           | 30 |

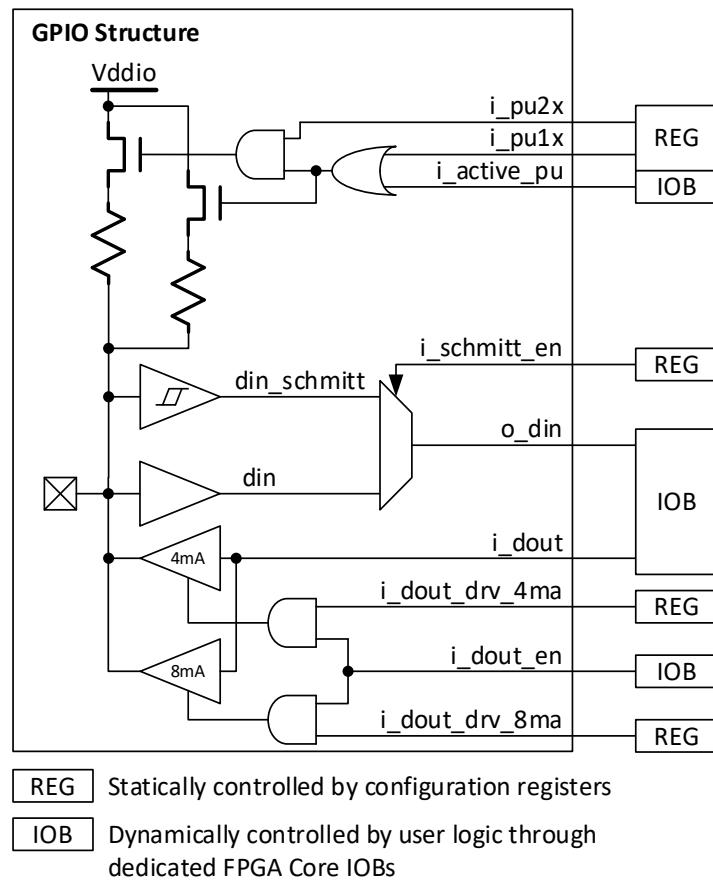

| Figure 6. GPIO Buffers.....                                                        | 35 |

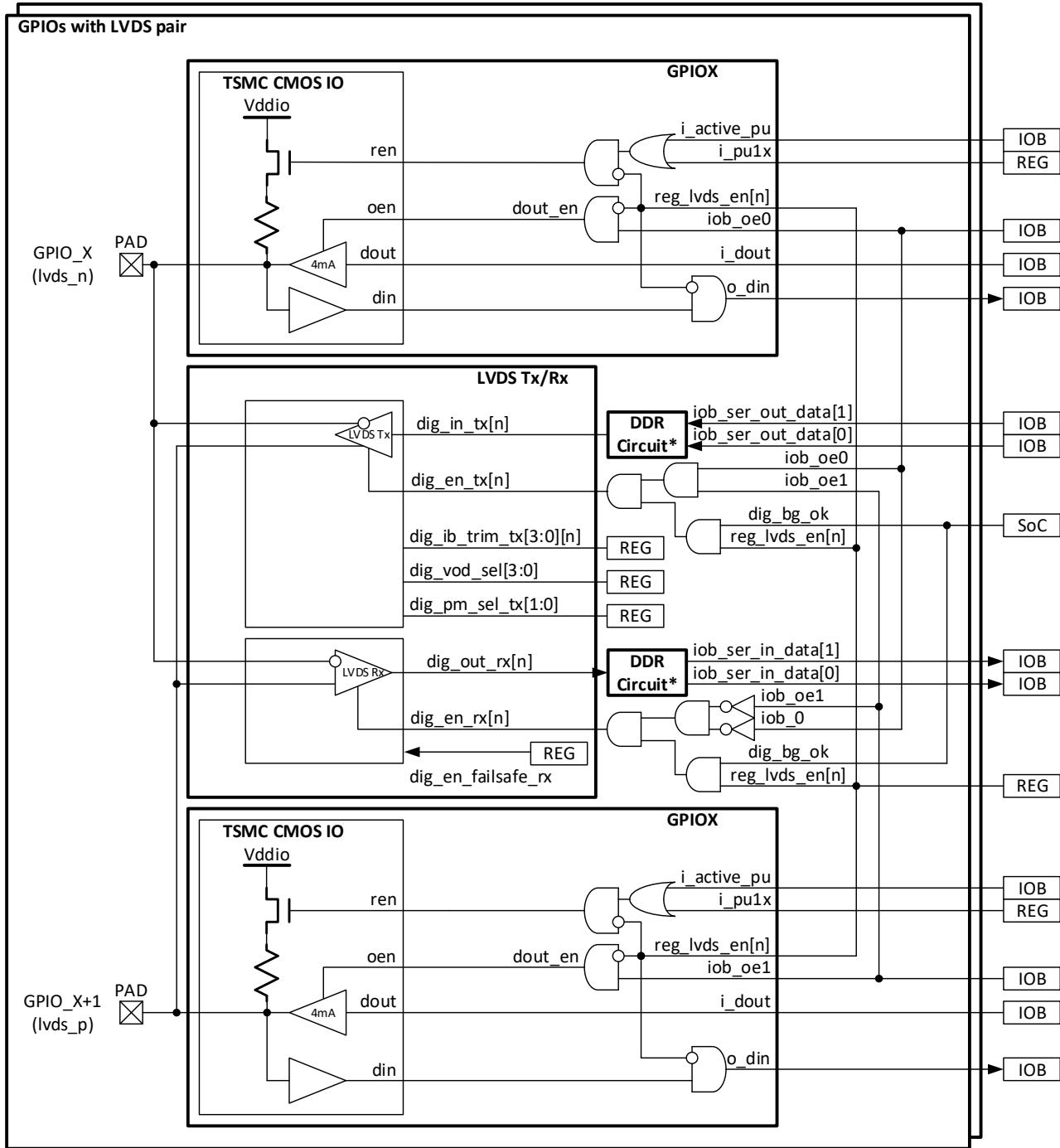

| Figure 7. GPIOs Pair with LVDS Capability.....                                     | 37 |

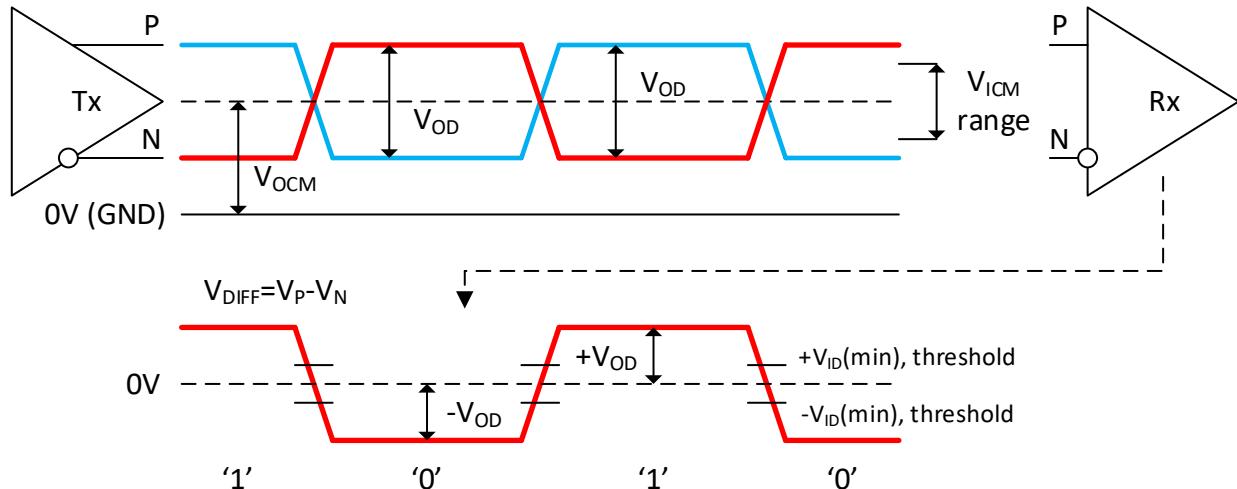

| Figure 8. LVDS Signal Levels .....                                                 | 38 |

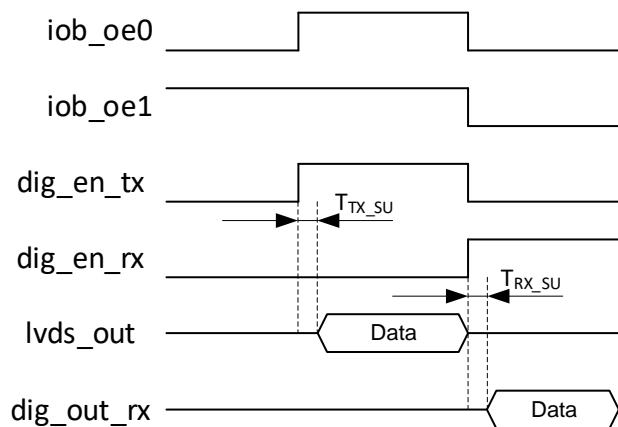

| Figure 9. LVDS Bi-Directional Operation.....                                       | 39 |

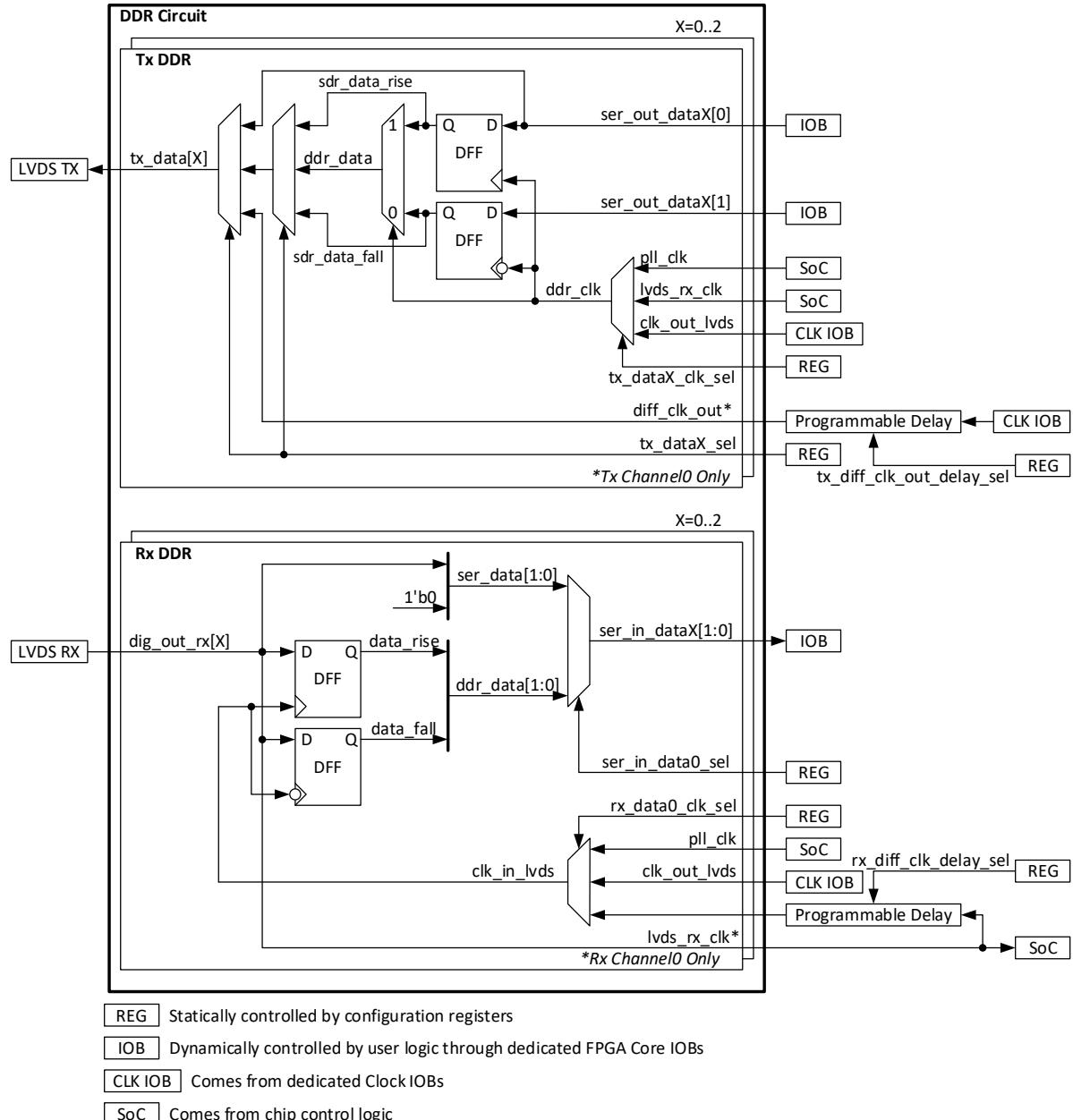

| Figure 10. DDR Circuit .....                                                       | 40 |

| Figure 11. LVDS Bias Circuit.....                                                  | 41 |

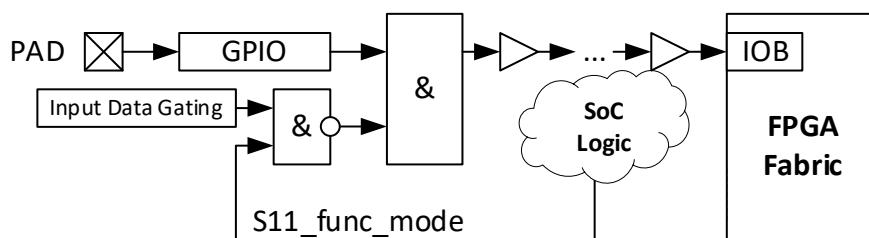

| Figure 12. Input Path Optional Gating.....                                         | 41 |

| Figure 13. Fast Routing.....                                                       | 42 |

| Figure 14. GPIOs Fast Routs Routing Topology .....                                 | 42 |

| Figure 15. Peripheral Connections to FPGA Core.....                                | 45 |

| Figure 16. FPGA Core.....                                                          | 46 |

| Figure 17. Configurable Logic Blocks for Logic .....                               | 47 |

| Figure 18. Configurable Logic Blocks for Logic (Cont.).....                        | 48 |

| Figure 19. Configurable Logic Blocks for Memory .....                              | 49 |

| Figure 20. Configurable Logic Blocks for Memory Used in Shift Register Mode .....  | 50 |

| Figure 21. Configurable Logic Blocks for Memory Used in Embedded Memory Mode ..... | 51 |

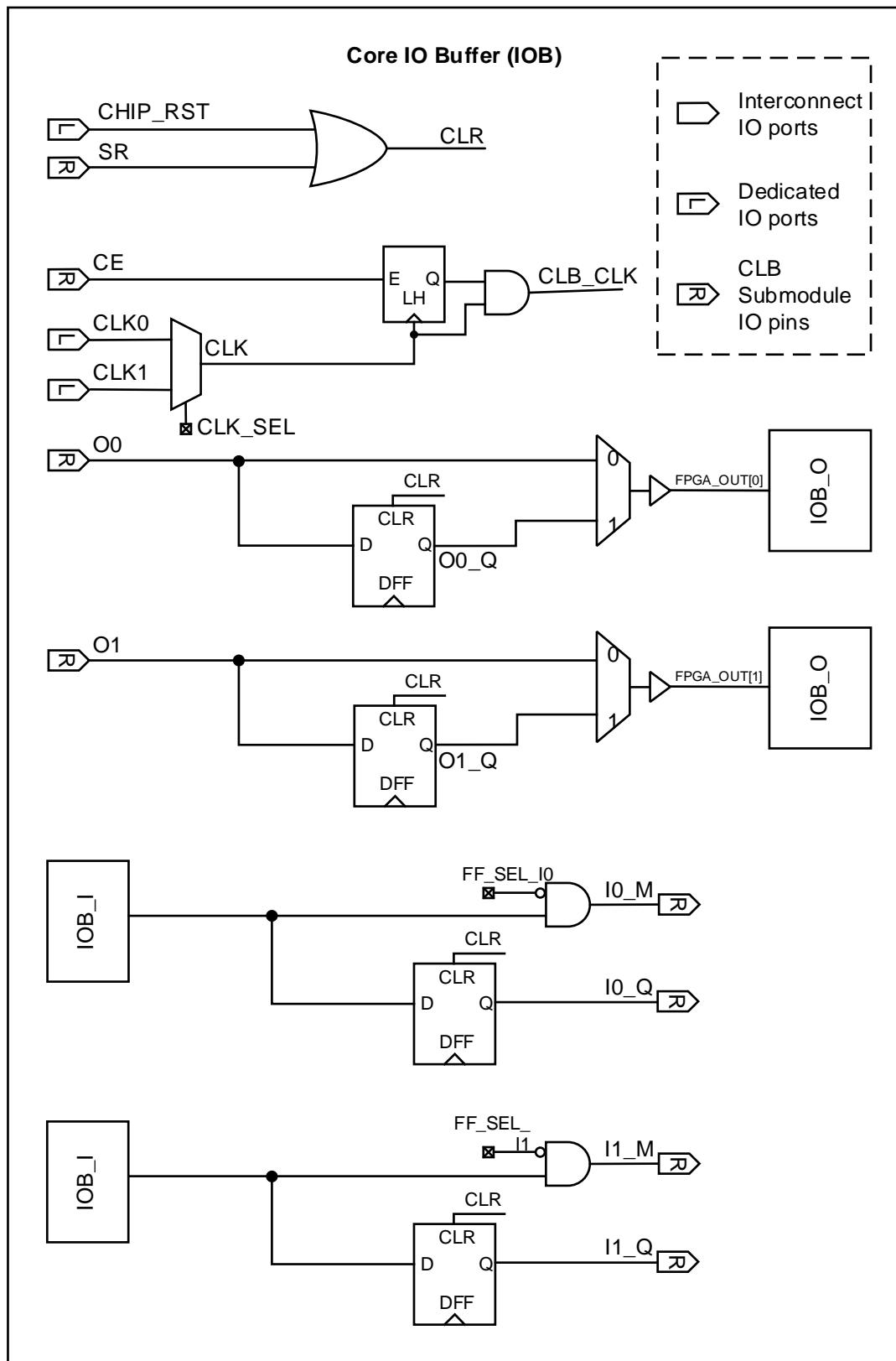

| Figure 22. Core IO Buffers .....                                                   | 55 |

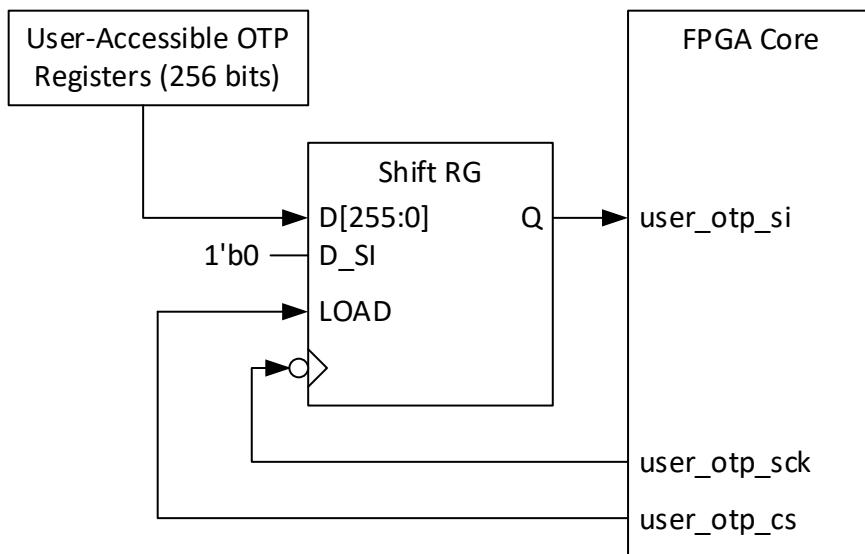

| Figure 23. Serial Interface for User Access to OTP .....                           | 58 |

| Figure 24. Serial Interface for User Accesses to OTP (Timing Diagram).....         | 58 |

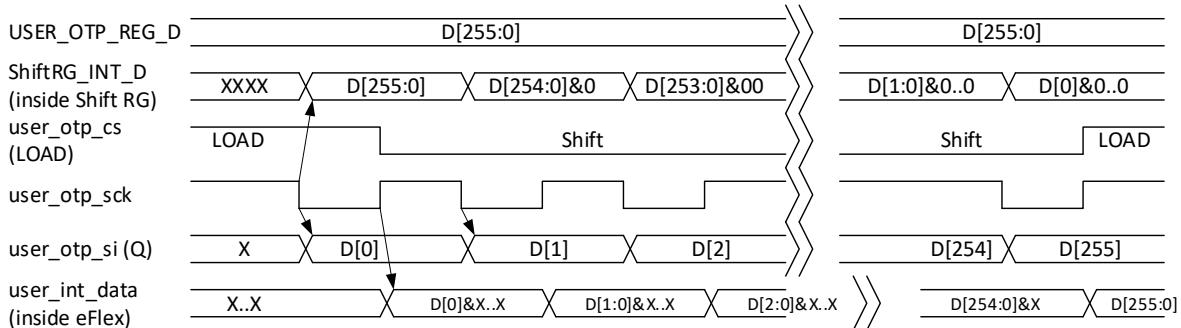

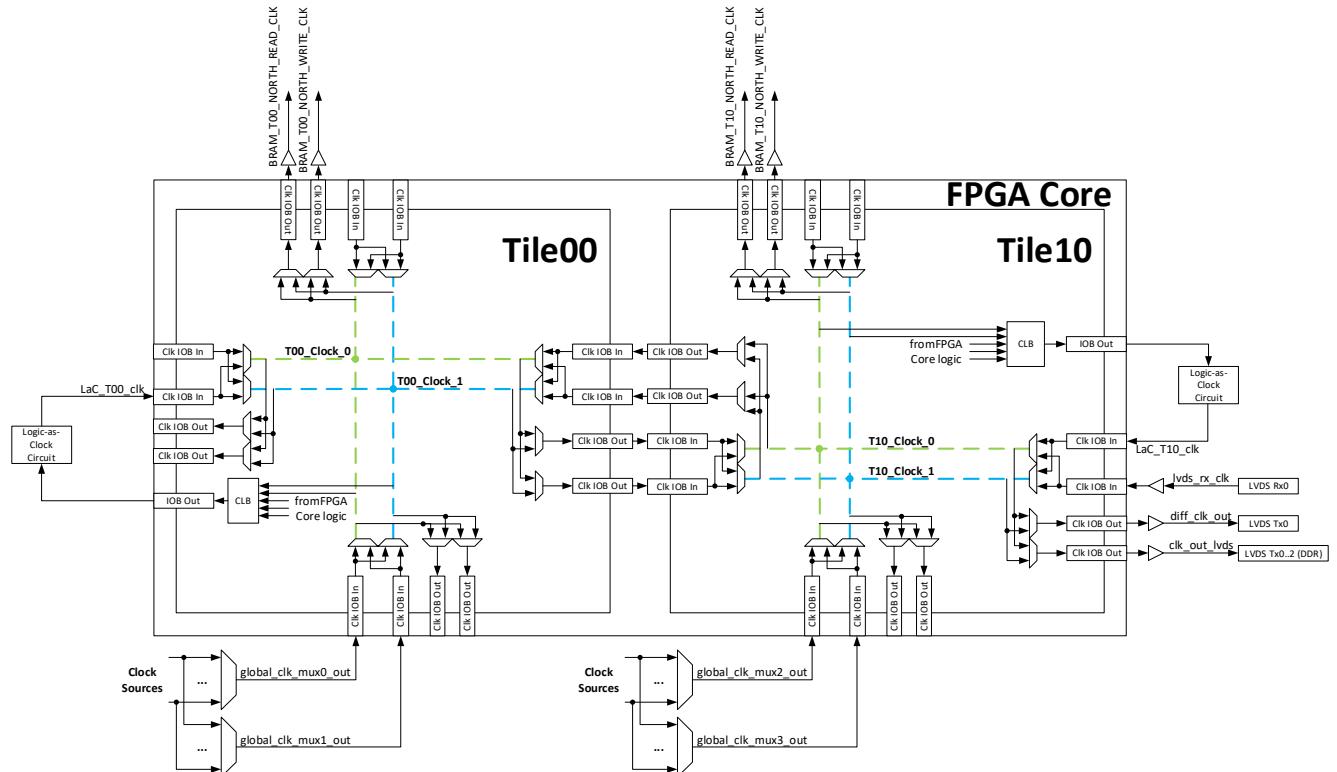

| Figure 25. FPGA Core Clock IOBs Connection.....                                    | 59 |

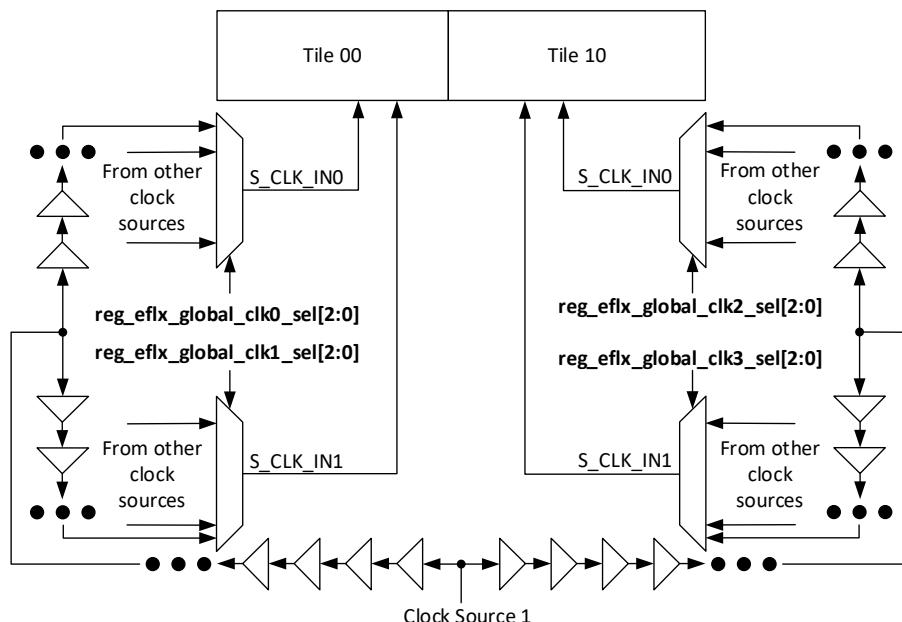

| Figure 26. Global Clock Distribution Network.....                                  | 60 |

| Figure 27. High-Frequency Oscillator Block Diagram.....                            | 61 |

| Figure 28. Oscillator Post Divider.....                                            | 61 |

| Figure 29. Phase-Locked Loop Block Diagram.....                                    | 63 |

| Figure 30. PLL with External Post Dividers .....                                   | 64 |

| Figure 31. External POSTDIV Architecture .....                                     | 65 |

| Figure 32. Logic-As-Clock Usage .....                                              | 67 |

| Figure 33. Power-Up Sequence.....                                                  | 69 |

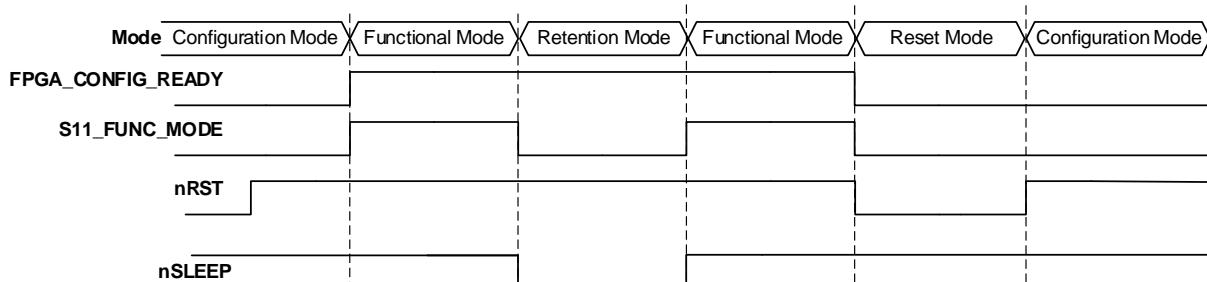

| Figure 34. Dedicated Signals Behavior .....                                        | 70 |

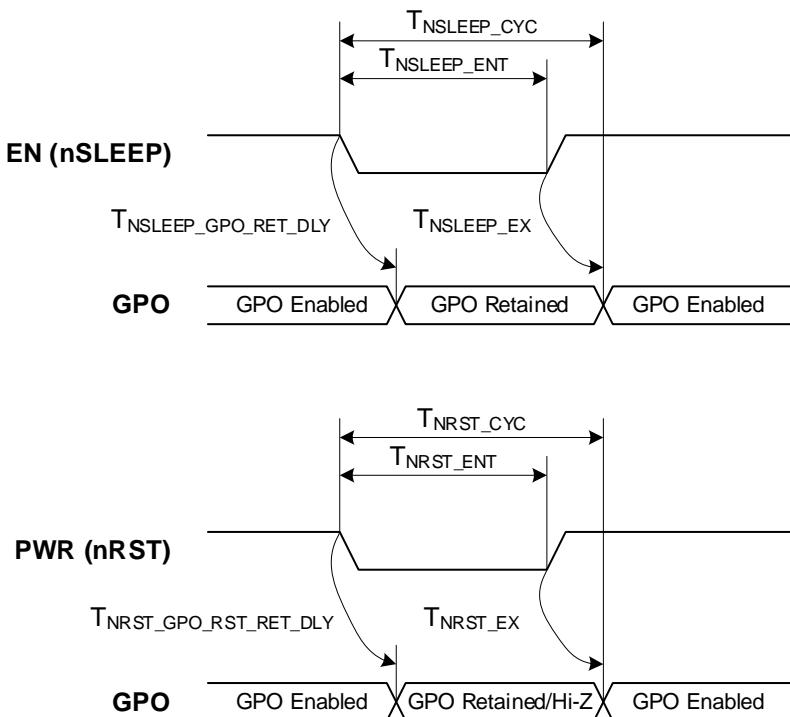

| Figure 35. Device On/Off State Cycle Timing Diagram (PWR/EN Pin) .....             | 71 |

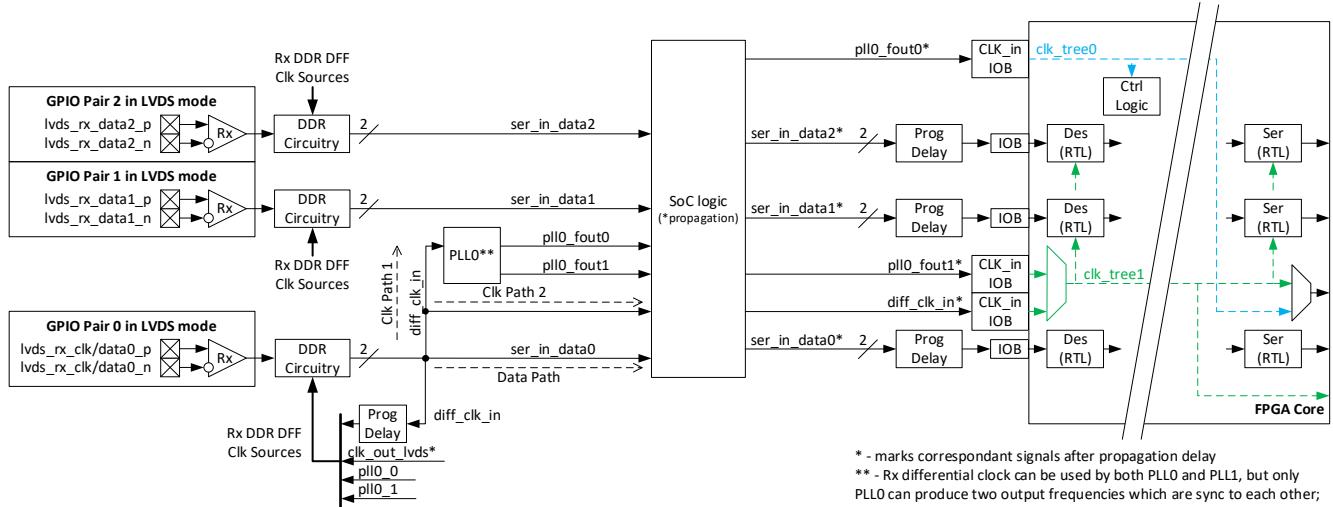

| Figure 36. LVDS Input Paths .....                                                  | 73 |

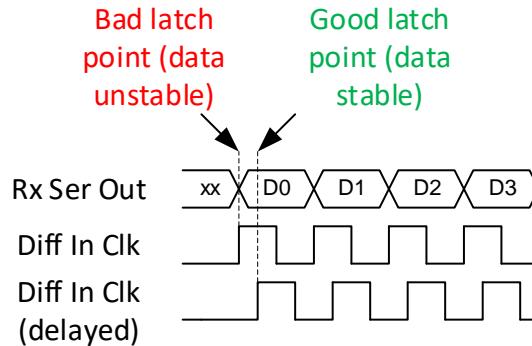

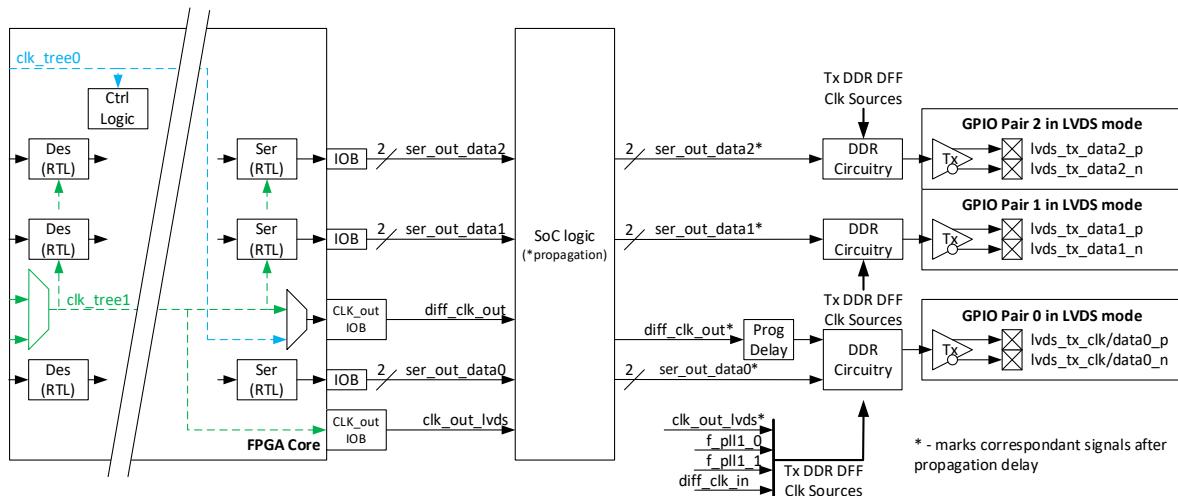

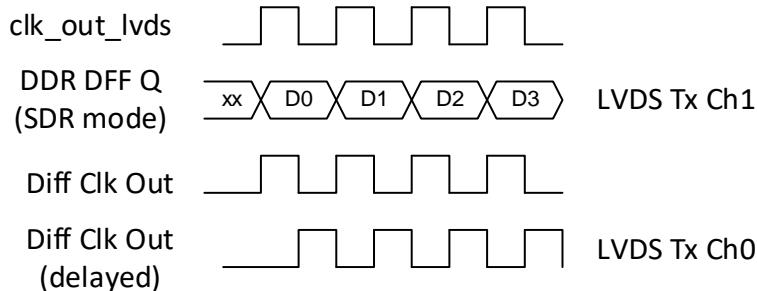

| Figure 37. Delayed Input Differential Clock Usage .....                            | 74 |

| Figure 38. LVDS Output Paths .....                                                 | 74 |

| Figure 39. Delayed Output Differential Clock Usage .....                           | 75 |

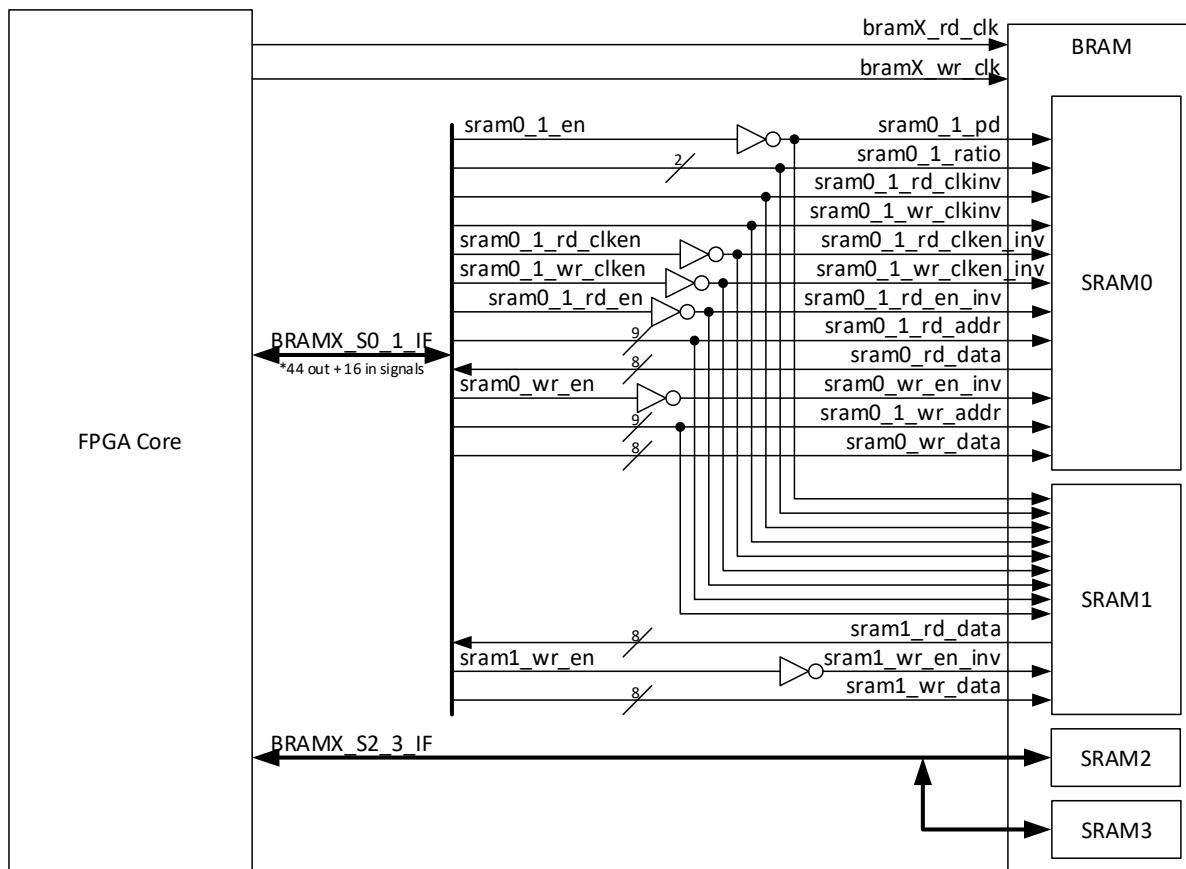

| Figure 40. BRAM Connections .....                                                  | 76 |

| Figure 41. Embedded Block RAM.....                                                 | 77 |

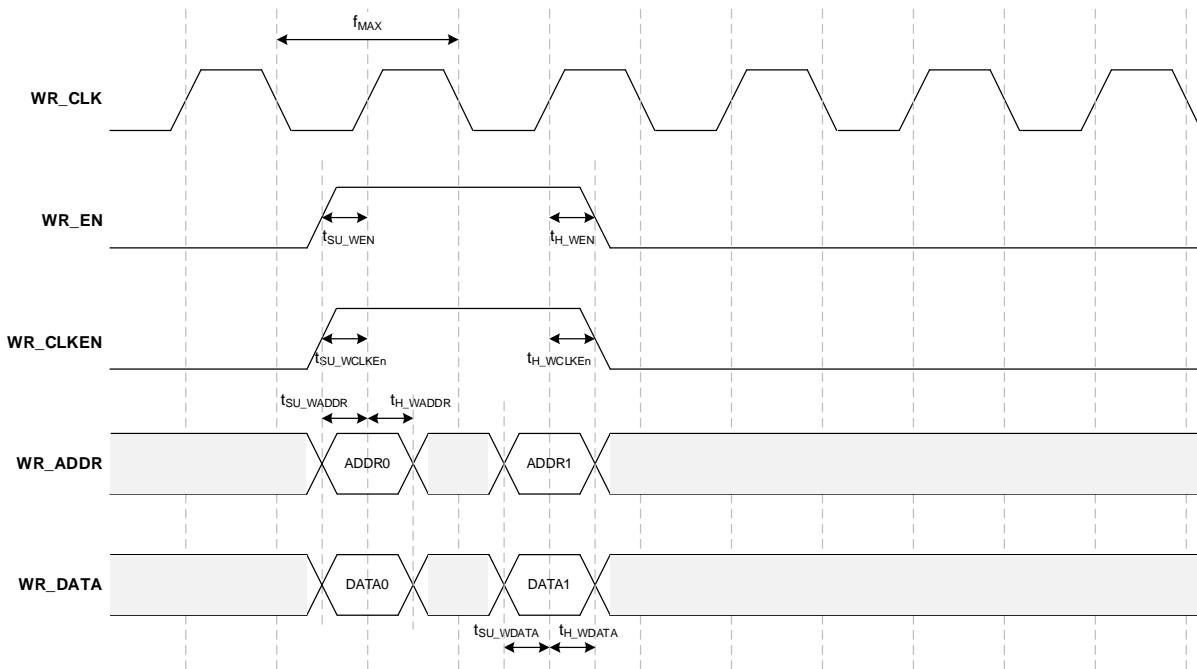

| Figure 42. BRAM Write Timing Diagram .....                                         | 80 |

| Figure 43. BRAM Read Timing Diagram .....                                          | 81 |

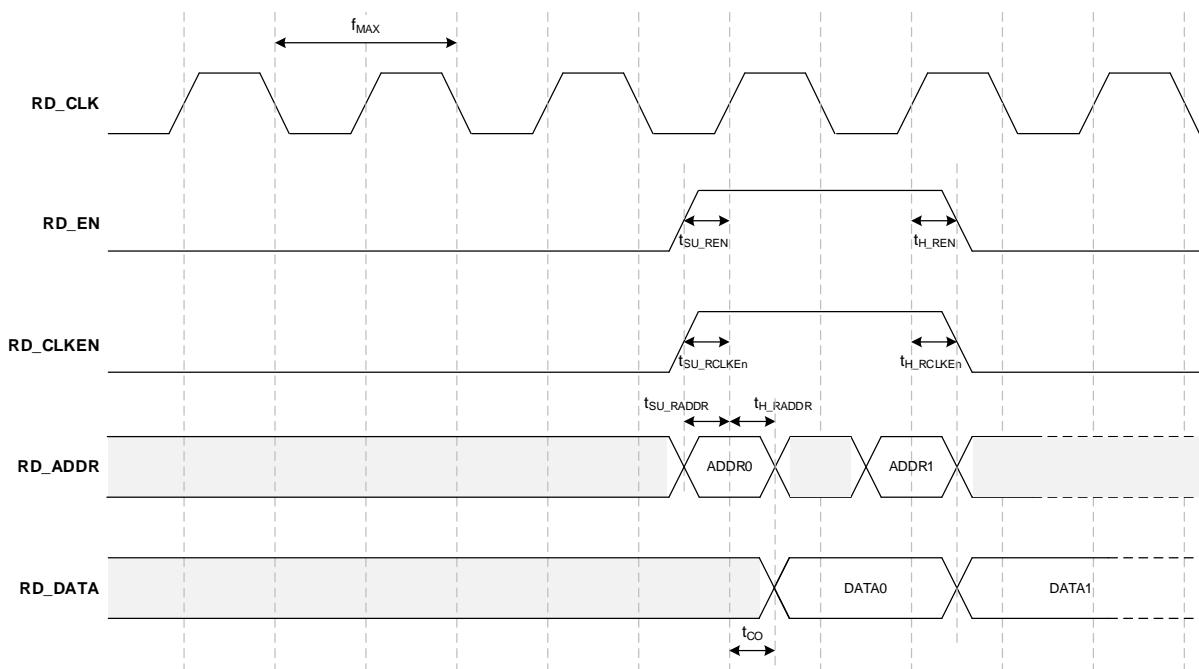

| Figure 44. FPGA Core Configuration Paths .....                                     | 83 |

| Figure 45. Package Outlines Drawing LQFN-48 .....                                  | 86 |

| Figure 46. Package Outline Drawing WLCSP-48 .....                                  | 87 |

| Figure 47. Package Top Marking LQFN-48.....                                        | 88 |

| Figure 48. Package Top Marking WLCSP-48.....                                       | 88 |

| Figure 49. Recommended Landing Pattern for LQFN 48L .....                          | 90 |

| Figure 50. Recommended Landing Pattern for WLCSP 48L .....                         | 90 |

| Figure 51. Tape and Reel Drawing for WLCSP 48L .....                               | 92 |

| Figure 52. Reel Drawing for LQFN 48L.....                                          | 93 |

| Figure 53. Tape Drawing for LQFN 48L .....                                         | 94 |

## Tables

|                                                              |    |

|--------------------------------------------------------------|----|

| Table 1. Block Control.....                                  | 9  |

| Table 2. LQFN-48 Pin Configuration.....                      | 11 |

| Table 3. WLCSP-48 Pin Configuration.....                     | 14 |

| Table 4. Configuration/Functional Pin Descriptions.....      | 16 |

| Table 5. Global Pins Descriptions.....                       | 17 |

| Table 6. Fast Routes GPIO Pairs and Timings.....             | 43 |

| Table 7. Supported Input/Output Standards.....               | 44 |

| Table 8. GPIO-to-IOB and IOB-to-GPIO Data Path Delays .....  | 52 |

| Table 9. Pin-to-Pin Performance.....                         | 57 |

| Table 10. Register-to-Register Performance.....              | 57 |

| Table 11. Oscillator Post Divider Available Frequencies..... | 62 |

| Table 12. State of Modules in Different Chip Modes .....     | 72 |

| Table 13. BRAM Ports .....                                   | 78 |

| Table 14. Write Address Extension Using Bits 5-7.....        | 79 |

| Table 15. Read Address Extension Using Bits 2-4 .....        | 80 |

| Table 16. BRAM Initialization.....                           | 82 |

| Table 17. Recommended Flash Memory Devices .....             | 85 |

| Table 18. MSL Classification .....                           | 89 |

# 1. Overview

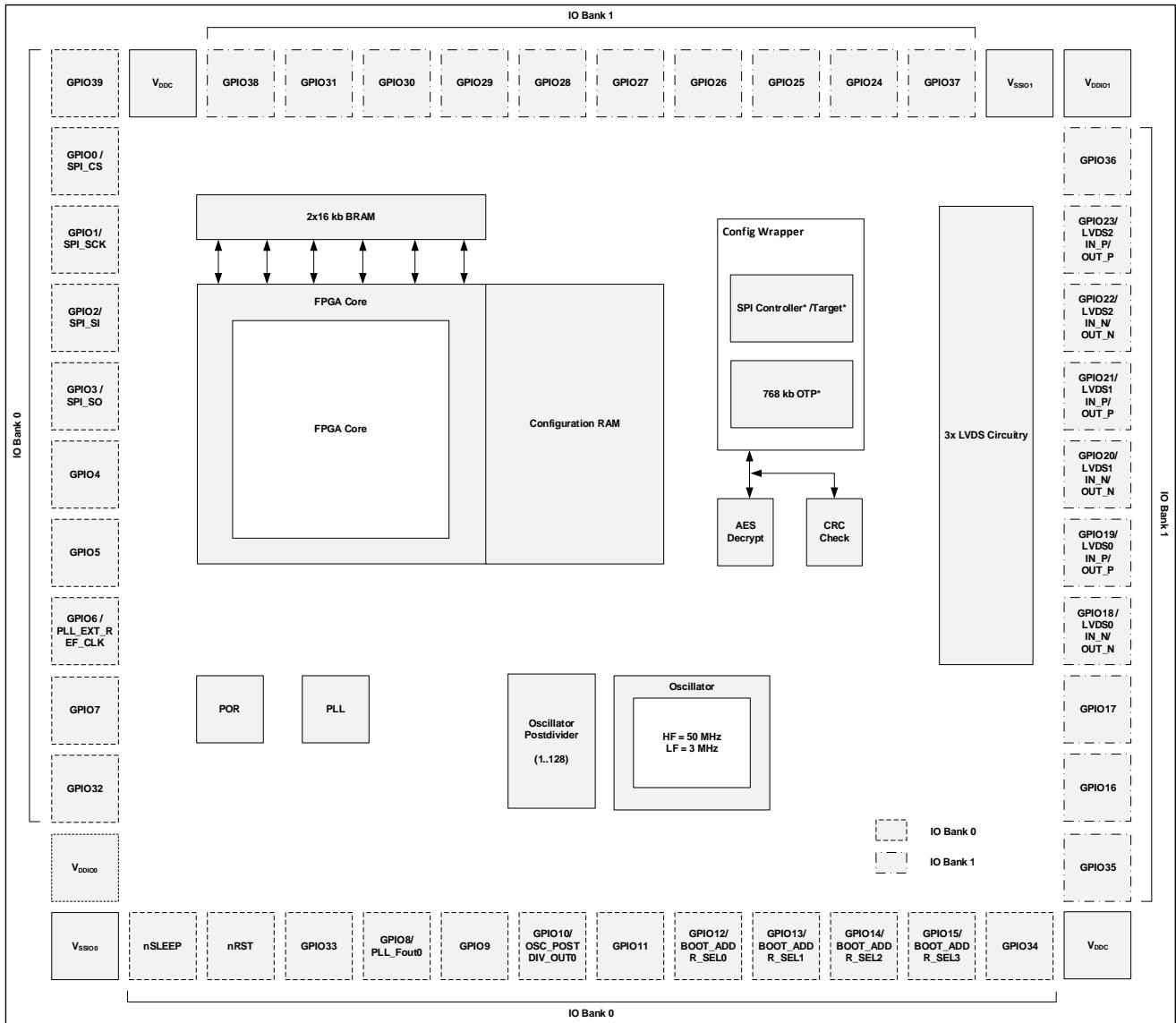

The components of the SLG47912 are shown in the Block Diagram (Figure 1).

## 1.1 Block Diagram

\*SPI Controller/Target and OTP can be accessed only for configuration mode.

Figure 1. Block Diagram

## 1.2 Block Description

The SLG47912 is FPGA device with 1.1k of LUTs and 1.1k DFFs available for user-defined digital logic. Main blocks of SLG47912 are described below.

### Power-on Reset

The POR circuit monitors the  $V_{DDIO}$  ( $V_{DDIO0}$  and  $V_{DDIO1}$  pins) and  $V_{DDC}$  power supplies and keeps the SLG47912 in reset state upon power up until  $V_{DDIO}$  and  $V_{DDC}$  are within the specified voltage ranges. The POR reset will occur if power rails drop below the specified voltage range after the device has been powered up. A POR reset will tri-state all GPIOs.

### GPIOs

The GPIO pins are general purpose programmable Digital IO circuits that can be programmed as an input or an output to the device. The GPIO pins connect to the FPGA Core. GPIO[3:0] are used to configure the device in SPI mode. GPIO[23:18] can operate in LVDS mode.

### FPGA Core

The device core consists of the FPGA Core and a ring of interface blocks called Input-Output Buffers (IOBs). The IOBs are inputs/outputs to FPGA Core and are used to communicate between FPGA Core and other sub-blocks. The FPGA Core itself, consists of an array of Configurable Logic Blocks (CLBs). Each CLB contains LUTs, Registers, 4-bit carry chain, and a clock network which are used to implement user-defined logic functions. In addition, some CLBs in the FPGA Core can be configured in Embedded Memory Mode (EMM) and Shift Register Mode (SRM). These modes are used to act as distributed memory. The Configuration RAM is a volatile memory that stores the FPGA design after chip configuration and can be loaded from the OTP or the SPI Blocks.

### BRAM

The 32 kb BRAM is an SRAM block that can be programmed in different width and depth configurations. Each 16 kb BRAM has one write port, one read port, and can be configured as a simple dual port SRAM. There are two 16 kb BRAM instances that interface with the FPGA Core. The BRAM does not connect directly with the GPIO. The width and depth configurations for the write and read ports must be the same.

### OTP Block

The 768 kb OTP is used to store user defined configuration. OTP is a One Time Programmable NVM block that allows users to store the FPGA design once the design has been finalized. In such case user bitstream is stored inside the device.

### SPI

The SPI Controller (Master) ([Note](#)) and SPI Target (Slave) ([Note](#)) are dedicated circuits that allow to configure SLG47912 FPGA Core from external source of bitstream. The SPI Controller and SPI Target connect to GPIO0 (SPI\_CS), GPIO1 (SPI\_SCK), GPIO2 (SPI\_SI) and GPIO3 (SPI\_SO). In this case user's bitstream is stored outside of the device and it transmitted to SLG47912 via SPI line during configuration process.

**Note:** For SPI Interface Controller is used as substitution for Master and Target is used as substitution for Slave. As for commonly used line names MISO (Master Input Slave Output) and MOSI (Master Output Slave Input) – they are used without change. Also, EC tables parameters related to SPI use M and S indexes.

## Clocking

SLG47912 has the following clock sources:

- Oscillator (selectable High Frequency or Low Frequency mode) – available for user only through Oscillator Post Divider or as reference clock for PLL.

- Oscillator Post Divider (division factor – powers of 2 in range 1 to 128).

- PLL with external Post Divider (two outputs).

- LVDS differential clock.

FPGA Core has totally available 4 clock domain.

Clock distribution network allows user to select which clocks are to be used for user-defined logic.

## Other Blocks

AES Decryption mechanism is used to decrypt bitstreams which are received through the SPI interface. It is optional and is disabled by default. Bitstream encryption allows user to ensure security of the design when it is transmitted through open interfaces and does not allow direct copying of the user-project.

A CRC Check mechanism is used to ensure integrity of configuration data that is being transferred during configuration process. It is applied to all configuration data regardless of the source (SPI interface or OTP). The CRC check is performed simultaneously with FPGA Core configuration process.

The nSLEEP(EN) and nRST(PWR) inputs are used to control the behavior and power consumption of SLG47912 as shown in [Table 1](#).

**Table 1. Block Control**

| nRST (PWR) | nSLEEP (EN) | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | X           | <p>Reset Mode:</p> <p>Configuration of FPGA Core is not retained, and FPGA Core is power-gated.</p> <p>PLL, OSC, and OTP memory are disabled.</p> <p>BRAM data are not retained unless option to retain content (<b>BRAM Keep</b>) is set (separate control for each BRAM).</p> <p>GPIOs in Hi-Z state and output state is not retained unless option to retain GPOs state (<b>GPIO Keep</b>) is set (common for all GPIOs).</p> |

| 1          | 0           | <p>Sleep Mode:</p> <p>Configuration and DFF states of FPGA Core are retained, and FPGA Core power is gated.</p> <p>PLL, OSC, and OTP memory are disabled.</p> <p>BRAM data are retained if BRAMs are not power gated with <b>BRAM Power</b> option (separate for each BRAM).</p> <p>GPIO not in Hi-Z state and output state is retained.</p>                                                                                     |

| 1          | 1           | <p>Configuration Mode:</p> <p>From internal OTP.</p> <p>From external SPI.</p> <p>From MCU interface.</p> <p>FPGA Core, GPIO, BRAM, PLL, and OSC controlled by Configuration Logic.</p> <p>OR</p> <p>Functional Mode:</p> <p>FPGA Core, GPIOs, PLL, OSC, and others are under user control.</p> <p>Device performs user-defined functions.</p>                                                                                   |

## 2. Pin Information

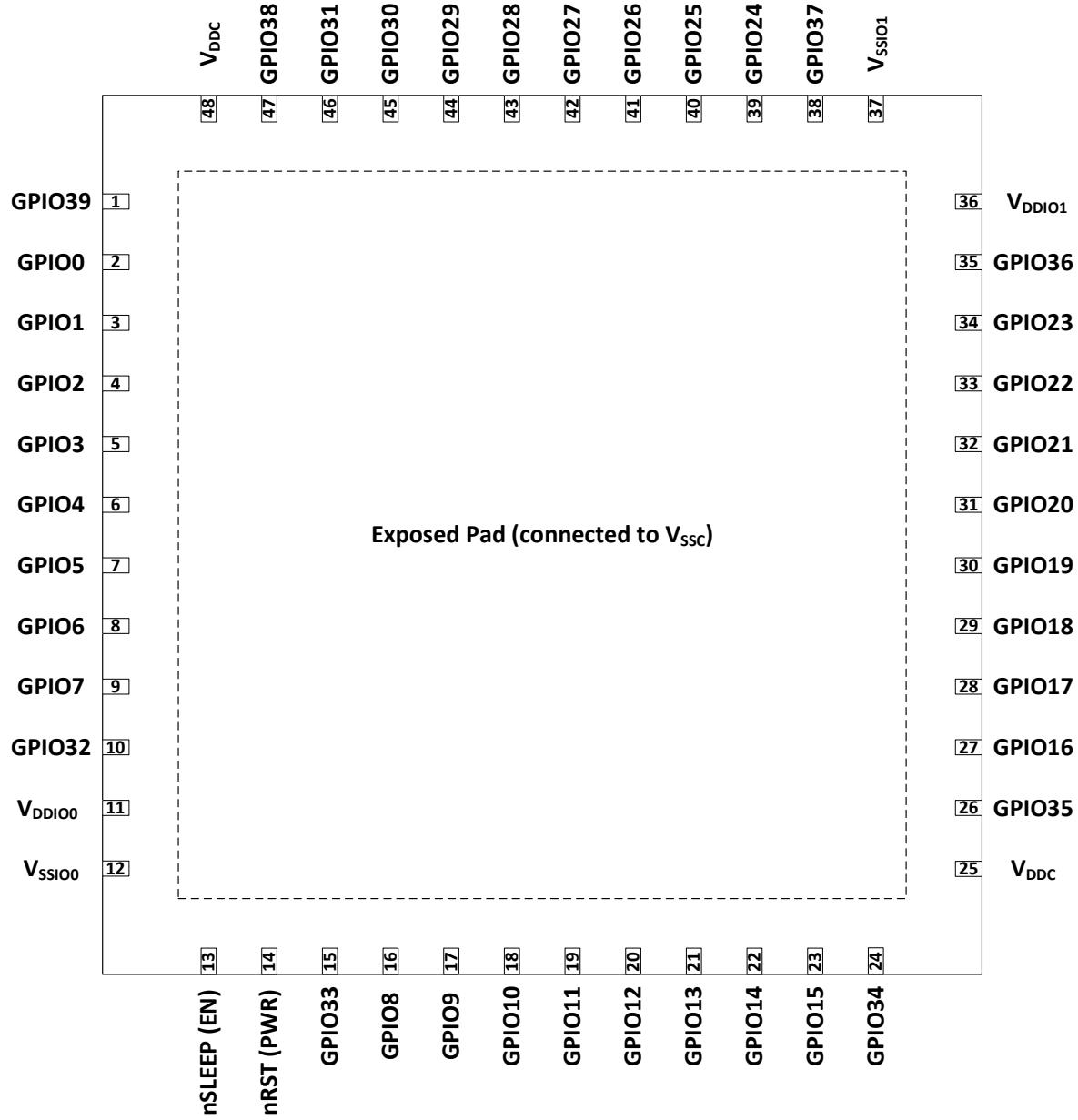

### 2.1 Pin Assignments - LQFN-48

Figure 2. Pinout for 48-pin LQFN Package

**Table 2. LQFN-48 Pin Configuration**

| Pin Number | Signal Name | V <sub>DDIO</sub> Bank | Pin Functions                                                          |

|------------|-------------|------------------------|------------------------------------------------------------------------|

| 14         | nRST        | V <sub>DDIO0</sub>     | Dedicated input pin to set device into Reset Mode. Active level – LOW. |

| 13         | nSLEEP      | V <sub>DDIO0</sub>     | Dedicated input pin to set device in Sleep Mode. Active level – LOW.   |

| 2          | GPIO0       | V <sub>DDIO0</sub>     | General Purpose Input/Output or SPI_CS                                 |

| 3          | GPIO1       | V <sub>DDIO0</sub>     | General Purpose Input/Output or SPI_SCK                                |

| 4          | GPIO2       | V <sub>DDIO0</sub>     | General Purpose Input/Output or SPI_SI                                 |

| 5          | GPIO3       | V <sub>DDIO0</sub>     | General Purpose Input/Output or SPI_SO or CONF_DONE                    |

| 6          | GPIO4       | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| 7          | GPIO5       | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| 8          | GPIO6       | V <sub>DDIO0</sub>     | General Purpose Input/Output or PLL_EXT_REF_CLK                        |

| 9          | GPIO7       | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| 16         | GPIO8       | V <sub>DDIO0</sub>     | General Purpose Input/Output or PLL_FOUT0                              |

| 17         | GPIO9       | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| 18         | GPIO10      | V <sub>DDIO0</sub>     | General Purpose Input/Output or OSC_POSTDIV_OUT0                       |

| 19         | GPIO11      | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| 20         | GPIO12      | V <sub>DDIO0</sub>     | General Purpose Input/Output or BOOT_ADDR_SEL0                         |

| 21         | GPIO13      | V <sub>DDIO0</sub>     | General Purpose Input/Output or BOOT_ADDR_SEL1                         |

| 22         | GPIO14      | V <sub>DDIO0</sub>     | General Purpose Input/Output or BOOT_ADDR_SEL2                         |

| 23         | GPIO15      | V <sub>DDIO0</sub>     | General Purpose Input/Output or BOOT_ADDR_SEL3                         |

| 27         | GPIO16      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 28         | GPIO17      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 29         | GPIO18      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 0 OUT_N/IN_N              |

| 30         | GPIO19      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 0 OUT_P/IN_P              |

| 31         | GPIO20      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 1 OUT_N/IN_N              |

| 32         | GPIO21      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 1 OUT_P/IN_P              |

| 33         | GPIO22      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 2 OUT_N/IN_N              |

| 34         | GPIO23      | V <sub>DDIO1</sub>     | General Purpose Input/Output or LVDS Channel 2 OUT_P/IN_P              |

| 39         | GPIO24      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 40         | GPIO25      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 41         | GPIO26      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 42         | GPIO27      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 43         | GPIO28      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 44         | GPIO29      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 45         | GPIO30      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 46         | GPIO31      | V <sub>DDIO1</sub>     | General Purpose Input/Output                                           |

| 10         | GPIO32      | V <sub>DDIO0</sub>     | General Purpose Input/Output                                           |

| Pin Number            | Signal Name        | V <sub>DDIO</sub> Bank | Pin Functions                |

|-----------------------|--------------------|------------------------|------------------------------|

| 15                    | GPIO33             | V <sub>DDIO0</sub>     | General Purpose Input/Output |

| 24                    | GPIO34             | V <sub>DDIO0</sub>     | General Purpose Input/Output |

| 26                    | GPIO35             | V <sub>DDIO1</sub>     | General Purpose Input/Output |

| 35                    | GPIO36             | V <sub>DDIO1</sub>     | General Purpose Input/Output |

| 38                    | GPIO37             | V <sub>DDIO1</sub>     | General Purpose Input/Output |

| 47                    | GPIO38             | V <sub>DDIO1</sub>     | General Purpose Input/Output |

| 1                     | GPIO39             | V <sub>DDIO0</sub>     | General Purpose Input/Output |

| 25, 48                | V <sub>DDC</sub>   | N/A                    | Core Supply Voltage          |

| 11                    | V <sub>DDIO0</sub> | N/A                    | IO Bank 0 Supply Voltage     |

| 36                    | V <sub>DDIO1</sub> | N/A                    | IO Bank 1 Supply Voltage     |

| ExpPAD <sup>[1]</sup> | V <sub>SSC</sub>   | N/A                    | Core GND                     |

| 12                    | V <sub>SSIO0</sub> | N/A                    | IO Bank 0 GND                |

| 37                    | V <sub>SSIO1</sub> | N/A                    | IO Bank 1 GND                |

[1] ExpPAD - Exposed PAD on the bottom side of QFN package.

**Note:** Some GPIOs also have secondary functions assigned. These functions are active only in certain operating mode (or activated with dedicated SW options). In other cases, they operate as simple GPIO (when in Functional mode).

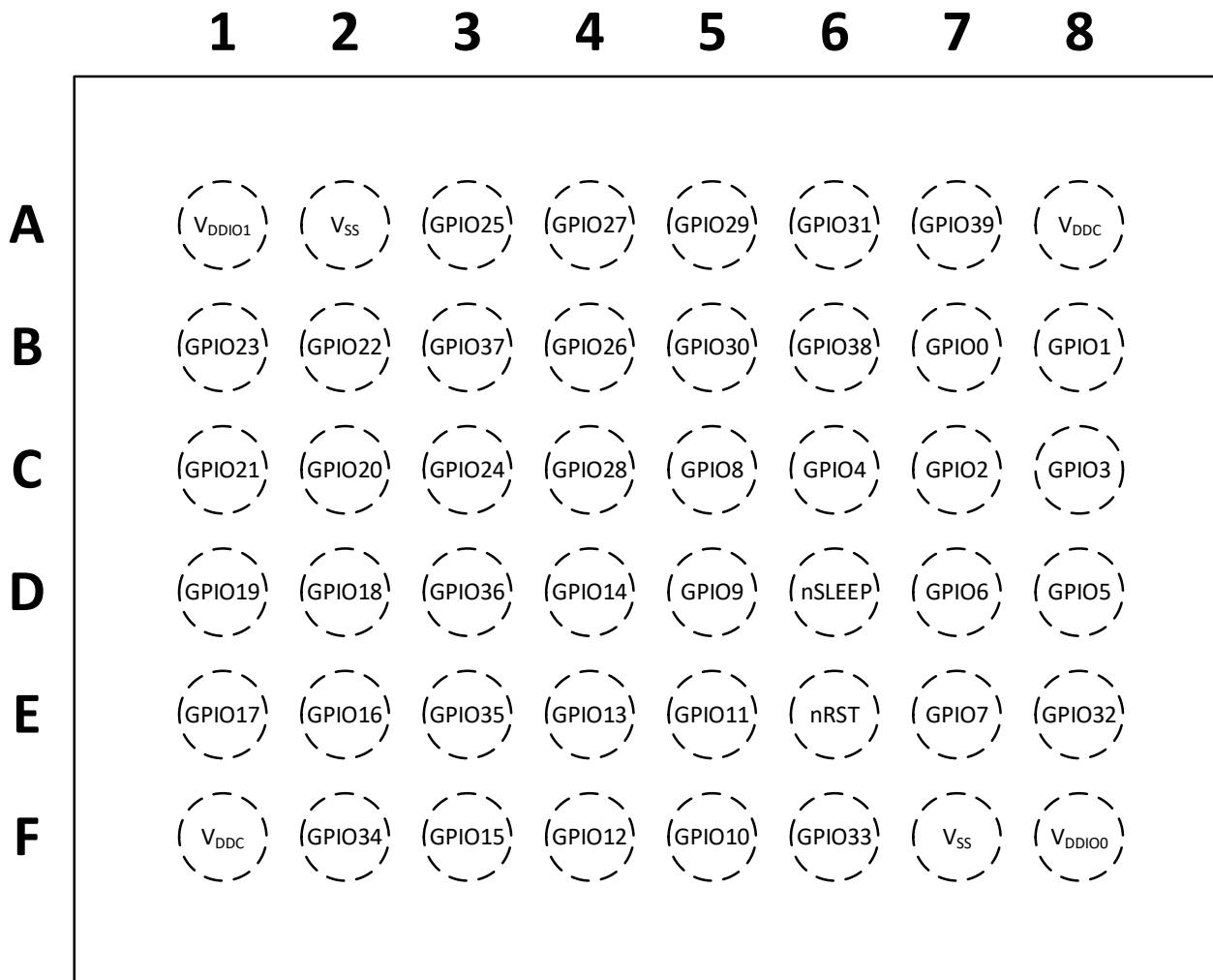

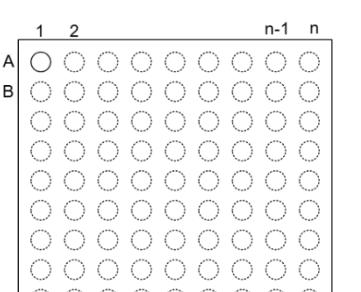

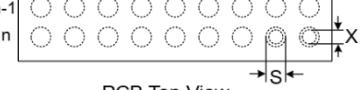

## 2.2 Pin Assignments - WLCSP-48

Figure 3. Pinout for 48-pin WLCSP Package (Top View)

Table 3. WLCSP-48 Pin Configuration

| Pin# | Signal Name | V <sub>DDIO</sub> Bank | Pin Function                                                           |

|------|-------------|------------------------|------------------------------------------------------------------------|

| D6   | nSLEEP (EN) | V <sub>DDIO0</sub>     | Dedicated input pin to set device in Sleep Mode. Active level – LOW.   |

| E6   | nRST (PWR)  | V <sub>DDIO0</sub>     | Dedicated input pin to set device into Reset Mode. Active level – LOW. |

| B7   | GPIO0       | V <sub>DDIO0</sub>     | General purpose Input/Output or SPI_CS                                 |

| B8   | GPIO1       | V <sub>DDIO0</sub>     | General purpose Input/Output or SPI_SCK                                |

| C7   | GPIO2       | V <sub>DDIO0</sub>     | General purpose Input/Output or SPI_SI                                 |

| C8   | GPIO3       | V <sub>DDIO0</sub>     | General purpose Input/Output or SPI_SO or CONF_DONE                    |

| C6   | GPIO4       | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| D8   | GPIO5       | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| D7   | GPIO6       | V <sub>DDIO0</sub>     | General purpose Input/Output or PLL_EXT_REF_CLK                        |

| E7   | GPIO7       | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| C5   | GPIO8       | V <sub>DDIO0</sub>     | General purpose Input/Output or PLL_FOUT0                              |

| D5   | GPIO9       | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| F5   | GPIO10      | V <sub>DDIO0</sub>     | General purpose Input/Output or OSC_POSTDIV_OUT0                       |

| E5   | GPIO11      | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| F4   | GPIO12      | V <sub>DDIO0</sub>     | General purpose Input/Output or BOOT_ADDR_SEL0                         |

| E4   | GPIO13      | V <sub>DDIO0</sub>     | General purpose Input/Output or BOOT_ADDR_SEL1                         |

| D4   | GPIO14      | V <sub>DDIO0</sub>     | General purpose Input/Output or BOOT_ADDR_SEL2                         |

| F3   | GPIO15      | V <sub>DDIO0</sub>     | General purpose Input/Output or BOOT_ADDR_SEL3                         |

| E2   | GPIO16      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| E1   | GPIO17      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| D2   | GPIO18      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 0 OUT_N/IN_N              |

| D1   | GPIO19      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 0 OUT_P/IN_P              |

| C2   | GPIO20      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 1 OUT_N/IN_N              |

| C1   | GPIO21      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 1 OUT_P/IN_P              |

| B2   | GPIO22      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 2 OUT_N/IN_N              |

| B1   | GPIO23      | V <sub>DDIO1</sub>     | General purpose Input/Output or LVDS Channel 2 OUT_P/IN_P              |

| C3   | GPIO24      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| A3   | GPIO25      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| B4   | GPIO26      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| A4   | GPIO27      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| C4   | GPIO28      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| A5   | GPIO29      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| B5   | GPIO30      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| A6   | GPIO31      | V <sub>DDIO1</sub>     | General purpose Input/Output                                           |

| E8   | GPIO32      | V <sub>DDIO0</sub>     | General purpose Input/Output                                           |

| Pin#   | Signal Name        | V <sub>DDIO</sub> Bank | Pin Function                 |

|--------|--------------------|------------------------|------------------------------|

| F6     | GPIO33             | V <sub>DDIO0</sub>     | General purpose Input/Output |

| F2     | GPIO34             | V <sub>DDIO0</sub>     | General purpose Input/Output |

| E3     | GPIO35             | V <sub>DDIO1</sub>     | General purpose Input/Output |

| D3     | GPIO36             | V <sub>DDIO1</sub>     | General purpose Input/Output |

| B3     | GPIO37             | V <sub>DDIO1</sub>     | General purpose Input/Output |

| B6     | GPIO38             | V <sub>DDIO1</sub>     | General purpose Input/Output |

| A7     | GPIO39             | V <sub>DDIO0</sub>     | General purpose Input/Output |

| A8, F1 | V <sub>DDC</sub>   | N/A                    | Core supply voltage          |

| F8     | V <sub>DDIO0</sub> | N/A                    | IO Bank 0 supply voltage     |

| A1     | V <sub>DDIO1</sub> | N/A                    | IO Bank 1 supply voltage     |

| A2, F7 | V <sub>SSC</sub>   | N/A                    | Core GND                     |

|        | V <sub>SSIO0</sub> |                        | IO Bank 1 GND                |

|        | V <sub>SSIO1</sub> |                        | IO Bank 2 GND                |

**Note:** Some GPIOs also have secondary functions assigned. These functions are active only in certain operating modes (or activated with dedicated SW options). In other cases, they operate as simple GPIO.

## 2.3 Pin Descriptions

Table 4. Configuration/Functional Pin Descriptions

| Signal Name |                           | Function                          | IO           | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|---------------------------|-----------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary     | Secondary                 |                                   |              |                                                                                                                                                                                                                                                                                                                                                                                                        |

| nRST        | -                         | Reset signal                      | Input        | This signal allows to set the device into Reset Mode. Active – LOW.                                                                                                                                                                                                                                                                                                                                    |

| nSLEEP      | -                         | Sleep signal                      | Input        | This signal allows to set the device into Sleep Mode. Active – LOW. Holding it LOW before OTP Configuration started – activates indication of configuration process success. Also, if it is held LOW after successful configuration – it would prevent the device from proceeding to Functional Mode until it is driven HIGH.                                                                          |

| GPIO0       | SPI_CS                    | SPI Controller Mode Configuration | Output       | In SPI Controller Mode, this pin outputs Chip Select signal to external Flash memory. Also, depending on configuration method settings, the SPI_CS input is used to define SPI programming mode to be used.                                                                                                                                                                                            |

|             |                           | SPI Target Mode Configuration     | Input        | In SPI Target Mode, this pin inputs Chip Select signal from external controller. Also, depending on configuration method settings, the SPI_CS input is used to define SPI programming mode to be used.                                                                                                                                                                                                 |

|             | -                         | General IO                        | IO           | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                                                                                                                                                                                                                                          |

| GPIO1       | SPI_SCK                   | SPI Controller Mode Configuration | Clock Output | In SPI Controller Mode, this pin outputs SPI clock to external Flash memory.                                                                                                                                                                                                                                                                                                                           |

|             |                           | SPI Target Mode Configuration     | Clock Input  | In SPI Target Mode, this pin inputs SPI clock from external controller.                                                                                                                                                                                                                                                                                                                                |

|             | -                         | General IO                        | IO           | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                                                                                                                                                                                                                                          |

| GPIO2       | SPI_SI (MISO)             | SPI Controller Mode Configuration | Input        | Serial Input (MISO) is a data pin. This pin is used to transmit data from the target to the controller. Whenever the target sends data, that data will be collected over the MISO pin by the controller.                                                                                                                                                                                               |

|             | SPI_SI (MOSI)             | SPI Target Mode Configuration     |              | Serial Input (MOSI) is a data pin. This pin is used to transmit data from the controller to the target device. Whenever the controller sends data, that data will be collected over the MOSI pin by the target.                                                                                                                                                                                        |

|             | -                         | General IO                        | IO           | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                                                                                                                                                                                                                                          |

| GPIO3       | SPI_SO (MOSI)/CONFIG_DONE | SPI Controller Mode Configuration | Output       | MOSI is a data pin. This pin is used to transmit data from the controller to the target device. Whenever the controller sends data, that data will be collected over the MOSI pin by the target. After configuration process is performed – this pin indicates if configuration was performed successfully or not.                                                                                     |

|             | SPI_SO (MISO)/CONFIG_DONE | SPI Target Mode Configuration     |              | MISO is a data pin. This pin is used to transmit data from the target to the controller. Whenever the target sends data, that data will be collected over the MISO pin by the controller. In MCU Mode, the CONFIG signal is flagged at this pin. After configuration process is performed – this pin indicates if configuration was performed successfully or not. See section 10 Configuration Modes. |

| Signal Name |             | Function               | IO     | Description                                                                                                                                                                          |

|-------------|-------------|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary     | Secondary   |                        |        |                                                                                                                                                                                      |

| GPIO3       | CONFIG_DONE | OTP Mode Configuration | Output | After configuration process is performed – optionally this pin can indicate if configuration was performed successfully or not. See section <a href="#">10 Configuration Modes</a> . |

|             | -           | General IO             | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                        |

Table 5. Global Pins Descriptions

| Signal Name            | Function                   | IO     | Description                                                                                                                                                                            |

|------------------------|----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO [5:4]             | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

| GPIO [6]               | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | PLL External Reference CLK | Input  | This IO can be programmed as a reference clock for the device in user function when receiving clock from PLL.<br>GPIO6: PLL_EXT_REF_CLK.                                               |

| GPIO [7]               | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

| GPIO [10],<br>GPIO[8]  | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | Clock source to Pin out    | Output | When activated with dedicated SW options – clock from different clock sources can be output to dedicated GPIOs:<br>GPIO8: PLL Fout0.<br>GPIO10: Oscillator Postdivider Out0.           |

| GPIO [9],<br>GPIO [11] | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

| GPIO [15:12]           | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | Boot Address Select        | Input  | When Boot Address Control is enabled – these GPIOs are used (all or only part of them) as controls to select needed boot address. See section <a href="#">10 Configuration Modes</a> . |

| GPIO [17:16]           | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

| GPIO18                 | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | LVDS Pair 0 IN_N/OUT_N     | IO     | The pin functions as an input/output pin for LVDS Channel 0 N-terminal.                                                                                                                |

| GPIO19                 | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | LVDS Pair 0 IN_P/OUT_P     | IO     | The pin functions as an input/output pin for LVDS Channel 0 P-terminal.                                                                                                                |

| GPIO20                 | General IO                 | IO     | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                          |

|                        | LVDS Pair 1 IN_N/OUT_N     | IO     | The pin functions as an input/output pin for LVDS Channel 1 N-terminal.                                                                                                                |

| Signal Name  | Function                  | IO | Description                                                                                   |

|--------------|---------------------------|----|-----------------------------------------------------------------------------------------------|

| GPIO21       | General IO                | IO | In user mode, after configuration, this pin can be programmed as general IO in user function. |

|              | LVDS Pair 1<br>IN_P/OUT_P | IO | The pin functions as an input/output pin for LVDS Channel 1 P-terminal.                       |

| GPIO22       | General IO                | IO | In user mode, after configuration, this pin can be programmed as general IO in user function. |

|              | LVDS Pair 2<br>IN_N/OUT_N | IO | The pin functions as an input/output pin for LVDS Channel 2 N-terminal.                       |

| GPIO23       | General IO                | IO | In user mode, after configuration, this pin can be programmed as general IO in user function. |

|              | LVDS Pair 2<br>IN_P/OUT_P | IO | The pin functions as an input/output pin for LVDS Channel 2 P-terminal.                       |

| GPIO [39:24] | General IO                | IO | In user mode, after configuration, this pin can be programmed as general IO in user function. |

### 3. Specifications

#### 3.1 Absolute Maximum Ratings

**Note:** Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to the absolute maximum conditions for extended periods may affect the device reliability.

| Parameter                                                        | Min                                                                    | Max | Unit |    |

|------------------------------------------------------------------|------------------------------------------------------------------------|-----|------|----|

| Supply Voltage ( $V_{DDC}$ )                                     | -0.3                                                                   | 1.5 | V    |    |

| Supply Voltage ( $V_{DDIO0}$ , $V_{DDIO1}$ )                     | -0.3                                                                   | 3.6 | V    |    |

| Voltage at Digital Input Pins, $I_{OL} = -100 \mu A$             | -0.3                                                                   | 3.6 | V    |    |

| Maximum RMS or DC Current (through Single GPIO Pin)              | -                                                                      | 40  | mA   |    |

| Current at Digital Input Pin                                     | -1.0                                                                   | 1.0 | mA   |    |

| $I_{VDDIO}$ DC Current through $V_{DDIO}$ Pin <sup>[1]</sup>     | -                                                                      | 650 | mA   |    |

| $I_{VDDC}$ DC Current through $V_{DDC}$ Pin <sup>[1]</sup>       | -                                                                      | 650 | mA   |    |

| $I_{GND}$ DC Current through GND <sup>[1]</sup>                  | -                                                                      | 650 | mA   |    |

| Continuous Power Dissipation<br>(JESD51-7, $T_A = +85^\circ C$ ) | QFN-48, no Thermal Vias (Derate 42.2 mW/°C above $T_A = +85^\circ C$ ) | -   | 2743 | mW |

|                                                                  | WLCSP-48 (Derate 34.1 mW/°C above $T_A = +85^\circ C$ )                | -   | 2218 | mW |

| Storage Temperature Range                                        | -65                                                                    | 150 | °C   |    |

| Junction Temperature                                             | -                                                                      | 150 | °C   |    |

| Moisture Sensitivity Level                                       | 1                                                                      |     |      |    |

| [1] Package limit.                                               |                                                                        |     |      |    |

#### 3.2 ESD Ratings

| Parameter                            | Conditions | Min  | Max | Unit |

|--------------------------------------|------------|------|-----|------|

| ESD Protection (Human Body Model)    |            | 2000 | -   | V    |

| ESD Protection (Charge Device Model) |            | 1300 | -   | V    |

### 3.3 Recommended Operating Conditions

| Parameter                                    | Min   | Typ | Max   | Unit |

|----------------------------------------------|-------|-----|-------|------|

| Supply Voltage ( $V_{DDC}$ ) <sup>[1]</sup>  | 1.045 | 1.1 | 1.155 | V    |

| Supply Voltage ( $V_{DDIO}$ ) <sup>[1]</sup> | 1.71  | 2.5 | 3.465 | V    |

| Ambient Temperature ( $T_A$ ) <sup>[2]</sup> | -40   | 25  | 85    | °C   |

| Capacitor Value at $V_{DDC}$                 | 0.1   | -   | -     | μF   |

[1] Device operation outside this range is not guaranteed. The nominal operating voltage is 1.1 V for  $V_{DDC}$  and 1.8 – 3.3 V for  $V_{DDIO}$ . A guard band of +/- 5 % is provided to account for the  $V_{DDC}/V_{DDIO}$  fluctuation from the nominal voltage level.

[2] Parameters were measured with  $T_A = T_J$ .

### 3.4 Thermal Specifications

| Parameter          | Package                       | Symbol        | Conditions          | Typ  | Unit |

|--------------------|-------------------------------|---------------|---------------------|------|------|

| Thermal Resistance | LQFN-48, 6.0 mm × 6.0 mm      | $\theta_{JA}$ | Junction-to-ambient | 23.7 | °C/W |

|                    | WLCSP-48, 3.241 mm × 2.575 mm |               |                     | 29.3 |      |

### 3.5 Electrical Specifications

#### 3.5.1 PLL Specifications

$T_A = -40$  °C to  $+85$  °C,  $V_{DDIO} = 2.5$  V,  $V_{DDC} = 1.1$  V  $\pm$  5 %, unless otherwise specified.

| Parameter                                           | Symbol          | Conditions                                                   | Min | Typ | Max                     | Unit   |

|-----------------------------------------------------|-----------------|--------------------------------------------------------------|-----|-----|-------------------------|--------|

| Input Clock Frequency <sup>[3]</sup>                | $f_{IN}$        |                                                              | 5   | -   | 500                     | MHz    |

| Output Clock Frequency <sup>[3]</sup>               | $f_{OUT}$       |                                                              | 10  | -   | 2000 <sup>[1] [2]</sup> | MHz    |

| VCO Frequency <sup>[3]</sup>                        | $f_{VCO}$       |                                                              | 500 | -   | 2000 <sup>[2]</sup>     | MHz    |

| Output Duty Cycle <sup>[4]</sup>                    | $f_{PLL\_DC}$   | $f_{OUT}$ VCO at any frequency                               | 48  | 50  | 55                      | %      |

| Number of PFD Cycles for PLL to Lock <sup>[4]</sup> | $T_{PLL\_LOCK}$ | Lock is defined as no cycle slips for 256 consecutive cycles | -   | 600 | 900                     | cycles |

| PFD Frequency Range <sup>[3]</sup>                  | $f_{PFD}$       |                                                              | 5   |     | $f_{VCO}/16$            | MHz    |

| Peak to Peak Period Jitter <sup>[4]</sup>           | $t_{JIT\_10.2}$ | $f_{OUT} = 10.2$ MHz                                         | -   | 245 | 474                     | ps     |

| Peak to Peak Period Jitter <sup>[4]</sup>           | $t_{JIT\_55.6}$ | $f_{OUT} = 55.6$ MHz                                         | -   | 148 | 474                     | ps     |

| Peak to Peak Period Jitter <sup>[4]</sup>           | $t_{JIT\_100}$  | $f_{OUT} = 100$ MHz                                          | -   | 98  | 581                     | ps     |

| Peak to Peak Period Jitter <sup>[4]</sup>           | $t_{JIT\_125}$  | $f_{OUT} = 125$ MHz                                          | -   | 120 | 581                     | ps     |

[1] The PLL block can support this range but in practice it would be much less due to peripheral logic limitations.

[2] PLL with External Post Divider is limited with 1000 MHz value.

[3] Guaranteed by design, not tested in production.

[4] Guaranteed by characterization, not tested in production.

### 3.5.2 GPIOs Specifications

$T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ ,  $V_{DDC} = 1.1\text{ V}$ ,  $V_{DDIO} = 1.71\text{ V}$  to  $3.46\text{ V}$ , unless otherwise specified.

| Parameter                                                            | Symbol              | Conditions                                                                                | Min              | Typ | Max   | Unit |

|----------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input/Output Pin Capacitance                                         | $C_{IO\_PIN}$       | Non-LVDS GPIO<br>$T_J = 25^\circ\text{C}$<br>$C_{IO\_PIN} = C_{GPIO} + C_{PAD} + C_{PIN}$ | -                | 5.6 | -     | pF   |

|                                                                      |                     | LVDS GPIO<br>$T_J = 25^\circ\text{C}$<br>$C_{IO\_PIN} = C_{GPIO} + C_{PAD} + C_{PIN}$     | -                | 9.4 | -     |      |

| Input Leakage Current                                                | $I_{I\_LKG}$        | $V_{DDIO} = 3.465\text{ V}$ ,<br>$V_{IN} = 0$ to $V_{DDIO}$                               | -600             | -   | 600   | nA   |

| Max Absolute Data Skew - Output Paths <sup>[3]</sup>                 | $T_{SKEW\_DO\_PIN}$ | $V_{DDC} = 1.1\text{ V} \pm 5\%$                                                          | 5.4              | -   | 11.3  | ns   |

| Max Absolute Data Skew - Input Paths <sup>[3]</sup>                  | $T_{SKEW\_DI\_PIN}$ | $V_{DDC} = 1.1\text{ V} \pm 5\%$                                                          | 6.5              | -   | 14.6  | ns   |

| Minimal/Maximal Voltage Applied to Pins in Hi-Z State <sup>[3]</sup> | $V_{I\_LIMIT}$      |                                                                                           | $V_{SSIO} - 0.3$ | -   | 3.465 | V    |

LVCMOS 1.8 V (Compatible with JESD8-7A, Normal Range),  $V_{DDIO} = 1.8\text{ V} \pm 5\%$

|                            |                 |                                                                     |                        |      |                        |               |

|----------------------------|-----------------|---------------------------------------------------------------------|------------------------|------|------------------------|---------------|

| $V_{DDIO}$ Leakage Current | $I_{DDIO\_LKG}$ |                                                                     | -                      | 0.32 | 3.9                    | $\mu\text{A}$ |

| HIGH-Level Input Voltage   | $V_{IH}$        | Simple Input settings                                               | $0.65 \times V_{DDIO}$ | -    | 3.465 <sup>[3]</sup>   | V             |

|                            |                 | Schmitt-trigger input, no PU settings                               | $0.65 \times V_{DDIO}$ | -    | 3.465 <sup>[3]</sup>   | V             |

|                            |                 | Schmitt-trigger input, 1xPU settings <sup>[2]</sup>                 | $0.65 \times V_{DDIO}$ | -    | 3.465 <sup>[3]</sup>   | V             |

|                            |                 | Schmitt-trigger input, 2xPU settings <sup>[2]</sup>                 | $0.65 \times V_{DDIO}$ | -    | 3.465 <sup>[3]</sup>   | V             |

| LOW-Level Input Voltage    | $V_{IL}$        | Simple Input settings                                               | -0.3 <sup>[3]</sup>    | -    | $0.35 \times V_{DDIO}$ | V             |

|                            |                 | Schmitt-trigger input, no PU settings                               | -0.3 <sup>[3]</sup>    | -    | $0.35 \times V_{DDIO}$ | V             |

|                            |                 | Schmitt-trigger input, 1xPU settings <sup>[2]</sup>                 | -0.3 <sup>[3]</sup>    | -    | $0.35 \times V_{DDIO}$ | V             |

|                            |                 | Schmitt-trigger input, 2xPU settings <sup>[2]</sup>                 | -0.3 <sup>[3]</sup>    | -    | $0.35 \times V_{DDIO}$ | V             |

| HIGH-Level Output Voltage  | $V_{OH}$        | Push-pull 4 mA settings,<br>$I_{OH} = 0.5\text{ mA}$ <sup>[2]</sup> | $V_{DDIO} - 0.45$      | -    | -                      | V             |

|                            |                 | Push-pull 4 mA settings,<br>$I_{OH} = 1\text{ mA}$ <sup>[2]</sup>   | $V_{DDIO} - 0.45$      | -    | -                      | V             |

|                            |                 | Push-pull 4 mA settings,<br>$I_{OH} = 2\text{ mA}$                  | $V_{DDIO} - 0.45$      | -    | -                      | V             |

|                            |                 | Push-pull 8 mA settings,<br>$I_{OH} = 0.5\text{ mA}$ <sup>[2]</sup> | $V_{DDIO} - 0.45$      | -    | -                      | V             |

|                            |                 | Push-pull 8 mA settings,<br>$I_{OH} = 1\text{ mA}$ <sup>[2]</sup>   | $V_{DDIO} - 0.45$      | -    | -                      | V             |

| Parameter                 | Symbol          | Conditions                                                           | Min                      | Typ | Max  | Unit |

|---------------------------|-----------------|----------------------------------------------------------------------|--------------------------|-----|------|------|

| HIGH-Level Output Voltage | V <sub>OH</sub> | Push-pull 8 mA settings,<br>I <sub>OH</sub> = 2 mA                   | V <sub>DDIO</sub> - 0.45 | -   | -    | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OH</sub> = 0.5 mA <sup>[2]</sup> | V <sub>DDIO</sub> - 0.45 | -   | -    | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OH</sub> = 1 mA <sup>[2]</sup>   | V <sub>DDIO</sub> - 0.45 | -   | -    | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OH</sub> = 2 mA <sup>[2]</sup>   | V <sub>DDIO</sub> - 0.45 | -   | -    | V    |

| LOW-Level Output Voltage  | V <sub>OL</sub> | Push-pull 4 mA settings,<br>I <sub>OL</sub> = 0.5 mA <sup>[2]</sup>  | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 4 mA settings,<br>I <sub>OL</sub> = 1 mA <sup>[2]</sup>    | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 4 mA settings,<br>I <sub>OL</sub> = 2 mA                   | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 8 mA settings,<br>I <sub>OL</sub> = 0.5 mA <sup>[2]</sup>  | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 8 mA settings,<br>I <sub>OL</sub> = 1 mA <sup>[2]</sup>    | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 8 mA settings,<br>I <sub>OL</sub> = 2 mA                   | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OL</sub> = 0.5 mA <sup>[2]</sup> | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OL</sub> = 1 mA <sup>[2]</sup>   | -                        | -   | 0.45 | V    |

|                           |                 | Push-pull 12 mA settings,<br>I <sub>OL</sub> = 2 mA <sup>[2]</sup>   | -                        | -   | 0.45 | V    |

|                           |                 | Open-drain 4 mA settings,<br>I <sub>OL</sub> = 2 mA                  | -                        | -   | 0.45 | V    |

|                           |                 | Open-drain 8 mA settings,<br>I <sub>OL</sub> = 2 mA                  | -                        | -   | 0.45 | V    |

|                           |                 | Open-drain 12 mA settings,<br>I <sub>OL</sub> = 2 mA <sup>[2]</sup>  | -                        | -   | 0.45 | V    |

| HIGH-Level Output Current | I <sub>OH</sub> | Push-pull 4 mA settings,<br>V <sub>OH</sub> = 1.35 V <sup>[2]</sup>  | 4.96                     | -   | -    | mA   |

|                           |                 | Push-pull 8 mA settings,<br>V <sub>OH</sub> = 1.35 V <sup>[2]</sup>  | 6.46                     | -   | -    | mA   |

|                           |                 | Push-pull 12 mA settings,<br>V <sub>OH</sub> = 1.35 V                | 10.83                    | -   | -    | mA   |

| Parameter                                                                                        | Symbol                | Conditions                                                           | Min                 | Typ | Max                  | Unit |

|--------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|---------------------|-----|----------------------|------|

| LOW-Level Output Current                                                                         | I <sub>OL</sub>       | Push-pull 4 mA settings,<br>V <sub>OL</sub> = 0.45 V <sup>[2]</sup>  | 5.95                | -   | -                    | mA   |

|                                                                                                  |                       | Push-pull 8 mA settings,<br>V <sub>OL</sub> = 0.45 V <sup>[2]</sup>  | 8.57                | -   | -                    | mA   |

|                                                                                                  |                       | Push-pull 12 mA settings,<br>V <sub>OL</sub> = 0.45 V                | 14.07               | -   | -                    | mA   |

|                                                                                                  |                       | Open-drain 4 mA settings,<br>V <sub>OL</sub> = 0.45 V <sup>[2]</sup> | 5.95                | -   | -                    | mA   |

|                                                                                                  |                       | Open-drain 8 mA settings,<br>V <sub>OL</sub> = 0.45 V <sup>[2]</sup> | 8.57                | -   | -                    | mA   |

|                                                                                                  |                       | Open-drain 12 mA settings,<br>V <sub>OL</sub> = 0.45 V               | 14.07               | -   | -                    | mA   |

| Max GPIO Output Frequency<br>(20 % - 80 %) <sup>[1]</sup> <sup>[2]</sup>                         | F <sub>IO_MAX</sub>   | Push-pull 4 mA settings,<br>C <sub>LOAD</sub> = 10 pF                | 135                 | 200 | 300                  | MHz  |

|                                                                                                  |                       | Push-pull 8 mA settings,<br>C <sub>LOAD</sub> = 10 pF                | 170                 | 250 | 380                  | MHz  |

|                                                                                                  |                       | Push-pull 12 mA settings,<br>C <sub>LOAD</sub> = 10 pF               | 270                 | 375 | 530                  | MHz  |

| <b>LVCMOS 2.5 V (Compatible with JESD8-5A.01, Normal Range), V<sub>DDIO</sub> = 2.5 V ± 10 %</b> |                       |                                                                      |                     |     |                      |      |

| V <sub>DDIO</sub> Leakage Current                                                                | I <sub>DDIO_LKG</sub> |                                                                      | -                   | 1.6 | 5.8                  | µA   |

| HIGH-Level Input Voltage                                                                         | V <sub>IH</sub>       | Simple Input settings                                                | 1.7                 | -   | 3.465 <sup>[3]</sup> | V    |

|                                                                                                  |                       | Schmitt-trigger input, no PU settings                                | 1.7                 | -   | 3.465 <sup>[3]</sup> | V    |

|                                                                                                  |                       | Schmitt-trigger input, 1xPU settings <sup>[2]</sup>                  | 1.7                 | -   | 3.465 <sup>[3]</sup> | V    |

|                                                                                                  |                       | Schmitt-trigger input, 2xPU settings <sup>[2]</sup>                  | 1.7                 | -   | 3.465 <sup>[3]</sup> | V    |

| LOW-Level Input Voltage                                                                          | V <sub>IL</sub>       | Simple Input settings                                                | -0.3 <sup>[3]</sup> | -   | 0.7                  | V    |

|                                                                                                  |                       | Schmitt-trigger input, no PU settings                                | -0.3 <sup>[3]</sup> | -   | 0.7                  | V    |

|                                                                                                  |                       | Schmitt-trigger input, 1xPU settings <sup>[2]</sup>                  | -0.3 <sup>[3]</sup> | -   | 0.7                  | V    |

|                                                                                                  |                       | Schmitt-trigger input, 2xPU settings <sup>[2]</sup>                  | -0.3 <sup>[3]</sup> | -   | 0.7                  | V    |

| HIGH-Level Output Voltage                                                                        | V <sub>OH</sub>       | Push-pull 4 mA settings,<br>I <sub>OH</sub> = 0.5 mA <sup>[2]</sup>  | 2.1                 | -   | -                    | V    |

|                                                                                                  |                       | Push-pull 4 mA settings,<br>I <sub>OH</sub> = 1 mA <sup>[2]</sup>    | 2.0                 | -   | -                    | V    |

|                                                                                                  |                       | Push-pull 4 mA settings,<br>I <sub>OH</sub> = 2 mA                   | 1.7                 | -   | -                    | V    |