**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**General Description**

The SLG59M1558V is designed for load switching applications with ultra low quiescent current. The part comes with one 28.5 mΩ, 1.0 A rated P-channel MOSFET controlled by a single ON control pin. The product is packaged in an ultra-small 1.0 mm x 1.0 mm package.

**Features**

- One 1.0 A MOSFET

- Ultra Low Quiescent Current

- Low  $R_{DS\text{ON}}$

- 28.5 mΩ at  $V_{IN} = 5.0$  V

- 36.4 mΩ at  $V_{IN} = 3.3$  V

- 44.3 mΩ at  $V_{IN} = 2.5$  V

- 60.8 mΩ at  $V_{IN} = 1.8$  V

- 77.6 mΩ at  $V_{IN} = 1.5$  V

- $V_{IN}$  = 1.5 V to 5.5 V

- Pb-Free / Halogen-Free / RoHS compliant

- STDFN 4L, 1.0 x 1.0 x 0.55 mm

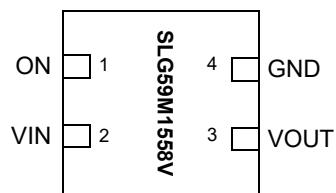

**Pin Configuration**

**4-pin STDFN**

(Top View)

**Applications**

- Notebook Power Rail Switching

- Tablet Power Rail Switching

- Smartphone Power Rail Switching

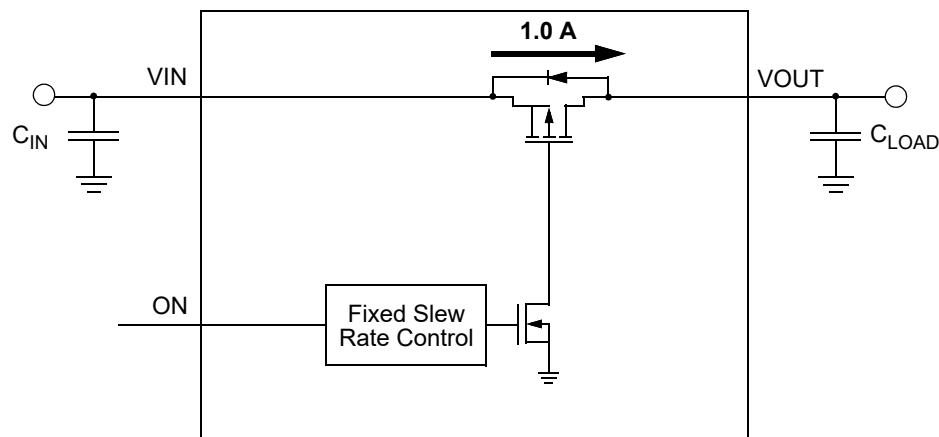

**Block Diagram**

**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**Pin Description**

| Pin # | Pin Name | Type   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ON       | Input  | A low-to-high transition on this pin initiates the operation of the SLG59M1558V. ON is an asserted HIGH, level-sensitive CMOS input with $ON\_V_{IL} < 0.3$ V and $ON\_V_{IH} > 0.85$ V. As the ON pin input circuit does not have an internal pull-down resistor, connect this pin to a general-purpose output (GPO) of a microcontroller, an application processor, or a system controller – do not allow this pin to be open-circuited. |

| 2     | VIN      | MOSFET | Input terminal connection of the power MOSFET. Connect a 10 µF (or larger) low-ESR capacitor from this pin to ground. Capacitors used at VIN should be rated at 10 V or higher.                                                                                                                                                                                                                                                            |

| 3     | VOUT     | MOSFET | Output terminal connection of the power MOSFET. Capacitors used at VOUT should be rated at 10 V or higher.                                                                                                                                                                                                                                                                                                                                 |

| 4     | GND      | GND    | Ground connection. Connect this pin to system analog or power ground plane.                                                                                                                                                                                                                                                                                                                                                                |

**Ordering Information**

| Part Number   | Type                     | Production Flow             |

|---------------|--------------------------|-----------------------------|

| SLG59M1558V   | STDFN 4L                 | Industrial, -40 °C to 85 °C |

| SLG59M1558VTR | STDFN 4L (Tape and Reel) | Industrial, -40 °C to 85 °C |

## Absolute Maximum Ratings

| Parameter                  | Description                   | Conditions                                                                                                                            | Min. | Typ. | Max. | Unit |

|----------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>            | Load Switch Input Voltage     |                                                                                                                                       | --   | --   | 6    | V    |

| T <sub>S</sub>             | Storage Temperature           |                                                                                                                                       | -65  | --   | 140  | °C   |

| T <sub>J</sub>             | Junction Temperature          |                                                                                                                                       | -40  | --   | 150  | °C   |

| ESD <sub>HBM</sub>         | ESD Protection                | Human Body Model                                                                                                                      | 2000 | --   | --   | V    |

| MSL                        | Moisture Sensitivity Level    |                                                                                                                                       |      | 1    |      |      |

| θ <sub>JA</sub>            | Thermal Resistance            | 1.0 x 1.0 mm, 4L STDFN; Determined using 1 in <sup>2</sup> , 2 oz. copper pads under each VIN and VOUT terminals and FR4 pcb material | --   | 122  | --   | °C/W |

| W <sub>DIS</sub>           | Package Power Dissipation     |                                                                                                                                       | --   | --   | 0.5  | W    |

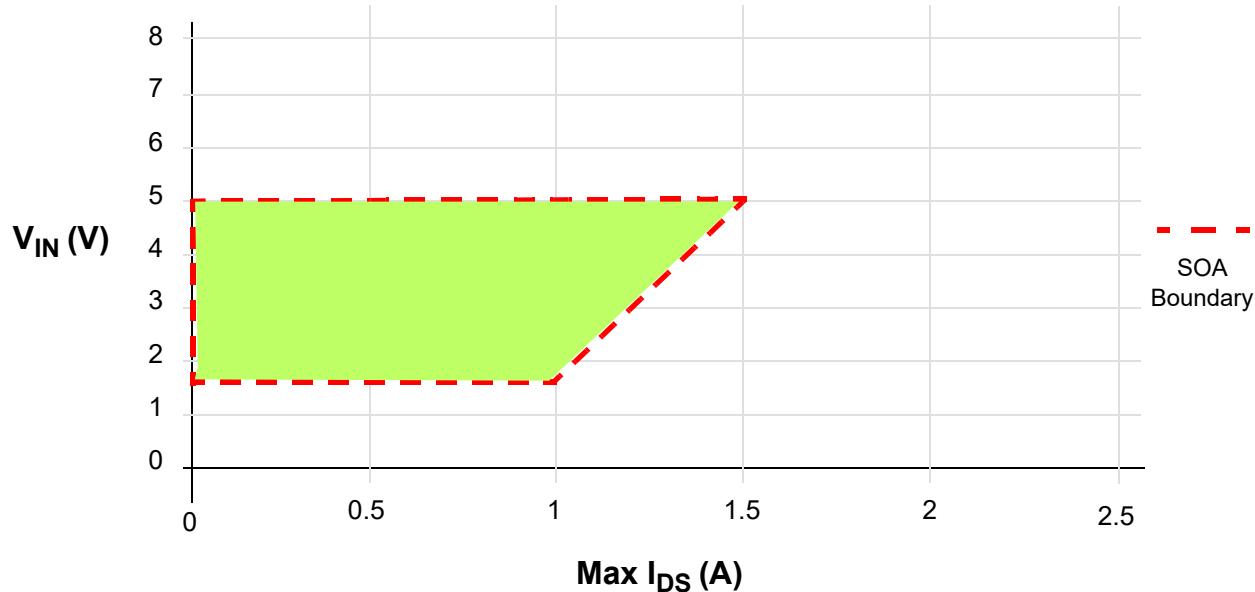

| MOSFET IDS <sub>PEAK</sub> | Peak Current from VIN to VOUT | For no more than 1 ms with 1% duty cycle                                                                                              | --   | --   | 1.5  | A    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## Electrical Characteristics

T<sub>A</sub> = -40 °C to 85 °C unless otherwise noted. Typical values are at T<sub>A</sub> = 25 °C

| Parameter            | Description                           | Conditions                                        | Min. | Typ. | Max. | Unit |

|----------------------|---------------------------------------|---------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>      | Load Switch Input Voltage             | -40 °C to 85 °C                                   | 1.5  | --   | 5.5  | V    |

| I <sub>IN</sub>      | Load Switch Input Current (PIN 2)     | when OFF, V <sub>IN</sub> = 5.5 V, No load        | --   | 0.02 | 1    | µA   |

|                      |                                       | when ON, ON = V <sub>IN</sub> , No load           | --   | 0.05 | 0.5  | µA   |

| I <sub>FET_OFF</sub> | MOSFET OFF Leakage Current            | ON = LOW; V <sub>IN</sub> = 5.5 V                 | --   | 0.05 | 1    | µA   |

| I <sub>ON_LKG</sub>  | ON Pin Input Leakage                  |                                                   | --   | --   | 0.1  | µA   |

| RDS <sub>ON</sub>    | ON Resistance, T <sub>A</sub> = 25 °C | V <sub>IN</sub> = 5.5 V, I <sub>DS</sub> = 100 mA | --   | 28.5 | 32.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 3.3 V, I <sub>DS</sub> = 100 mA | --   | 36.4 | 40.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 2.5 V, I <sub>DS</sub> = 100 mA | --   | 44.3 | 49.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 1.8 V, I <sub>DS</sub> = 100 mA | --   | 60.8 | 65.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 1.5 V, I <sub>DS</sub> = 100 mA | --   | 77.6 | 82.0 | mΩ   |

| RDS <sub>ON</sub>    | ON Resistance, T <sub>A</sub> = 85 °C | V <sub>IN</sub> = 5.5 V, I <sub>DS</sub> = 100 mA | --   | 34.0 | 36.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 3.3 V, I <sub>DS</sub> = 100 mA | --   | 43.8 | 46.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 2.5 V, I <sub>DS</sub> = 100 mA | --   | 53.3 | 56.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 1.8 V, I <sub>DS</sub> = 100 mA | --   | 72.2 | 76.0 | mΩ   |

|                      |                                       | V <sub>IN</sub> = 1.5 V, I <sub>DS</sub> = 100 mA | --   | 90.7 | 94.0 | mΩ   |

| MOSFET IDS           | Current from VIN to VOUT              | Continuous                                        | --   | --   | 1.0  | A    |

## Electrical Characteristics (continued)

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted. Typical values are at  $T_A = 25^\circ\text{C}$

| Parameter        | Description                  | Conditions                                                                                                                           | Min. | Typ. | Max.     | Unit |

|------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|

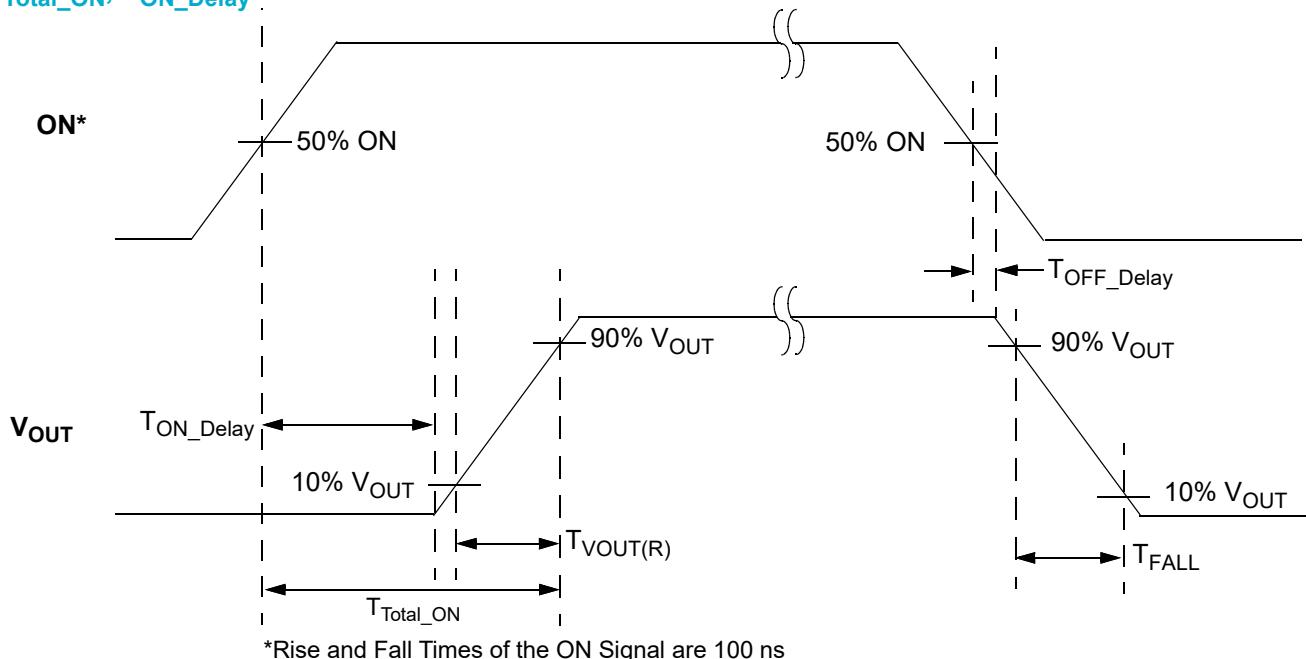

| $T_{ON\_Delay}$  | ON Delay Time                | 50% ON to $V_{OUT}$ Ramp Start;<br>$V_{IN} = 5\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$    | 10   | 15   | 27       | μs   |

|                  |                              | 50% ON to $V_{OUT}$ Ramp Start;<br>$V_{IN} = 3.3\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$  | 17   | 31   | 40       | μs   |

|                  |                              | 50% ON to $V_{OUT}$ Ramp Start;<br>$V_{IN} = 1.5\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$  | 44   | 69   | 96       | μs   |

| $T_{Total\_ON}$  | Total Turn ON Time           | 50% ON to 90% $V_{OUT}$ ;<br>$V_{IN} = 5.0\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$        | 114  | 122  | 134      | μs   |

|                  |                              | 50% ON to 90% $V_{OUT}$ ;<br>$V_{IN} = 3.3\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$        | 146  | 156  | 176      | μs   |

|                  |                              | 50% ON to 90% $V_{OUT}$ ;<br>$V_{IN} = 1.5\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$        | 292  | 332  | 399      | μs   |

| $T_{VOUT(R)}$    | $V_{OUT}$ Rise Time          | 10% $V_{OUT}$ to 90% $V_{OUT}$ ;<br>$V_{IN} = 5.0\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$ | 92   | 97   | 107      | μs   |

|                  |                              | 10% $V_{OUT}$ to 90% $V_{OUT}$ ;<br>$V_{IN} = 3.3\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$ | 116  | 120  | 131      | μs   |

|                  |                              | 10% $V_{OUT}$ to 90% $V_{OUT}$ ;<br>$V_{IN} = 1.5\text{ V}$ , $C_{LOAD} = 0.1\text{ }\mu\text{F}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$ | 228  | 253  | 296      | μs   |

| ON_ $V_{IH}$     | High Input Voltage on ON pin |                                                                                                                                      | 0.85 | --   | $V_{IN}$ | V    |

| ON_ $V_{IL}$     | Low Input Voltage on ON pin  |                                                                                                                                      | -0.3 | 0    | 0.3      | V    |

| $T_{OFF\_Delay}$ | OFF Delay Time               | 50% ON to $V_{OUT}$ Fall Start, $V_{IN} = 5\text{ V}$ ,<br>$R_{LOAD} = 10\text{ }\Omega$ , no $C_{LOAD}$                             | 6.2  | 6.5  | 7.0      | μs   |

## SLG59M1558V

An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load SwitchV<sub>IN</sub> vs. Max I<sub>DS</sub>, Safe Operation AreaT<sub>Total\_ON</sub>, T<sub>ON\_Delay</sub> and Rise Time Measurement

**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**SLG59M1558V Power-Up/Power-Down Sequence Considerations**

A nominal power-up sequence is to apply  $V_{IN}$  and toggle the ON pin LOW-to-HIGH after  $V_{IN}$  is at least 90% of its final value. A nominal power-down sequence is the power-up sequence in reverse order. If  $V_{IN}$  ramp is too fast, a voltage glitch may appear on the output pin at  $V_{OUT}$ . To prevent glitches at the output, it is recommended to connect at least 0.1uF capacitor from the  $V_{OUT}$  pin to GND and to keep the  $V_{IN}$  ramp time higher than 2 ms.

**Power Dissipation Considerations**

The junction temperature of the SLG59M1558V depends on factors such as board layout, ambient temperature, external air flow over the package, load current, and the  $R_{DS\text{ON}}$  generated voltage drop across each power MOSFET. While the primary contributor to the increase in the junction temperature of the SLG59M1558V is the power dissipation of its power MOSFETs, its power dissipation and the junction temperature in nominal operating mode can be calculated using the following equations:

$$PD_{\text{TOTAL}} = R_{DS\text{ON}} \times I_{DS}^2$$

where:

$PD_{\text{TOTAL}}$  = Total package power dissipation, in Watts (W)

$R_{DS\text{ON}}$  = Power MOSFET ON resistance, in Ohms (Ω)

$I_{DS}$  = Output current, in Amps (A)

and

$$T_J = PD_{\text{TOTAL}} \times \theta_{JA} + T_A$$

where:

$T_J$  = Die junction temperature, in Celsius degrees (°C)

$\theta_{JA}$  = Package thermal resistance, in Celsius degrees per Watt (°C/W) – highly dependent on pcb layout

$T_A$  = Ambient temperature, in Celsius degrees (°C)

In nominal operating mode, the SLG59M1558V's power dissipation can also be calculated by taking into account the voltage drop across the load switch ( $V_{IN} - V_{OUT}$ ) and the magnitude of the switch's output current ( $I_{DS}$ ):

$$PD_{\text{TOTAL}} = (V_{IN} - V_{OUT}) \times I_{DS} \text{ or}$$

$$PD_{\text{TOTAL}} = (V_{IN} - (R_{LOAD} \times I_{DS})) \times I_{DS}$$

where:

$PD_{\text{TOTAL}}$  = Total package power dissipation, in Watts (W)

$V_{IN}$  = Switch input Voltage, in Volts (V)

$R_{LOAD}$  = Output Load Resistance, in Ohms (Ω)

$I_{DS}$  = Switch output current, in Amps (A)

$V_{OUT}$  = Switch output voltage, or  $R_{LOAD} \times I_{DS}$

**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**SLG59M1558V Layout Suggestion**

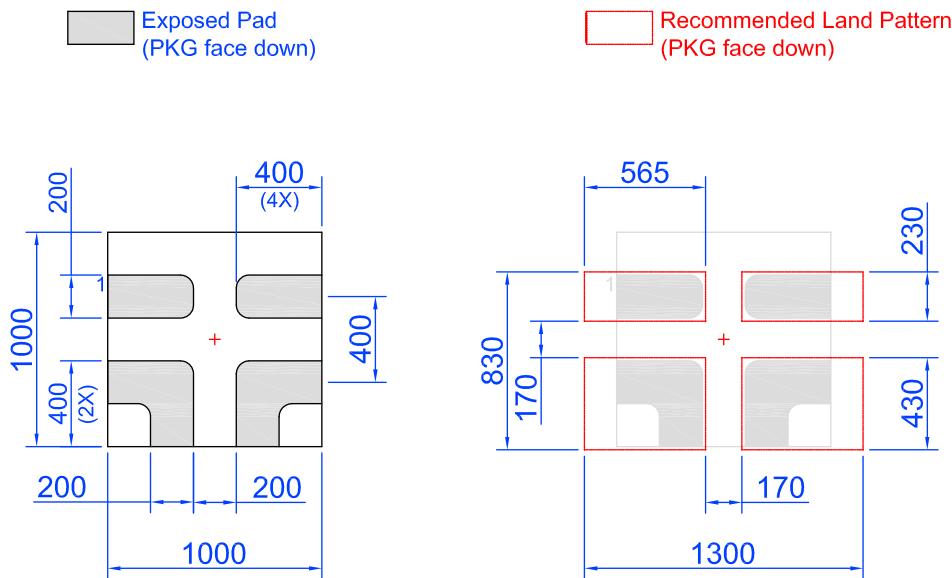

Note: All dimensions shown in micrometers (μm)

**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**Layout Guidelines:**

1. Since the VIN and VOUT pins dissipate most of the heat generated during high-load current operation, it is highly recommended to make power traces as short, direct, and wide as possible. A good practice is to make power traces with an absolute minimum widths of 15 mils (0.381 mm) per Ampere. A representative layout, shown in [Figure 1](#) illustrates proper techniques for heat to transfer as efficiently as possible out of the device;

2. To minimize the effects of parasitic trace inductance on normal operation, it is recommended to connect input C<sub>IN</sub> and output C<sub>LOAD</sub> low-ESR capacitors as close as possible to the SLG59M1558V's VIN and VOUT pins;

3. The GND pin should be connected to system analog or power ground plane.

4. 2 oz. copper is recommended for high current operation.

**SLG59M1558V Evaluation Board:**

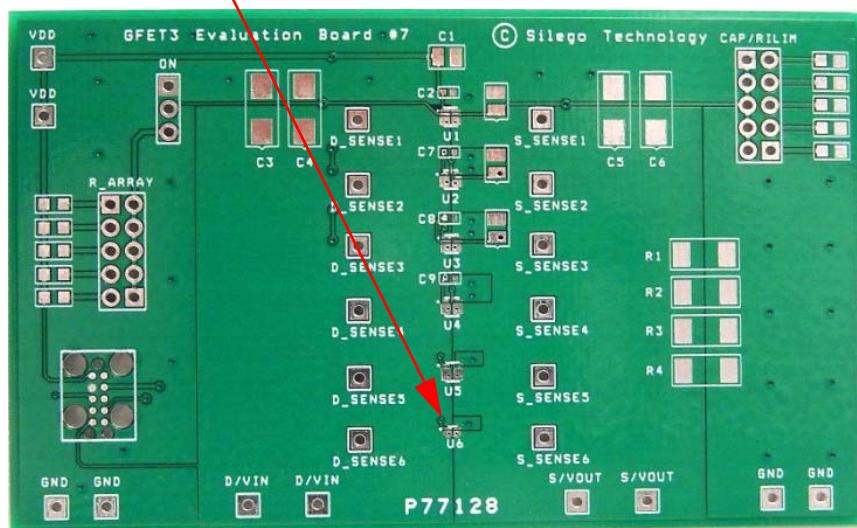

A GreenFET Evaluation Board for SLG59M1558V is designed according to the statements above and is illustrated on [Figure 1](#). Please note that evaluation board has D\_Sense and S\_Sense pads. They cannot carry high currents and dedicated only for RDS<sub>ON</sub> evaluation.

Please solder your SLG59M1558V here

**Figure 1. SLG59M1558V Evaluation Board**

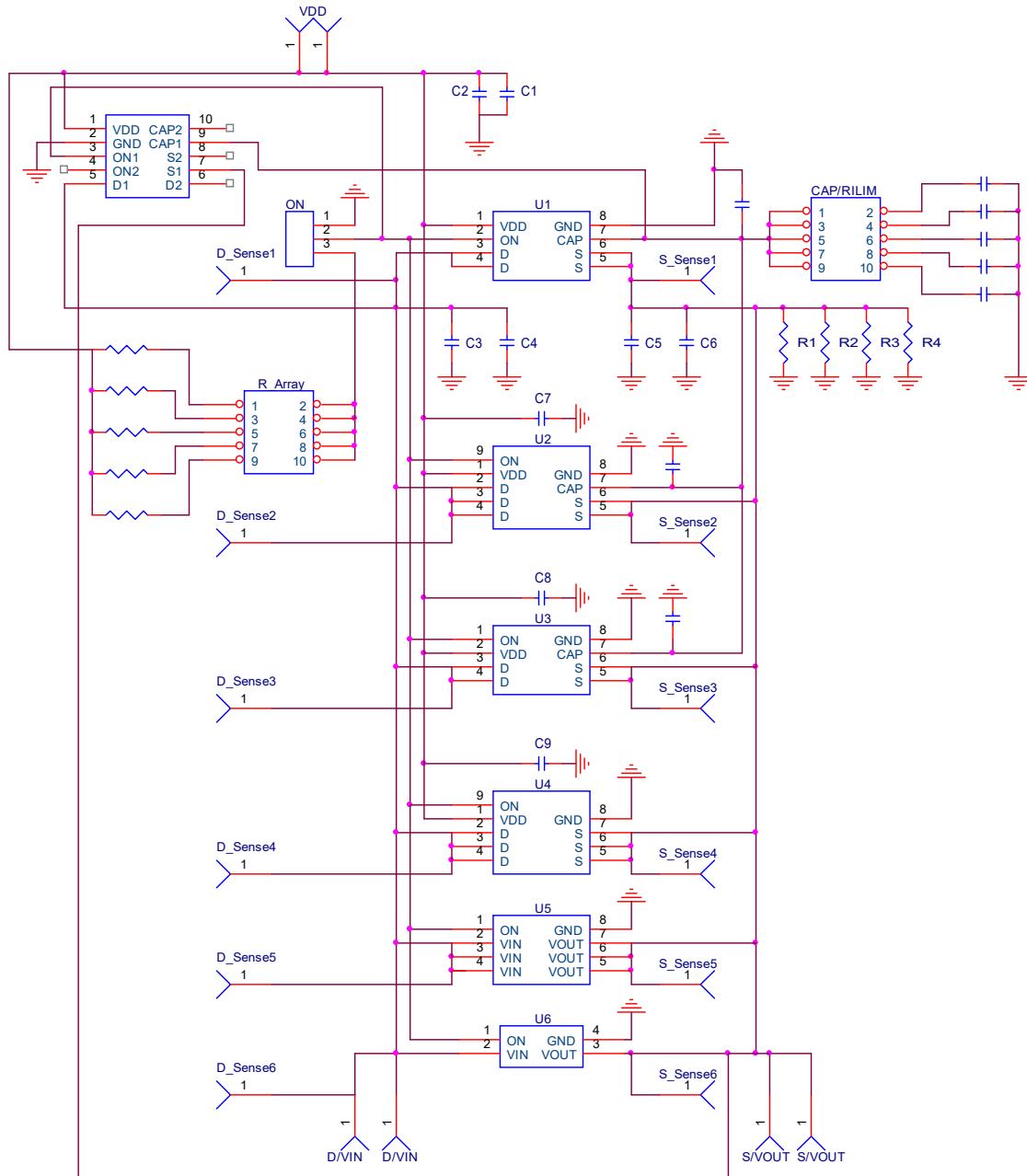

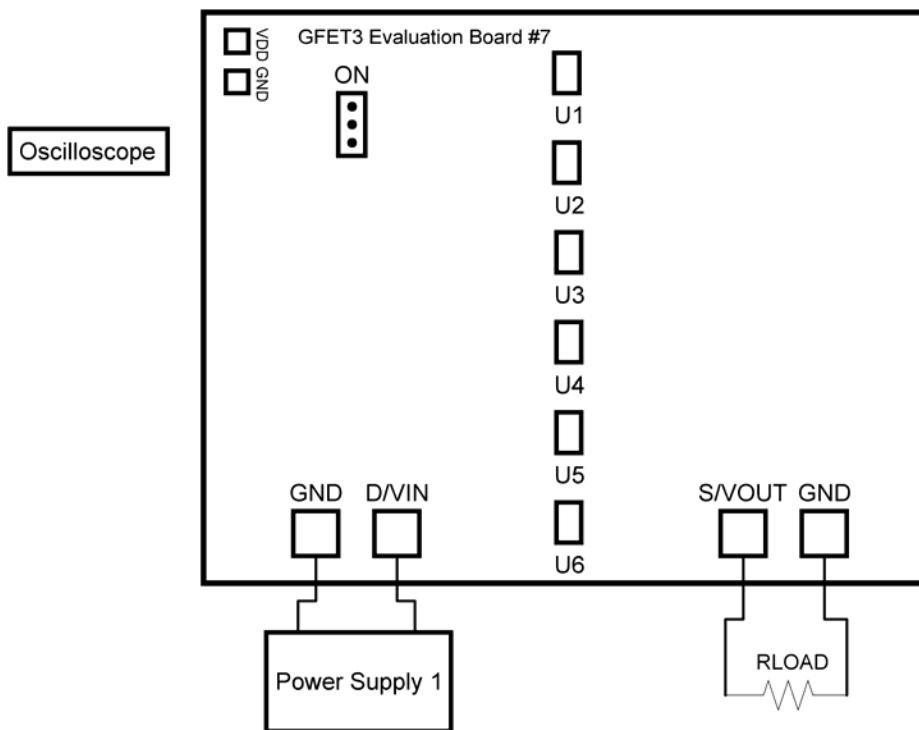

Figure 2. SLG59M1558V Evaluation Board Connection Circuit

# SLG59M1558V

An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch

## Basic Test Setup and Connections

Figure 3. SLG59M1558V Evaluation Board Connection Circuit

### EVB Configuration

1. Connect oscilloscope probes to D/VIN, S/VOUT, ON, etc.;

2. Turn on Power Supply 1 and set desired  $V_{IN}$  from 1.5 V...5.5 V range;

3. Toggle the ON signal High or Low to observe SLG59M1558V operation.

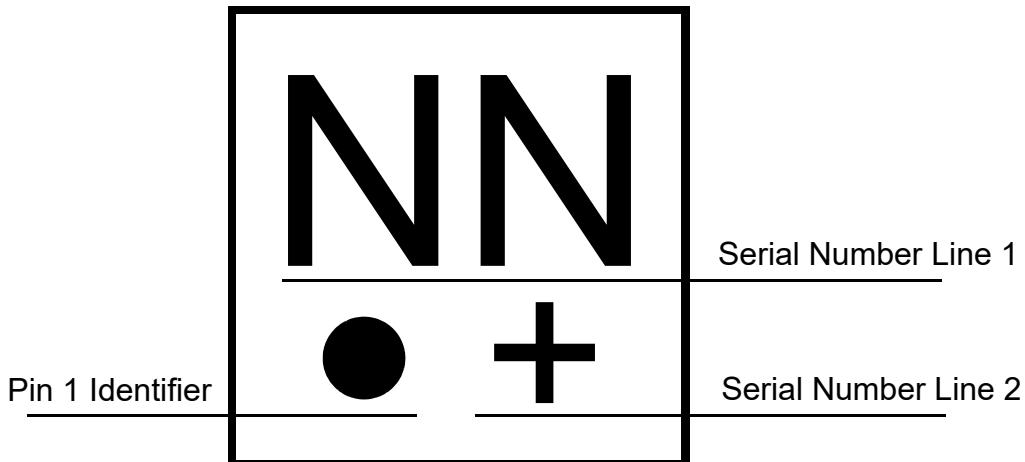

## Package Top Marking System Definition

NN -Part Serial Number Field Line 1

where each "N" character can be A-Z and 0-9

+ -Part Serial Number Field Line 2

where "+" character can be +, -, =, or blank

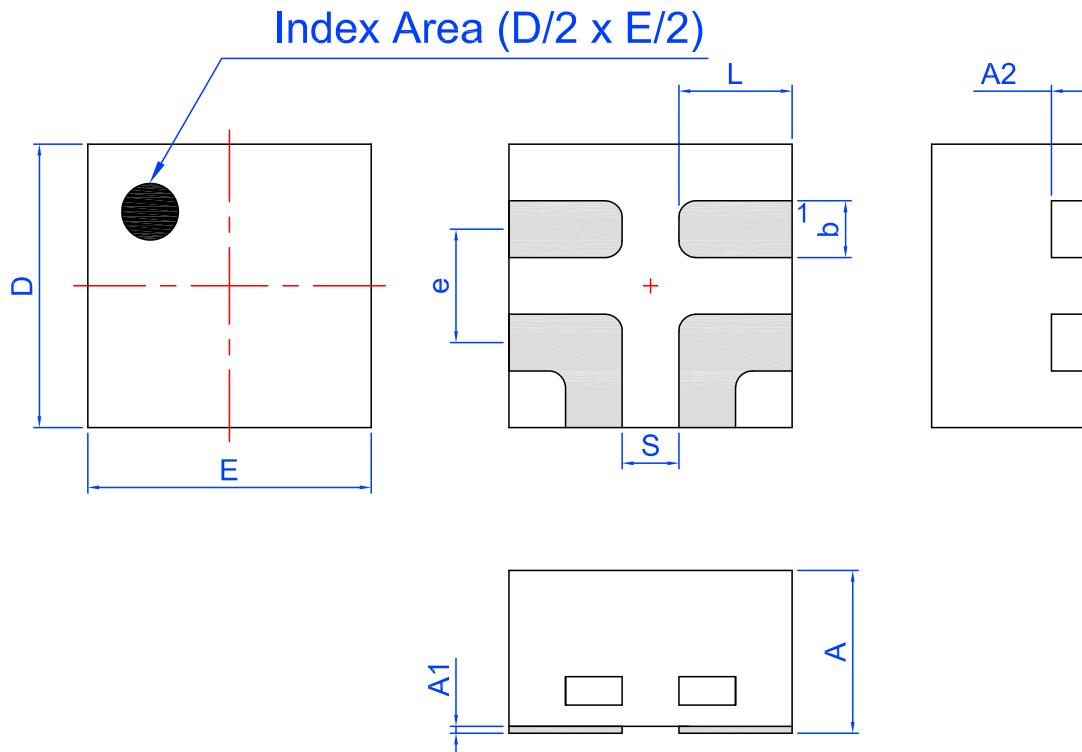

## Package Drawing and Dimensions

4 Lead STDFN Package 1.0 x 1.0 mm

Unit: mm

| Symbol | Min      | Nom. | Max   | Symbol | Min     | Nom. | Max  |

|--------|----------|------|-------|--------|---------|------|------|

| A      | 0.50     | 0.55 | 0.60  | D      | 0.95    | 1.00 | 1.05 |

| A1     | 0.005    | -    | 0.060 | E      | 0.95    | 1.00 | 1.05 |

| A2     | 0.10     | 0.15 | 0.20  | L      | 0.35    | 0.40 | 0.45 |

| b      | 0.15     | 0.20 | 0.25  | S      | 0.2 REF |      |      |

| e      | 0.40 BSC |      |       |        |         |      |      |

## SLG59M1558V

An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch

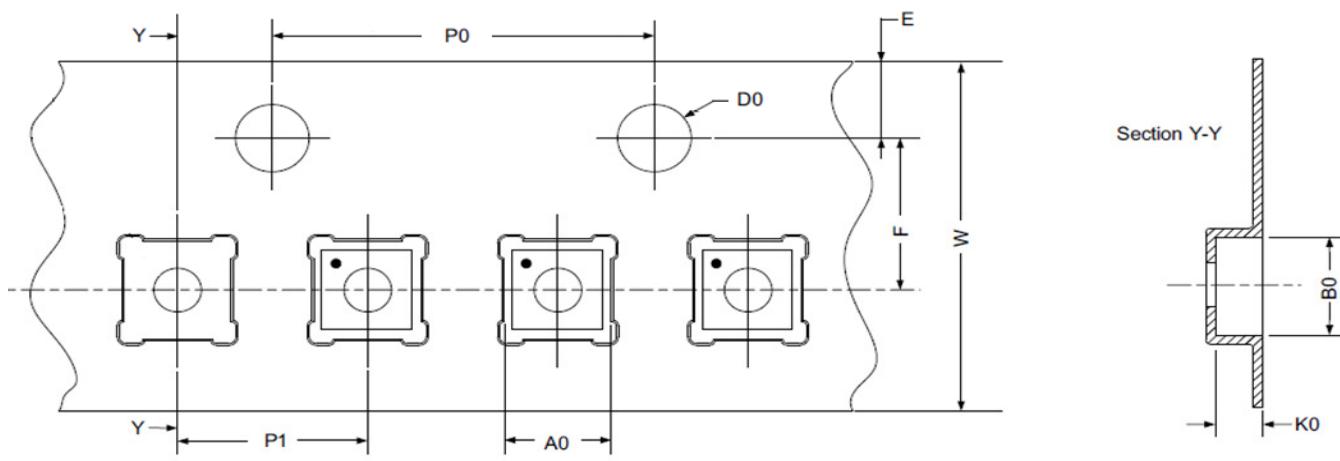

## Tape and Reel Specifications

| Package Type   | # of Pins | Nominal Package Size [mm] | Max Units |         | Reel & Hub Size [mm] | Leader (min) |             | Trailer (min) |             | Tape Width [mm] | Part Pitch [mm] |

|----------------|-----------|---------------------------|-----------|---------|----------------------|--------------|-------------|---------------|-------------|-----------------|-----------------|

|                |           |                           | per Reel  | per Box |                      | Pockets      | Length [mm] | Pockets       | Length [mm] |                 |                 |

| STDFN 4L Green | 4         | 1.0 x 1.0 x 0.55          | 8000      | 8000    | 178 / 60             | 200          | 400         | 200           | 400         | 8               | 2               |

## Carrier Tape Drawing and Dimensions

| Package Type   | Pocket BTM Length | Pocket BTM Width | Pocket Depth | Index Hole Pitch | Pocket Pitch | Index Hole Diameter | Index Hole to Tape Edge | Index Hole to Pocket Center | Tape Width |

|----------------|-------------------|------------------|--------------|------------------|--------------|---------------------|-------------------------|-----------------------------|------------|

|                | A0                | B0               | K0           | P0               | P1           | D0                  | E                       | F                           | W          |

| STDFN 4L Green | 1.16              | 1.16             | 0.63         | 4                | 2            | 1.5                 | 1.75                    | 3.5                         | 8          |

## Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 0.55 mm<sup>3</sup> (nominal). More information can be found at [www.jedec.org](http://www.jedec.org).

**SLG59M1558V**An Ultra-small 1.0 mm<sup>2</sup>, 28.5 mΩ, 1.0 A, Load Switch**Revision History**

| Date       | Version | Change                                                                                                                                              |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 8/7/2023   | 1.08    | Fixed typo in Title                                                                                                                                 |

| 2/2/2022   | 1.07    | Updated Company name and logo<br>Fixed typos                                                                                                        |

| 10/27/2020 | 1.06    | Added MSL to Abs Max Table                                                                                                                          |

| 6/10/2020  | 1.05    | Updated Style and formatting<br>Added Power Dissipation Considerations<br>Added Layout Guidelines<br>Fixed typos                                    |

| 11/14/2017 | 1.04    | Updated Package Marking Definition                                                                                                                  |

| 11/30/2016 | 1.03    | Fixed Parameter name from VDD to VIN in Abs. Max Table                                                                                              |

| 6/22/2016  | 1.02    | Added section on Power Up/Down Sequence Considerations<br>Removed IDS_lkg parameter (same as IDD when OFF)<br>Updated Recommended Layout suggestion |

| 9/11/2015  | 1.01    | Updated IDD and Tdelay_ON                                                                                                                           |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).