## SLG47105V Training Board HVPAK Design

### General Description

The SLG7RN46465 provides a small, low power component for commonly used Mixed-Signal and H-Bridge functions.

The SoC is housed in a 2mm x 3mm STQFN package which is optimal for using with small devices.

Configurable PWM macrocells in combination with Special High Voltage outputs will be useful for a motor drive or load drive applications. High Voltage pins allow to design smart level translators or to drive the high voltage high current load.

### Features

- Low Power Consumption

- Pb - Free / RoHS Compliant

- Halogen - Free

- STQFN - 20 Package

- Four High Voltage High Current Drive GPOs

- Current up to 1.5A RMS per GPO/ H-Bridge

- Differential Amplifier with Integrator

- Two Current Sense Comparators

- Two PWM Macrocells

### Output Summary

2 Outputs - High Drive Push Pull

2 Outputs - Push Pull 2X

### Pin name

| Pin # | Pin name   | Pin # | Pin name  |

|-------|------------|-------|-----------|

| 1     | VDD        | 11    | VDD2      |

| 2     | STATUS     | 12    | GND       |

| 3     | START/STOP | 13    | GND       |

| 4     | GND        | 14    | DIRECTION |

| 5     | ISENSE     | 15    | SCL       |

| 6     | VDD2       | 16    | SDA       |

| 7     | M+         | 17    | MODE      |

| 8     | M-         | 18    | GND       |

| 9     | NC         | 19    | M- FB     |

| 10    | NC         | 20    | M+ FB     |

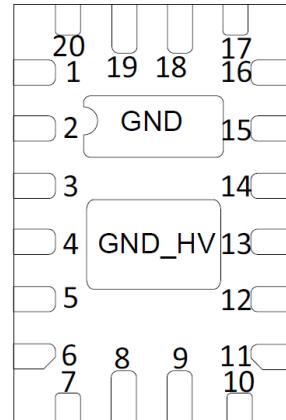

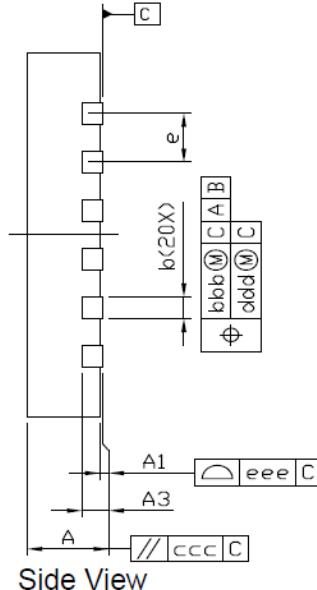

### Pin Configuration

**STQFN-20L

(Top View)**

# SLG47105V Training Board HVPAK Design

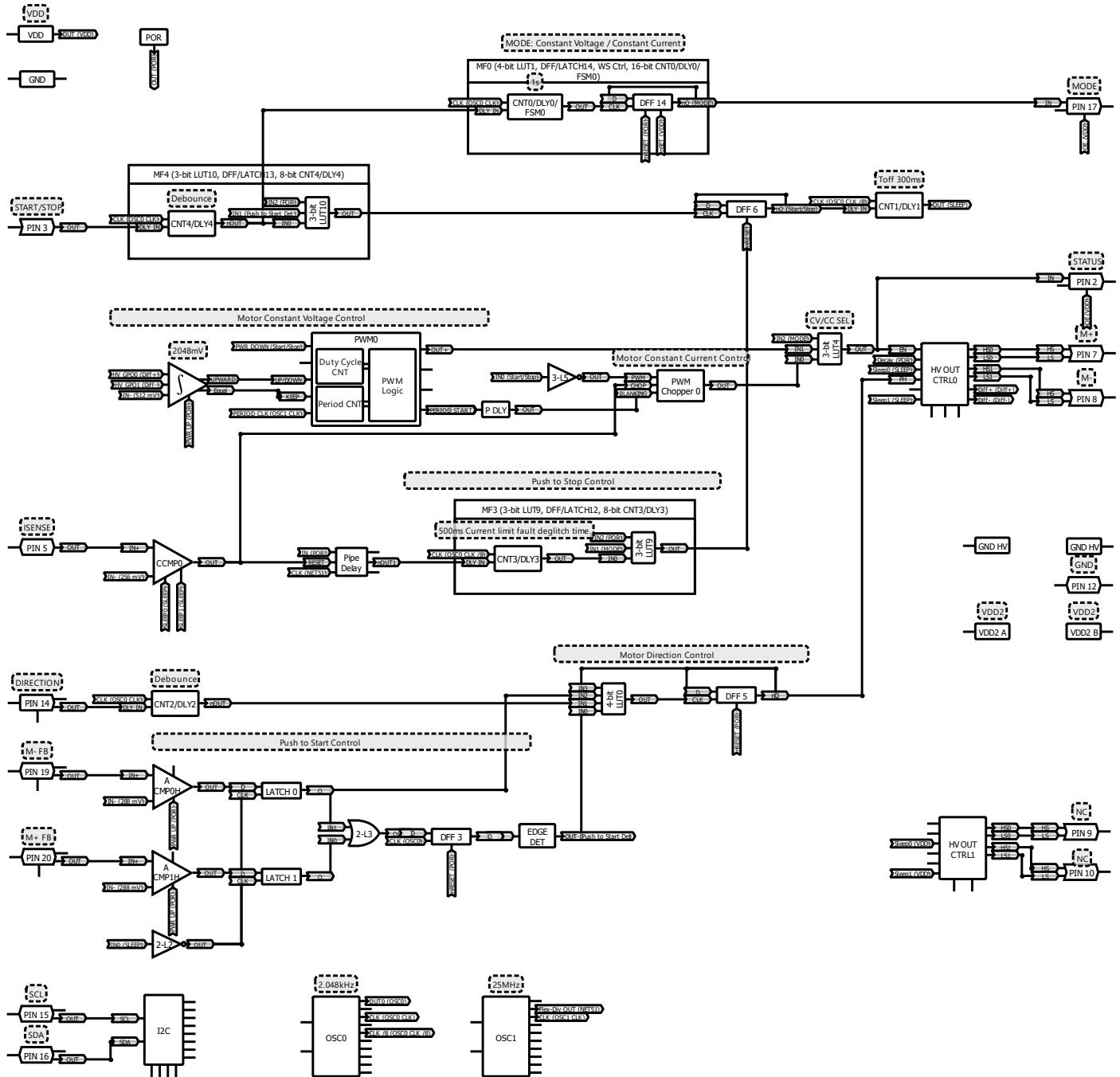

## Block Diagram

## SLG47105V Training Board HVPAK Design

## Pin Configuration

| Pin # | Pin Name    | Type                | Pin Description                       | Internal Resistor |

|-------|-------------|---------------------|---------------------------------------|-------------------|

| 1     | VDD         | PWR                 | Supply Voltage                        | --                |

| 2     | STATUS      | Digital Output      | Push Pull 2X                          | floating          |

| 3     | START /STOP | Digital Input       | Digital Input with Schmitt trigger    | 10kΩ pullup       |

| 4     | GND         | GND                 | Ground                                | --                |

| 5     | ISENSE      | Analog Input/Output | Analog Input/Output                   | floating          |

| 6     | VDD2_A      | PWR                 | Supply Voltage                        |                   |

| 7     | M+          | High Drive Output   | High Drive Push Pull                  | floating          |

| 8     | M-          | High Drive Output   | High Drive Push Pull                  | floating          |

| 9     | NC          | --                  | Keep Floating or Connect to GND       | --                |

| 10    | NC          | --                  | Keep Floating or Connect to GND       | --                |

| 11    | VDD2_B      | PWR                 | Supply Voltage                        |                   |

| 12    | GND         | Analog Input/Output | Analog Input/Output                   | floating          |

| 13    | GND         | GND                 | Ground                                | --                |

| 14    | DIRECTION   | Digital Input       | Digital Input with Schmitt trigger    | 10kΩ pullup       |

| 15    | SCL         | Digital Input       | Digital Input without Schmitt trigger | floating          |

| 16    | SDA         | Digital Input       | Digital Input without Schmitt trigger | floating          |

| 17    | MODE        | Digital Output      | Push Pull 2X                          | floating          |

| 18    | GND         | GND                 | Ground                                | --                |

| 19    | M- FB       | Analog Input/Output | Analog Input/Output                   | 10kΩ pulldown     |

| 20    | M+ FB       | Analog Input/Output | Analog Input/Output                   | 10kΩ pulldown     |

## Ordering Information

| Part Number    | Package Type                            |

|----------------|-----------------------------------------|

| SLG7RN46465V   | 20-pin STQFN                            |

| SLG7RN46465VTR | 20-pin STQFN - Tape and Reel (3k units) |

**Absolute Maximum Conditions**

| Parameter                                         | Description                                           | Condition                            | Min.                | Max.       | Unit                         |

|---------------------------------------------------|-------------------------------------------------------|--------------------------------------|---------------------|------------|------------------------------|

| Supply voltage on VDD relative to GND             |                                                       |                                      | -0.3                | 7.0        | V                            |

| Supply voltage on VDD2 relative to GND            |                                                       |                                      | -0.3                | 18         | V                            |

| DC Input Voltage                                  |                                                       |                                      | GND - 0.5V          | VDD + 0.5V | V                            |

| Maximum VDD Average or DC Current                 | (Through VDD or GND pin) for VDD group                |                                      | --                  | 120        | mA                           |

| Maximum VDD2 Average or DC Current                | (Through each VDD2_A, VDD2_B, SENSE_A or SENSE_B pin) |                                      | --                  | 2000       | mA                           |

| Maximum Average or DC Current (VDD power supply)  | Push-Pull 2x                                          | Through VDD Group pins               | TJ = -40°C to 85°C  | --         | 16 mA                        |

| Maximum Average or DC Current (VDD power supply)  | Push-Pull 2x                                          | Through VDD Group pins.              | TJ = -40°C to 150°C | --         | 7.6 mA                       |

| Maximum Average or DC Current (VDD2 power supply) | Push-Pull /Half Bridge                                | Through VDD2 High Current Group pins |                     | --         | 1500 mA                      |

| Maximum pulsed current sink/sourced per HV HD pin |                                                       | Pulse width < 0.5ms; duty cycle < 2% |                     | --         | Internally limited by OCP mA |

| Current at Input Pin                              |                                                       | Through VDD Group pin                |                     | -0.1       | 1.0 mA                       |

| Input Leakage Current (Absolute Value)            |                                                       |                                      | --                  | 1000 nA    |                              |

| Storage Temperature Range                         |                                                       |                                      | -65                 | 150        | °C                           |

| Junction Temperature                              |                                                       |                                      | --                  | 150        | °C                           |

| ESD Protection (Human Body Model)                 |                                                       |                                      |                     | 4000       | -- V                         |

| ESD Protection (Charged Device Model)             |                                                       |                                      |                     | 1300       | -- V                         |

| Moisture Sensitivity Level                        |                                                       |                                      |                     | 1          |                              |

**Thermal Information**

| Parameter                 | Description                                       | Condition                                                                               | Min. | Typ.  | Max. | Unit |

|---------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------|------|-------|------|------|

| $\Theta_{JA}$             | Thermal Resistance                                | 4L JEDEC PCB                                                                            | --   | --    | 65   | °C/W |

| $\Theta_{JA}$             | Thermal Resistance                                | 4L JEDEC PCB with a thermal vias that connect thermal pad through all layers of the PCB | --   | --    | 46   | °C/W |

| $\Theta_{JC(\text{top})}$ | Junction-to-case (top) Thermal Resistance         |                                                                                         | --   | 23.50 | --   | °C/W |

| $\Theta_{JB}$             | Junction-to-board Thermal Resistance              |                                                                                         | --   | 25.51 | --   | °C/W |

| $\Psi_{JC(\text{top})}$   | Junction-to-case (top) Characterization Parameter |                                                                                         | --   | 6.80  | --   | °C/W |

| $\Psi_{JB}$               | Junction-to-board Characterization Parameter      |                                                                                         | --   | 24.44 | --   | °C/W |

## SLG47105V Training Board HVPAK Design

## Electrical Characteristics

| Symbol       | Parameter                                                                                   | Condition/Note                                           | Min.     | Typ. | Max.     | Unit |

|--------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|------|----------|------|

| $V_{DD}$     | Supply Voltage                                                                              |                                                          | 2.3      | 3.3  | 5.5      | V    |

| $V_{DD2\_A}$ | Supply Voltage                                                                              |                                                          | 3        | 12   | 13.2     | V    |

| $V_{DD2\_B}$ | Supply Voltage                                                                              |                                                          | 3        | 12   | 13.2     | V    |

| $T_A$        | Operating Temperature                                                                       |                                                          | -40      | 25   | 85       | °C   |

| $C_{VDD}$    | Capacitor Value at VDD                                                                      |                                                          | 0.1      | --   | --       | μF   |

| $C_{IN}$     | Input Capacitance                                                                           |                                                          | --       | 4    | --       | pF   |

| $I_Q$        | Quiescent Current VDD side                                                                  | Static inputs and floating outputs                       | --       | 46   | --       | μA   |

| $V_{IH}$     | HIGH-Level Input Voltage (Note 3)                                                           | Logic Input (Note 1)                                     | 0.7x VDD | --   | VDD+ 0.3 | V    |

|              |                                                                                             | Logic Input with Schmitt Trigger                         | 0.8x VDD | --   | VDD+ 0.3 | V    |

| $V_{IL}$     | LOW-Level Input Voltage (Note 3)                                                            | Logic Input (Note 1)                                     | GND- 0.3 | --   | 0.3x VDD | V    |

|              |                                                                                             | Logic Input with Schmitt Trigger                         | GND- 0.3 | --   | 0.2x VDD | V    |

| $V_{OH}$     | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$  | Push-Pull 2X, $I_{OH}=1\text{mA}$ at $VDD=2.5\text{V}$   | 2.13     | --   | --       | V    |

|              | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$  | Push-Pull 2X, $I_{OH}=3\text{mA}$ at $VDD=3.3\text{V}$   | 2.69     | --   | --       | V    |

|              | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$  | Push-Pull 2X, $I_{OH}=5\text{mA}$ at $VDD=5.0\text{V}$   | 4.11     | --   | --       | V    |

|              | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $150^\circ\text{C}$ | Push-Pull 2X, $I_{OH}=1\text{mA}$ at $VDD=2.5\text{V}$   | 2.12     | --   | --       | V    |

|              | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $150^\circ\text{C}$ | Push-Pull 2X, $I_{OH}=3\text{mA}$ at $VDD=3.3\text{V}$   | 2.67     | --   | --       | V    |

|              | HIGH-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $150^\circ\text{C}$ | Push-Pull 2X, $I_{OH}=5\text{mA}$ at $VDD=5.0\text{V}$   | 4.09     | --   | --       | V    |

| $V_{OL}$     | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$   | Push-Pull 2X, $I_{OL}=1\text{mA}$ , at $VDD=2.5\text{V}$ | --       | --   | 0.04     | V    |

|              | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$   | Push-Pull 2X, $I_{OL}=3\text{mA}$ , at $VDD=3.3\text{V}$ | --       | --   | 0.09     | V    |

|              | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $85^\circ\text{C}$   | Push-Pull 2X, $I_{OL}=5\text{mA}$ , at $VDD=5.0\text{V}$ | --       | --   | 0.11     | V    |

|              | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $150^\circ\text{C}$  | Push-Pull 2X, $I_{OL}=1\text{mA}$ , at $VDD=2.5\text{V}$ | --       | --   | 0.04     | V    |

|              | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^\circ\text{C}$ to $150^\circ\text{C}$  | Push-Pull 2X, $I_{OL}=3\text{mA}$ , at $VDD=3.3\text{V}$ | --       | --   | 0.11     | V    |

## SLG47105V Training Board HVPAK Design

|           |                                                                                                                         |                                                               |        |    |       |    |

|-----------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|----|-------|----|

|           | LOW-Level Output Voltage for $V_{DD}$ Group $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$                          | Push-Pull 2X, $I_{OL}=5\text{mA}$ , at $VDD=5.0\text{V}$      | --     | -- | 0.13  | V  |

| $V_{OH2}$ | HIGH-Level Output Voltage for $V_{DD2}$ High Current Group                                                              | Push-Pull, $V_{DD}=5\pm10\%$ , $I_{OH2}=10\text{mA}$          | 4.496  | -- | --    | V  |

|           |                                                                                                                         | Push-Pull, $V_{DD}=9\text{V}\pm10\%$ , $I_{OH2}=10\text{mA}$  | 8.097  | -- | --    | V  |

|           |                                                                                                                         | Push-Pull, $V_{DD}=12\text{V}\pm10\%$ , $I_{OH2}=10\text{mA}$ | 10.797 | -- | --    | V  |

| $V_{OL2}$ | LOW-Level Output Voltage for $V_{DD2}$ High Current Group                                                               | Push-Pull, $V_{DD}=5\pm10\%$ , $I_{OL2}=10\text{mA}$          | --     | -- | 0.004 | V  |

|           |                                                                                                                         | Push-Pull, $V_{DD}=9\text{V}\pm10\%$ , $I_{OL2}=10\text{mA}$  | --     | -- | 0.004 | V  |

|           |                                                                                                                         | Push-Pull, $V_{DD}=12\text{V}\pm10\%$ , $I_{OL2}=10\text{mA}$ | --     | -- | 0.004 | V  |

| $I_{OH}$  | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$  | Push-Pull 2X, $VOH=VDD-0.2\text{V}$ at $VDD=2.5\text{V}$      | 2.87   | -- | --    | mA |

|           | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$  | Push-Pull 2X, $VOH=2.4\text{V}$ at $VDD=3.3\text{V}$          | 9.56   | -- | --    | mA |

|           | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$  | Push-Pull 2X, $VOH=2.4\text{V}$ at $VDD=5.0\text{V}$          | 36.83  | -- | --    | mA |

|           | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$ | Push-Pull 2X, $VOH=VDD-0.2\text{V}$ at $VDD=2.5\text{V}$      | 2.52   | -- | --    | mA |

|           | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$ | Push-Pull 2X, $VOH=2.4\text{V}$ at $VDD=3.3\text{V}$          | 8.57   | -- | --    | mA |

|           | HIGH-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$ | Push-Pull 2X, $VOH=2.4\text{V}$ at $VDD=5.0\text{V}$          | 32.99  | -- | --    | mA |

| $I_{OL}$  | LOW-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$   | Push-Pull 2X, $VO_L=0.15\text{V}$ , at $VDD=2.5\text{V}$      | 3.82   | -- | --    | mA |

|           | LOW-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$   | Push-Pull 2X, $VO_L=0.4\text{V}$ , at $VDD=3.3\text{V}$       | 12.25  | -- | --    | mA |

|           | LOW-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$   | Push-Pull 2X, $VO_L=0.4\text{V}$ , at $VDD=5.0\text{V}$       | 17.67  | -- | --    | mA |

|           | LOW-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$  | Push-Pull 2X, $VO_L=0.15\text{V}$ , at $VDD=2.5\text{V}$      | 3.22   | -- | --    | mA |

|           | LOW-Level Output Pulse Current (Note 2) Voltage for $V_{DD}$ Group, $T_J=-40^{\circ}\text{C}$ to $150^{\circ}\text{C}$  | Push-Pull 2X, $VO_L=0.4\text{V}$ , at $VDD=3.3\text{V}$       | 10.34  | -- | --    | mA |

## SLG47105V Training Board HVPAK Design

|                        |                                                                                                           |                                                                                                      |       |      |      |    |

|------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|------|----|

|                        | V <sub>DD</sub> Group, T <sub>J</sub> =-40°C to 150°C                                                     |                                                                                                      |       |      |      |    |

|                        | LOW-Level Output Pulse Current (Note 2) Voltage for V <sub>DD</sub> Group, T <sub>J</sub> =-40°C to 150°C | Push-Pull 2X, V <sub>OL</sub> =0.4V, at V <sub>DD</sub> =5.0V                                        | 14.78 | --   | --   | mA |

| R <sub>PULL_UP</sub>   | Pull Up Resistance T <sub>J</sub> =-40°C to 85°C                                                          | Pull up on PINs 3, 14                                                                                | 8.2   | --   | 13.6 | kΩ |

|                        | Pull Up Resistance T <sub>J</sub> =-40°C to 150°C                                                         | Pull up on PINs 3, 14                                                                                | 8.2   | --   | 13.6 | kΩ |

| R <sub>PULL_DOWN</sub> | Pull Down Resistance T <sub>J</sub> =-40°C to 85°C                                                        | Pull down on PINs 19, 20                                                                             | 8.2   | --   | 13.6 | kΩ |

|                        | Pull Down Resistance T <sub>J</sub> =-40°C to 150°C                                                       | Pull down on PINs 19, 20                                                                             | 8.2   | --   | 13.6 | kΩ |

| V <sub>SET</sub>       | Voltage control threshold                                                                                 |                                                                                                      | --    | --   | --   | mV |

| ΔV <sub>LINE</sub>     | Line Regulation                                                                                           | VDD2=5V to 13.2V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =25°C            |       | ±0.8 |      | %  |

|                        |                                                                                                           | VDD2=9V to 13.2V, V <sub>OUT</sub> =8.064V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =25°C            |       | ±1.2 |      | %  |

|                        |                                                                                                           | VDD2=5V to 13.2V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =-40°C to 85°C   |       | ±0.8 |      | %  |

|                        |                                                                                                           | VDD2=9V to 13.2V, V <sub>OUT</sub> =8.064V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =-40°C to 85°C   |       | ±1.2 |      | %  |

|                        |                                                                                                           | VDD2=5V to 13.2V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =-40°C to 150°C  |       | ±0.8 |      | %  |

|                        |                                                                                                           | VDD2=9V to 13.2V, V <sub>OUT</sub> =8.064V, I <sub>LOAD</sub> =0.5A, T <sub>J</sub> =-40°C to 150°C  |       | ±1.2 |      | %  |

| ΔV <sub>LOAD</sub>     | Load Regulation                                                                                           | VDD2=5V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 500mA, T <sub>J</sub> =25°C           | --    | ±1.8 | --   | %  |

|                        |                                                                                                           | VDD2=9V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 900mA, T <sub>J</sub> =25°C           | --    | ±2.1 | --   | %  |

|                        |                                                                                                           | VDD2=5V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 500mA, T <sub>J</sub> =-40°C to 85°C  | --    | ±1.8 | --   | %  |

|                        |                                                                                                           | VDD2=9V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 900mA, T <sub>J</sub> =-40°C to 85°C  | --    | ±2.1 | --   | %  |

|                        |                                                                                                           | VDD2=5V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 500mA, T <sub>J</sub> =-40°C to 150°C | --    | ±1.8 | --   | %  |

|                        |                                                                                                           | VDD2=9V, V <sub>OUT</sub> =4.096V, I <sub>LOAD</sub> =200mA to 900mA, T <sub>J</sub> =-40°C to 150°C | --    | ±2.1 | --   | %  |

## SLG47105V Training Board HVPAK Design

|                      |                     |                                                       |      |      |      |    |

|----------------------|---------------------|-------------------------------------------------------|------|------|------|----|

| T <sub>SU</sub>      | Startup Time        | From VDD rising past PON <sub>THR</sub>               | --   | 1    | 2    | ms |

| PON <sub>THR</sub>   | Power On Threshold  | V <sub>DD</sub> Level Required to Start Up the Chip   | 1.8  | 1.98 | 2.16 | V  |

| P OFF <sub>THR</sub> | Power Off Threshold | V <sub>DD</sub> Level Required to Switch Off the Chip | 1.33 | 1.55 | 1.83 | V  |

Note: 1 No hysteresis.

Note: 2 DC or average current through any pin should not exceed value given in Absolute Maximum Conditions.

Note: 3 ESD resistor should be taken into consideration when using pull-up/pull-down resistors. It may affect VIH and VIL.

### HV Output Electrical Characteristic (Full Bridge or Half Bridge Modes)

| Parameter             | Description                                                                                                                     | Condition                                                            | Min. | Typ.                                | Max. | Unit     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------------------------------------|------|----------|

| t <sub>R</sub>        | Rise time HV OUT                                                                                                                | VDD2=5V, 16Ω to GND, 10% to 90% VDD2, T <sub>J</sub> =-40°C to 150°C | 81   | 116                                 | 156  | ns       |

| t <sub>F</sub>        | Fall time HV OUT                                                                                                                | VDD2=5V, 16Ω to GND, 90% to 10% VDD2, T <sub>J</sub> =-40°C to 85°C  | 80   | 115                                 | 198  | ns       |

|                       |                                                                                                                                 | VDD2=5V, 16Ω to GND, 90% to 10% VDD2, T <sub>J</sub> =-40°C to 150°C | 80   | 115                                 | 225  | ns       |

| t <sub>DEAD</sub>     | Dead band time of HV_GPOx_HD in Predriver mode (not for Driver mode) (Break before making For Full Bridge and Half Bridge mode) | VDD2=3V, T <sub>J</sub> =-40°C to 150°C                              | --   | 337                                 | --   | ns       |

|                       |                                                                                                                                 | VDD2=5V, T <sub>J</sub> =-40°C to 150°C                              | --   | 75                                  | --   | ns       |

|                       |                                                                                                                                 | VDD2=13.2V, T <sub>J</sub> =-40°C to 150°C                           | --   | 91                                  | --   | ns       |

| PWM_t <sub>DEAD</sub> | Dead band time, generated by PWM block                                                                                          | Configured in PWM block                                              |      | 0;<br>1·Tclk;<br>2·Tclk;<br>3·Tclk; |      | Clk time |

| R <sub>DS(ON)</sub>   | HS FET on resistance (SENSE, GND_HV and GND Pins are connected together)                                                        | VDD2=13.2V, I <sub>O</sub> =500mA, T <sub>J</sub> =25°C              | --   | 170                                 | --   | mΩ       |

|                       |                                                                                                                                 | VDD2=13.2V, I <sub>O</sub> =500mA, T <sub>J</sub> =150°C             | --   | --                                  | 295  | mΩ       |

|                       |                                                                                                                                 | VDD2=9.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =25°C               | --   | 170                                 | --   | mΩ       |

|                       |                                                                                                                                 | VDD2=9.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =150°C              | --   | --                                  | 295  | mΩ       |

|                       |                                                                                                                                 | VDD2=5.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =25°C               | --   | 176                                 | --   | mΩ       |

|                       |                                                                                                                                 | VDD2=5.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =150°C              | --   | --                                  | 304  | mΩ       |

|                       |                                                                                                                                 | VDD2=3.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =25°C               | --   | 255                                 | --   | mΩ       |

|                       |                                                                                                                                 | VDD2=3.0V, I <sub>O</sub> =500mA, T <sub>J</sub> =150°C              | --   | --                                  | 426  | mΩ       |

| R <sub>DS(ON)</sub>   | LS FET on resistance (SENSE_A, SENSE_B)                                                                                         | VDD2=13.2V, I <sub>O</sub> =500mA, T <sub>J</sub> =25°C              | --   | 182                                 | --   | mΩ       |

## SLG47105V Training Board HVPAK Design

|                   |                                                                                                                               |                                                                                                                |      |      |      |    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|----|

|                   | GND_HV and GND Pins are connected together, RDS(ON) with Sense Pin=GND, If Sense Pin VDD=0.5V additional 100mΩ at worst case) | VDD2=13.2V, Io=500mA, T <sub>J</sub> =150°C                                                                    | --   | --   | 332  | mΩ |

|                   |                                                                                                                               | VDD2=9.0V, Io=500mA, T <sub>J</sub> =25°C                                                                      | --   | 182  | --   | mΩ |

|                   |                                                                                                                               | VDD2=9.0V, Io=500mA, T <sub>J</sub> =150°C                                                                     | --   | --   | 332  | mΩ |

|                   |                                                                                                                               | VDD2=5.0V, Io=500mA, T <sub>J</sub> =25°C                                                                      | --   | 185  | --   | mΩ |

|                   |                                                                                                                               | VDD2=5.0V, Io=500mA, T <sub>J</sub> =150°C                                                                     | --   | --   | 338  | mΩ |

|                   |                                                                                                                               | VDD2=3.0V, Io=500mA, T <sub>J</sub> =25°C                                                                      | --   | 232  | --   | mΩ |

|                   |                                                                                                                               | VDD2=3.0V, Io=500mA, T <sub>J</sub> =150°C                                                                     | --   | --   | 414  | mΩ |

| I <sub>OFF</sub>  | Off-state leakage current                                                                                                     | GPO0_HD, GPO1_HD (Note 1), VDD2=5.0V, T <sub>J</sub> =-40°C to 85°C PWM is off, including the charge pump OSC  | 23.2 | --   | 32.9 | μA |

|                   |                                                                                                                               | GPO0_HD, GPO1_HD (Note 1), VDD2=5.0V, T <sub>J</sub> =-40°C to 150°C PWM is off, including the charge pump OSC | 23.2 | --   | 35.2 | μA |

|                   |                                                                                                                               | GPO2_HD, GPO3_HD, VDD2=5.0V, T <sub>J</sub> =-40°C to 85°C PWM is off, including the charge pump OSC           | --   | --   | 0.2  | nA |

|                   |                                                                                                                               | GPO2_HD, GPO3_HD, VDD2=5.0V, T <sub>J</sub> =-40°C to 150°C PWM is off, including the charge pump OSC          | --   | --   | 1.5  | μA |

| I <sub>CC</sub>   | Charge Pump consumption current (from VDD1 Pin or VDD2 Pin)                                                                   | VDD2=5.0V, T <sub>J</sub> =-40°C to 150°C PWM is off, including the charge pump OSC                            | --   | --   | 200  | μA |

| I <sub>CC</sub>   | Charge Pump consumption current (from VDD1 Pin or VDD2 Pin)                                                                   | VDD2=5.0V, T <sub>J</sub> =-40°C to 150°C PWM=250kHz                                                           | 100  | --   | 800  | μA |

| t <sub>WAKE</sub> | Wake-up time                                                                                                                  | HV SLEEP OUT high to output transition, BG is always on, Another pins SLEEP - disable                          | --   | 82.3 | 134  | μs |

Note: 1 There is a resistive voltage divider in front of Diff Amplifier that is connected to GPO0\_HD and GPO1\_HD.

## Protection Circuits

| Parameter        | Description                      | Condition            | Min. | Typ. | Max. | Unit |

|------------------|----------------------------------|----------------------|------|------|------|------|

| I <sub>OCP</sub> | Overcurrent protection threshold | Per any HS or LS FET | --   | 2.18 | --   | A    |

## SLG47105V Training Board HVPAK Design

|                            |                                   |                                                     |     |       |      |    |

|----------------------------|-----------------------------------|-----------------------------------------------------|-----|-------|------|----|

| t <sub>OCP1</sub>          | OCP deglitch time (Note 1)        | VDD=5V, VDD2=5V, T=25°C, Deglitch=Enable, High Side | --  | 2.497 | --   | μs |

|                            |                                   | VDD=5V, VDD2=5V, T=25°C, Deglitch=Enable, Low Side  | --  | 1.232 | --   | μs |

| t <sub>OCP2</sub>          | OCP retry time (Note 2)           | Delay=492μs                                         | --  | 491   | --   | μs |

| V <sub>UVLO</sub> (Note 3) | Recover from undervoltage lockout | At rising edge of VDD2                              | --  | --    | 2.90 | V  |

|                            | Undervoltage lockout              | At falling edge of VDD2                             | --  | --    | 2.77 | V  |

| T <sub>TSD</sub>           | Thermal shutdown temperature      | Junction temperature T <sub>J</sub>                 | 135 | 141   | 159  | °C |

| T <sub>HYST</sub>          | Thermal shutdown hysteresis       |                                                     | --  | 16    | --   | °C |

Note: 1 OCP deglitch time option can be enabled by register [873] and register [875] separately for each Full Bridge. The High Side FETs doesn't have OCP deglitch time if the current through the FET is higher than IOCP level during enable time. This is done to avoid huge currents during retry when the short is persist on the output.

Note: 2 OCP retry time can be selected separately for each HV OUT: HV GPO0 - registers[780:778], HV GPO1 - registers[788:786], HV GPO2 - registers[796:794], HV GPO3 - registers[804:802].

Note: 3 UVLO Function can be enabled separately for VDD2\_A by register [864] and VDD2\_B by register [865].

I<sup>2</sup>C Specifications

| Symbol              | Parameter                                 | Condition/Note                  | Min. | Typ. | Max. | Unit |

|---------------------|-------------------------------------------|---------------------------------|------|------|------|------|

| F <sub>SCL</sub>    | Clock Frequency, SCL                      | V <sub>DD</sub> = (2.3...5.5) V | --   | --   | 400  | kHz  |

| t <sub>LOW</sub>    | Clock Pulse Width Low                     | V <sub>DD</sub> = (2.3...5.5) V | 1300 | --   | --   | ns   |

| t <sub>HIGH</sub>   | Clock Pulse Width High                    | V <sub>DD</sub> = (2.3...5.5) V | 600  | --   | --   | ns   |

| t <sub>I</sub>      | Input Filter Spike Suppression (SCL, SDA) | V <sub>DD</sub> = (2.3...5.5) V | --   | --   | 50   | ns   |

| t <sub>AA</sub>     | Clock Low to Data Out Valid               | V <sub>DD</sub> = (2.3...5.5) V | --   | --   | 900  | ns   |

| t <sub>BUF</sub>    | Bus Free Time between Stop and Start      | V <sub>DD</sub> = (2.3...5.5) V | 1300 | --   | --   | ns   |

| t <sub>HD_STA</sub> | Start Hold Time                           | V <sub>DD</sub> = (2.3...5.5) V | 600  | --   | --   | ns   |

| t <sub>SU_STA</sub> | Start Set-up Time                         | V <sub>DD</sub> = (2.3...5.5) V | 600  | --   | --   | ns   |

| t <sub>HD_DAT</sub> | Data Hold Time                            | V <sub>DD</sub> = (2.3...5.5) V | 0    | --   | --   | ns   |

| t <sub>SU_DAT</sub> | Data Set-up Time                          | V <sub>DD</sub> = (2.3...5.5) V | 100  | --   | --   | ns   |

| t <sub>R</sub>      | Inputs Rise Time                          | V <sub>DD</sub> = (2.3...5.5) V | --   | --   | 300  | ns   |

| t <sub>F</sub>      | Inputs Fall Time                          | V <sub>DD</sub> = (2.3...5.5) V | --   | --   | 300  | ns   |

| t <sub>SU_STO</sub> | Stop Set-up Time                          | V <sub>DD</sub> = (2.3...5.5) V | 600  | --   | --   | ns   |

| t <sub>DH</sub>     | Data Out Hold Time                        | V <sub>DD</sub> = (2.3...5.5) V | 50   | --   | --   | ns   |

Note: 1 Please follow official I<sup>2</sup>C spec UM10204.

Note: 2 When SCL Input is in Low - Level Logic mode max frequency is 400kHz.

## Chip address

| HEX  | BIN     | DEC |

|------|---------|-----|

| 0x08 | 0001000 | 8   |

## I2C Description

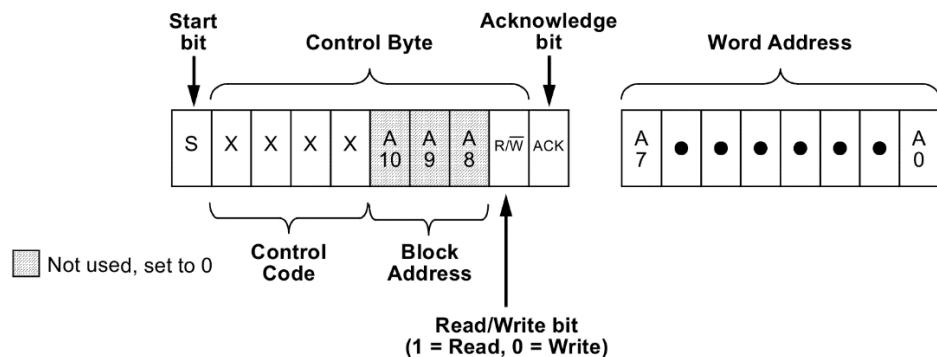

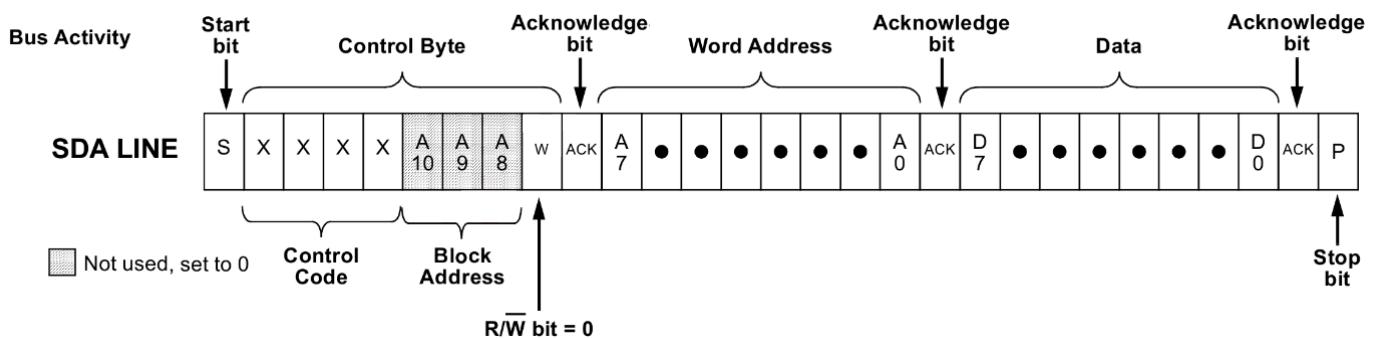

### 1. I2C Basic Command Structure

Each command to the I2C Serial Communications macrocell begins with a Control Byte. The bits inside this Control Byte are shown in Figure 1. After the Start bit, the first four bits are a control code. Each bit in a control code can be sourced independently from the register or by value defined externally by GPIO0, GPIO6, GPIO4, and GPIO1. The LSB of the control code is defined by the value of GPIO0, while the MSB is defined by the value of GPIO1. The address source (either register bit or PIN) for each bit in the control code is defined by registers [2027:2024]. This gives the user flexibility on the chip level addressing of this device and other devices on the same I2C bus. The Block Address is the next three bits (A10, A9, A8), which will define the most significant bits in the addressing of the data to be read or written by the command. The last bit in the Control Byte is the R/W bit, which selects whether a read command or write command is requested, with a "1" selecting for a Read command, and a "0" selecting for a Write command. This Control Byte will be followed by an Acknowledge bit (ACK), which is sent by this device to indicate successful communication of the Control Byte data. In the I2C-bus specification and user manual, there are two groups of eight addresses (0000 xxx and 1111 xxx) that are reserved for the special functions, such as a system General Call address. If the user of this device chooses to set the Control Code to either "1111" or "0000" in a system with other slave device, please consult the I2C-bus specification and user manual to understand the addressing and implementation of these special functions, to ensure reliable operation. In the read and write command address structure, there are a total of 11 bits of addressing, each pointing to a unique byte of information, resulting in a total address space of 2K bytes. Of this 2K byte address space, the valid addresses accessible to the I2C Macrocell on the SLG7RN46465 are in the range from 0 (0x00) to 255 (0xFF). The MSB address bits (A10, A9, and A8) will be "0" for all commands to the SLG7RN46465. With the exception of the Current Address Read command, all commands will have the Control Byte followed by the Word Address.

Figure1. I2C Basic Command Structure

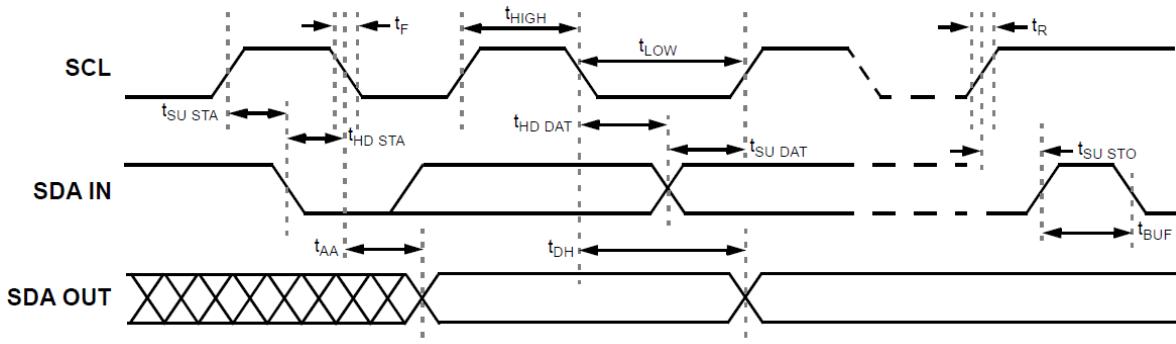

### 2. I2C Serial General Timing

Shown in Figure 2 is the general timing characteristics for the I2C Serial Communications block.

Figure2. I2C Serial General Timing

## SLG47105V Training Board HVPAK Design

## 3. I2C Serial Communications: Read and Write Commands

Following the Start condition from the master, the Control Code [4 bits], the block address [3 bits] and the R/W bit (set to "0"), is placed onto the bus by the Bus Master. After the I2C Serial Communications block has provided an Acknowledge bit (ACK) the next byte transmitted by the master is the Word Address. The Block Address is the next three bits, and is the higher order addressing bits (A10, A9, A8), which when added to the Word Address will together set the internal address pointer in the SLG7RN46465 to the correct data byte to be written. After the SLG7RN46465 sends another Acknowledge bit, the Bus Master will transmit the data byte to be written into the addressed memory location. The SLG7RN46465 again provides an Acknowledge bit and then the Bus Master generates a Stop condition. The internal write cycle for the data will take place at the time that the SLG7RN46465 generates the Acknowledge bit.

Figure3. I2C Write Command

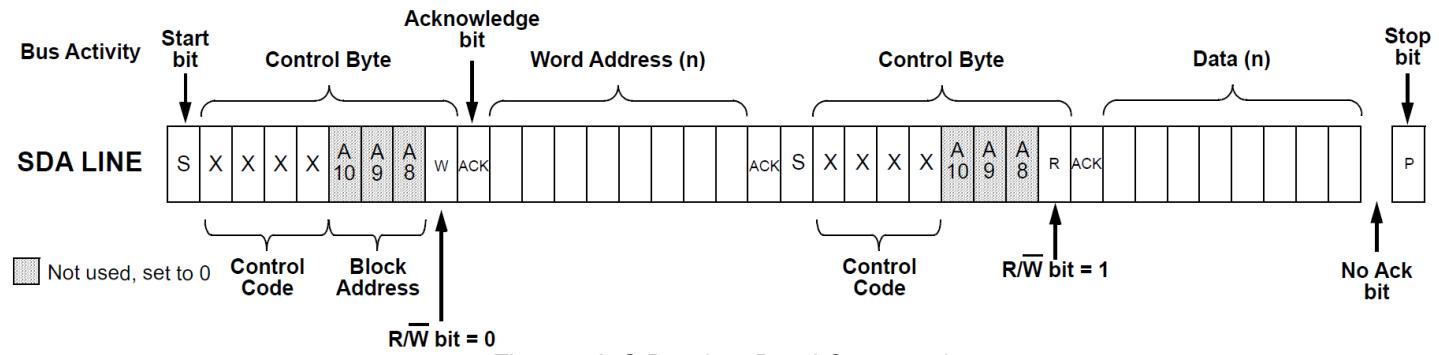

The Random Read command starts with a Control Byte (with R/W bit set to "0", indicating a write command) and Word Address to set the internal byte address, followed by a Start bit, and then the Control Byte for the read (exactly the same as the Byte Write command). The Start bit in the middle of the command will halt the decoding of a Write command, but will set the internal address counter in preparation for the second half of the command. After the Start bit, the Bus Master issues a second control byte with the R/W bit set to "1", after which the SLG7RN46465 issues an Acknowledge bit, followed by the requested eight data bits.

Figure4. I2C Random Read Command

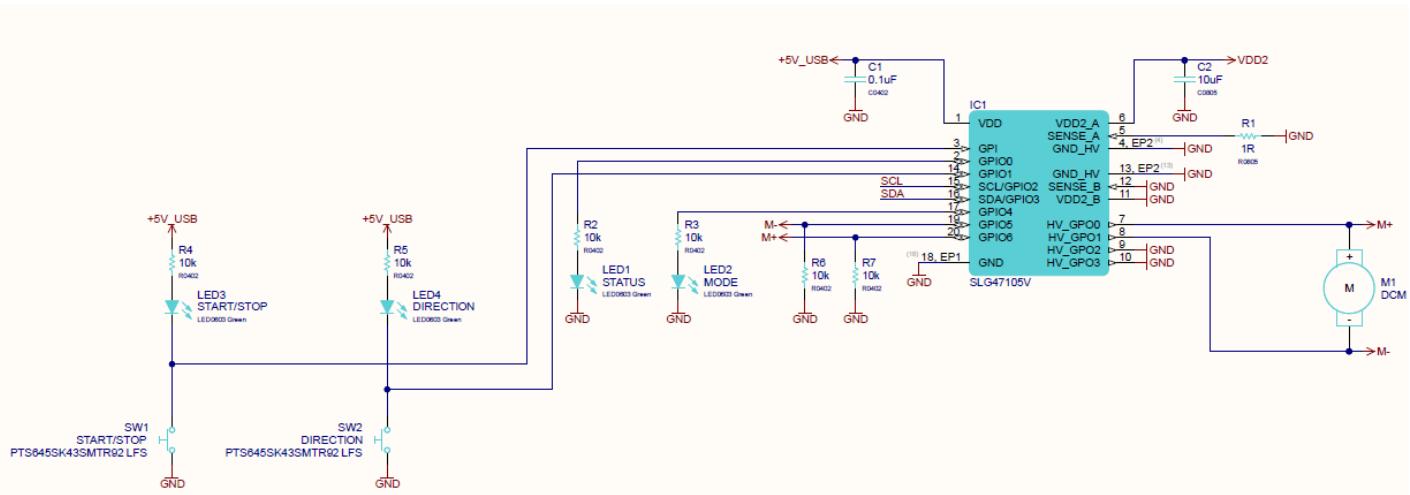

## Typical Application Circuit

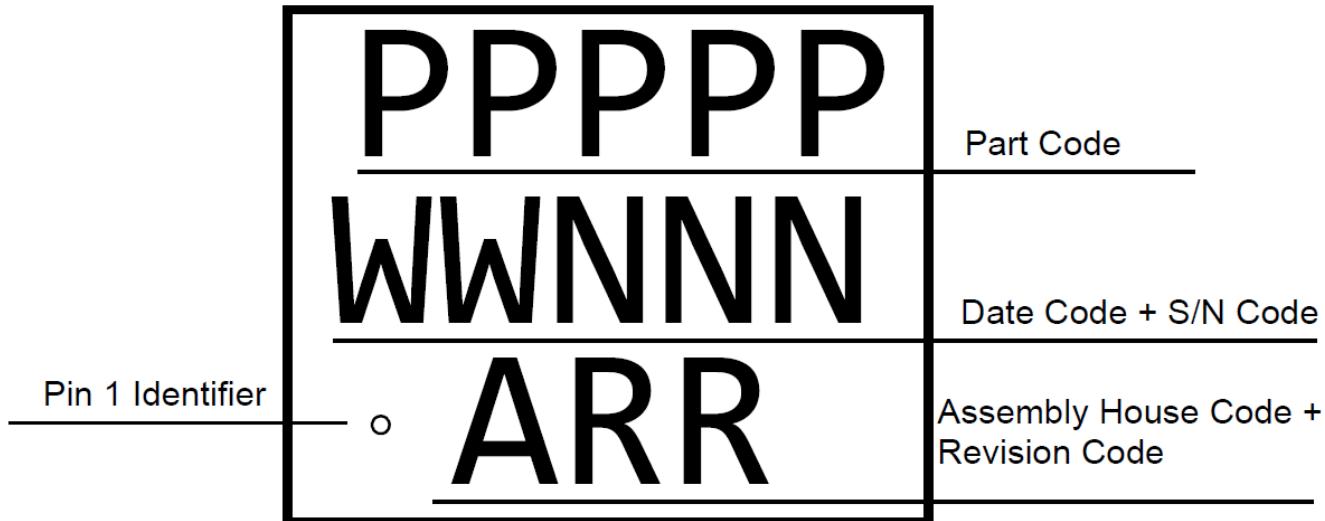

## Package Top Marking

| Datasheet Revision | Programming Code Number | Lock Status | Checksum   | Part Code | Revision | Date       |

|--------------------|-------------------------|-------------|------------|-----------|----------|------------|

| 0.11               | 001                     | U           | 0x6BB479E8 | 46465     | AA       | 04/13/2023 |

Lock coverage for this part is indicated by √, from one of the following options:

|   |                                  |

|---|----------------------------------|

| √ | Unlocked                         |

|   | Partly lock read (mode 1)        |

|   | Partly lock read2 (mode 2)       |

|   | Partly lock read2/write (mode 3) |

|   | All lock read (mode 4)           |

|   | All lock write (mode 5)          |

|   | All lock read/write (mode 6)     |

The IC security bit is locked/set for code security for production unless otherwise specified.

The Programming Code Number is not changed based on the choice of locked vs. unlocked status.

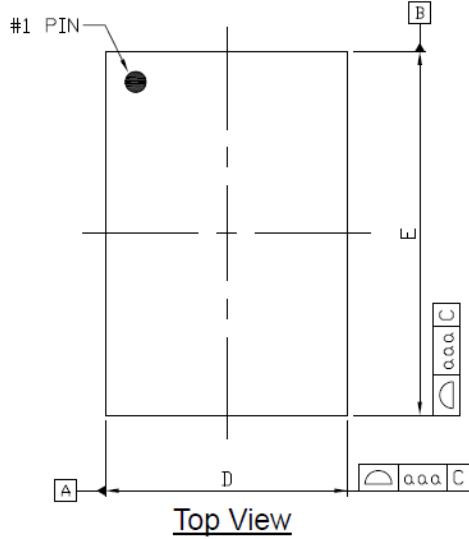

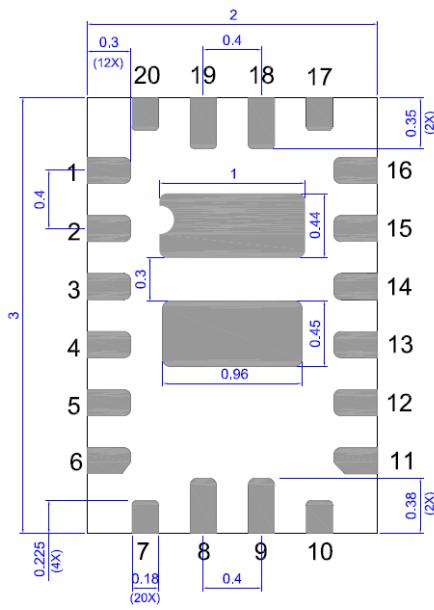

## Package Outlines

## Notes:

1. All dimensions are in millimeters.

2. Dimension "b" applies to metallized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension "b" should not be measured in that radius area.

3. Bilateral coplanarity zone applies to the exposed heat sink slug as well as the terminal.

## Controlling dimension: mm

| Symbol | MILLIMETER |       |       | INCH      |       |       |

|--------|------------|-------|-------|-----------|-------|-------|

|        | MIN.       | NOM.  | MAX.  | MIN.      | NOM.  | MAX.  |

| A      | 0.50       | 0.55  | 0.60  | 0.020     | 0.022 | 0.024 |

| A1     | 0.000      | 0.020 | 0.050 | 0.000     | 0.001 | 0.002 |

| A3     | 0.10       | 0.15  | 0.20  | 0.004     | 0.006 | 0.008 |

| D      | 1.95       | 2.00  | 2.05  | 0.077     | 0.079 | 0.081 |

| E      | 2.95       | 3.00  | 3.05  | 0.116     | 0.118 | 0.120 |

| D1     | 1.15       | 1.20  | 1.25  | 0.045     | 0.047 | 0.049 |

| E1     | 1.95       | 2.00  | 2.05  | 0.077     | 0.079 | 0.081 |

| D2     | 0.95       | 1.00  | 1.05  | 0.037     | 0.039 | 0.041 |

| E2     | 0.39       | 0.44  | 0.49  | 0.015     | 0.017 | 0.019 |

| D3     | 0.91       | 0.96  | 1.01  | 0.036     | 0.038 | 0.040 |

| E3     | 0.40       | 0.45  | 0.50  | 0.016     | 0.018 | 0.020 |

| S1     | 1.10       | 1.15  | 1.20  | 0.043     | 0.045 | 0.047 |

| S2     | 0.61       | 0.66  | 0.71  | 0.024     | 0.026 | 0.028 |

| S3     | 0.45       | 0.50  | 0.55  | 0.018     | 0.020 | 0.022 |

| S4     | 0.47       | 0.52  | 0.57  | 0.018     | 0.020 | 0.022 |

| S5     | 0.208 REF  |       |       | 0.008 REF |       |       |

| S6     | 0.180 REF  |       |       | 0.007 REF |       |       |

| S7     | 0.300 REF  |       |       | 0.012 REF |       |       |

"A1" max lead coplanarity 0.05 mm

Standard tolerance:  $\pm 0.05$

| Symbol | MILLIMETER |       |       | INCH  |       |       |

|--------|------------|-------|-------|-------|-------|-------|

|        | MIN.       | NOM.  | MAX.  | MIN.  | NOM.  | MAX.  |

| e      | 0.40       | BSC   |       | 0.016 | BSC   |       |

| L      | 0.175      | 0.225 | 0.275 | 0.007 | 0.009 | 0.011 |

| L1     | 0.250      | 0.300 | 0.350 | 0.010 | 0.012 | 0.014 |

| L2     | 0.300      | 0.350 | 0.400 | 0.012 | 0.014 | 0.016 |

| L3     | 0.330      | 0.380 | 0.430 | 0.013 | 0.015 | 0.017 |

| b      | 0.130      | 0.180 | 0.230 | 0.005 | 0.007 | 0.009 |

| aaa    | 0.07       |       |       | 0.003 |       |       |

| bbb    | 0.07       |       |       | 0.003 |       |       |

| ccc    | 0.1        |       |       | 0.004 |       |       |

| ddd    | 0.05       |       |       | 0.002 |       |       |

| eee    | 0.08       |       |       | 0.003 |       |       |

## SLG47105V Training Board HVPAK Design

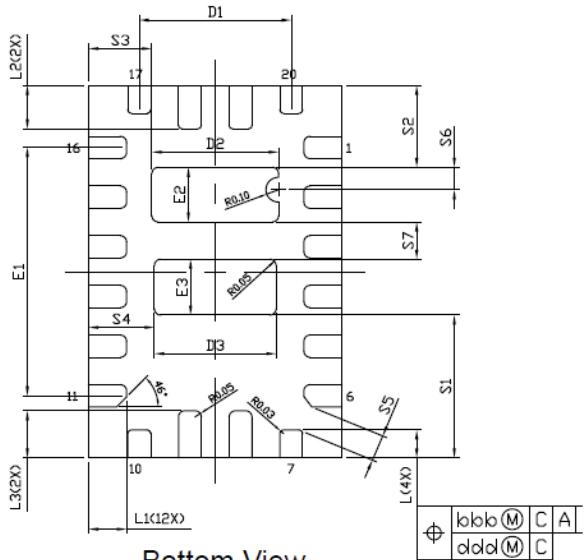

### Tape and Reel Specification

| Package Type                          | # of Pins | Nominal Package Size [mm] | Max Units |         | Reel & Hub Size [mm] | Leader (min) |             | Trailer (min) |             | Tape Width [mm] | Part Pitch [mm] |

|---------------------------------------|-----------|---------------------------|-----------|---------|----------------------|--------------|-------------|---------------|-------------|-----------------|-----------------|

|                                       |           |                           | per Reel  | per Box |                      | Pockets      | Length [mm] | Pockets       | Length [mm] |                 |                 |

| STQFN<br>20L 2mm x 3mm 0.4P FCD Green | 20        | 2.0x3.0x0.55              | 3000      | 3000    | 178 / 60             | 100          | 400         | 100           | 400         | 8               | 4               |

### Carrier Tape Drawing and Dimensions

| Package Type                          | Pocket BTM Length | Pocket BTM Width | Pocket Depth | Index Hole Pitch | Pocket Pitch | Index Hole Diameter | Index Hole to Tape Edge | Index Hole to Pocket Center | Tape Width |

|---------------------------------------|-------------------|------------------|--------------|------------------|--------------|---------------------|-------------------------|-----------------------------|------------|

|                                       | A0                | B0               | K0           | P0               | P1           | D0                  | E                       | F                           | W          |

| STQFN<br>20L 2mm x 3mm 0.4P FCD Green | 2.2               | 3.15             | 0.76         | 4                | 4            | 1.5                 | 1.75                    | 3.5                         | 8          |

### Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020. More information can be found at [www.jedec.org](http://www.jedec.org).

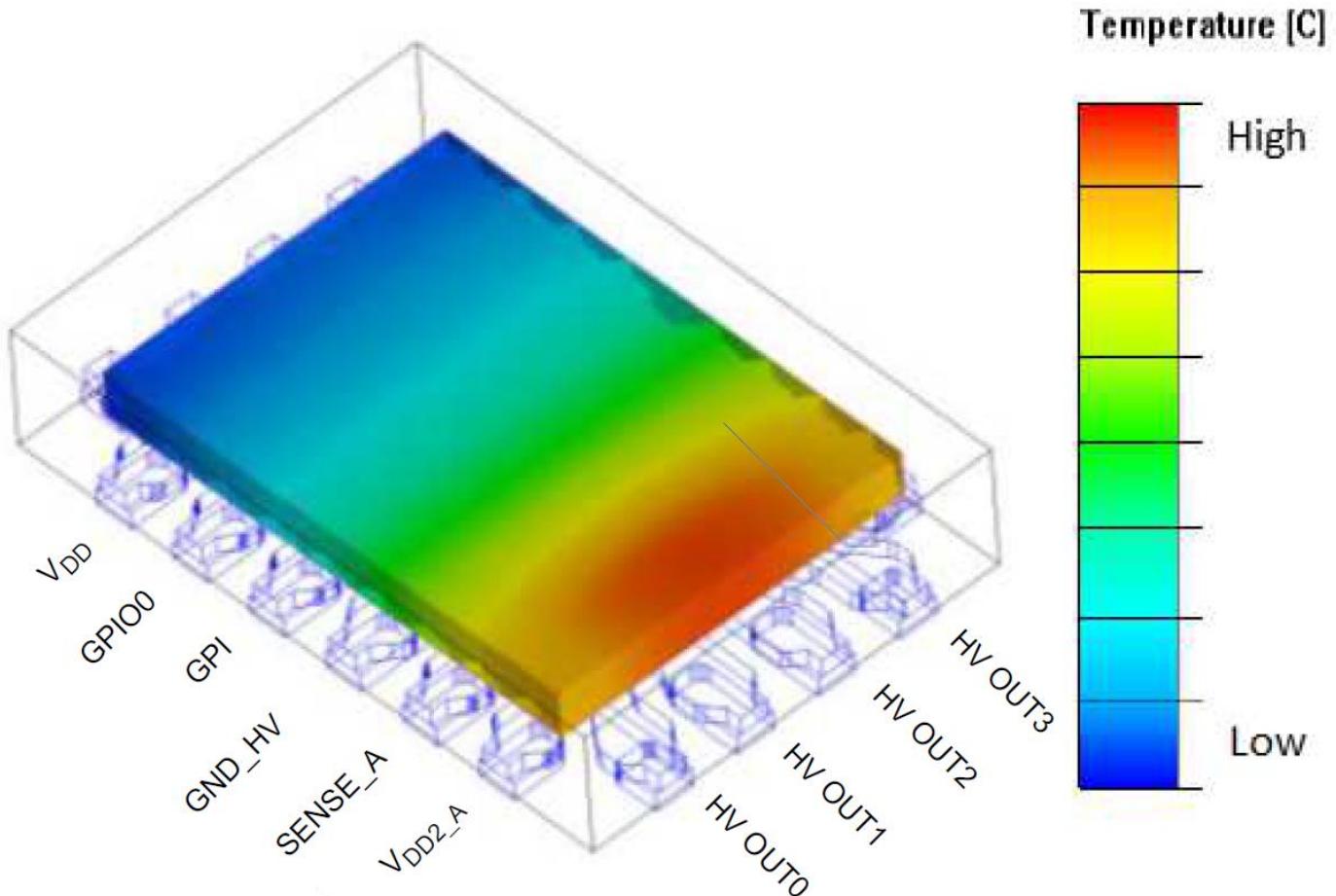

## Thermal Guidelines

Actual thermal characteristics will depend on number and position of vias, PCB type, copper layers, and other factors. Operating temperature range is from -40 °C to 85 °C. To guarantee reliable operation, the junction temperature of the SLG7RN46465 must not exceed 150 °C.

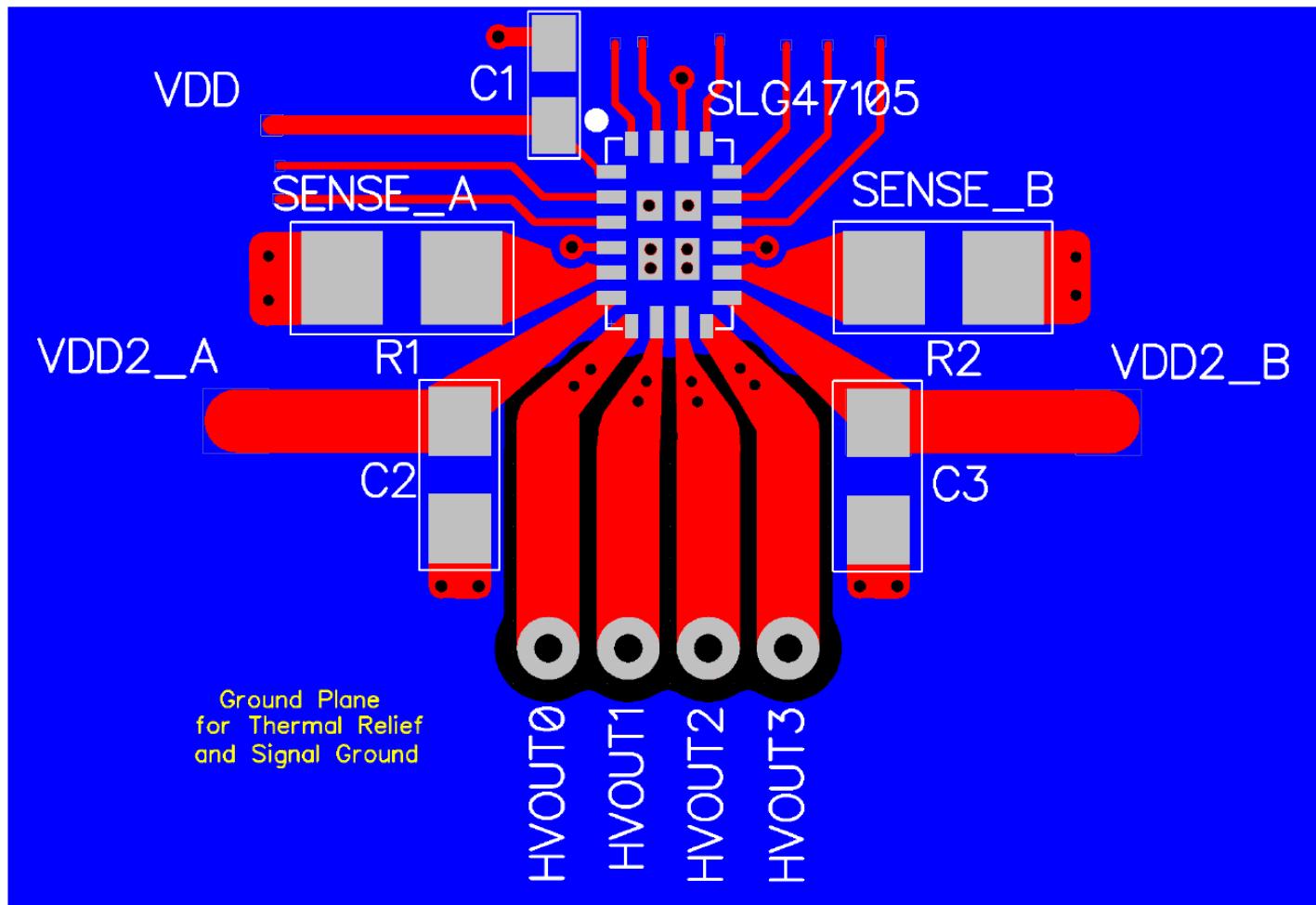

## Layout consideration

PCB should have enough ground plane to dissipate heat. SLG7RN46465 has two additional pads which provide enhanced thermal dissipation. Thermal vias are used to transfer heat from chip to other layers of the PCB.

The sense resistors and power capacitors should be placed as close as possible to the chip for reducing parasitic parameters.

It's highly recommended to place low-ESR capacitor between VDD2\_A, VDD2\_B, and GND pin to keep input voltage stable and reduce ripple. This capacitor should be placed as close to the pins as possible. Also, the capacitor must have the low input impedance at the switching frequency. The recommended value of this capacitor is 1-10  $\mu$ F for most applications. Motors with larger armature inductors require larger input capacitors.

Also, it's highly recommended to place 0.1  $\mu$ F ceramic capacitor between VDD and GND.

## PCB Layout Example

## SLG47105V Training Board HVPAK Design

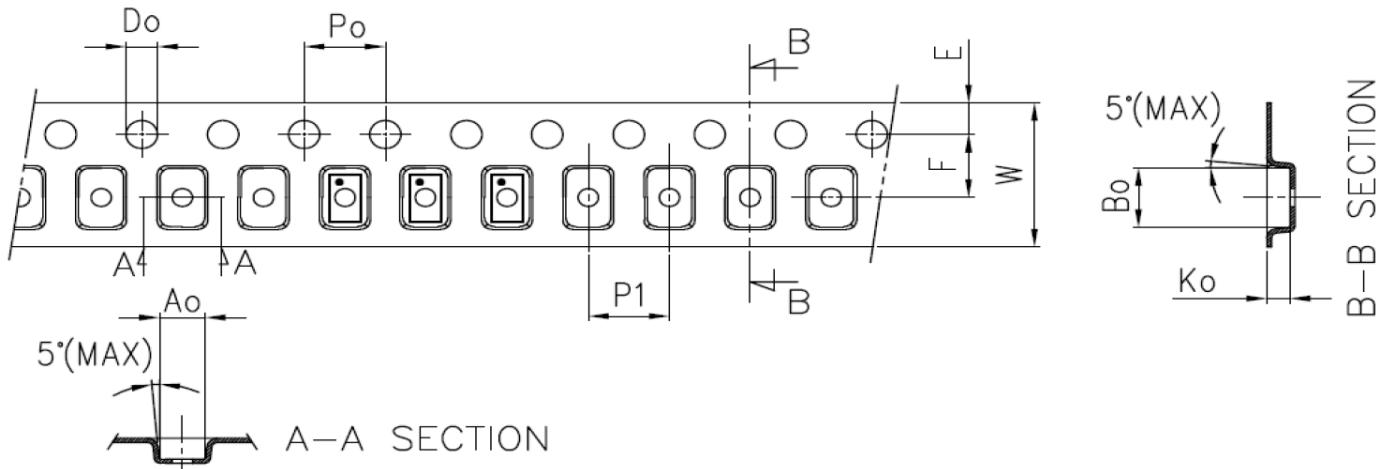

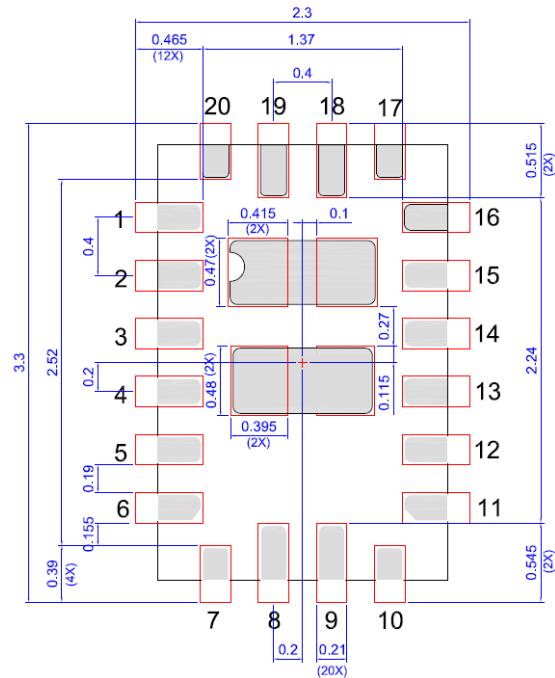

## Recommended Land Pattern

Expose Pad

(Package face down)

Recommended Landing Pattern

(Package face down)

**Datasheet Revision History**

| Date       | Version | Change                        |

|------------|---------|-------------------------------|

| 04/05/2023 | 0.10    | New design for SLG47105V chip |

| 04/13/2023 | 0.11    | Updated Device Revision Table |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).