# **DDR 14-Bit Registered Buffer**

### **Recommended Applications:**

- DDR Memory Modules

- Provides complete DDR DIMM logic solution with ICS93V857 or ICS95V857

- SSTL\_2 compatible data registers

- DDR400 recommended (backward compatible to DDR200/266/333)

#### **Product Features:**

- Exceeds "SSTVN16857" performance

- Differential clock signal

- Meets SSTL\_2 signal data

- Supports SSTL\_2 class I & II specifications

- Low-voltage operation

- $-V_{DD} = 2.3V \text{ to } 2.7V$

- 48 pin TSSOP package

# Truth Table<sup>1</sup>

|        | Q Outputs         |                  |                  |                               |  |

|--------|-------------------|------------------|------------------|-------------------------------|--|

| RESET# | RESET# CLK CLK# D |                  |                  |                               |  |

| L      | X or<br>Floating  | X or<br>Floating | X or<br>Floating | L                             |  |

| Н      | 1                 | $\downarrow$     | Н                | H                             |  |

| Н      | <b>↑</b>          | $\downarrow$     | L                | L                             |  |

| Н      | L or H            | L or H           | Х                | Q <sub>0</sub> <sup>(2)</sup> |  |

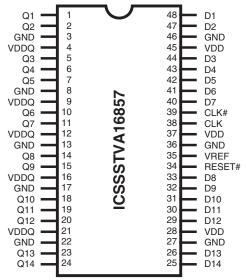

# Pin Configuration

48-Pin TSSOP

6.10 mm. Body, 0.50 mm. pitch = TSSOP

### Notes:

- 1. H = High Signal Level

- L = Low Signal Level

- ↑ = Transition LOW-to-HIGH

- ↓ = Transition HIGH -to LOW

- X = Irrelevant

- Output level before the indicated steady state input conditions were established.

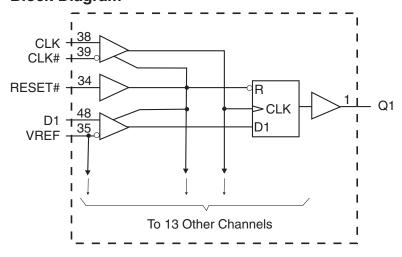

## **Block Diagram**

### **General Description**

The 14-bit ICSSSTVA16857 is a universal bus driver designed for 2.3V to 2.7V  $V_{DD}$  operation and SSTL\_2 I/O levels, except for the LVCMOS RESET# input.

Data flow from D to Q is controlled by the differential clock (CLK/CLK#) and a control signal (RESET#). The positive edge of CLK is used to trigger the data flow and CLK# is used to maintain sufficient noise margins where as RESET#, an LVCMOS asynchronous signal, is intended for use at the time of power-up only. ICSSSTVA16857 supports low-power standby operation. A logic level "Low" at RESET# assures that all internal registers and outputs (Q) are reset to the logic "Low" state, and all input receivers, data (D) and clock (CLK/CLK#) are switched off. Please note that RESET# must always be supported with LVCMOS levels at a valid logic state because VREF may not be stable during power-up.

To ensure that outputs are at a defined logic state before a stable clock has been supplied, RESET# must be held at a logic "Low" level during power up.

In the DDR DIMM application, RESET# is specified to be completely asynchronous with respect to CLK and CLK#. Therefore, no timing relationship can be guaranteed between the two signals. When entering a low-power standby state, the register will be cleared and the outputs will be driven to a logic "Low" level quickly relative to the time to disable the differential input receivers. This ensures there are no glitches on the output. However, when coming out of low-power standby state, the register will become active quickly relative to the time to enable the differential input receivers. When the data inputs are at a logic level "Low" and the clock is stable during the "Low"-to-"High" transition of RESET# until the input receivers are fully enabled, the design ensures that the outputs will remain at a logic "Low" level.

### **Pin Configuration**

| PIN NUMBER                                              | PIN NAME | TYPE   | DESCRIPTION             |

|---------------------------------------------------------|----------|--------|-------------------------|

| 24, 23, 20, 19, 18,<br>15, 14, 11, 10, 7,<br>6, 5, 2, 1 | Q (14:1) | OUTPUT | Data output             |

| 3, 8, 13, 22,<br>27, 36, 46                             | GND      | PWR    | Ground                  |

| 4, 9, 12, 16, 21                                        | VDDQ     | PWR    | Output supply voltage   |

| 25, 26, 29, 30, 31, 32, 33, 40, 41, 42, 43, 44, 47, 48  | D (14:1) | INPUT  | Data input              |

| 38                                                      | CLK      | INPUT  | Positive clock input    |

| 39                                                      | CLK#     | INPUT  | Negative clock input    |

| 28, 37, 45                                              | VDD      | PWR    | Core supply voltage     |

| 34                                                      | RESET#   | INPUT  | Reset (active low)      |

| 35                                                      | VREF     | INPUT  | Input reference voltage |

# **Absolute Maximum Ratings**

| Storage Temperature                                     | -65°C to +150°C             |

|---------------------------------------------------------|-----------------------------|

| Supply Voltage                                          |                             |

| Input Voltage <sup>1</sup>                              | 0.5 to V <sub>DD</sub> +0.5 |

| Output Voltage <sup>1,2</sup>                           | $0.5$ to $V_{DDQ} + 0.5$    |

| Input Clamp Current ±                                   | ±50 mA                      |

| Output Clamp Current                                    | ±50 mA                      |

| Continuous Output Current ±                             | ±50 mA                      |

| V <sub>DD</sub> , V <sub>DDQ</sub> or GND Current/Pin ± | ±100 mA                     |

| Package Thermal Impedance <sup>3</sup> 5                | 55°C/W                      |

#### Notes:

- The input and output negative voltage ratings may be excluded if the input and output clamp ratings are observed.

- This current will flow only when the output is in the high state level V<sub>0</sub> > V<sub>DDQ</sub>.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

Recommended Operating Conditions - DDRI/DDR333 (PC1600, PC2100, PC2700)

| PARAMETER            | DESCRIPTION                                       |             | MIN                         | TYP       | MAX                     | UNITS |

|----------------------|---------------------------------------------------|-------------|-----------------------------|-----------|-------------------------|-------|

| $V_{DD}$             | Supply Voltage                                    | 2.3         | 2.5                         | 2.7       |                         |       |

| $V_{DDQ}$            | I/O Supply Voltage                                |             | 2.3                         | 2.5       | 2.7                     |       |

| $V_{REF}$            | Reference Voltage                                 |             | 1.15                        | 1.25      | 1.35                    |       |

| $V_{TT}$             | Termination Voltage                               |             | V <sub>REF</sub> - 0.04     | $V_{REF}$ | V <sub>REF</sub> + 0.04 |       |

| $V_{I}$              | Input Voltage                                     |             | 0                           |           | $V_{DDQ}$               |       |

| V <sub>IH (DC)</sub> | DC Input High Voltage                             |             | V <sub>REF</sub> + 0.15     |           |                         |       |

| V <sub>IH (AC)</sub> | AC Input High Voltage                             | Data Inputs | V <sub>REF</sub> + 0.31     |           |                         |       |

| V <sub>IL (DC)</sub> | DC Input Low Voltage                              | Data Inputs |                             |           | V <sub>REF</sub> - 0.15 | V     |

| V <sub>IL (DC)</sub> | AC Input Low Voltage                              |             |                             |           | V <sub>REF</sub> - 0.31 |       |

| $V_{IH}$             | Input High Voltage Level                          | RESET#      | 1.7                         |           |                         |       |

| $V_{IL}$             | Input Low Voltage Level                           | nesei#      |                             |           | 0.7                     |       |

| $V_{ICR}$            | Common mode Input Range                           | CLK, CLK#   | 0.97                        |           | 1.53                    |       |

| $V_{ID}$             | Differential Input Voltage                        | CLN, CLN#   | 0.36                        |           |                         |       |

| V <sub>IX</sub>      | Cross Point Voltage of Differential Clock<br>Pair |             | (V <sub>DDQ</sub> /2) - 0.2 |           | $(V_{DDQ}/2) + 0.2$     |       |

| I <sub>OH</sub>      | High-Level Output Current                         |             |                             |           | -16                     | m A   |

| I <sub>OL</sub>      | Low-Level Output Current                          |             |                             | 16        | mA                      |       |

| T <sub>A</sub>       | Operating Free-Air Temperatu                      | re          | 0                           |           | 70                      | °C    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

Recommended Operating Conditions - DDRI-400 (PC3200)

|                      |                                                    |             |                             | <del>/</del> |                         |    |

|----------------------|----------------------------------------------------|-------------|-----------------------------|--------------|-------------------------|----|

| PARAMETER            | DESCRIPTION                                        | MIN         | TYP                         | MAX          | UNITS                   |    |

| $V_{DD}$             | Supply Voltage                                     | 2.5         | 2.6                         | 2.7          |                         |    |

| $V_{DDQ}$            | I/O Supply Voltage                                 |             | 2.5                         | 2.6          | 2.7                     |    |

| $V_{REF}$            | Reference Voltage                                  |             | 1.25                        | 1.3          | 1.35                    |    |

| V <sub>TT</sub>      | Termination Voltage                                |             | V <sub>REF</sub> - 0.04     | $V_{REF}$    | V <sub>REF</sub> + 0.04 | ]  |

| Vı                   | Input Voltage                                      |             | 0                           |              | $V_{DDQ}$               |    |

| V <sub>IH (DC)</sub> | DC Input High Voltage                              |             | V <sub>REF</sub> + 0.15     |              |                         |    |

| V <sub>IH (AC)</sub> | AC Input High Voltage                              | Data Inputs | V <sub>REF</sub> + 0.31     |              |                         |    |

| V <sub>IL (DC)</sub> | DC Input Low Voltage                               | Data Inputs |                             |              | V <sub>REF</sub> - 0.15 | V  |

| V <sub>IL (DC)</sub> | AC Input Low Voltage                               |             |                             |              | V <sub>REF</sub> - 0.31 |    |

| $V_{IH}$             | Input High Voltage Level                           | RESET#      | 1.7                         |              |                         |    |

| $V_{IL}$             | Input Low Voltage Level                            | INESET#     |                             |              | 0.7                     |    |

| V <sub>ICR</sub>     | Common mode Input Range                            | CLK, CLK#   | 0.97                        |              | 1.53                    |    |

| $V_{ID}$             | Differential Input Voltage                         | CLN, CLN#   | 0.36                        |              |                         |    |

| V <sub>IX</sub>      | Cross Point Voltage of Differential Clock<br>Pair  |             | (V <sub>DDQ</sub> /2) - 0.2 |              | $(V_{DDQ}/2) + 0.2$     |    |

| I <sub>OH</sub>      | High-Level Output Current Low-Level Output Current |             |                             |              | -16                     | A  |

| I <sub>OL</sub>      |                                                    |             |                             |              | 16                      | mA |

| T <sub>A</sub>       | Operating Free-Air Temperatu                       | re          | 0                           |              | 70                      | °C |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# DC Electrical Characteristics - DDRI/DDR333 (PC1600, PC2100, PC2700) $T_A = 0 - 70^{\circ}\text{C}$ ; $V_{DD} = 2.5 + /-0.2\text{V}$ , $V_{DDQ} = 2.5 + /-0.2\text{V}$ ; (unless otherwise stated)

| SYMBOL            | PARAMETERS                                                | CONDITIONS                                                                                                                                                                            |                      | $V_{DDQ}$ | MIN                    | TYP  | MAX        | UNITS                 |

|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|------------------------|------|------------|-----------------------|

| V <sub>IK</sub>   |                                                           | I <sub>I</sub> = -18mA                                                                                                                                                                |                      | 2.3V      |                        |      | -1.2       |                       |

| $V_{OH}$          |                                                           | I <sub>OH</sub> = -100μA                                                                                                                                                              |                      | 2.3V-2.7V | V <sub>DDQ</sub> - 0.2 |      |            | V                     |

|                   |                                                           | $I_{OH} = -8mA$                                                                                                                                                                       |                      | 2.3V      | 1.95                   |      |            | V                     |

| V                 |                                                           | $I_{OL} = 100\mu A$                                                                                                                                                                   |                      | 2.3V-2.7V |                        |      | 0.2        |                       |

| V <sub>OL</sub>   |                                                           | $I_{OL} = 8mA$                                                                                                                                                                        |                      | 2.3V      |                        |      | 0.35       |                       |

| $I_{l}$           | All Inputs                                                | $V_I = V_{DD}$ or GND                                                                                                                                                                 |                      | 2.7V      |                        |      | ±5         | μΑ                    |

|                   | Standby (Static)                                          | RESET# = GND                                                                                                                                                                          |                      |           |                        |      | 0.01       | μΑ                    |

| I <sub>DD</sub>   | Operating (Static)                                        | $V_{I} = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>RESET# = $V_{DD}$                                                                                                                           |                      |           |                        | 25   |            | mA                    |

|                   | Dynamic operating (clock only)                            | RESET# = $V_{DD}$ ,<br>$V_1 = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>CLK and CLK# switching<br>50% duty cycle.                                                                              | . I <sub>O</sub> = 0 | 2.7V      |                        | 30   |            | μ/clock<br>MHz        |

| I <sub>DDD</sub>  | Dynamic Operating (per each data input)                   | RESET# = $V_{DD}$ ,<br>$V_{I} = V_{IH(AC)}$ or $V_{IL (AC)}$ ,<br>CLK and CLK# switching<br>50% duty cycle. One data<br>input switching at half<br>clock frequency, 50%<br>duty cycle | 10 = 0               | 2.7 V     |                        | 10   |            | μΑ/ clock<br>MHz/data |

| r <sub>OH</sub>   | Output High                                               |                                                                                                                                                                                       |                      | 2.3V-2.7V | 7                      | 13.5 | 20         | Ω                     |

| r <sub>OL</sub>   | Output Low                                                | I <sub>OL</sub> = 16mA                                                                                                                                                                |                      | 2.3V-2.7V | 7                      | 13   | 20         | Ω                     |

| r <sub>O(D)</sub> | [r <sub>OH</sub> - r <sub>OL</sub> ] each<br>separate bit | I <sub>O</sub> = 20mA, T <sub>A</sub> = 25° C                                                                                                                                         |                      | 2.5V      |                        |      | 4          | Ω                     |

| C <sub>i</sub>    | Data Inputs CLK and CLK#                                  | $V_{I} = V_{REF} \pm 350 \text{mV}$<br>$V_{ICR} = 1.25 \text{V}, V_{I(PP)} = 360 \text{mV}$                                                                                           |                      | 2.5V      | 2.5<br>2.5             |      | 3.5<br>3.5 | pF                    |

### Notes:

1 - Guaranteed by design, not 100% tested in production.

# DC Electrical Characteristics - DDRI-400 (PC3200)

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 2.5 + -0.2V$ ,  $V_{DDQ} = 2.5 + -0.2V$ ; (unless otherwise stated)

| SYMBOL            | PARAMETERS                                                | CONDITIONS                                                                                                                                                                            |        | $V_{DDQ}$ | MIN                    | TYP  | MAX        | UNITS                 |

|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------------------|------|------------|-----------------------|

| V <sub>IK</sub>   |                                                           | I <sub>I</sub> = -18mA                                                                                                                                                                |        | 2.5V      |                        |      | -1.2       |                       |

| V <sub>OH</sub>   |                                                           | I <sub>OH</sub> = -100μA                                                                                                                                                              |        | 2.5V-2.7V | V <sub>DDQ</sub> - 0.2 |      |            | V                     |

|                   |                                                           | $I_{OH} = -8mA$                                                                                                                                                                       |        | 2.7V      | 1.95                   |      |            | V                     |

| V                 |                                                           | $I_{OL} = 100 \mu A$                                                                                                                                                                  |        | 2.5V-2.7V |                        |      | 0.2        |                       |

| V <sub>OL</sub>   |                                                           | $I_{OL} = 8mA$                                                                                                                                                                        |        | 2.5V      |                        |      | 0.35       |                       |

| $I_1$             | All Inputs                                                | $V_I = V_{DD}$ or GND                                                                                                                                                                 |        | 2.7V      |                        |      | ±5         | μΑ                    |

|                   | Standby (Static)                                          | RESET# = GND                                                                                                                                                                          |        |           |                        |      | 0.01       | μΑ                    |

| I <sub>DD</sub>   | Operating (Static)                                        | $V_{I} = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>RESET# = $V_{DD}$                                                                                                                           |        |           |                        | 25   |            | mA                    |

|                   | Dynamic operating (clock only)                            | $\begin{tabular}{ll} RESET\# = V_{DD}, \\ V_I = V_{IH(AC)} \mbox{ or } V_{IL(AC)}, \\ CLK \mbox{ and } CLK\# \mbox{ switching} \\ 50\% \mbox{ duty cycle.} \\ \end{tabular}$          |        | 2.7V      |                        | 30   |            | μ/clock<br>MHz        |

| I <sub>DDD</sub>  | Dynamic Operating (per each data input)                   | RESET# = $V_{DD}$ ,<br>$V_{I} = V_{IH(AC)}$ or $V_{IL (AC)}$ ,<br>CLK and CLK# switching<br>50% duty cycle. One data<br>input switching at half<br>clock frequency, 50%<br>duty cycle | 10 = 0 | 2.7 V     |                        | 10   |            | μΑ/ clock<br>MHz/data |

| $r_{OH}$          | Output High                                               | I <sub>OH</sub> = -16mA                                                                                                                                                               |        | 2.5V-2.7V | 7                      | 13.5 | 20         | Ω                     |

| r <sub>OL</sub>   | Output Low                                                | I <sub>OL</sub> = 16mA                                                                                                                                                                |        | 2.5V-2.7V | 7                      | 13   | 20         | Ω                     |

| r <sub>O(D)</sub> | [r <sub>OH</sub> - r <sub>OL</sub> ] each<br>separate bit | I <sub>O</sub> = 20mA, T <sub>A</sub> = 25° C                                                                                                                                         |        | 2.6V      |                        |      | 4          | Ω                     |

| C <sub>i</sub>    | Data Inputs CLK and CLK#                                  | $V_{I} = V_{REF} \pm 350 \text{mV}$<br>$V_{ICR} = 1.25 \text{V}, V_{I(PP)} = 360 \text{n}$                                                                                            |        |           | 2.5<br>2.5             |      | 3.5<br>3.5 | pF                    |

### Notes:

<sup>1 -</sup> Guaranteed by design, not 100% tested in production.

# Timing Requirements<sup>1</sup>

(over recommended operating free-air temperature range, unless otherwise noted)

| SYMBOL             | PARAMETERS                                      |                          | $V_{DDQ} = 2.5$ | 5V ± 0.2V | UNITS  |

|--------------------|-------------------------------------------------|--------------------------|-----------------|-----------|--------|

| STIVIDOL           | FAHAMETERS                                      |                          | MIN             | MAX       | OIVITO |

| f <sub>clock</sub> | Clock frequency                                 |                          |                 | 270       | MHz    |

| t <sub>SL</sub>    | Output slew rate                                |                          | 1               | 4         | V/ns   |

| +.                 | Setup time, fast slew rate <sup>2 &amp; 4</sup> | Data before CLK↑, CLK#↓  | 0.4             |           | ns     |

| t <sub>S</sub>     | Setup time, slow slew rate 3 & 4                | Data before CERT, CER#\$ | 0.6             |           | ns     |

|                    | Hold time foot alow rate 2 & 4                  | Data after CLK↑, CLK#↓   | 0.4             |           | ns     |

| T <sub>h</sub>     | Hold time, slow slew rate 3 & 4                 | Data affer GLN , GLN#4   | 0.5             |           | ns     |

Notes:

- 1 Guaranteed by design, not 100% tested in production.

- 2 For data signal input slew rate of  $\geq 1V/ns$ .

- 3 For data signal input slew rate of  $\geq$  0.5V/ns and < 1V/ns.

- 4 CLK, CLK# signals input slew rate of  $\geq$  1V/ns.

### Switching Characteristics - DDRI/DDR333 (PC1600, PC2100, PC2700)

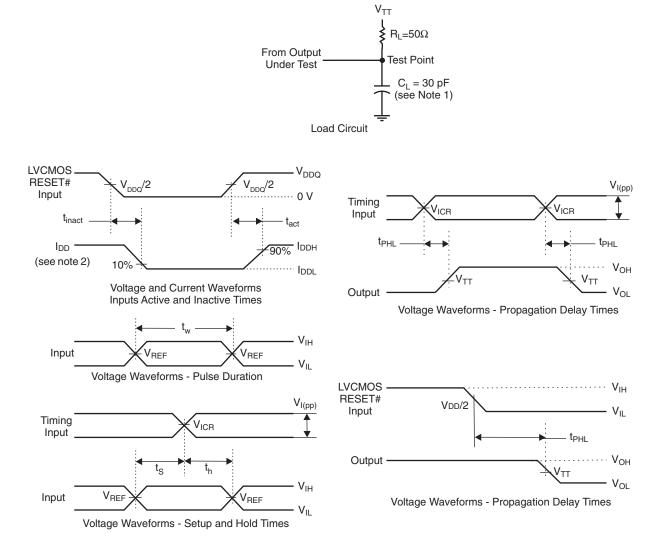

(over recommended operating free-air temperature range, unless otherwise noted) (see Figure 1)

| SYMBOL           | From              | То       | V <sub>DD</sub> : | = 2.5V ±0. | 2V  | UNITS |

|------------------|-------------------|----------|-------------------|------------|-----|-------|

| STWIDOL          | (Input)           | (Output) | MIN               | TYP        | MAX | UNITS |

| f <sub>max</sub> |                   |          | 210               |            |     | MHz   |

| t <sub>PD</sub>  | CLK, CLK# (TSSOP) | Q        | 1.6               | 2.1        | 2.6 | ns    |

| t <sub>phl</sub> | RESET#            | Q        |                   |            | 3.5 | ns    |

### **Switching Characteristics - DDRI-400 (PC3200)**

(over recommended operating free-air temperature range, unless otherwise noted) (see Figure 1)

| SYMBOL           | From              | То       | V <sub>DD</sub> = | = 2.6V ±0. | 1V   | UNITS |

|------------------|-------------------|----------|-------------------|------------|------|-------|

| STIVIDOL         | (Input)           | (Output) | MIN               | TYP        | MAX  | UNITS |

| f <sub>max</sub> |                   |          | 210               |            |      | MHz   |

| t <sub>PD</sub>  | CLK, CLK# (TSSOP) | Q        | 1.1               | 1.6        | 1.89 | ns    |

| t <sub>phl</sub> | RESET#            | Q        |                   |            | 3.5  | ns    |

Figure 1 - Parameter Measurement Information ( $V_{DDQ} = 2.5V \pm 0.2V$ )

Notes

- 1. CL incluces probe and jig capacitance.

- 2.  $I_{DD}$  tested with clock and data inputs held at  $V_{DDQ}$  or GND, and  $I_{O} = 0$  mA.

- 3. All input pulses are supplied by generators having the following characteristics: PRR @ 10 MHz, Zo=50 $\Omega$ , input slew rate = 1 V/ns ±20% (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- 5.  $V_{TT} = V_{REF} = V_{DDQ}/2$

- 6. VIH = VREF + 310mV (AC voltage levels) for differential inputs. VIH = VDDQ for LVCMOS input.

- 7.  $V_{IL} = V_{REF}$  310mV (AC voltage levels) for differential inputs.  $V_{IL} = GND$  for LVCMOS input.

- 8. tplH and tpHL are the same as tpd

0932A--05/12/04

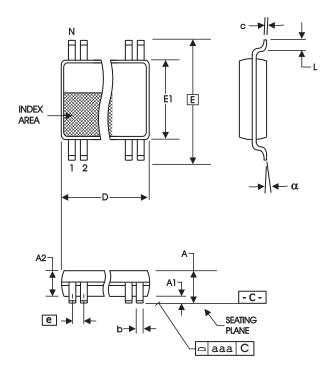

6.10 mm. Body, 0.50 mm. pitch TSSOP (240 mil) (0.020 mil)

|         | In Millimeters |         | In Inches |          |  |

|---------|----------------|---------|-----------|----------|--|

| SYMBOL  | COMMON DI      |         |           |          |  |

| OTTOBOL |                |         |           |          |  |

|         | MIN            | MAX     | MIN       | MAX      |  |

| Α       |                | 1.20    |           | .047     |  |

| A1      | 0.05           | 0.15    | .002      | .006     |  |

| A2      | 0.80           | 1.05    | .032      | .041     |  |

| b       | 0.17           | 0.27    | .007      | .011     |  |

| С       | 0.09           | 0.20    | .0035     | .008     |  |

| D       | SEE VAR        | IATIONS | SEE VAR   | RIATIONS |  |

| Е       | 8.10 B         | ASIC    | 0.319 E   | BASIC    |  |

| E1      | 6.00           | 6.20    | .236 .244 |          |  |

| е       | 0.50 B         | ASIC    | 0.020 E   | BASIC    |  |

| L       | 0.45           | 0.75    | .018      | .030     |  |

| N       | SEE VARIATIONS |         | SEE VAR   | RIATIONS |  |

| α       | 0°             | 8°      | 0°        | 8°       |  |

| aaa     |                | 0.10    |           | .004     |  |

### **VARIATIONS**

| N  | D m     | m.    | D (inch) |      |  |

|----|---------|-------|----------|------|--|

| IN | MIN MAX |       | MIN      | MAX  |  |

| 48 | 12.40   | 12.60 | .488     | .496 |  |

Reference Doc.: JEDEC Publication 95, M O-153

10-0039

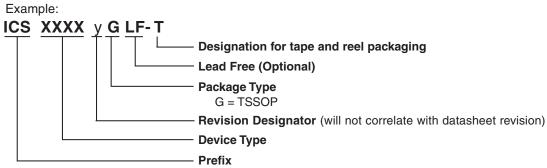

# **Ordering Information**

ICSSSTVA16857yGLF-T

ICS = Standard Device

0932A--05/12/04

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.