お客様各位

---

## カタログ等資料中の旧社名の扱いについて

---

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願ひ申し上げます。

ルネサスエレクトロニクス ホームページ (<http://www.renesas.com>)

2010年4月1日

ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (<http://www.renesas.com>)

【問い合わせ先】<http://japan.renesas.com/inquiry>

## ご注意書き

1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

3. 当社製品を改造、改変、複製等しないでください。

4. 本資料に記載された回路、ソフトウェアおよびこれらに関する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準： コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パソコン機器、産業用ロボット

高品質水準： 輸送機器（自動車、電車、船舶等）、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器（厚生労働省定義の管理医療機器に相当）

特定水準： 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器（生命維持装置、人体に埋め込み使用するもの、治療行為（患部切り出し等）を行うもの、その他直接人命に影響を与えるもの）（厚生労働省定義の高度管理医療機器に相当）またはシステム等

8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエーペンギング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# データ・シート

**RENESAS**

MOS集積回路

MOS Integrated Circuit

μ PD78011F,78012F,78013F,78014F,78015F,78016F,78018F

## 8ビット・シングルチップ・マイクロコンピュータ

**保守／廃止**

- ★ μ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018Fは、78K/0シリーズの中のμ PD78018Fサブシリーズの製品です。

従来のμ PD78014サブシリーズに比べてより低電圧で動作し、ROM, RAM容量のバリエーションを充実させました。

また、マスクROM製品と同じ電源電圧範囲で動作可能なワン・タイムPROMまたはEPROM製品μ PD78P018Fや各種開発ツールも用意しております。

詳しい機能説明などは次のユーザーズ・マニュアルに記載しております。設計の際には必ずお読みください。

μ PD78018F, 78018FYサブシリーズ ユーザーズ・マニュアル : U10659J

78K/0シリーズ ユーザーズ・マニュアル 命令編 : U12326J

### 特 徴

大容量ROM, RAM内蔵

| 品名        | 項目<br>プログラム・<br>メモリ(ROM) | データ・メモリ |         |         | パッケージ                           |

|-----------|--------------------------|---------|---------|---------|---------------------------------|

|           |                          | 内部高速RAM | 内部拡張RAM | バッファRAM |                                 |

| μPD78011F | 8 Kバイト                   | 512バイト  | -       | 32バイト   | ・64ピン・プラスチック・シュリンクDIP (750 mil) |

| μPD78012F | 16 Kバイト                  |         |         |         | ・64ピン・プラスチックQFP ( 14 mm )       |

| μPD78013F | 24 Kバイト                  | 1024バイト |         |         | ・64ピン・プラスチックLQFP ( 12 mm )      |

| μPD78014F | 32 Kバイト                  |         |         |         |                                 |

| μPD78015F | 40 Kバイト                  |         |         |         |                                 |

| μPD78016F | 48 Kバイト                  |         |         |         |                                 |

| μPD78018F | 60 Kバイト                  |         | 1024バイト |         |                                 |

外部メモリ拡張空間 : 64 Kバイト

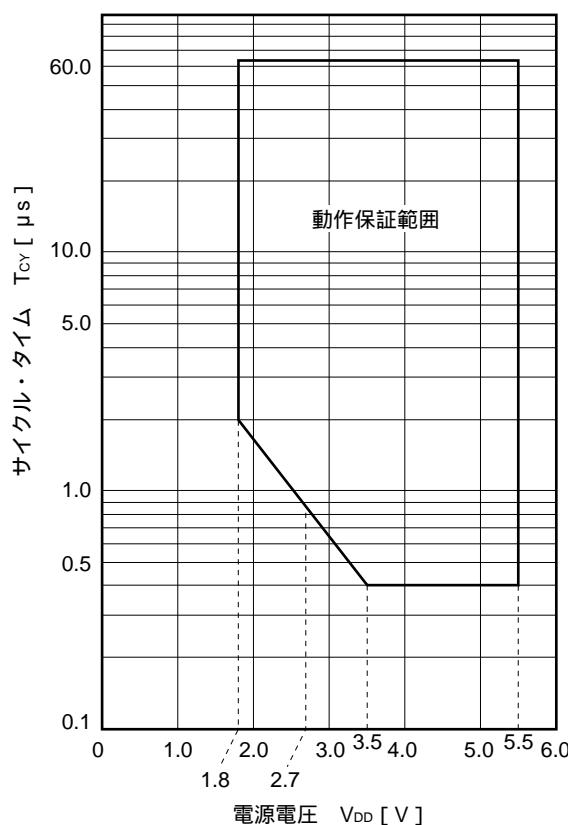

高速 (0.4 μs) から超低速 (122 μs) まで最小命令実行時間変更可能

I/Oポート : 53本 (N-chオープン・ドレーン : 4本を含む)

8ビット分解能A/Dコンバータ : 8チャネル

シリアル・インターフェース : 2チャネル

タイマ : 5チャネル

電源電圧 : V<sub>DD</sub>=1.8 ~ 5.5 V

### 応用分野

携帯電話, ページャ, VTR, オーディオ, カメラ, 家電製品など

本資料の内容は, 後日変更する場合があります。

## オーダ情報

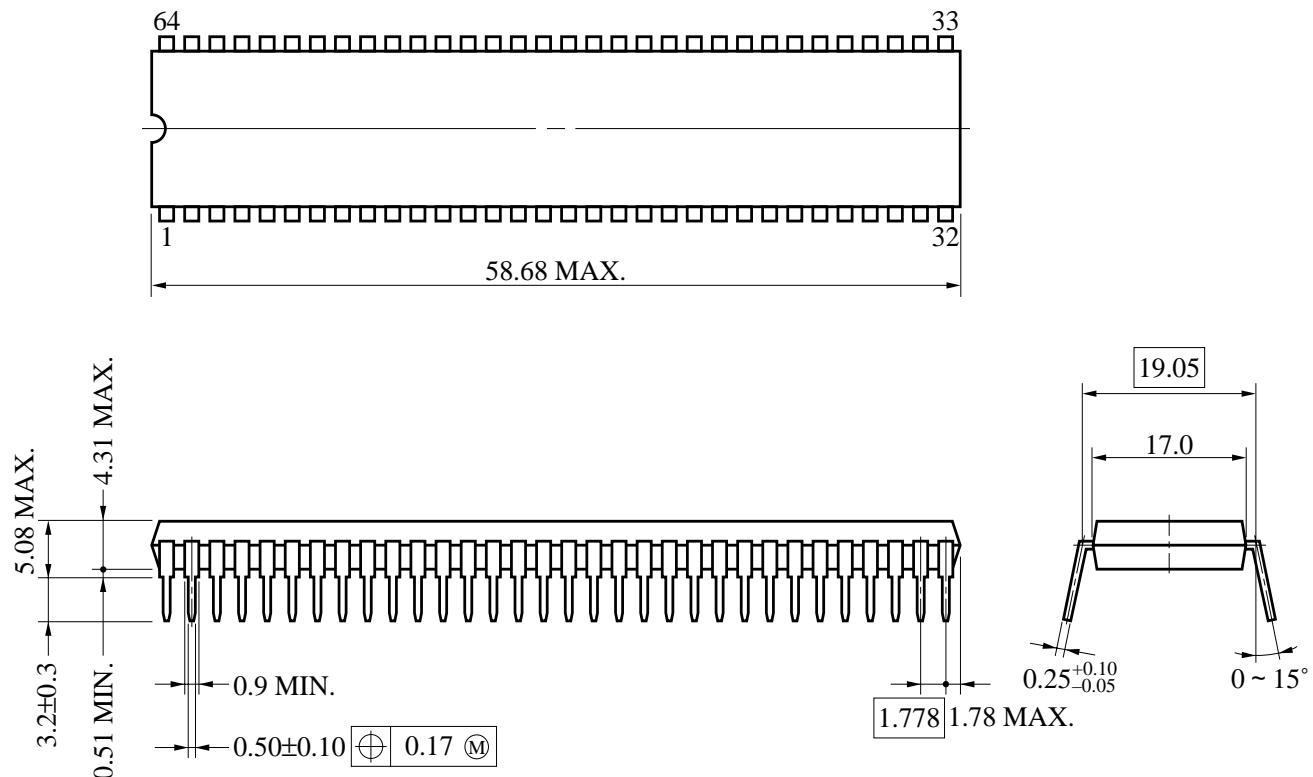

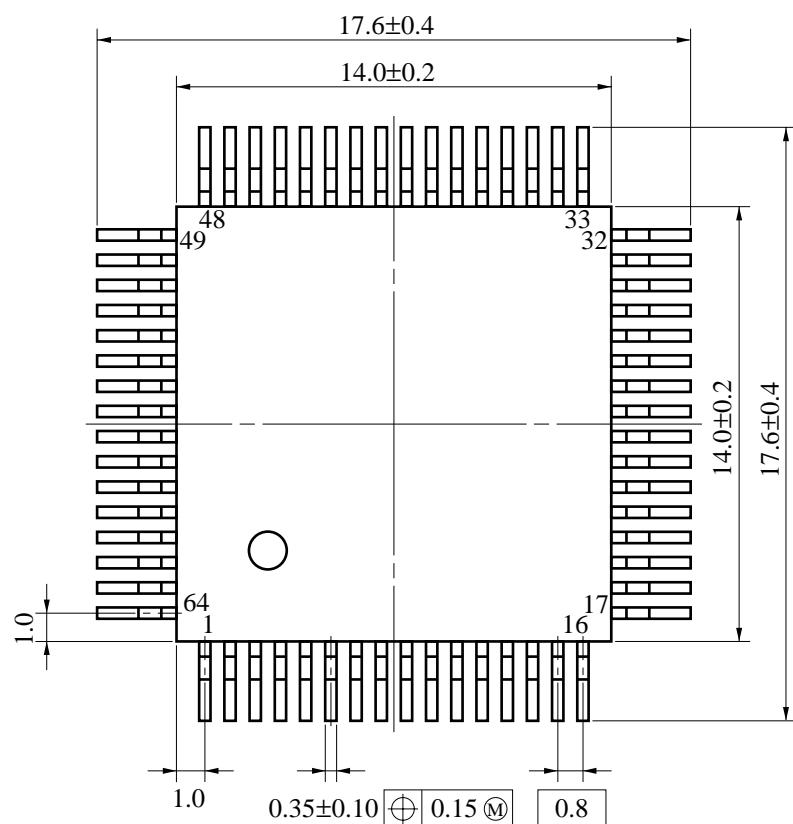

| オーダ名称                        | パッケージ                            |

|------------------------------|----------------------------------|

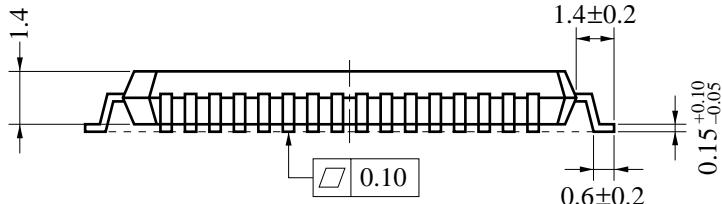

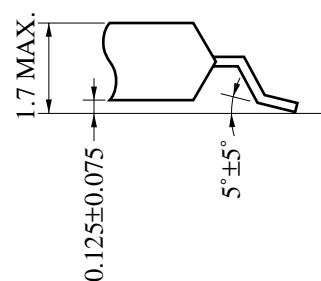

| $\mu$ PD78011FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

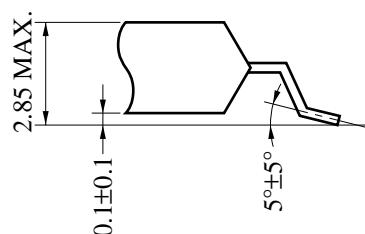

| $\mu$ PD78011FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

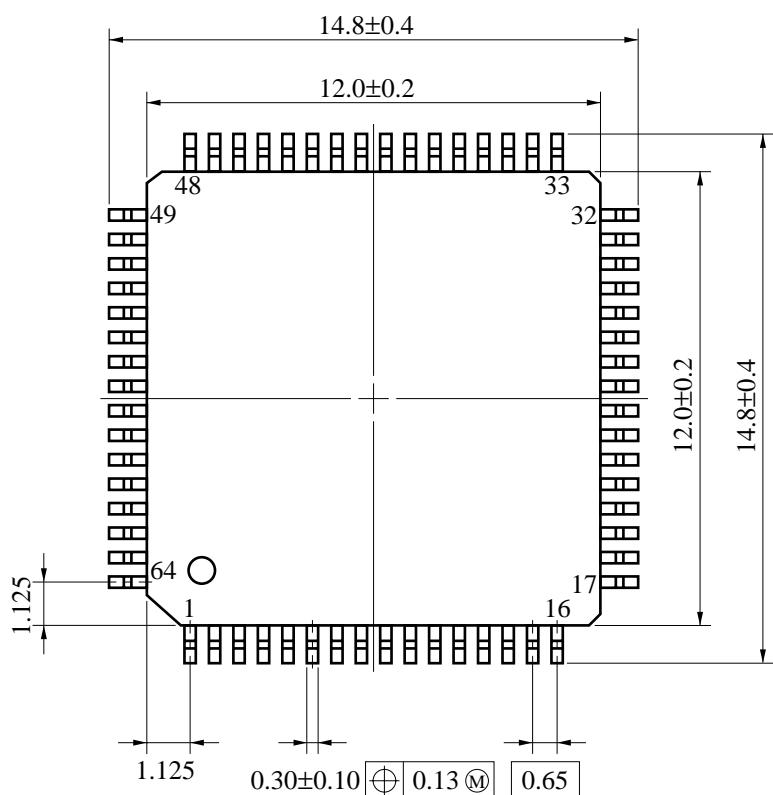

| $\mu$ PD78011FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| $\mu$ PD78012FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| $\mu$ PD78012FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

| $\mu$ PD78012FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| $\mu$ PD78013FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| $\mu$ PD78013FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

| $\mu$ PD78013FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| $\mu$ PD78014FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| $\mu$ PD78014FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

| $\mu$ PD78014FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| $\mu$ PD78015FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| $\mu$ PD78015FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

| $\mu$ PD78015FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| $\mu$ PD78016FCW-× × ×       | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| $\mu$ PD78016FGC-× × ×-AB8   | 64ピン・プラスチックQFP ( 14 mm )         |

| $\mu$ PD78016FGK-× × ×-8A8   | 64ピン・プラスチックLQFP ( 12 mm )        |

| ★ $\mu$ PD78018FCW-× × ×     | 64ピン・プラスチック・シュリンクDIP ( 750 mil ) |

| ★ $\mu$ PD78018FGC-× × ×-AB8 | 64ピン・プラスチックQFP ( 14 mm )         |

| ★ $\mu$ PD78018FGK-× × ×-8A8 | 64ピン・プラスチックLQFP ( 12 mm )        |

備考　× × × はROMコード番号です。

## ★ 78K/0シリーズの展開

78K/0シリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

Yサブシリーズは、I<sup>2</sup>Cバス対応の製品です。

| 制御用      |                          |

|----------|--------------------------|

| 100ピン    | μPD78075B / μPD78075BY   |

| 100ピン    | μPD78078 / μPD78078Y     |

| 100ピン    | μPD78070A / μPD78070AY   |

| 100ピン    | μPD780018注 / μPD780018Y注 |

| 80ピン     | μPD780058 / μPD780058Y   |

| 80ピン     | μPD78058F / μPD78058FY   |

| 80ピン     | μPD78054 / μPD78054Y     |

| 64ピン     | μPD780034 / μPD780034Y   |

| 64ピン     | μPD780024 / μPD780024Y   |

| 64ピン     | μPD78014H                |

| 64ピン     | μPD78018F / μPD78018FY   |

| 64ピン     | μPD78014 / μPD78014Y     |

| 64ピン     | μPD780001                |

| 64ピン     | μPD78002 / μPD78002Y     |

| 42/44ピン  | μPD78083                 |

| インバータ制御用 |                          |

| 64ピン     | μPD780964                |

| 64ピン     | μPD780924                |

| FIP®駆動用  |                          |

| 100ピン    | μPD780208                |

| 100ピン    | μPD780228                |

| 80ピン     | μPD78044H                |

| 80ピン     | μPD78044F                |

| LCD駆動用   |                          |

| 100ピン    | μPD780308 / μPD780308Y   |

| 100ピン    | μPD78064B                |

| 100ピン    | μPD78064 / μPD78064Y     |

| IEBus™対応 |                          |

| 80ピン     | μPD78098B                |

| 80ピン     | μPD78098                 |

| メータ制御用   |                          |

| 80ピン     | μPD780973                |

| LV用      |                          |

| 64ピン     | μPD78P0914               |

注 計画中

各サブシリーズ間の主な機能の違いを次に示します。

| サブシリーズ名      | 機能              | ROM容量     | タイマ      |           |           |           | 8-bit<br>A/D | 10-bit<br>A/D | 8-bit<br>D/A | シリアル・<br>インタフェース              | I/O             | V <sub>DD</sub><br>MIN.値 | 外部<br>拡張 |       |   |

|--------------|-----------------|-----------|----------|-----------|-----------|-----------|--------------|---------------|--------------|-------------------------------|-----------------|--------------------------|----------|-------|---|

|              |                 |           | 8-bit    | 16-bit    | 時計        | WDT       |              |               |              |                               |                 |                          |          |       |   |

| 制御用          | $\mu$ PD78075B  | 32 K-40 K | 4ch      | 1ch       | 1ch       | 1ch       | 8ch          | -             | 2ch          | 3ch( UART:1ch )               | 88本             | 1.8 V                    |          |       |   |

|              | $\mu$ PD78078   | 48 K-60 K |          |           |           |           |              |               |              |                               | 61本             | 2.7 V                    |          |       |   |

|              | $\mu$ PD78070A  | -         |          |           |           |           |              |               |              |                               | -               | 2ch( 時分割3線:1ch )         | 88本      |       |   |

|              | $\mu$ PD780018  | 48 K-60 K |          |           |           |           |              |               |              |                               | 2ch             | 3ch( 時分割UART:1ch )       | 68本      | 1.8 V |   |

|              | $\mu$ PD780058  | 24 K-60 K | 2ch      | 8 K-32 K  | 16 K-60 K | 16 K-60 K | 8ch          | -             | 8ch          | 3ch( UART:1ch,<br>時分割3線:1ch ) | 69本             | 2.7 V                    |          |       |   |

|              | $\mu$ PD78058F  | 48 K-60 K |          |           |           |           |              |               |              |                               | 3ch( UART:1ch ) | 69本                      | 2.0 V    |       |   |

|              | $\mu$ PD78054   | 16 K-60 K |          |           |           |           |              |               |              |                               | -               | 51本                      | 1.8 V    |       |   |

|              | $\mu$ PD780034  | 8 K-32 K  | 8 K-32 K | 16 K-60 K | 16 K-60 K | 16 K-60 K | 8ch          | -             | 8ch          | 2ch                           | 53本             | 2.7 V                    | -        |       |   |

|              | $\mu$ PD780024  |           |          |           |           |           |              |               |              |                               | 1ch             | 39本                      |          |       |   |

|              | $\mu$ PD78014H  |           |          |           |           |           |              |               |              |                               | 53本             |                          |          |       |   |

|              | $\mu$ PD78018F  | 8 K-60 K  | 8 K-16 K | 8 K-32 K  | 8 K-32 K  | 8 K-32 K  | 8ch          | -             | 8ch          | 1ch( UART:1ch )               | 33本             | 1.8 V                    | -        | -     |   |

|              | $\mu$ PD78014   | 8 K-32 K  |          |           |           |           |              |               |              |                               | 1ch( UART:1ch ) | 33本                      |          |       |   |

|              | $\mu$ PD780001  | 8 K       |          |           |           |           |              |               |              |                               | -               | 47本                      | 2.7 V    |       |   |

| インバータ<br>制御用 | $\mu$ PD780964  | 8 K-32 K  | 3ch      | 注         | -         | 1ch       | 8ch          | -             | 2ch          | 2ch( UART:2ch )               | 47本             | 2.7 V                    | -        | -     | - |

|              | $\mu$ PD780924  |           |          |           |           |           |              |               |              |                               |                 | 8ch                      | -        |       |   |

| FIP<br>駆動用   | $\mu$ PD780208  | 32 K-60 K | 2ch      | 1ch       | 1ch       | 1ch       | 8ch          | -             | -            | 2ch                           | 74本             | 2.7 V                    | -        | -     | - |

|              | $\mu$ PD780228  | 48 K-60 K | 3ch      | -         | -         |           |              |               |              | 1ch                           | 72本             | 4.5 V                    |          |       |   |

|              | $\mu$ PD78044H  | 32 K-48 K | 2ch      | 1ch       | 1ch       |           |              |               |              | 68本                           | 2.7 V           |                          |          |       |   |

|              | $\mu$ PD78044F  | 16 K-40 K |          |           |           |           |              |               |              | 2ch                           |                 |                          |          |       |   |

| LCD<br>駆動用   | $\mu$ PD780308  | 48 K-60 K | 2ch      | 1ch       | 1ch       | 1ch       | 8ch          | -             | -            | 3ch( 時分割UART:1ch )            | 57本             | 2.0 V                    | -        | -     | - |

|              | $\mu$ PD78064B  | 32 K      |          |           |           |           |              |               |              |                               |                 | 2ch( UART:1ch )          |          |       |   |

|              | $\mu$ PD78064   | 16 K-32 K |          |           |           |           |              |               |              |                               |                 |                          |          |       |   |

| IEBus<br>対応  | $\mu$ PD78098B  | 40 K-60 K | 2ch      | 1ch       | 1ch       | 1ch       | 8ch          | -             | 2ch          | 3ch( UART:1ch )               | 69本             | 2.7 V                    | -        | -     | - |

|              | $\mu$ PD78098   | 32 K-60 K |          |           |           |           |              |               |              |                               |                 |                          |          |       |   |

| メータ<br>制御用   | $\mu$ PD780973  | 24 K-32 K | 3ch      | 1ch       | 1ch       | 1ch       | 5ch          | -             | -            | 2ch( UART:1ch )               | 56本             | 4.5 V                    | -        |       |   |

| LV用          | $\mu$ PD78P0914 | 32 K      | 6ch      | -         | -         | 1ch       | 8ch          | -             | -            | 2ch                           | 54本             | 4.5 V                    |          |       |   |

注 10ビット・タイマ：1チャネル

## 機能概要

| 品名                            |                  | $\mu$ PD78011F                                                                                                                                                                                                              | $\mu$ PD78012F | $\mu$ PD78013F | $\mu$ PD78014F | $\mu$ PD78015F | $\mu$ PD78016F | $\mu$ PD78018F |    |       |          |       |           |       |                               |       |

|-------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----|-------|----------|-------|-----------|-------|-------------------------------|-------|

| 内部メモリ                         | ROM              | 8 Kバイト                                                                                                                                                                                                                      | 16 Kバイト        | 24 Kバイト        | 32 Kバイト        | 40 Kバイト        | 48 Kバイト        | 60 Kバイト        |    |       |          |       |           |       |                               |       |

|                               | 高速RAM            | 512バイト                                                                                                                                                                                                                      |                | 1024バイト        |                |                |                |                |    |       |          |       |           |       |                               |       |

|                               | 拡張RAM            | -                                                                                                                                                                                                                           |                |                |                | 512 バイト        | 1024バイト        |                |    |       |          |       |           |       |                               |       |

|                               | バッファRAM          | 32バイト                                                                                                                                                                                                                       |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| メモリ空間                         |                  | 64 Kバイト                                                                                                                                                                                                                     |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 汎用レジスタ                        |                  | 8 ビット × 32 レジスタ ( 8 ビット × 8 レジスタ × 4 バンク )                                                                                                                                                                                  |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 最小命令実行時間                      |                  | 最小命令実行時間の可変機能内蔵                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

|                               | メイン・システム・クロック選択時 | 0.4 $\mu$ s/0.8 $\mu$ s/1.6 $\mu$ s/3.2 $\mu$ s/6.4 $\mu$ s ( 10.0 MHz動作時 )                                                                                                                                                 |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

|                               | サブシステム・クロック選択時   | 122 $\mu$ s ( 32.768 kHz動作時 )                                                                                                                                                                                               |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 命令セット                         |                  | <ul style="list-style-type: none"> <li>・ 16ビット演算</li> <li>・ 乗除算 ( 8 ビット × 8 ビット , 16 ビット ÷ 8 ビット )</li> <li>・ ビット操作 ( セット , リセット , テスト , ブール演算 )</li> <li>・ BCD補正など</li> </ul>                                              |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| I/Oポート                        |                  | <table border="0"> <tr> <td>合計</td> <td>: 53本</td> </tr> <tr> <td>・ CMOS入力</td> <td>: 2 本</td> </tr> <tr> <td>・ CMOS入出力</td> <td>: 47本</td> </tr> <tr> <td>・ N-chオープン・ドレーン入出力 ( 15 V耐圧 )</td> <td>: 4 本</td> </tr> </table> |                |                |                |                |                |                | 合計 | : 53本 | ・ CMOS入力 | : 2 本 | ・ CMOS入出力 | : 47本 | ・ N-chオープン・ドレーン入出力 ( 15 V耐圧 ) | : 4 本 |

| 合計                            | : 53本            |                                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| ・ CMOS入力                      | : 2 本            |                                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| ・ CMOS入出力                     | : 47本            |                                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| ・ N-chオープン・ドレーン入出力 ( 15 V耐圧 ) | : 4 本            |                                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| A/Dコンバータ                      |                  | <ul style="list-style-type: none"> <li>・ 8 ビット分解能 × 8 チャネル</li> <li>・ 広い電源電圧範囲で動作可能 : AV<sub>DD</sub> = 1.8 ~ 5.5 V</li> </ul>                                                                                              |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| シリアル・インターフェース                 |                  | <ul style="list-style-type: none"> <li>・ 3 線式シリアルI/O / SBI / 2線式シリアルI/Oモード選択可能 : 1 チャネル</li> <li>・ 3 線式モード ( 最大32バイト自動送受信機能内蔵 ) : 1 チャネル</li> </ul>                                                                         |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| タイマ                           |                  | <ul style="list-style-type: none"> <li>・ 16ビット・タイマ / イベント・カウンタ : 1 チャネル</li> <li>・ 8 ビット・タイマ / イベント・カウンタ : 2 チャネル</li> <li>・ 時計用タイマ : 1 チャネル</li> <li>・ ウオッヂドッギング・タイマ : 1 チャネル</li> </ul>                                   |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| タイマ出力                         |                  | 3 本 ( 14ビットPWM出力可能 1 本 )                                                                                                                                                                                                    |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| クロック出力                        |                  | 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz<br>( メイン・システム・クロック : 10.0 MHz動作時 )<br>32.768 kHz ( サブシステム・クロック : 32.768 kHz動作時 )                                                                                    |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| ブザー出力                         |                  | 2.4 kHz, 4.9 kHz, 9.8 kHz ( メイン・システム・クロック : 10.0 MHz動作時 )                                                                                                                                                                   |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| ペクタ                           | マスカブル            | 内部 : 8 , 外部 : 4                                                                                                                                                                                                             |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

|                               | ノンマスカブル          | 内部 : 1                                                                                                                                                                                                                      |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 割り込み                          | 要因               | ソフトウエア                                                                                                                                                                                                                      |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| テスト入力                         |                  | 内部 : 1 本 , 外部 : 1 本                                                                                                                                                                                                         |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 電源電圧                          |                  | VDD = 1.8 ~ 5.5 V                                                                                                                                                                                                           |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| 動作周囲温度                        |                  | TA = - 40 ~ + 85                                                                                                                                                                                                            |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

| パッケージ                         |                  | <ul style="list-style-type: none"> <li>・ 64ピン・プラスチック・シュリンクDIP ( 750 mil )</li> <li>・ 64ピン・プラスチックQFP ( 14 mm )</li> <li>・ 64ピン・プラスチックLQFP ( 12 mm )</li> </ul>                                                               |                |                |                |                |                |                |    |       |          |       |           |       |                               |       |

## 目 次

|                           |    |

|---------------------------|----|

| 1 . 端子接続図 (Top View) ...  | 8  |

| 2 . ブロック図 ...             | 11 |

| 3 . 端子機能一覧 ...            | 12 |

| 3.1 ポート端子 ...             | 12 |

| 3.2 ポート以外の端子 ...          | 13 |

| 3.3 端子の入出力回路と未使用端子の処理 ... | 15 |

| 4 . メモリ空間 ...             | 17 |

| 5 . 周辺ハードウェア機能の特徴 ...     | 19 |

| 5.1 ポート ...               | 19 |

| 5.2 クロック発生回路 ...          | 20 |

| 5.3 タイマ/イベント・カウンタ ...     | 21 |

| 5.4 クロック出力制御回路 ...        | 23 |

| 5.5 ブザー出力制御回路 ...         | 23 |

| 5.6 A/Dコンバータ ...          | 24 |

| 5.7 シリアル・インターフェース ...     | 24 |

| 6 . 割り込み機能とテスト機能 ...      | 26 |

| 6.1 割り込み機能 ...            | 26 |

| 6.2 テスト機能 ...             | 29 |

| 7 . 外部デバイス拡張機能 ...        | 30 |

| 8 . スタンバイ機能 ...           | 30 |

| 9 . リセット機能 ...            | 30 |

| 10 . 命令セット ...            | 31 |

| 11 . 電気的特性 ...            | 33 |

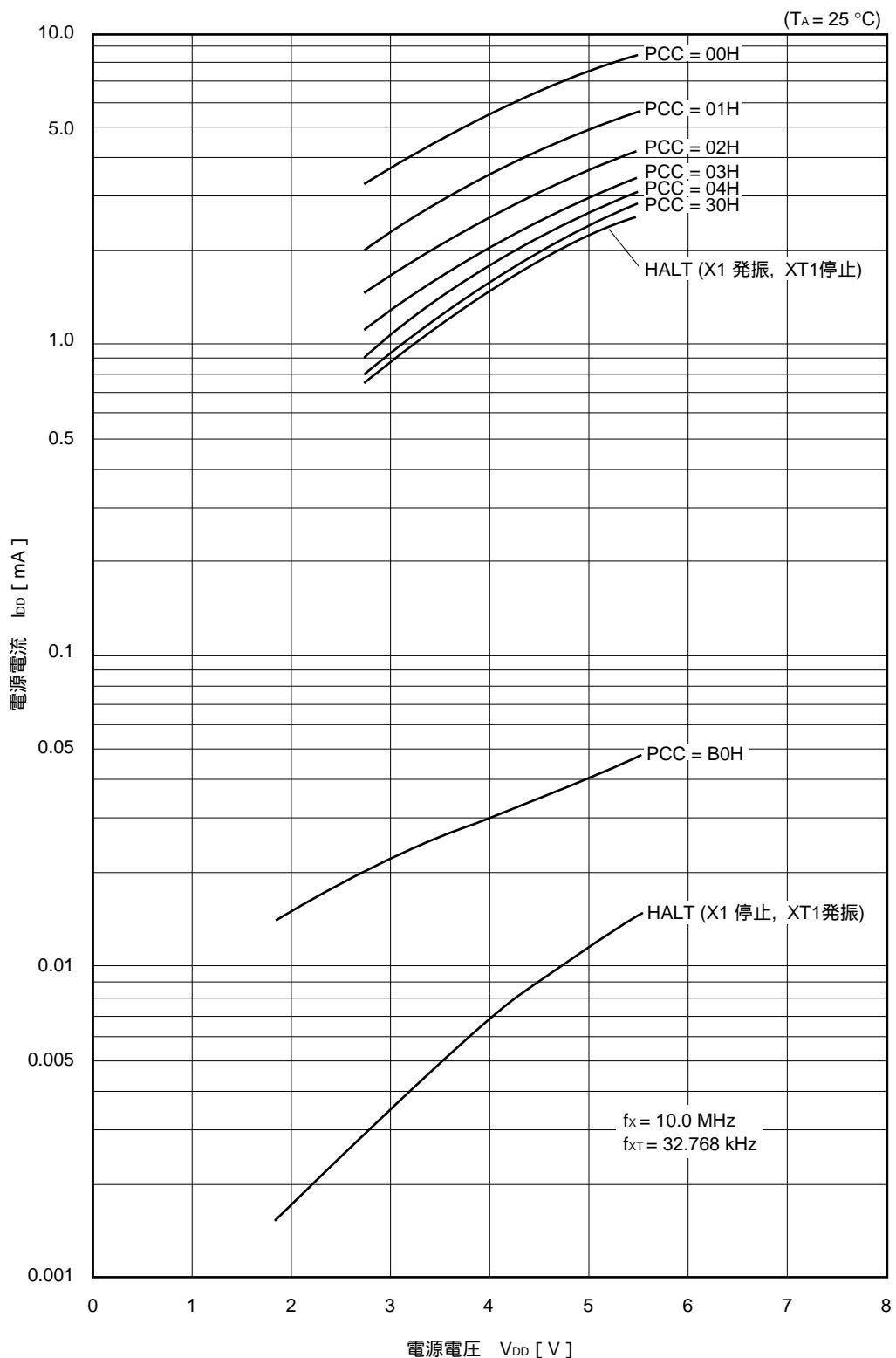

| 12 . 特性曲線 (参考値) ...       | 56 |

| 13 . 外形図 ...              | 57 |

| 14 . 半田付け推奨条件 ...         | 60 |

付録A . 開発ツール ... 63

付録B . 関連資料 ... 65

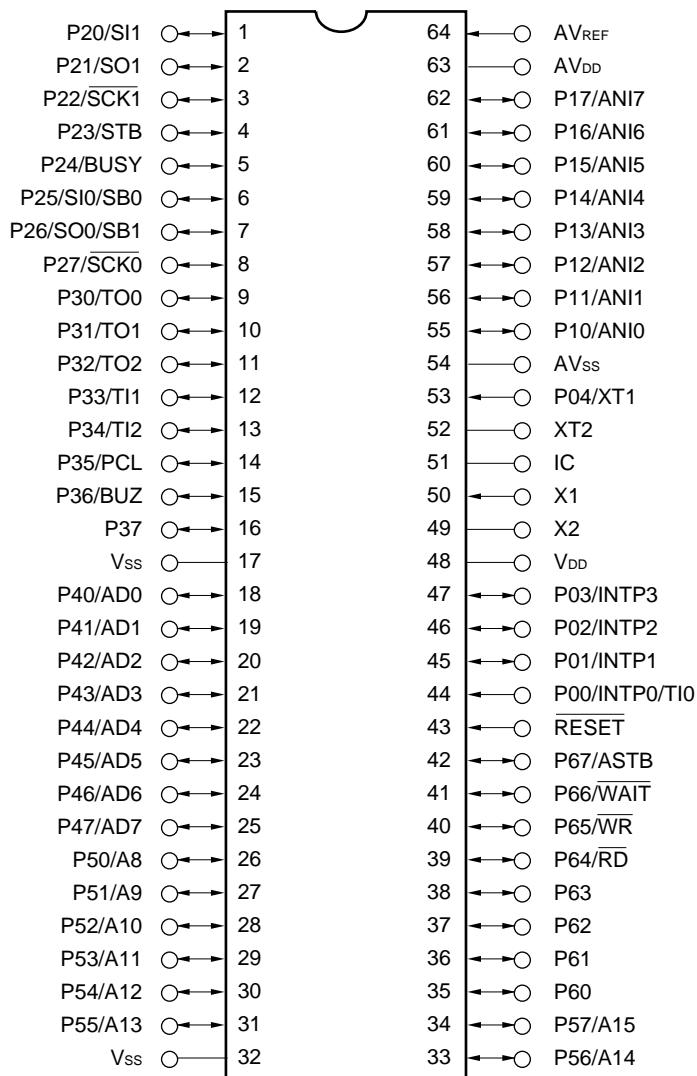

## 1. 端子接続図 (Top View)

• 64ピン・プラスチック・シュリンクDIP (750 mil)

$\mu$ PD78011FCW-×××, 78012FCW-×××, 78013FCW-×××

$\mu$ PD78014FCW-×××, 78015FCW-×××, 78016FCW-×××

★  $\mu$ PD78018FCW-×××

注意 1. IC (Internally Connected) 端子はVssに直接接続してください。

2. AVDD端子はVDDに接続してください。

3. AVss端子はVssに接続してください。

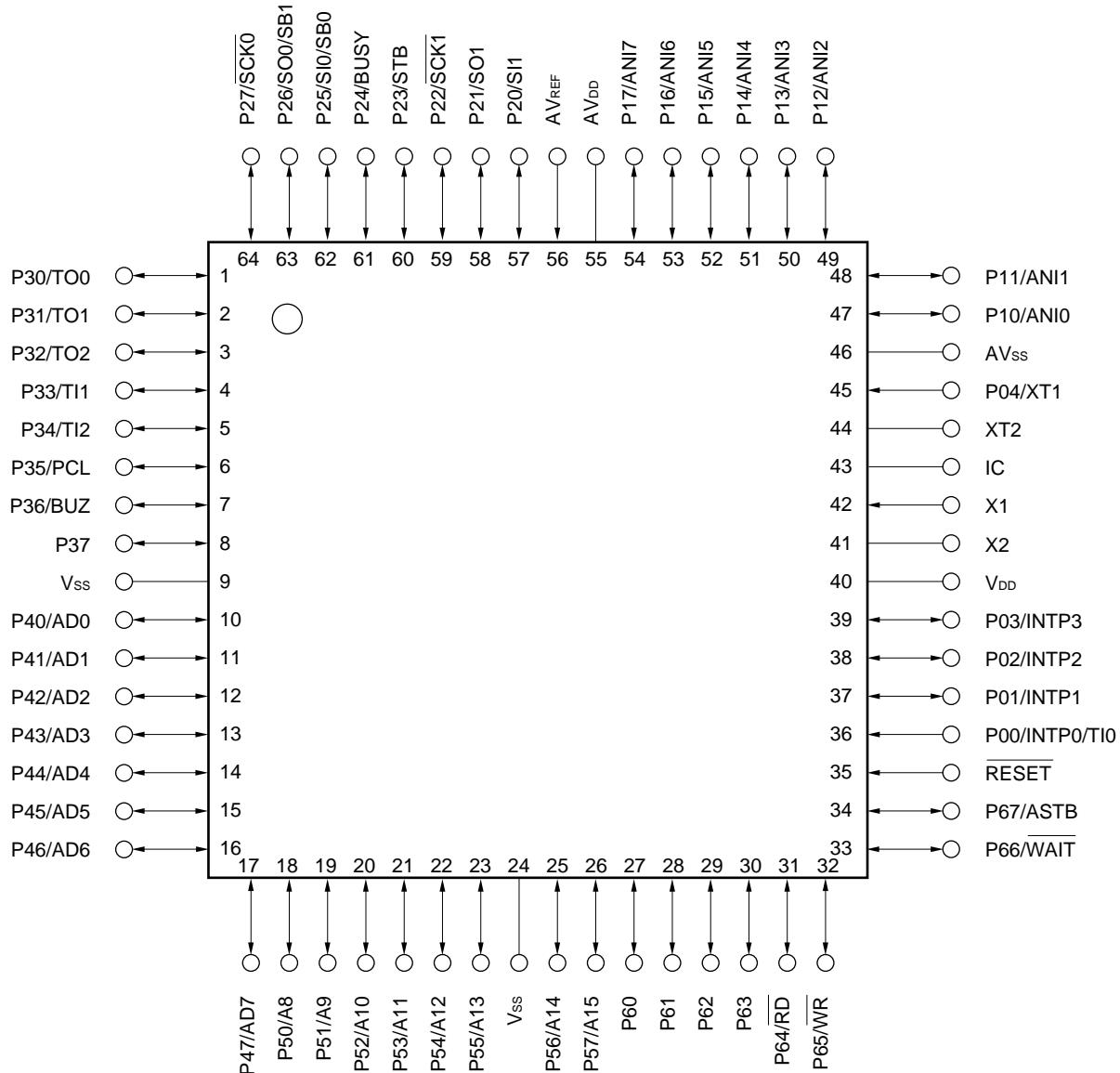

## • 64ピン・プラスチックQFP ( 14 mm )

$\mu$ PD78011FGC-×××-AB8, 78012FGC-×××-AB8, 78013FGC-×××-AB8,

$\mu$ PD78014FGC-×××-AB8, 78015FGC-×××-AB8, 78016FGC-×××-AB8,

★  $\mu$ PD78018FGC-×××-AB8

## • 64ピン・プラスチックLQFP ( 12 mm )

$\mu$ PD78011FGK-×××-8A8, 78012FGK-×××-8A8, 78013FGK-×××-8A8,

$\mu$ PD78014FGK-×××-8A8, 78015FGK-×××-8A8, 78016FGK-×××-8A8,

★  $\mu$ PD78018FGK-×××-8A8

注意 1 . IC (Internally Connected) 端子はVssに直接接続してください。

2 . AV<sub>DD</sub>端子はV<sub>DD</sub>に接続してください。

3 . AV<sub>SS</sub>端子はV<sub>SS</sub>に接続してください。

保守／廃止

|                   |                              |                           |                                 |

|-------------------|------------------------------|---------------------------|---------------------------------|

| A8-A15            | : Address Bus                | PCL                       | : Programmable Clock            |

| AD0-AD7           | : Address/Data Bus           | <u>RD</u>                 | : Read Strobe                   |

| ANIO-ANI7         | : Analog Input               | <u>RESET</u>              | : Reset                         |

| ASTB              | : Address Strobe             | SB0, SB1                  | : Serial Bus                    |

| AV <sub>DD</sub>  | : Analog Power Supply        | <u>SCK0</u> , <u>SCK1</u> | : Serial Clock                  |

| AV <sub>REF</sub> | : Analog Reference Voltage   | SI0, SI1                  | : Serial Input                  |

| AV <sub>ss</sub>  | : Analog Ground              | SO0, SO1                  | : Serial Output                 |

| BUSY              | : Busy                       | STB                       | : Strobe                        |

| BUZ               | : Buzzer Clock               | TI0-TI2                   | : Timer Input                   |

| IC                | : Internally Connected       | TO0-TO2                   | : Timer Output                  |

| INTP0-INTP3       | : Interrupt from Peripherals | V <sub>DD</sub>           | : Power Supply                  |

| P00-P04           | : Port0                      | V <sub>ss</sub>           | : Ground                        |

| P10-P17           | : Port1                      | <u>WAIT</u>               | : Wait                          |

| P20-P27           | : Port2                      | <u>WR</u>                 | : Write Strobe                  |

| P30-P37           | : Port3                      | X1, X2                    | : Crystal ( Main System Clock ) |

| P40-P47           | : Port4                      | XT1, XT2                  | : Crystal ( Subsystem Clock )   |

| P50-P57           | : Port5                      |                           |                                 |

| P60-P67           | : Port6                      |                           |                                 |

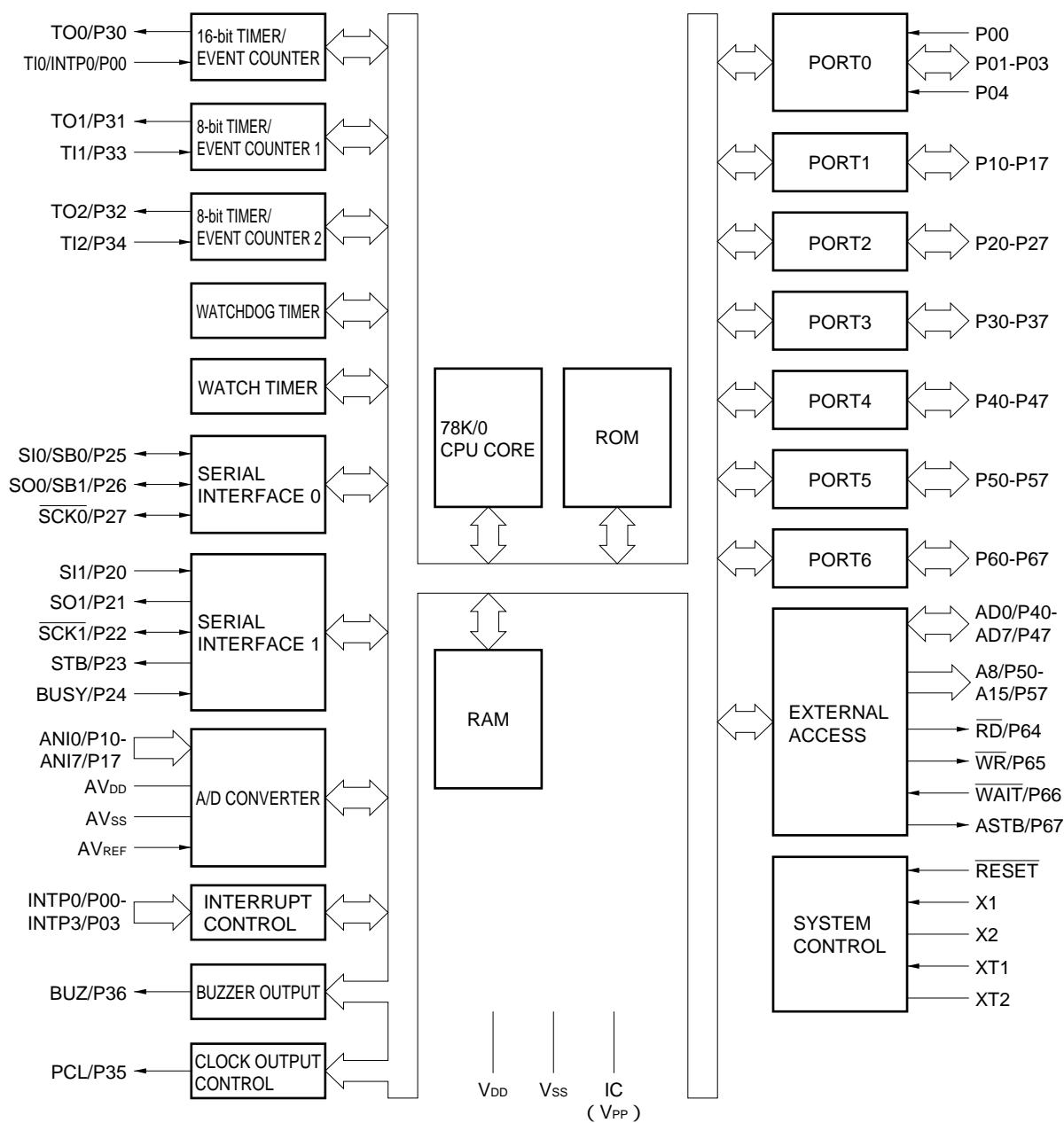

## 2. ブロック図

備考1. 内部ROM, RAM容量は製品によって異なります。

2. ( )内は  $\mu$ PD78P018Fのとき

## 3. 端子機能一覧

## 3.1 ポート端子 (1/2)

| 端子名称              | 入出力 | 機能                                                                                                                                      | リセット時 | 兼用端子      |

|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| P00               | 入力  | ポート 0。<br>入力専用。                                                                                                                         | 入力    | INTP0/TI0 |

| P01               | 入出力 | 5 ビット入出力ポート。<br>1 ビット単位で入力 / 出力の指定可能。                                                                                                   | 入力    | INTP1     |

| P02               |     | 入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                                                                                |       | INTP2     |

| P03               |     |                                                                                                                                         |       | INTP3     |

| P04 <sup>注1</sup> | 入力  | 入力専用。                                                                                                                                   | 入力    | XT1       |

| P10-P17           | 入出力 | ポート 1。<br>8 ビット入出力ポート。<br>1 ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。 <sup>注2</sup>                               | 入力    | ANI0-ANI7 |

| P20               | 入出力 | ポート 2。<br>8 ビット入出力ポート。<br>1 ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                             | 入力    | SI1       |

| P21               |     |                                                                                                                                         |       | SO1       |

| P22               |     |                                                                                                                                         |       | SCK1      |

| P23               |     |                                                                                                                                         |       | STB       |

| P24               |     |                                                                                                                                         |       | BUSY      |

| P25               |     |                                                                                                                                         |       | SI0/SB0   |

| P26               |     |                                                                                                                                         |       | SO0/SB1   |

| P27               |     |                                                                                                                                         |       | SCK0      |

| P30               | 入出力 | ポート 3。<br>8 ビット入出力ポート。<br>1 ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                             | 入力    | TO0       |

| P31               |     |                                                                                                                                         |       | TO1       |

| P32               |     |                                                                                                                                         |       | TO2       |

| P33               |     |                                                                                                                                         |       | TI1       |

| P34               |     |                                                                                                                                         |       | TI2       |

| P35               |     |                                                                                                                                         |       | PCL       |

| P36               |     |                                                                                                                                         |       | BUZ       |

| P37               |     |                                                                                                                                         |       | -         |

| P40-P47           | 入出力 | ポート 4。<br>8 ビット入出力ポート。<br>8 ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。<br>立ち下がりエッジの検出により、テスト入力フラグ (KRIF) を 1 にセット。 | 入力    | AD0-AD7   |

注1 . P04/XT1端子を入力ポートとして使用するときは、プロセッサ・クロック・コントロール・レジスタ (PCC) のビット6 (FRC) に1を設定してください (サブシステム・クロック発振回路の内蔵フィードバック抵抗を使用しないでください)。

2 . P10/ANI0-P17/ANI7端子をA/Dコンバータのアナログ入力として使用するとき、内蔵プルアップ抵抗が自動的に使用されなくなります。

## 3.1 ポート端子 (2/2)

| 端子名称    | 入出力 | 機能                                                                                                    | リセット時 | 兼用端子   |

|---------|-----|-------------------------------------------------------------------------------------------------------|-------|--------|

| P50-P57 | 入出力 | ポート5。<br>8ビット入出力ポート。<br>LEDを直接駆動可能。<br>1ビット単位で入力／出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。 | 入力    | A8-A15 |

| P60     | 入出力 | ポート6。<br>8ビット入出力ポート。<br>1ビット単位で入力／出力の指定可能。                                                            | 入力    | -      |

| P61     |     |                                                                                                       |       |        |

| P62     |     |                                                                                                       |       |        |

| P63     |     |                                                                                                       |       |        |

| P64     |     |                                                                                                       |       | RD     |

| P65     |     |                                                                                                       |       | WR     |

| P66     |     |                                                                                                       |       | WAIT   |

| P67     |     |                                                                                                       |       | ASTB   |

## 3.2 ポート以外の端子 (1/2)

| 端子名称  | 入出力 | 機能                                                          | リセット時 | 兼用端子      |

|-------|-----|-------------------------------------------------------------|-------|-----------|

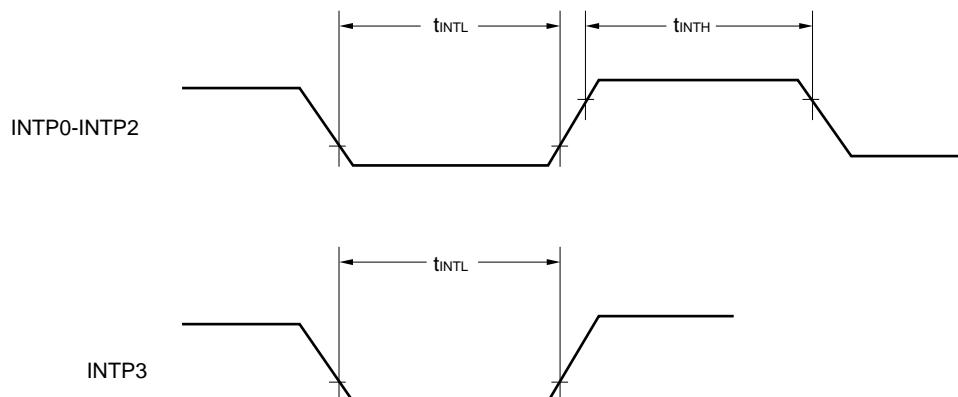

| INTP0 | 入力  | 有効エッジ（立ち上がりエッジ、立ち下がりエッジ、立ち上がりおよび立ち下がりの両エッジ）指定可能な外部割り込み要求入力。 | 入力    | P00/TI0   |

| INTP1 |     |                                                             |       | P01       |

| INTP2 |     |                                                             |       | P02       |

| INTP3 |     |                                                             |       | P03       |

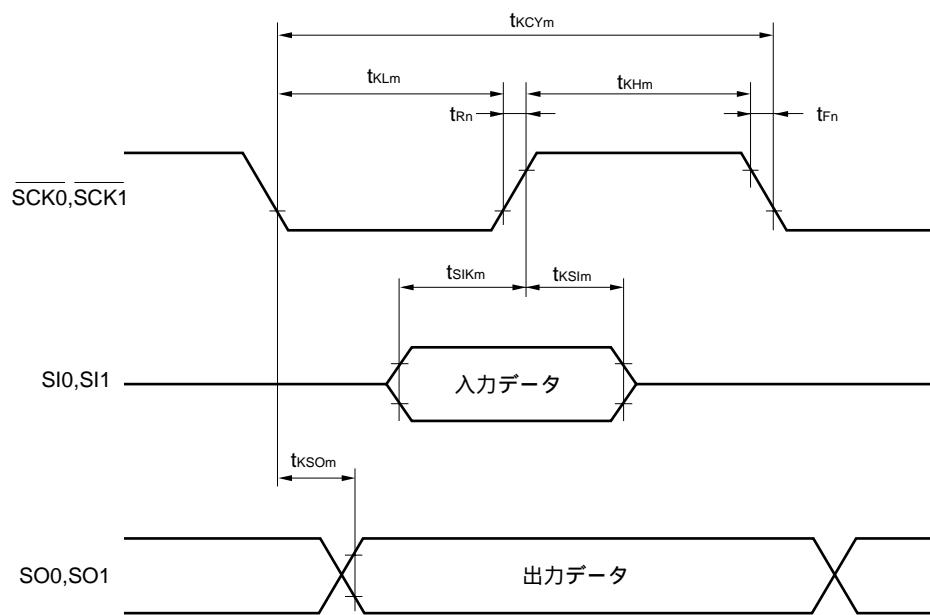

| SI0   | 入力  | シリアル・インターフェースのシリアル・データ入力。                                   | 入力    | P25/SB0   |

| SI1   |     |                                                             |       | P20       |

| SO0   | 出力  | シリアル・インターフェースのシリアル・データ出力。                                   | 入力    | P26/SB1   |

| SO1   |     |                                                             |       | P21       |

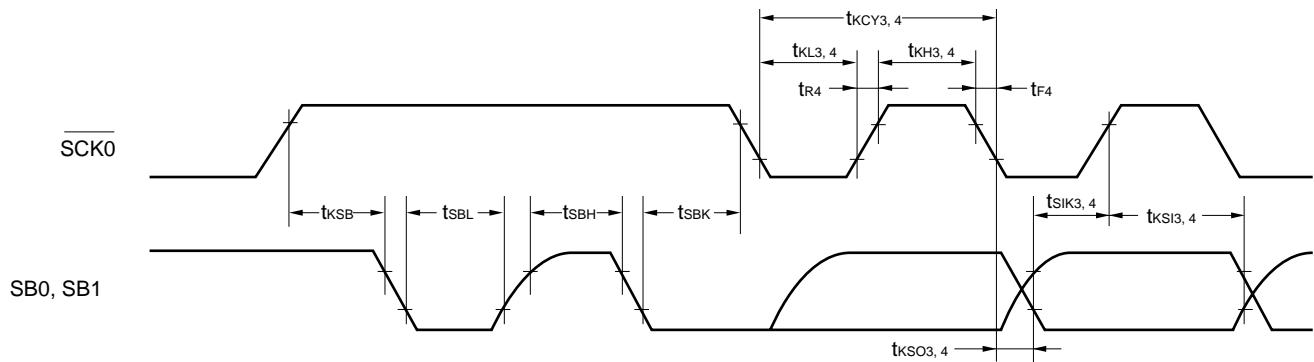

| SB0   | 入出力 | シリアル・インターフェースのシリアル・データ入力／出力。                                | 入力    | P25/SI0   |

| SB1   |     |                                                             |       | P26/SO0   |

| SCK0  | 入出力 | シリアル・インターフェースのシリアル・クロック入力／出力。                               | 入力    | P27       |

| SCK1  |     |                                                             |       | P22       |

| STB   | 出力  | シリアル・インターフェース自動送受信用ストローブ出力。                                 | 入力    | P23       |

| BUSY  | 入力  | シリアル・インターフェース自動送受信用ビジィ入力。                                   | 入力    | P24       |

| TI0   | 入力  | 16ビット・タイマ(TM0)への外部カウント・クロック入力。                              | 入力    | P00/INTP0 |

| TI1   |     | 8ビット・タイマ(TM1)への外部カウント・クロック入力。                               |       | P33       |

| TI2   |     | 8ビット・タイマ(TM2)への外部カウント・クロック入力。                               |       | P34       |

| TO0   | 出力  | 16ビット・タイマ(TM0)出力(14ビットPWM出力と兼用)。                            | 入力    | P30       |

| TO1   |     | 8ビット・タイマ(TM1)出力。                                            |       | P31       |

| TO2   |     | 8ビット・タイマ(TM2)出力。                                            |       | P32       |

## 3.2 ポート以外の端子 (2/2)

| 端子名称              | 入出力 | 機能                                                       | リセット時 | 兼用端子    |

|-------------------|-----|----------------------------------------------------------|-------|---------|

| PCL               | 出力  | クロック出力 (メイン・システム・クロック, サブシステム・クロックのトリミング用)。              | 入力    | P35     |

| BUZ               | 出力  | ブザー出力。                                                   | 入力    | P36     |

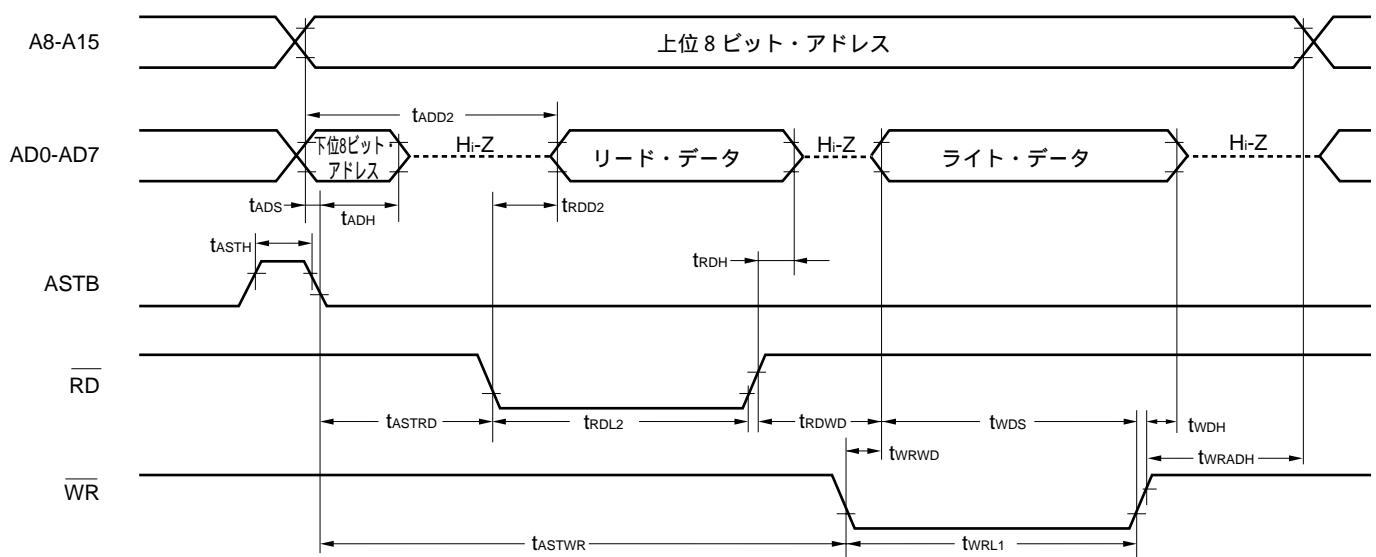

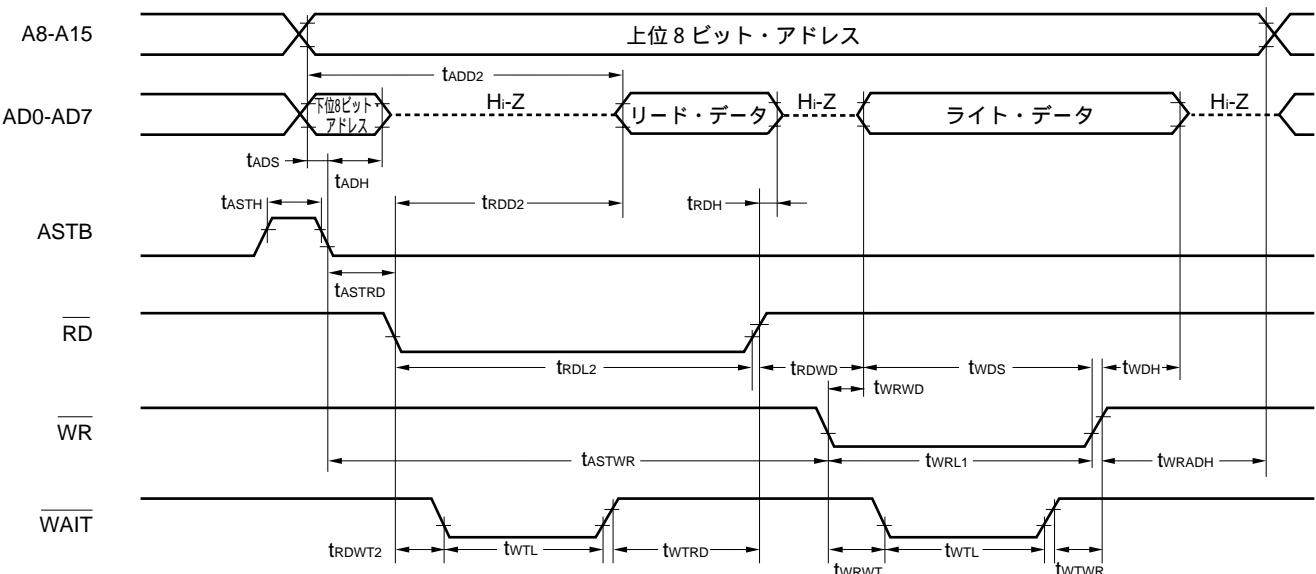

| AD0-AD7           | 入出力 | 外部にメモリを拡張する場合の, 下位アドレス / データ・バス。                         | 入力    | P40-P47 |

| A8-A15            | 出力  | 外部にメモリを拡張する場合の, 上位アドレス・バス。                               | 入力    | P50-P57 |

| RD                | 出力  | 外部メモリのリード動作用ストローブ信号出力。                                   | 入力    | P64     |

| WR                |     | 外部メモリのライト動作用ストローブ信号出力。                                   |       | P65     |

| WAIT              | 入力  | 外部メモリ・アクセス時のウェイト挿入。                                      | 入力    | P66     |

| ASTB              | 出力  | 外部メモリをアクセスするために, ポート4, ポート5に出力されるアドレス情報を外部でラッチするストローブ出力。 | 入力    | P67     |

| ANIO0-ANI7        | 入力  | A/Dコンバータのアナログ入力。                                         | 入力    | P10-P17 |

| AV <sub>REF</sub> | 入力  | A/Dコンバータの基準電圧入力。                                         | -     | -       |

| AV <sub>DD</sub>  | -   | A/Dコンバータのアナログ電源。V <sub>DD</sub> に接続。                     | -     | -       |

| AV <sub>SS</sub>  | -   | A/Dコンバータのグランド電位。V <sub>SS</sub> に接続。                     | -     | -       |

| RESET             | 入力  | システム・リセット入力。                                             | -     | -       |

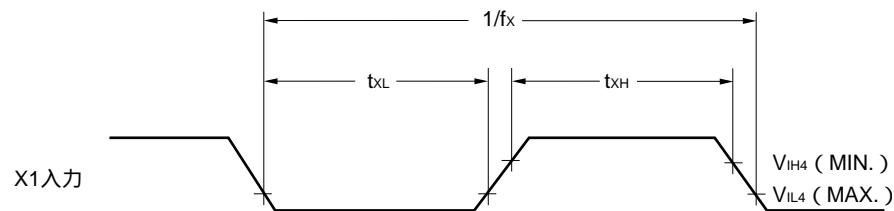

| X1                | 入力  | メイン・システム・クロック発振用クリ��石接続。                                 | -     | -       |

| X2                | -   |                                                          | -     | -       |

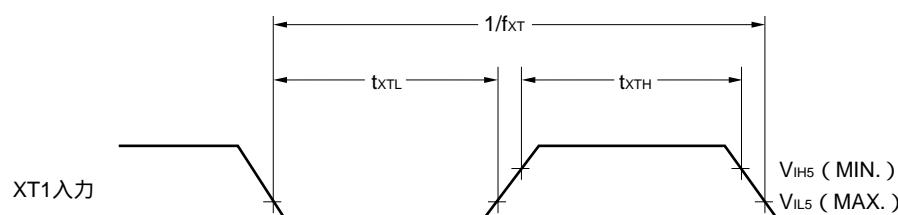

| XT1               | 入力  | サブシステム・クロック発振用クリ��石接続。                                   | 入力    | P04     |

| XT2               | -   |                                                          | -     | -       |

| V <sub>DD</sub>   | -   | 正電源。                                                     | -     | -       |

| V <sub>SS</sub>   | -   | グランド電位。                                                  | -     | -       |

| IC                | -   | 内部接続。VSSに直接接続。                                           | -     | -       |

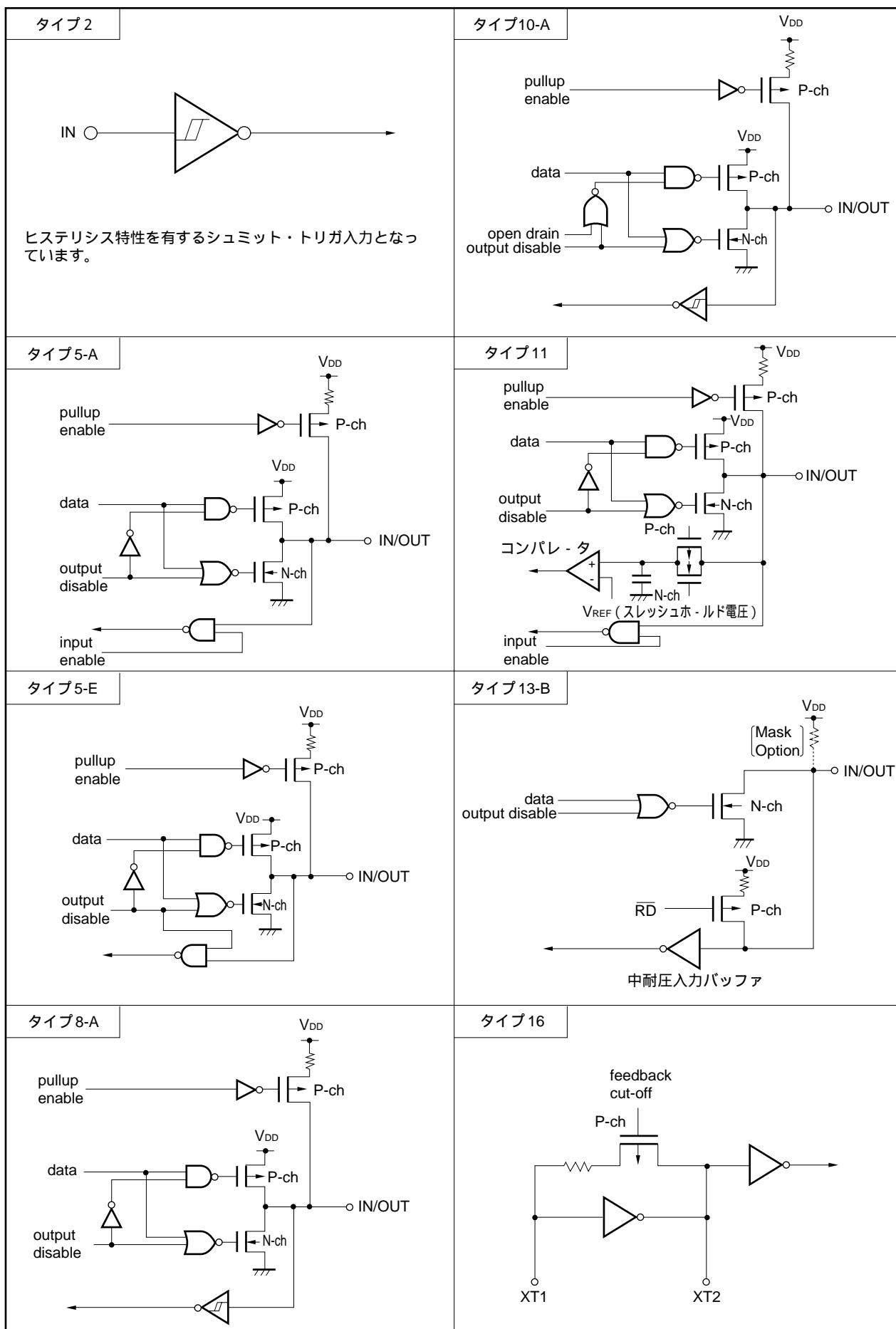

### 3.3 端子の入出力回路と未使用端子の処理

各端子の入出力回路タイプと、未使用端子の処理を表3-1に示します。

また、各タイプの入出力回路の構成は、図3-1を参照してください。

表3-1 各端子の入出力回路タイプ

| 端子名               | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法                                      |  |  |

|-------------------|----------|-----|--------------------------------------------------|--|--|

| P00/INTP0/TI0     | 2        | 入力  | V <sub>SS</sub> に接続                              |  |  |

| P01/INTP1         | 8-A      | 入出力 | 個別に抵抗を介して、V <sub>SS</sub> に接続                    |  |  |

| P02/INTP2         |          |     |                                                  |  |  |

| P03/INTP3         |          |     |                                                  |  |  |

| P04/XT1           | 16       | 入力  | V <sub>DD</sub> に接続                              |  |  |

| P10/ANI0-P17/ANI7 | 11       | 入出力 | 個別に抵抗を介して、V <sub>DD</sub> またはV <sub>SS</sub> に接続 |  |  |

| P20/SI1           | 8-A      |     |                                                  |  |  |

| P21/SO1           | 5-A      |     |                                                  |  |  |

| P22/SCK1          | 8-A      |     |                                                  |  |  |

| P23/STB           | 5-A      |     |                                                  |  |  |

| P24/BUSY          | 8-A      |     |                                                  |  |  |

| P25/SI0/SB0       | 10-A     |     |                                                  |  |  |

| P26/SO0/SB1       |          |     |                                                  |  |  |

| P27/SCK0          |          |     |                                                  |  |  |

| P30/TO0           | 5-A      |     |                                                  |  |  |

| P31/TO1           |          |     |                                                  |  |  |

| P32/TO2           |          |     |                                                  |  |  |

| P33/TI1           | 8-A      |     |                                                  |  |  |

| P34/TI2           |          |     |                                                  |  |  |

| P35/PCL           |          |     |                                                  |  |  |

| P36/BUZ           | 5-A      |     |                                                  |  |  |

| P37               |          |     |                                                  |  |  |

| P40/AD0-P47/AD7   | 5-E      |     |                                                  |  |  |

| P50/A8-P57/A15    | 5-A      |     |                                                  |  |  |

| P60-P63           | 13-B     |     |                                                  |  |  |

| P64/RD            | 5-A      |     |                                                  |  |  |

| P65/WR            |          |     |                                                  |  |  |

| P66/WAIT          |          |     |                                                  |  |  |

| P67/ASTB          | 2        |     |                                                  |  |  |

| RESET             |          |     |                                                  |  |  |

| XT2               |          |     |                                                  |  |  |

| AV <sub>REF</sub> |          |     |                                                  |  |  |

| AV <sub>DD</sub>  |          |     |                                                  |  |  |

| AV <sub>SS</sub>  | -        |     | V <sub>SS</sub> に接続                              |  |  |

| IC                |          |     |                                                  |  |  |

図3-1 端子の入出力回路一覧

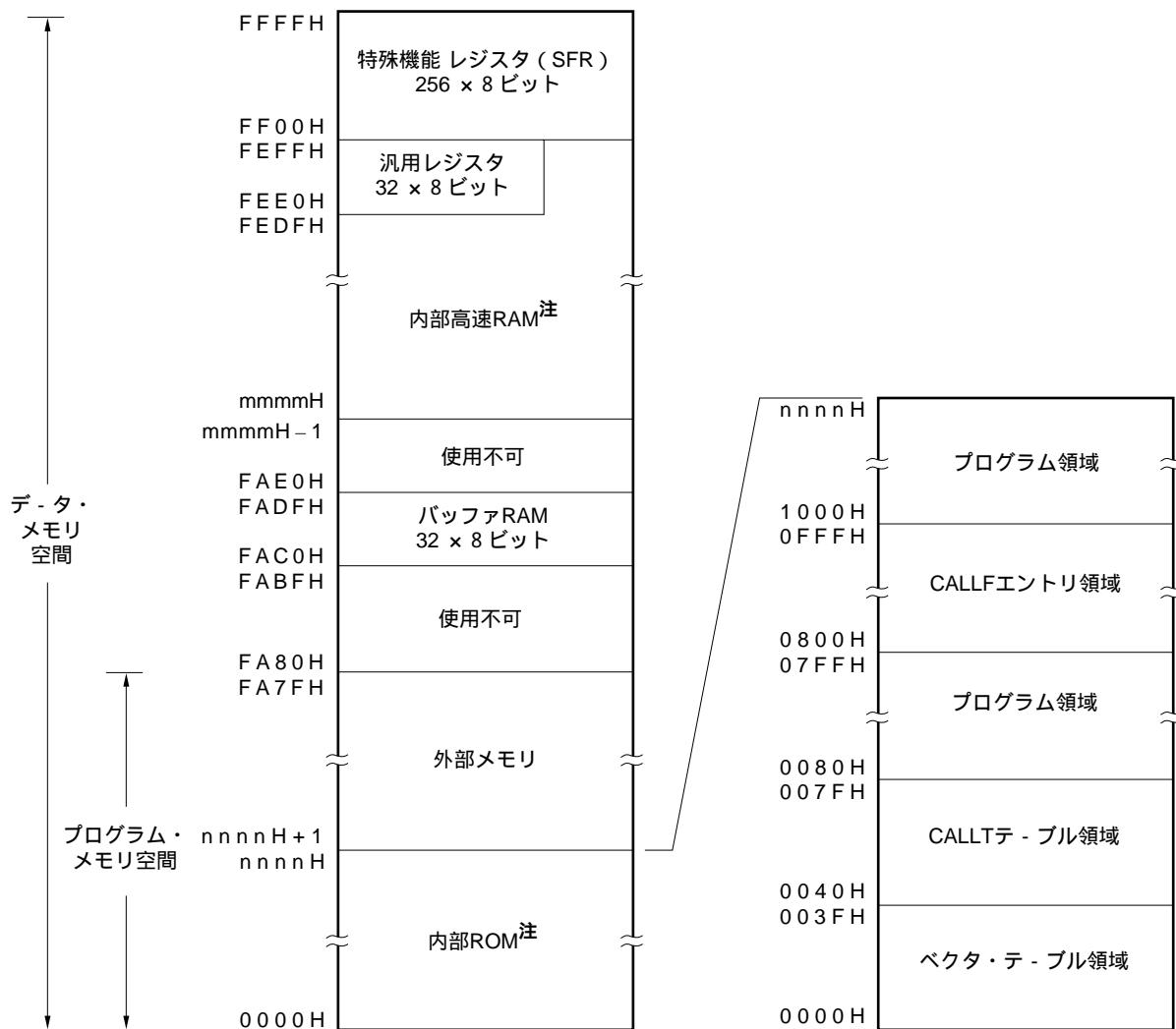

## ★ 4. メモリ空間

図4-1, 図4-2に,  $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018Fのメモリ・マップを示します。

図4-1 メモリ・マップ( $\mu$ PD78011F, 78012F, 78013F, 78014F)

注 内部ROM, 内部高速RAM容量は製品により異なります(下表参照)。

| 品名             | 内部ROM最終アドレス<br>nnnnH | 内部高速RAM先頭アドレス<br>mmmmH |

|----------------|----------------------|------------------------|

| $\mu$ PD78011F | 1FFFH                | FD00H                  |

| $\mu$ PD78012F | 3FFFH                |                        |

| $\mu$ PD78013F | 5FFFH                | FB00H                  |

| $\mu$ PD78014F | 7FFFH                |                        |

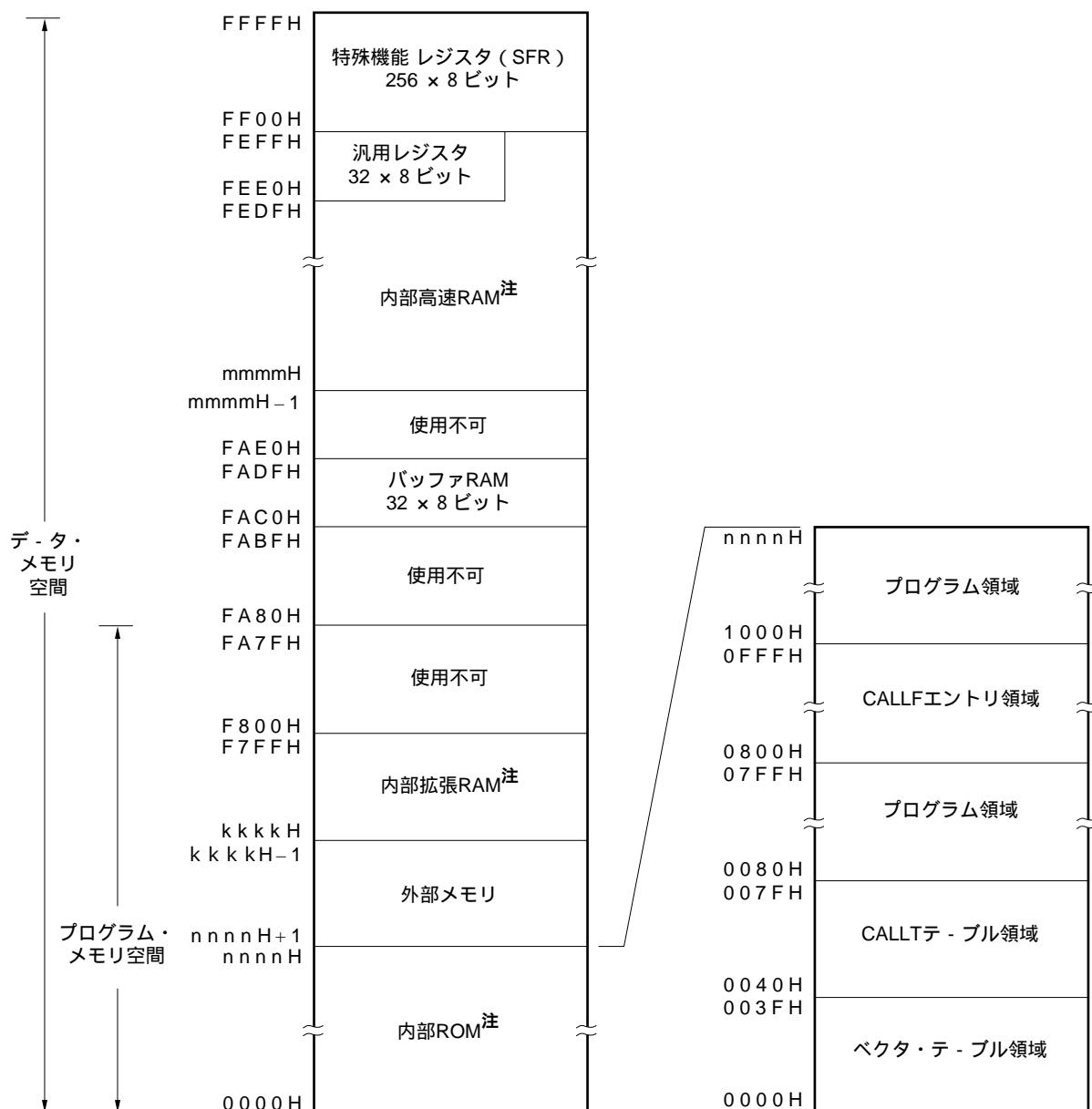

図4-2 メモリ・マップ ( $\mu$ PD78015F, 78016F, 78018F)

**注** 内部ROM, 内部高速RAM, 内部拡張RAM容量は製品により異なります(下表参照)。

| 品名             | 内部ROM最終アドレス<br>nnnnH | 内部高速RAM先頭アドレス<br>mmmmH | 内部拡張RAM先頭アドレス<br>kkkH |

|----------------|----------------------|------------------------|-----------------------|

| $\mu$ PD78015F | 9FFFH                | FB00H                  | F600H                 |

| $\mu$ PD78016F | BFFFH                |                        |                       |

| $\mu$ PD78018F | EFFFH                |                        | F400H                 |

## 5. 周辺ハードウェア機能の特徴

### 5.1 ポート

I/Oポートには次の3種類があります。

- ・CMOS入力 (P00, P04) : 2本

- ・CMOS入出力 (P01-P03, ポート1-ポート5, P64-P67) : 47本

- ・N-chオープン・ドレーン入出力 (15V耐圧) (P60-P63) : 4本

-

- |     |       |

|-----|-------|

| 合 計 | : 53本 |

|-----|-------|

表5-1 ポートの機能

| 名 称  | 端子名称     | 機 能                                                                                                             |

|------|----------|-----------------------------------------------------------------------------------------------------------------|

| ポート0 | P00, P04 | 入力専用ポート。                                                                                                        |

|      | P01-P03  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                         |

| ポート1 | P10-P17  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                         |

| ポート2 | P20-P27  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                         |

| ポート3 | P30-P37  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                         |

| ポート4 | P40-P47  | 入出力ポート。8ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。<br>立ち下がりエッジ検出によりテスト入力フラグ (KRIF) を1にセット。 |

| ポート5 | P50-P57  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。<br>LEDを直接駆動可能。                          |

| ポート6 | P60-P63  | N-chオープン・ドレーン入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>マスク・オプションで、プルアップ抵抗の内蔵可能。<br>LEDを直接駆動可能。                             |

|      | P64-P67  | 入出力ポート。1ビット単位で入力 / 出力の指定可能。<br>入力ポートとして使用する場合、ソフトウェアにより、内蔵プルアップ抵抗を使用可能。                                         |

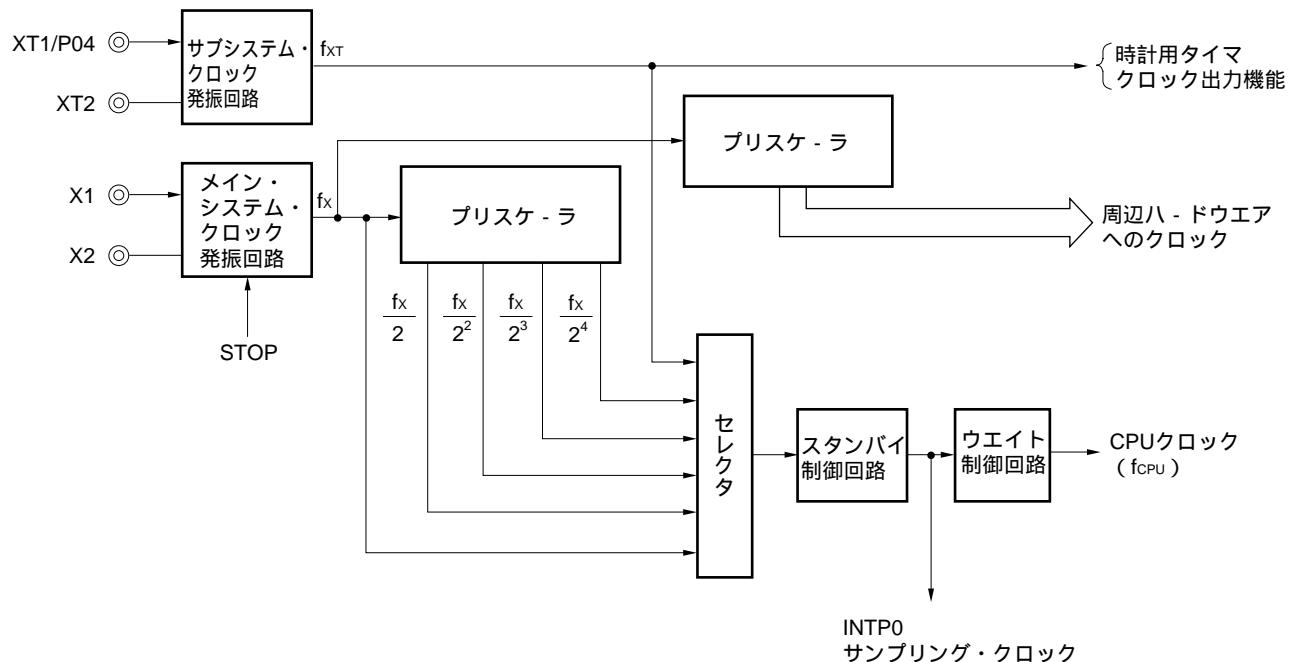

## 5.2 クロック発生回路

メイン・システム・クロックとサブシステム・クロックの2種類の発生回路があります。

また、最小命令実行時間を変化させることができます。

- 0.4  $\mu$ s/0.8  $\mu$ s/1.6  $\mu$ s/3.2  $\mu$ s/6.4  $\mu$ s (メイン・システム・クロック : 10.0 MHz動作時)

- 122  $\mu$ s (サブシステム・クロック : 32.768 kHz動作時)

図5－1 クロック発生回路のブロック図

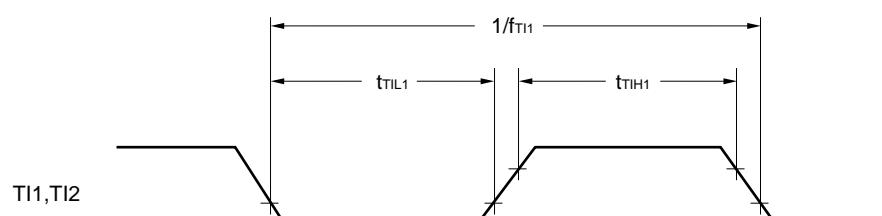

### 5.3 タイマ/イベント・カウンタ

タイマ/イベント・カウンタを5チャネル内蔵しています。

- ・16ビット・タイマ/イベント・カウンタ：1チャネル

- ・8ビット・タイマ/イベント・カウンタ：2チャネル

- ・時計用タイマ：1チャネル

- ・ウォッチドッグ・タイマ：1チャネル

表5-2 タイマ/イベント・カウンタの動作

|     | 16ビット・タイマ/イベント・カウンタ | 8ビット・タイマ/イベント・カウンタ | 時計用タイマ | ウォッチドッグ・タイマ |

|-----|---------------------|--------------------|--------|-------------|

| 動作  | インターバル・タイマ          | 1チャネル              | 2チャネル  | 1チャネル       |

| モード | 外部イベント・カウンタ         | 1チャネル              | 2チャネル  | -           |

| 機能  | タイマ出力               | 1出力                | 2出力    | -           |

|     | PWM出力               | 1出力                | -      | -           |

|     | パルス幅測定              | 1入力                | -      | -           |

|     | 方形波出力               | 1出力                | 2出力    | -           |

|     | 割り込み要求              | 2                  | 2      | 1           |

|     | テスト入力               | -                  | -      | 1入力         |

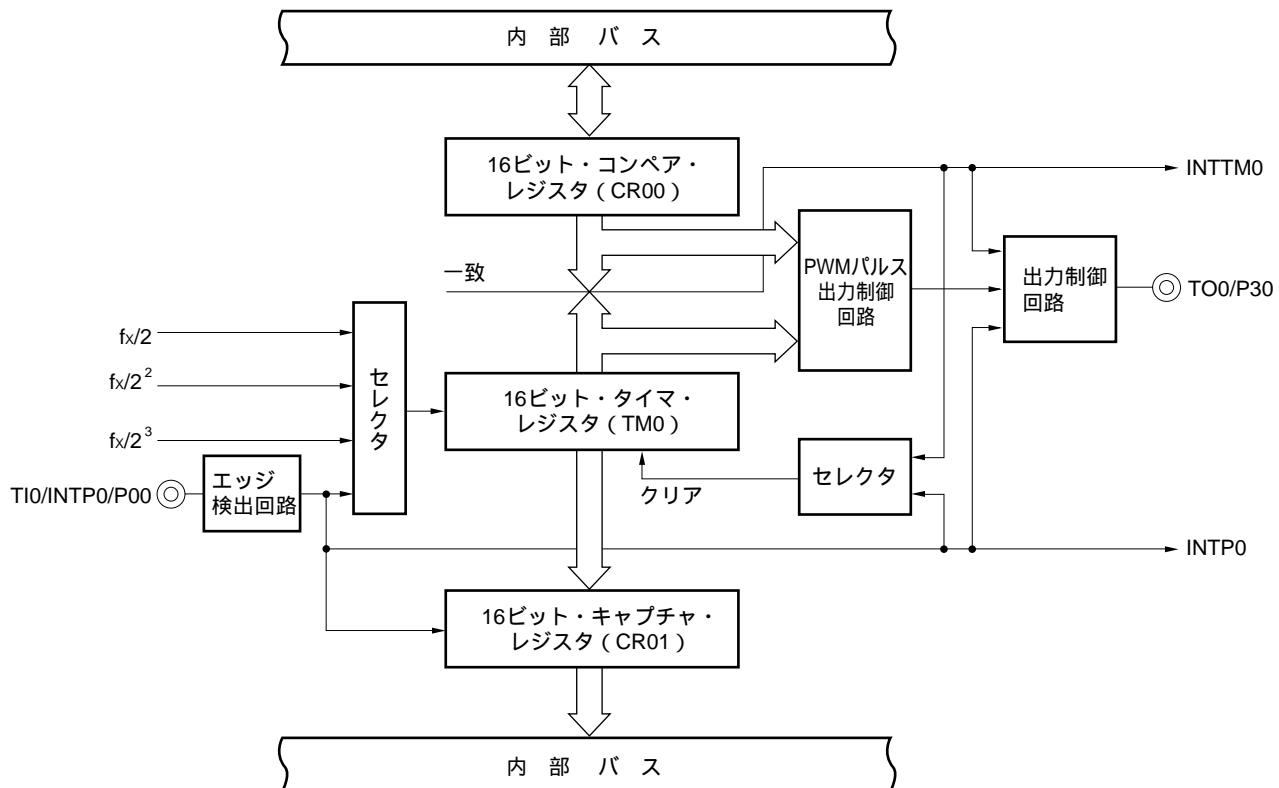

図5-2 16ビット・タイマ/イベント・カウンタのブロック図

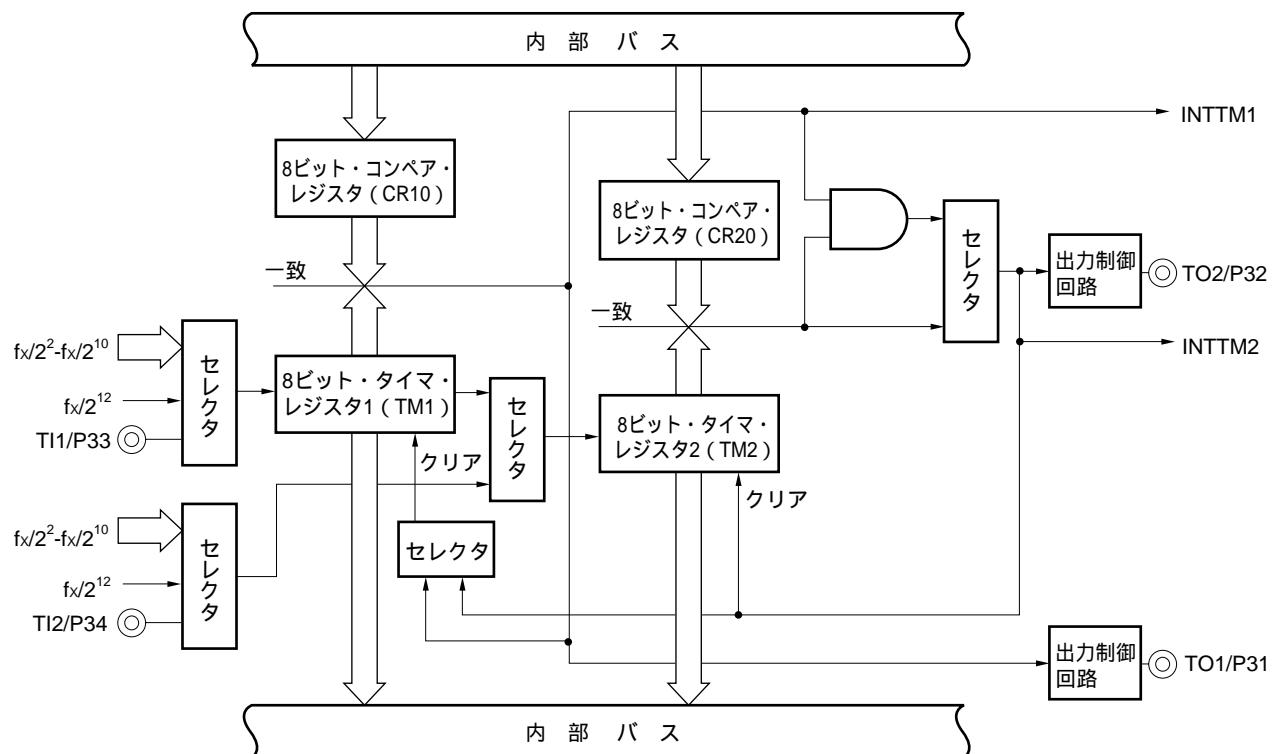

図5-3 8ビット・タイマ/イベント・カウンタのブロック図

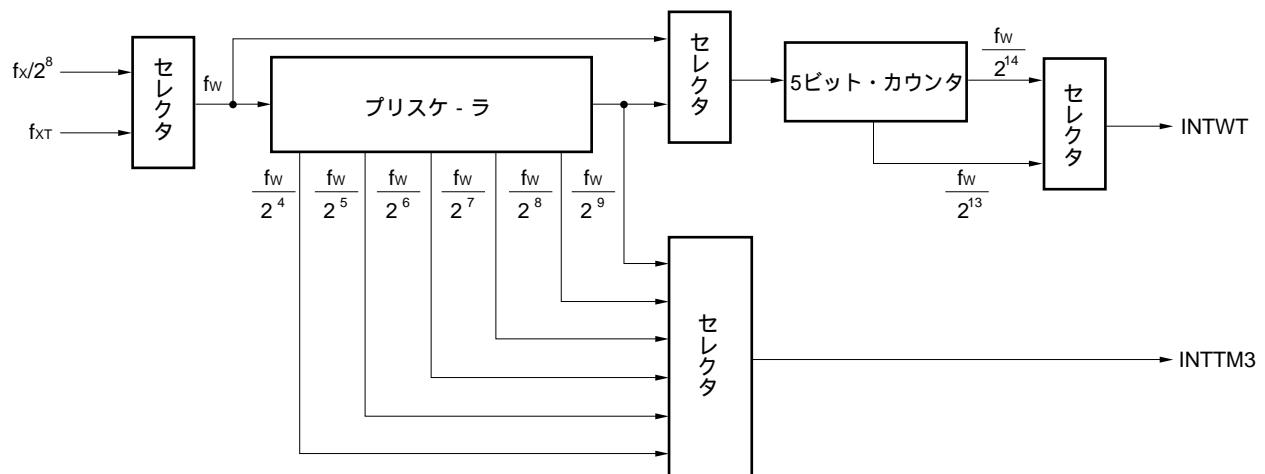

図5-4 時計用タイマのブロック図

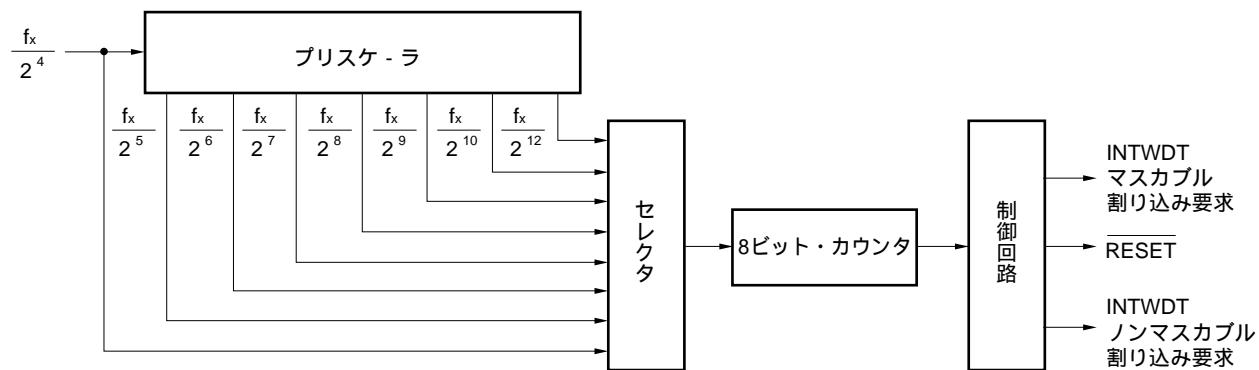

図5-5 ウォッチドッグ・タイマのブロック図

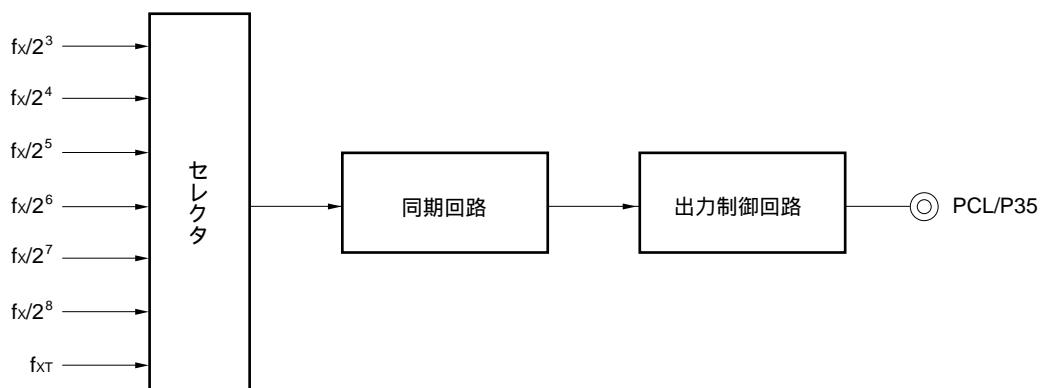

#### 5.4 クロック出力制御回路

クロック出力として次の周波数のクロックを出力できます。

- 39.1 kHz/78.1 kHz/156 kHz/313 kHz/625 kHz/1.25 MHz (メイン・システム・クロック : 10.0 MHz動作時)

- 32.768 kHz (サブシステム・クロック : 32.768 kHz動作時)

図5-6 クロック出力制御回路のブロック図

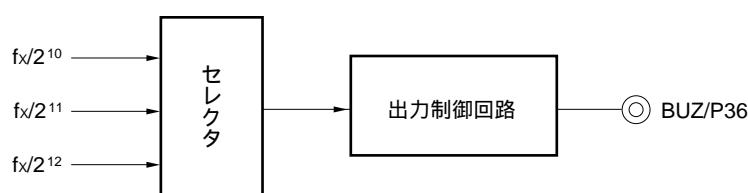

#### 5.5 ブザー出力制御回路

ブザー出力として次の周波数のクロックを出力できます。

- 2.4 kHz/4.9 kHz/9.8 kHz (メイン・システム・クロック : 10.0 MHz動作時)

図5-7 ブザー出力制御回路のブロック図

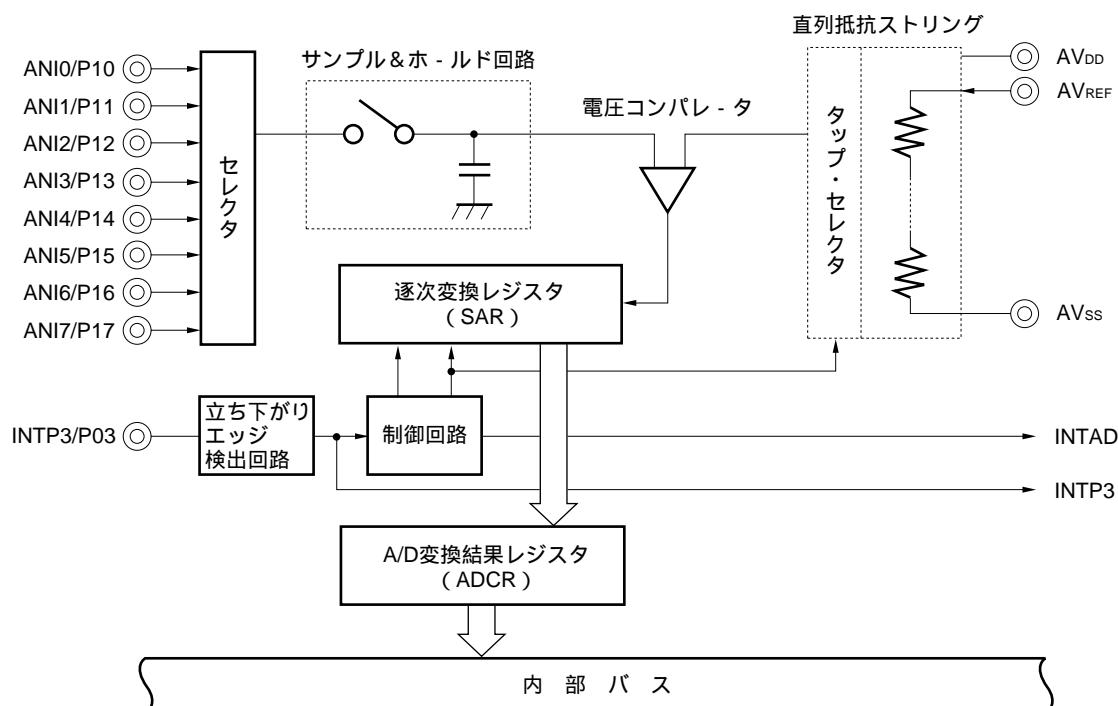

### 5.6 A/Dコンバータ

8ビット分解能8チャネルのA/Dコンバータを内蔵しています。

A/D変換動作の起動方法として次の2種類があります。

- ・ハードウェア・スタート

- ・ソフトウェア・スタート

図5-8 A/Dコンバータのブロック図

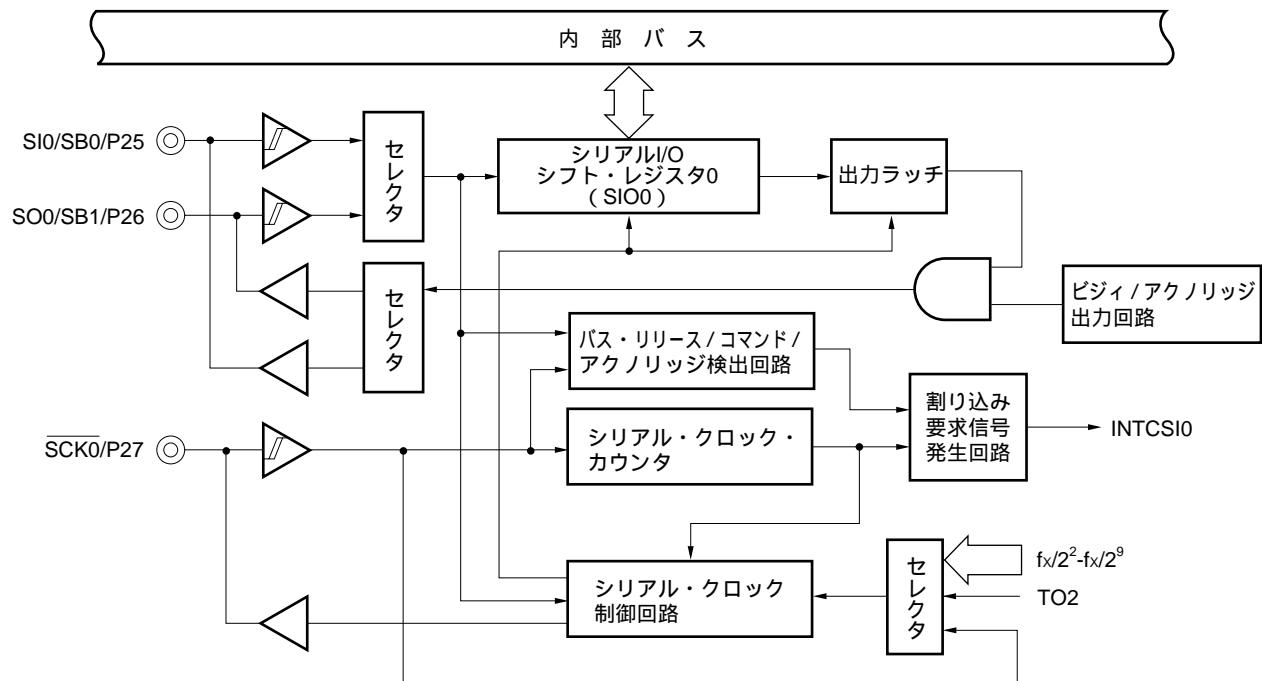

### 5.7 シリアル・インターフェース

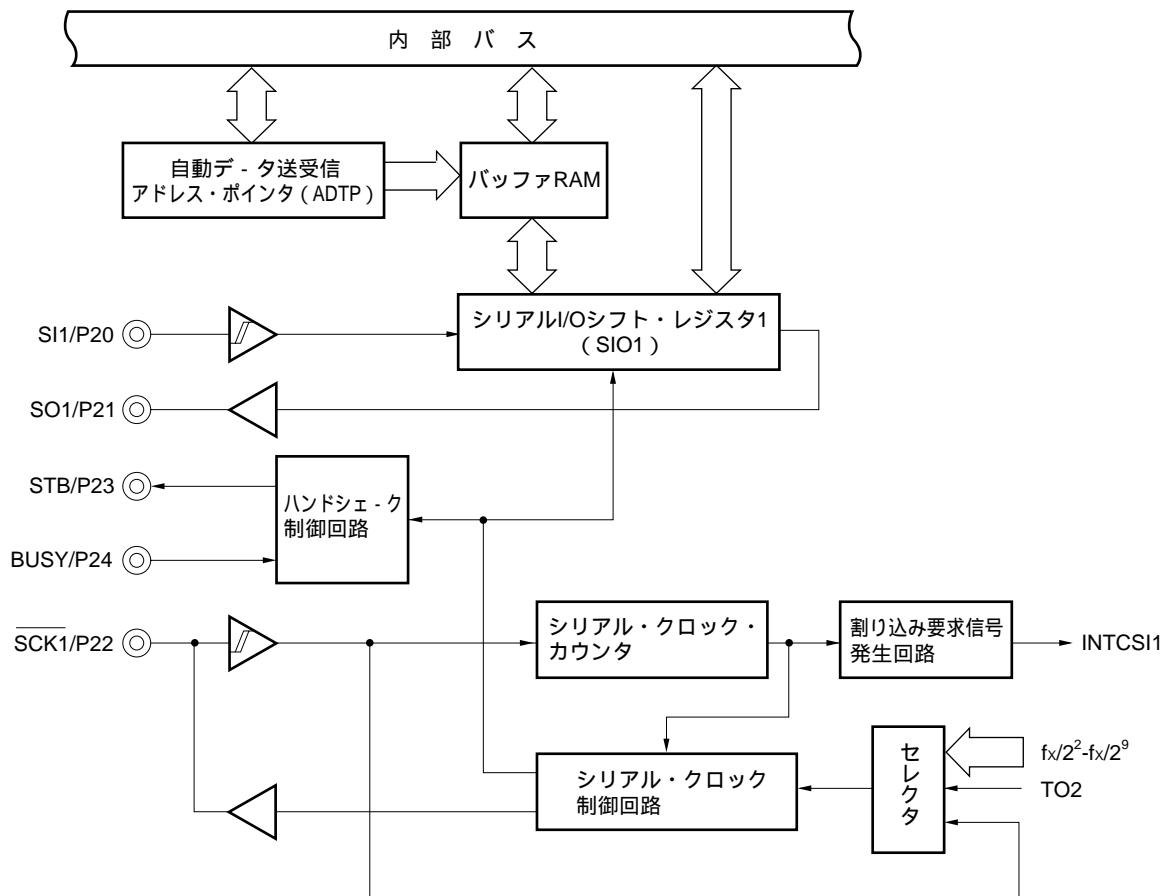

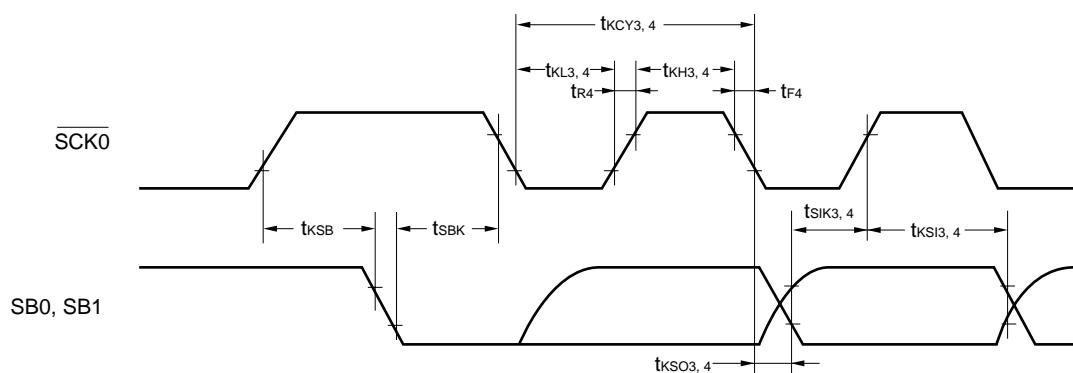

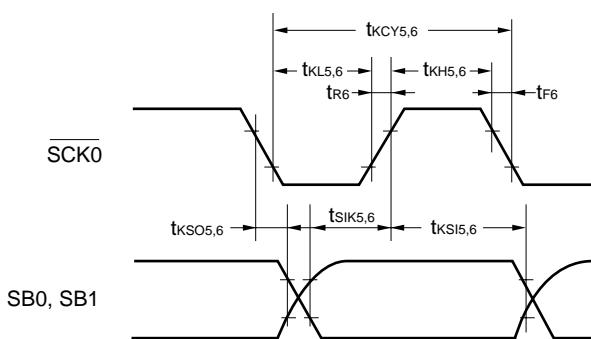

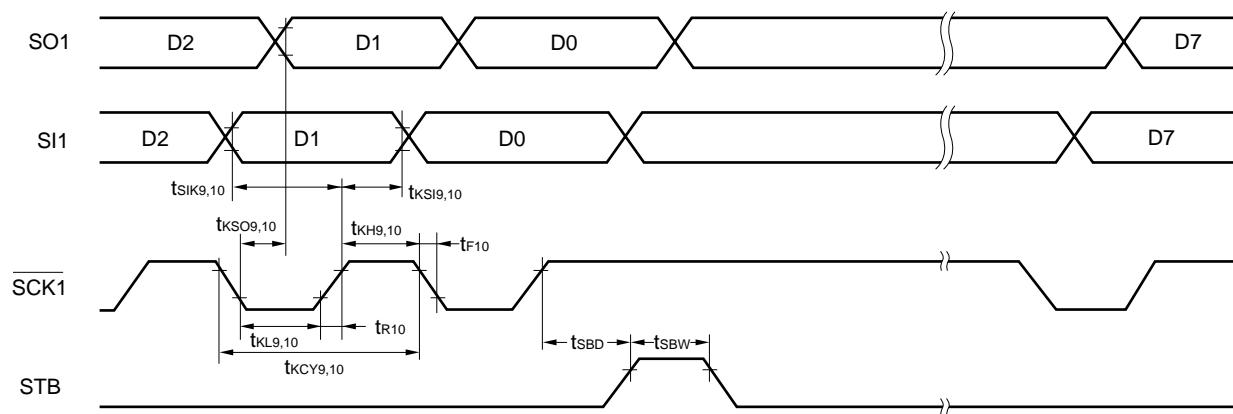

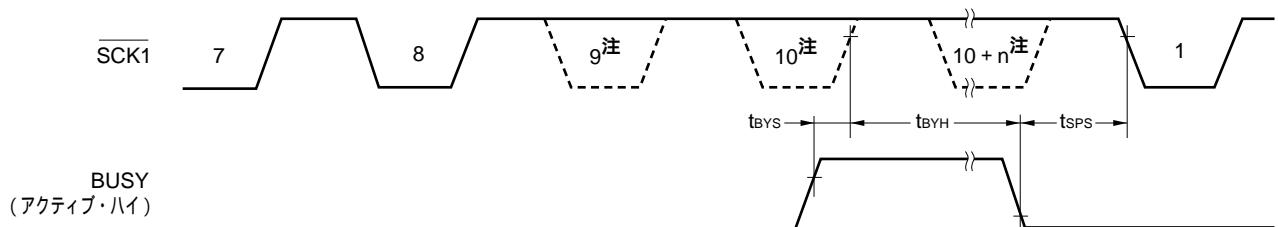

クロック同期式シリアル・インターフェースを2チャネル内蔵しています。

- ・シリアル・インターフェース・チャネル0

- ・シリアル・インターフェース・チャネル1

表5-3 シリアル・インターフェースの種類と機能

| 機能                       | シリアル・インターフェース・チャネル0 | シリアル・インターフェース・チャネル1 |

|--------------------------|---------------------|---------------------|

| 3線式シリアルI/Oモード            | (MSB/LSB先頭切り替え可能)   | (MSB/LSB先頭切り替え可能)   |

| 自動送受信機能付き3線式シリアルI/Oモード   | -                   | (MSB/LSB先頭切り替え可能)   |

| SBI(シリアル・バス・インターフェース)モード | (MSB先頭)             | -                   |

| 2線式シリアルI/Oモード            | (MSB先頭)             | -                   |

保守／廃止

図5-9 シリアル・インターフェース・チャネル0のブロック図

図5-10 シリアル・インターフェース・チャネル1のブロック図

## 6. 割り込み機能とテスト機能

### 6.1 割り込み機能

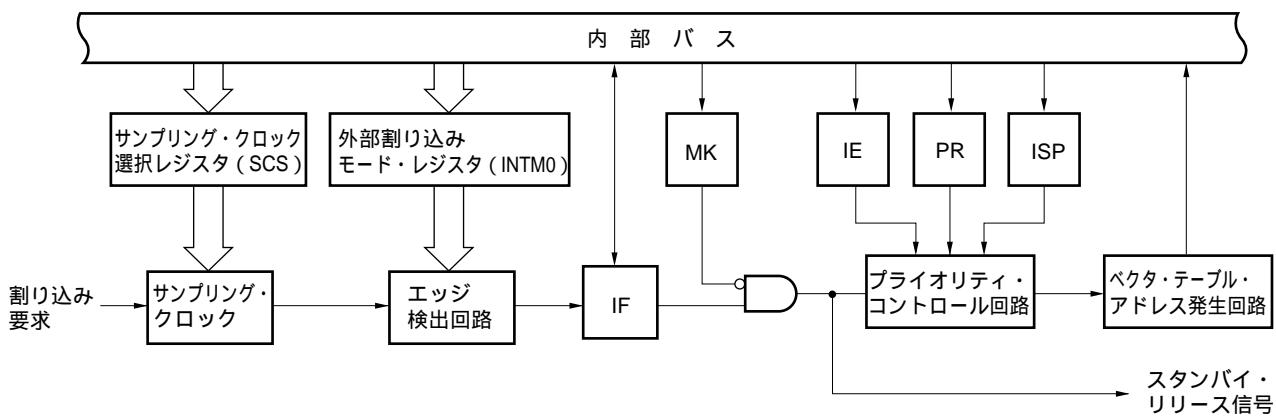

割り込み機能には次に示す3種類、14要因があります。

- ・ノンマスカブル：1

- ・マスカブル：12

- ・ソフトウェア：1

表6-1 割り込み要因一覧

| 割り込み<br>の種類 | 注1<br>ディフォールト・<br>プライオリティ | 割り込み要因  |                                             | 内部 /<br>外部 | ベクタ・<br>テーブル・<br>アドレス | 注2<br>基本構成<br>タイプ |  |

|-------------|---------------------------|---------|---------------------------------------------|------------|-----------------------|-------------------|--|

|             |                           | 名 称     | ト リ ガ                                       |            |                       |                   |  |

| ノンマスカブル     | -                         | INTWDT  | ウォッチドッグ・タイマのオーバフロー<br>(ウォッチドッグ・タイマ・モード1選択時) | 内部         | 0004H                 | (A)               |  |

| マスカブル       | 0                         | INTWDT  | ウォッチドッグ・タイマのオーバフロー<br>(インターバル・タイマ・モード選択時)   | 外部         | 0006H                 | (B)               |  |

|             | 1                         | INTP0   | 端子入力エッジ検出                                   |            | 0008H                 | (C)               |  |

|             | 2                         | INTP1   |                                             |            | 000AH                 | (D)               |  |

|             | 3                         | INTP2   |                                             |            | 000CH                 |                   |  |

|             | 4                         | INTP3   |                                             |            | 000EH                 | (B)               |  |

|             | 5                         | INTCSI0 | シリアル・インターフェース・チャネル0の転送終了                    |            | 0010H                 |                   |  |

|             | 6                         | INTCSI1 | シリアル・インターフェース・チャネル1の転送終了                    |            | 0012H                 |                   |  |

|             | 7                         | INTTM3  | 時計用タイマからの基準時間間隔信号                           |            | 0014H                 |                   |  |

|             | 8                         | INTTM0  | 16ビット・タイマ/イベント・カウンタの一致信号発生                  |            | 0016H                 |                   |  |

|             | 9                         | INTTM1  | 8ビット・タイマ/イベント・カウンタ1の一致信号発生                  |            | 0018H                 |                   |  |

|             | 10                        | INTTM2  | 8ビット・タイマ/イベント・カウンタ2の一致信号発生                  |            | 001AH                 |                   |  |

|             | 11                        | INTAD   | A/Dコンバータの変換終了                               | -          | 003EH                 | (E)               |  |

| ソフトウェア      | -                         | BRK     | BRK命令の実行                                    |            |                       |                   |  |

注1. ディフォールト・プライオリティは、複数のマスカブル割り込み要求が同時に発生している場合に、優先する順位です。0が最高順位、11が最低順位です。

2. 基本構成タイプの(A)～(E)は、それぞれ次頁の(A)～(E)に対応しています。

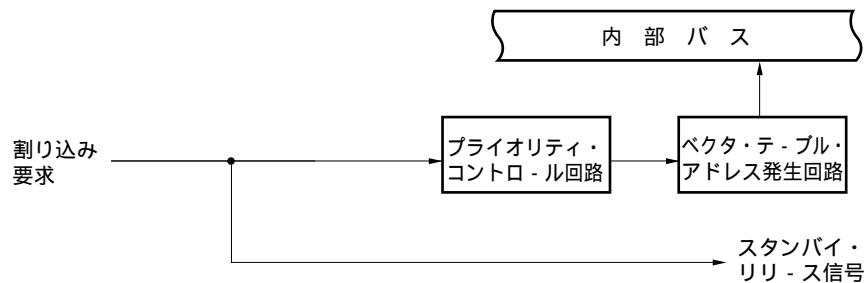

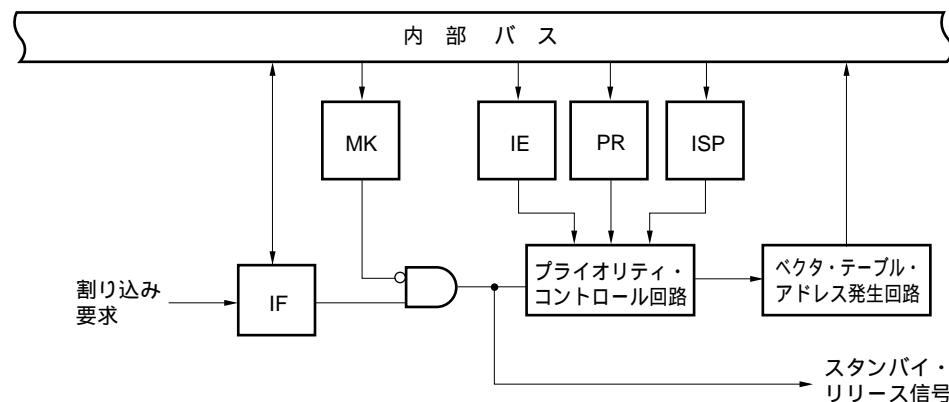

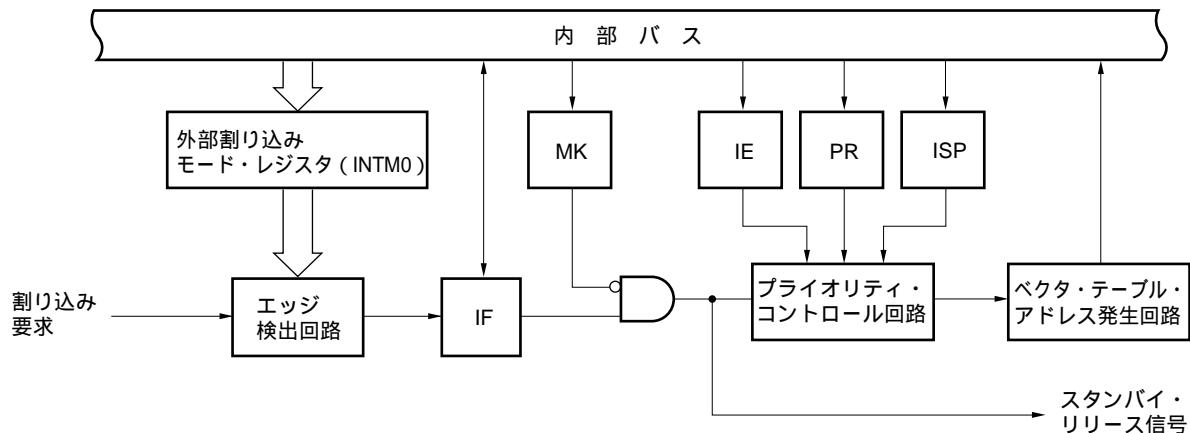

図6-1 割り込み機能の基本構成 (1/2)

## (A) 内部ノンマスカブル割り込み

## (B) 内部マスカブル割り込み

## (C) 外部マスカブル割り込み (INTP0)

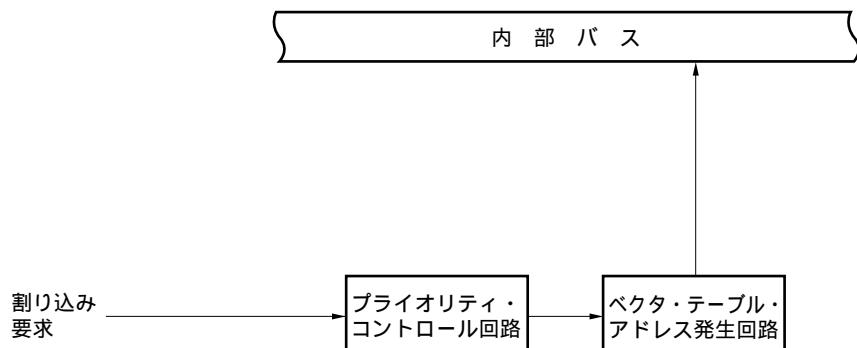

図6-1 割り込み機能の基本構成 (2/2)

## (D) 外部マスカブル割り込み (INTP0を除く)

## (E) ソフトウェア割り込み

IF : 割り込み要求フラグ

IE : 割り込み許可フラグ

ISP : インサービス・プライオリティ・フラグ

MK : 割り込みマスク・フラグ

PR : 優先順位指定フラグ

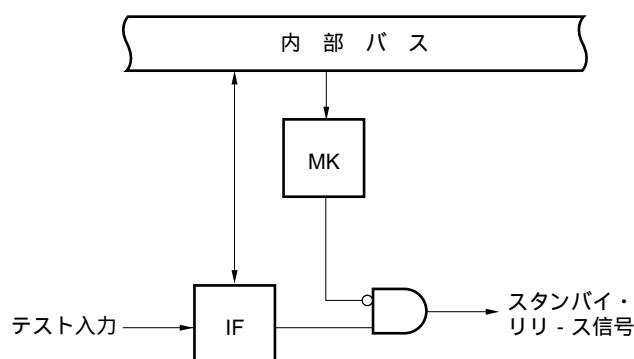

## 6.2 テスト機能

テスト機能には表 6 - 2 に示す 2 本があります。

表 6 - 2 テスト要因一覧

| テス ト 要 因 |                   | 内 部 / 外 部 |

|----------|-------------------|-----------|

| 名 称      | トリ ガ              |           |

| INTWT    | 時計用タイマのオーバフロー     | 内 部       |

| INTPT4   | ポート 4 の立ち下がりエッジ検出 | 外 部       |

図 6 - 2 テスト機能の基本構成

IF : テスト入力フラグ

MK : テスト・マスク・フラグ

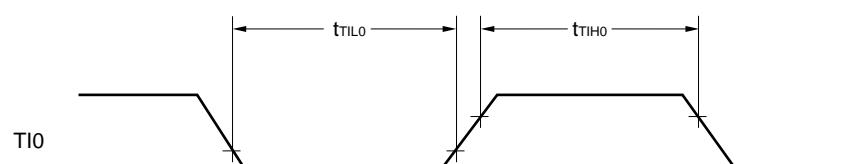

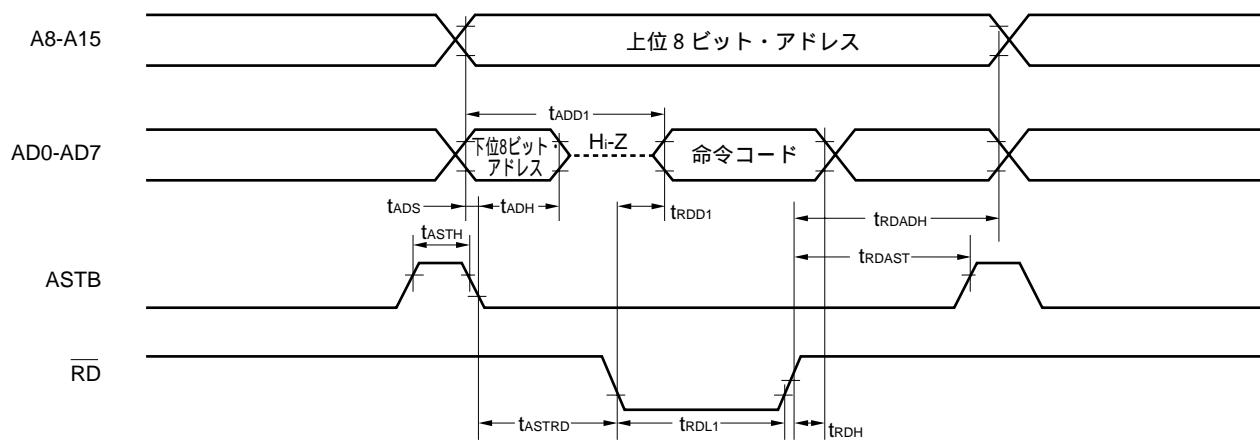

## 7 . 外部デバイス拡張機能

外部デバイス拡張機能は、内部ROM, RAM, SFR以外の領域に外部デバイスを接続する機能です。外部デバイスとの接続にはポート4-ポート6を使用します。

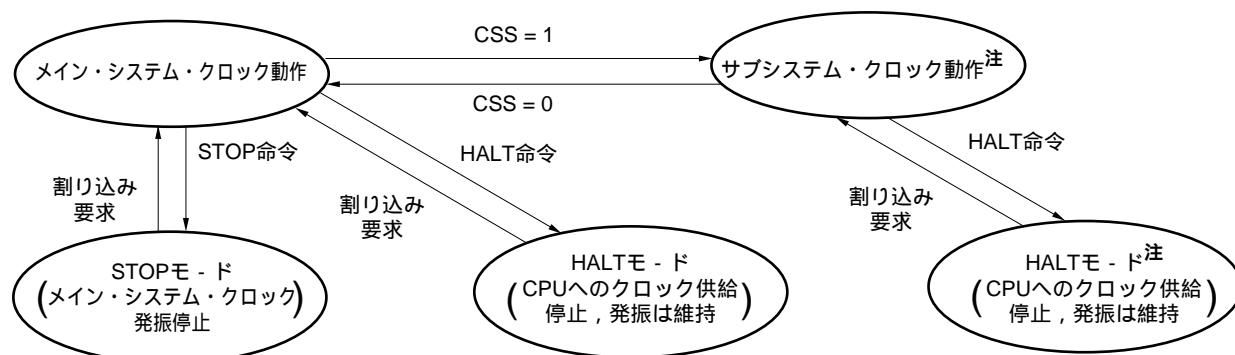

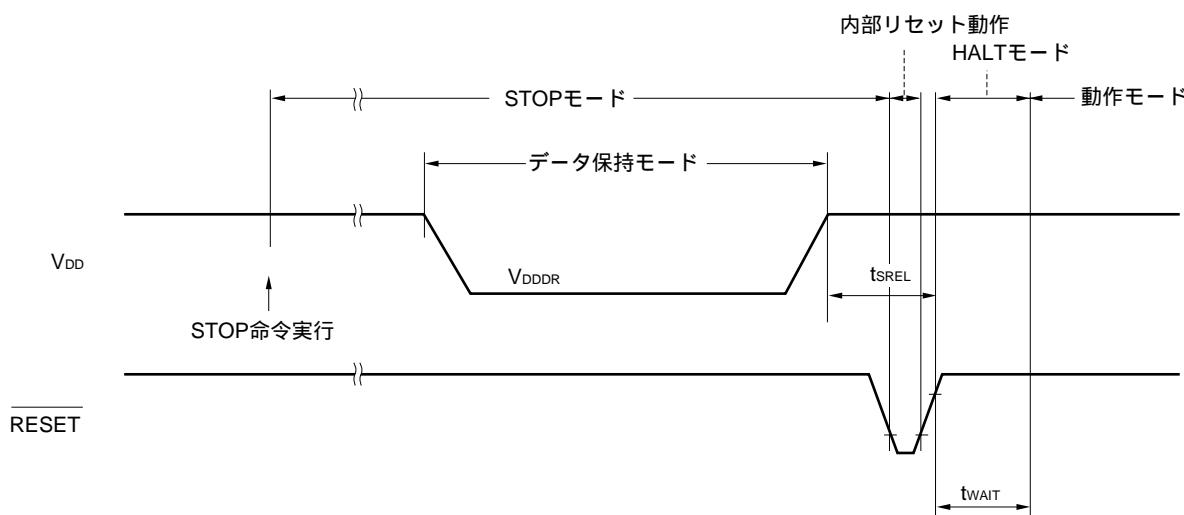

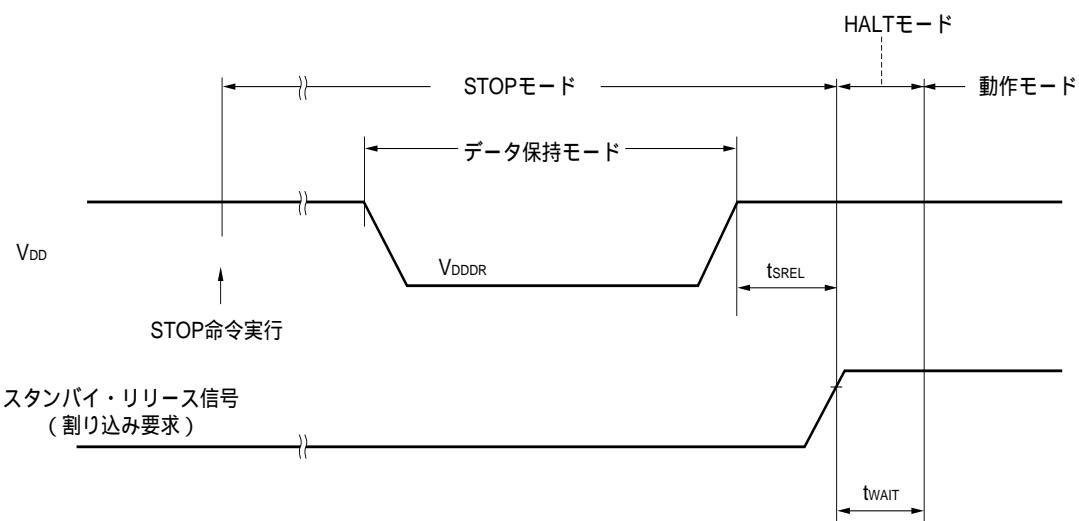

## 8 . スタンバイ機能

スタンバイ機能は、消費電流をより低減するための機能で、次の2種類があります。

- ・HALTモード：CPUの動作クロックを停止させます。通常動作との間欠動作により、平均消費電流を低減できます。

- ・STOPモード：メイン・システム・クロックの発振を停止させます。メイン・システム・クロックによる動作をすべて停止させ、サブシステム・クロックだけの微小消費電力状態にします。

図8-1 スタンバイ機能

<sup>注</sup> メイン・システム・クロックを停止させることにより、消費電流を低減できます。

CPUがサブシステム・クロックで動作しているときは、プロセッサ・クロック・コントロール・レジスタ (PCC) のビット7 (MCC) のセットによってメイン・システム・クロックを停止させてください。STOP命令は使用できません。

**注意** メイン・システム・クロックを停止させサブシステム・クロックで動作させているときに、再度メイン・システム・クロックに切り替える場合には、プログラムで発振安定時間を確保したあとに切り替えてください。

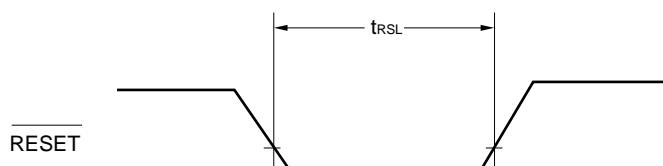

## 9 . リセット機能

次の2種類の方法によってリセットがかかります。

- ・RESET端子による外部リセット

- ・ウォッチドッグ・タイマの暴走時間検出による内部リセット

## 10. 命令セット

## (1) 8ビット命令

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

| 第2オペランド<br>第1オペランド                        | # byte                                                       | A                                                                   | r <sup>注</sup>                                                      | sfr                                                                 | saddr                                                               | !addr16                                                             | PSW                                                                 | [ DE ]                                                              | [ HL ]                                                              | [ HL + byte ]<br>[ HL + B ]<br>[ HL + C ]                           | \$addr16                   | 1            | なし         |

|-------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|--------------|------------|

| A                                         | ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP        | MOV<br>XCH<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | ROR<br>ROL<br>RORC<br>ROLC |              |            |

| r                                         | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP        |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            | INC<br>DEC   |            |

| B, C                                      |                                                              |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     | DBNZ                       |              |            |

| sfr                                       | MOV                                                          | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            |              |            |

| saddr                                     | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     | DBNZ                       |              | INC<br>DEC |

| !addr16                                   |                                                              | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            |              |            |

| PSW                                       | MOV                                                          | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            | PUSH<br>POP  |            |

| [ DE ]                                    |                                                              | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            |              |            |

| [ HL ]                                    |                                                              | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            | ROR4<br>ROL4 |            |

| [ HL + byte ]<br>[ HL + B ]<br>[ HL + C ] |                                                              | MOV                                                                 |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            |              |            |

| X                                         |                                                              |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            | MULU         |            |

| C                                         |                                                              |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                            | DIVUW        |            |

注 r = Aは除く。

## (2) 16ビット命令

MOVW, XCHW, ADDW, SUBW, CMPW, PUSH, POP, INCW, DECW

| 第2オペラント<br>第1オペラント | # word               | AX                | rp <sup>注</sup> | sfrp | saddrp | !addr16 | SP   | なし                      |

|--------------------|----------------------|-------------------|-----------------|------|--------|---------|------|-------------------------|

| AX                 | ADDW<br>SUBW<br>CMPW |                   | MOVW<br>XCHW    | MOVW | MOVW   | MOVW    | MOVW |                         |

| rp                 | MOVW                 | MOVW <sup>注</sup> |                 |      |        |         |      | INCW, DECW<br>PUSH, POP |

| sfrp               | MOVW                 | MOVW              |                 |      |        |         |      |                         |

| saddrp             | MOVW                 | MOVW              |                 |      |        |         |      |                         |

| !addr16            |                      | MOVW              |                 |      |        |         |      |                         |

| SP                 | MOVW                 | MOVW              |                 |      |        |         |      |                         |

注 rp = BC, DE, HLのときのみ。

## (3) ビット操作命令

MOV1, AND1, OR1, XOR1, SET1, CLR1, NOT1, BT, BF, BTCLR

| 第2オペラント<br>第1オペラント | A.bit                       | sfr.bit                     | saddr.bit                   | PSW.bit                     | [HL].bit                    | CY   | \$addr16          | なし                   |

|--------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|-------------------|----------------------|

| A.bit              |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| sfr.bit            |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| saddr.bit          |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| PSW.bit            |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| [HL].bit           |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| CY                 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 |      |                   | SET1<br>CLR1<br>NOT1 |

## (4) コール命令 / 分岐命令

CALL, CALLF, CALLT, BR, BC, BNC, BZ, BNZ, BT, BF, BTCLR, DBNZ

| 第2オペラント<br>第1オペラント | AX | !addr16    | !addr11 | [addr5] | \$addr16                |

|--------------------|----|------------|---------|---------|-------------------------|

| 基本命令               | BR | CALL<br>BR | CALLF   | CALLT   | BR, BC, BNC<br>BZ, BNZ  |

| 複合命令               |    |            |         |         | BT, BF<br>BTCLR<br>DBNZ |

## (5) その他の命令

ADJBA, ADJBS, BRK, RET, RETI, RETB, SEL, NOP, EI, DI, HALT, STOP

## 11. 電気的特性

絶対最大定格 ( $T_A = 25^\circ C$ )

| 項目             | 略号                  | 条件                                                                            | 定格                     | 単位                                  |    |

|----------------|---------------------|-------------------------------------------------------------------------------|------------------------|-------------------------------------|----|

| 電源電圧           | $V_{DD}$            |                                                                               | - 0.3 ~ + 7.0          | V                                   |    |

|                | $AV_{DD}$           |                                                                               | - 0.3 ~ $V_{DD} + 0.3$ | V                                   |    |

|                | $AV_{REF}$          |                                                                               | - 0.3 ~ $V_{DD} + 0.3$ | V                                   |    |

|                | $AV_{SS}$           |                                                                               | - 0.3 ~ + 0.3          | V                                   |    |

| 入力電圧           | $V_{I1}$            | P00-P04, P10-P17, P20-P27, P30-P37,<br>P40-P47, P50-P57, P64-P67, X1, X2, XT2 | - 0.3 ~ $V_{DD} + 0.3$ | V                                   |    |

|                | $V_{I2}$            | P60-P63                                                                       | オーブン・ドレーン              | - 0.3 ~ + 16                        | V  |

| 出力電圧           | $V_O$               |                                                                               | - 0.3 ~ $V_{DD} + 0.3$ | V                                   |    |

| アナログ入力電圧       | $V_{AN}$            | P10-P17                                                                       | アナログ入力端子               | $AV_{SS} - 0.3 \sim AV_{REF} + 0.3$ | V  |

| ハイ・レベル<br>出力電流 | $I_{OH}$            | 1端子                                                                           | - 10                   | mA                                  |    |

|                |                     | P10-P17, P20-P27, P30-P37 合計                                                  | - 15                   | mA                                  |    |

|                |                     | P01-P03, P40-P47, P50-P57, P60-P67 合計                                         | - 15                   | mA                                  |    |

| ロウ・レベル<br>出力電流 | $I_{OL}^{\text{注}}$ | 1端子                                                                           | ピーク値                   | 30                                  | mA |

|                |                     |                                                                               | 実効値                    | 15                                  | mA |

|                |                     | P40-P47, P50-P55                                                              | ピーク値                   | 100                                 | mA |

|                |                     | 合計                                                                            | 実効値                    | 70                                  | mA |

|                |                     | P01-P03, P56, P57, P60-P67                                                    | ピーク値                   | 100                                 | mA |

|                |                     | 合計                                                                            | 実効値                    | 70                                  | mA |

|                |                     | P01-P03, P64-P67                                                              | ピーク値                   | 50                                  | mA |

|                |                     | 合計                                                                            | 実効値                    | 20                                  | mA |

|                |                     | P10-P17, P20-P27, P30-P37                                                     | ピーク値                   | 50                                  | mA |

|                |                     | 合計                                                                            | 実効値                    | 20                                  | mA |

| 動作周囲温度         | $T_A$               |                                                                               | - 40 ~ + 85            |                                     |    |

| 保存温度           | $T_{stg}$           |                                                                               | - 65 ~ + 150           |                                     |    |

注 実効値は [ 実効値 ] = [ ピーク値 ]  $\times \sqrt{\text{デューティ}}$  で計算してください。

注意 各項目のうち 1 項目でも、また一瞬でも絶対最大定格を越えると、製品の品質を損なう恐れがあります。つまり絶対最大定格とは、製品に物理的な損傷を与えるかねない定格値です。必ずこの定格値を越えない状態で、製品をご使用ください。

容量 ( $T_A = 25^\circ C$ ,  $V_{DD} = V_{SS} = 0 V$ )