# SLG47104 Errata Note

# **Abstract**

This document contains the known errata for SLG47104 and the recommended workarounds.

# **Contents**

| 1. | Information      | 1    |

|----|------------------|------|

| 2. | Errata Summary   | 1    |

| 3. | Errata Details   | 2    |

| 4. | Revision History | . 10 |

# 1. Information

| Package(s) | 20-pin STQFN: 2 mm x 3 mm x 0.55 mm, 0.4 mm pitch |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

# 2. Errata Summary

| Issue # | Issue Title                                                                              |

|---------|------------------------------------------------------------------------------------------|

| 1       | Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPH                                |

| 2       | ACMPH Erroneous Behavior when Used with Wake-Sleep Controller for Certain VREF Selection |

| 3       | Abnormal ACMPH Behavior                                                                  |

# 3. Errata Details

# 3.1 Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPH

#### 3.1.1. Effect

**ACMPH**

#### 3.1.2. Conditions

$V_{DD} > 4.6 \text{ V}$ , with hysteresis 32 mV at  $V_{REF}$  range 1.344 V to 2.016 V.

$V_{DD} > 3.6 \text{ V}$ , with hysteresis 32 mV at  $V_{REF}$  range 1.344 V to 1.504 V.

$V_{DD} > 4.6 \text{ V}$ , with hysteresis 64 mV at  $V_{REF}$  range 1.376 V to 1.664 V.

$3.6 \text{ V} < V_{DD} < 4.6 \text{ V}$ , with hysteresis 64 mV only when  $V_{REF}$  is set to 1.376 V.

# 3.1.3. Technical Description

If using ACMPH with 32 mV or 64 mV hysteresis, ACMPH output could be glitching when ACMPH positive input (IN+) is close to the negative input (IN-). It can happen when  $V_{DD}$  is higher than 4.6 V,  $V_{REF}$  is in a range from 1.344 V to 2.016 V for 32 mV hysteresis, and  $V_{REF}$  is in a range from 1.376 V to 1.664 V for 64 mV hysteresis.

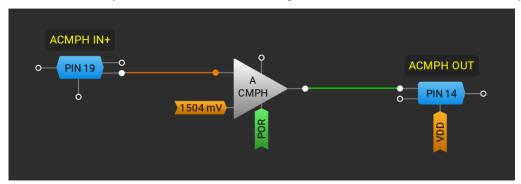

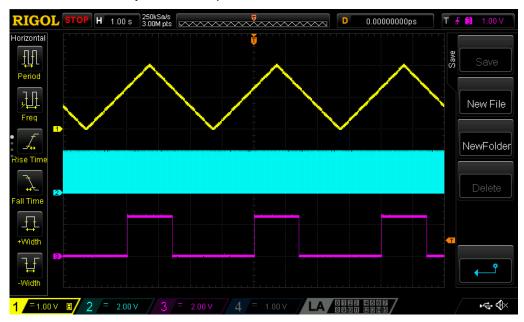

Figure 1. Testing Design

Channel 1 (yellow/top line) - PIN#19 (ACMPH IN+)

Channel 2 (light blue/2nd line) - PIN#14 (ACMPH OUT)

1. Waveform at  $V_{REF} = 1504 \text{ mV}$ , hysteresis is equal to 32 mV.

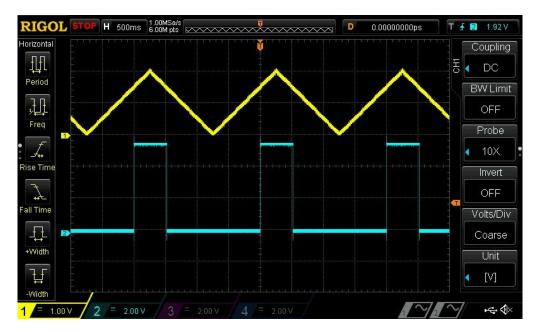

Figure 2. ACMPH Output during Glitching

2. Waveform at  $V_{REF} = 1504$  mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 3. Zoomed ACMPH Output during Glitching

#### 3.1.4. Workaround

Use the deglitch filter connected to the ACMPH output.

Avoid conditions described in paragraph 3.1.2.

Decrease the reference to avoid conditions described in paragraph 3.1.2 at IN- and add the IN+ gain to keep the needed threshold.

# 3.2 ACMPH Erroneous Behavior when Used with Wake-Sleep Controller for Certain VREF Selection

#### 3.2.1. Effect

**ACMPH**

#### 3.2.2. Conditions

ACMPH is used with the macrocell CNT0 configured as a wake-sleep controller (WS Ctrl).

WS Ctrl Short wake time mode is selected, for V<sub>REF</sub> range 1.312 V to 1.440 V.

WS Ctrl Normal wake time is selected, for two V<sub>REF</sub> ranges 0.832 V to 0.896 V and 1.312 V to 1.440 V.

# 3.2.3. Technical Description

When WS Ctrl is used for controlling the power ON/OFF of the analog macrocell ACMP for power saving, ACMPH shows erroneous behavior for certain  $V_{REF}$  selections.  $V_{REF}$  transient settling error is observed for both WS Ctrl Wake time modes, Short wake time, and Normal wake time (selections under CNT0 settings).

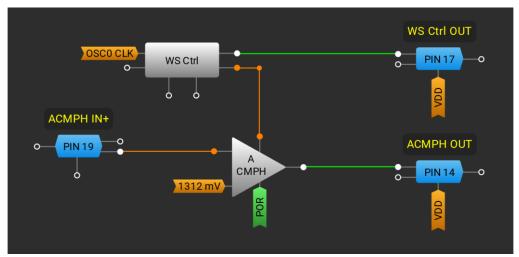

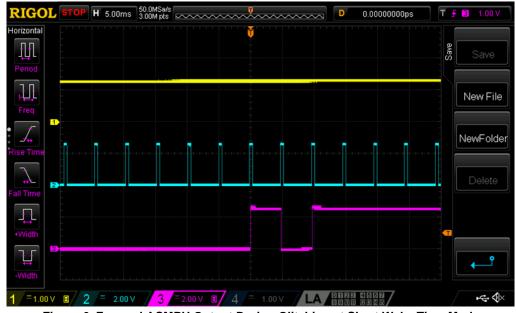

Figure 4. Testing Design

Channel 1 (yellow/top line) - PIN#19 (ACMPH IN+)

Channel 2 (light blue/2nd line) - PIN#17 (WS Ctrl OUT)

Channel 3 (magenta /3rd line) - PIN#14 (ACMPH OUT)

1. Waveform at  $V_{REF} = 1312 \text{ mV}$ , hysteresis is equal to 32 mV.

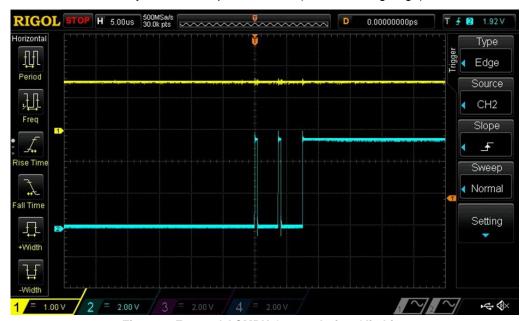

Figure 5. ACMPH Output during Glitching

2. Waveform at Short wake time mode, V<sub>REF</sub> = 1312 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 6. Zoomed ACMPH Output During Glitching at Short Wake Time Mode

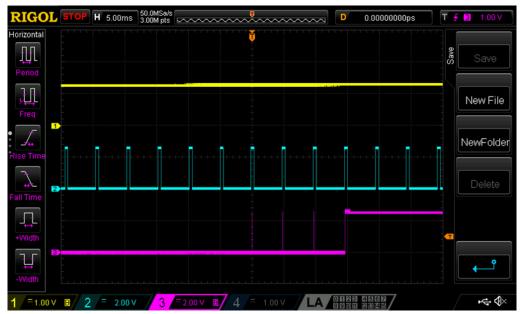

3. Waveform at Normal wake time mode, V<sub>REF</sub> = 1312 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 7. Zoomed ACMPH Output during Glitching at Normal Wake Time Mode

# 3.2.4. Workaround

- 1. If ACMPH is used with WS Ctrl counter, CNT0, avoid conditions described in paragraph 3.2.2.

- 2. Decrease the reference to avoid conditions described in paragraph 3.2.2 at IN- and add the IN+ gain to keep the needed threshold.

#### 3.3 Abnormal ACMPH Behavior

#### 3.3.1. Effect

GPIO5, ACMPH

#### 3.3.2. Conditions

The ACMPH IN+ source is set to VDD and GPIO5 is set to Analog IO or 3-State Output

# 3.3.3. Technical Description

When GPIO5 is configured as "Analog Input/Output", "Digital Input/Output in Analog In Mode", or "3-State Output" mode, ACMPH behavior may be abnormal when the ACMPH IN+ source is set to VDD.

ACMPH has an input MUX which selects the IN+ source for the comparator. The MUX Options are shown in Table 1.

**Table 1. ACMPH Input Options**

| ACMPH IN+ MUX Options |       |

|-----------------------|-------|

| АСМРН                 | GPIO5 |

|                       | VDD   |

In Go Configure GreenPAK design software, the input source is selected by the IN+ source dropdown within the ACMP's properties window. When the input source is selected and ACMP is enabled, the analog switch connects the source to the ACMP's IN+ port.

GPIO5 can be repurposed as Digital IO if the ACMP is disabled or if another input source is selected for the ACMP by the IN+ input MUX. Whenever GPIO5 input mode is configured as an "Analog IO" in accordance with the register definition below, then the ACMP behavior may be abnormal if the ACMP is enabled and connected to another input source.

**Table 2. GPIO5 Input/Output Mode Configurations**

| Byte | Register Bit | Signal Function           | Register Bit Definition                                                                                                |

|------|--------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

|      |              | GPIO5                     |                                                                                                                        |

| 0.04 | 849:848      | Input Mode Configuration  | 00: Digital without Schmitt Trigger 01: Digital with Schmitt Trigger 10: Low Voltage Digital In 11: Analog IO          |

| 0x6A | 851:850      | Output Mode Configuration | 00: Push-Pull 1x / 3-State Output 1x<br>01: Push-Pull 2x / 3-State Output 2x<br>10: Open-Drain 1x<br>11: Open-Drain 2x |

There are 3 standard GPIO5 settings that use the "Analog IO" configuration: Analog input/output, Digital input/output (with "Input mode" set to Analog input), and Digital output (with "Output mode" set to 1x/2x 3-State Output). The first setting is reserved for use with the ACMP, but the other two settings use the "Analog IO" configuration as a high-impedance input.

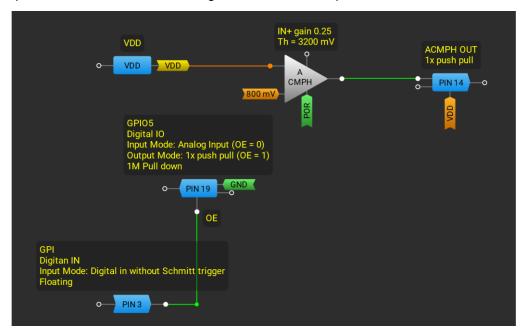

For example, Figure 8 shows the GreenPAK configured with GPIO5 as a Digital Input/Output (with "Input mode" set to Analog input and "Output mode" set to 1x Push Pull) with a 1M pull-down resistor. GPI0 is being used as a digital input and is connected to the OE input of GPIO5. This is used to determine the input/output mode:

- 1. when OE Input is LOW, then GPIO5 is acting as Analog Input.

- 2. when OE Input is HIGH, then GPIO5 is acting as 1x Push Pull Output.

Figure 8. Testing Design

Figure 9 shows that when GPIO5 is in Analog input mode then abnormal ACMPH behavior.

Channel 1 (yellow/top line) - PIN#1 (VDD)

D10 - PIN#3 (GPI)

D11 - PIN#14 (ACMPH OUT)

Figure 9. ACMP Output Behavior

# 3.3.4. Workaround

There is no workaround for this behavior. With this in mind, the GPIO5 should not be used as Digital IO (with "Input mode" set to Analog input) or as digital outputs (with "Output mode" set to 1x/2x 3-State Output) if the ACMPH is enabled and connected to another input source.

# 4. Revision History

| Revision | Date         | Description     |  |

|----------|--------------|-----------------|--|

| 1.00     | Jun 24, 2025 | Initial release |  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.