### **IP License**

## RX (Renesas Extreme) Core

# **Industry-Leading Performance, Power Efficient**32-bit CPU

The proven RX CPU is now available.

Our RX Core IP, widely adopted in high-quality industrial and consumer applications, makes your design easy from FPGA prototyping to SoC development.

#### All the development suite you need is supported.

- RX CPU Subsystem including basic peripherals, interconnect bus and memory interfaces

- Comprehensive Development Environment and Partner Ecosystem of RX family

#### **CPU Subsystem**

- RX CPU Core includes FPU

- MPU/MMU

- **■** Cache

- Memory Interface Instruction, Data memories

- **■** Debug Function

#### **■** Bus System

High-speed Interconnect Bus Peripheral Bus

External Bus Interface (SDRAMC)

#### ■ Peripherals

Timer

(AHB-Lite, APB, Renesas)

Interrupt Controller

**Data Transfer Function**

(DMAC/DTC)

## **Block Diagram**

Bus Master I/F JTAG I/F Type C (Microcontroller, Accelerator) MPU/ DMAC/ ICU Debug **RX CPU** MMU DTC Timer Interconnect Bus SDRAMC CSC Data Instruction Memory Memory Peripheral Bus I/F External Bus I/F

www.renesas.com 2019.12

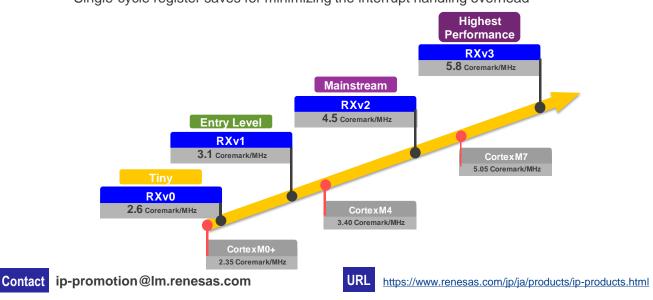

## **RX CPU Sub System Portfolio**

|                                                                                                                           | Type C                                                                                                                               | Type S                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                           | Microcontroller, Accelerator                                                                                                         | Microprocessor                                                                                                           |

| RXv3 Highest Performance                                                                                                  | Instruction Memory                                                                                                                   | Cache                                                                                                                    |

| 5-stage, enhanced superscalar pipeline<br>DSP/Single-precision FPU<br>Single-Cycle register saves<br>Double-precision FPU | <ul> <li>♠ RXv3-CM         Dual-core microcontroller     </li> <li>♠ RXv3-C         High performance microcontroller     </li> </ul> | <ul> <li>♠ RXv3-SM         Multicore microprocessor</li> <li>♠ RXv3-S         High performance microprocessor</li> </ul> |

| RXv2 Mainstream                                                                                                           |                                                                                                                                      |                                                                                                                          |

| 5-stage, superscalar pipeline<br>DSP/Single-precision FPU                                                                 | <ul> <li>RXv2-CM         Dual-core microcontroller     </li> <li>RXv2-C         Mainstream microcontroller     </li> </ul>           | ◆ RXv2-S  Mainstream microprocessor                                                                                      |

| RXv1 Entry Level                                                                                                          |                                                                                                                                      |                                                                                                                          |

| 5-stage, single issue pipeline<br>DSP/Single-precision FPU                                                                | ◆ RXv1-C  Entry-level microcontroller                                                                                                |                                                                                                                          |

| RXv0 Tiny                                                                                                                 |                                                                                                                                      |                                                                                                                          |

| 3-stage, single issue pipeline DSP/Single-precision FPU                                                                   | ◆ RXv0-C Tiny microcontroller                                                                                                        |                                                                                                                          |

## **RX CPU Core**

- Unified Architecture Covering the Small to Large Applications

- Superior Computing Performance and Power Efficiency

- Compact code size by adopting a variable-length instruction set

- Optimized pipeline architecture for industry-leading performance

- Energy-saving cache design to boost energy efficiency

- Unrivaled Digital Signal Processing Performance

- Integrated DSP and FPU as all the core's basic configuration

- Double-precision FPU for easy porting of high precision control models

- DSP/FPU operations and memory accesses simultaneously for high data supply capability

- Fastest Interrupt Response

- Single-cycle register saves for minimizing the interrupt handling overhead