### 8V79S680/8V79S683/RC18016

The 8V79S680 Evaluation Board (EVB) is designed to evaluate the JESD Buffers 8V79S680, 8V79S683 and RC18016. This document describes the following:

- Basic hardware and GUI setup using Renesas IC Toolbox (RICBox™) software

- Board power-up instructions

- Instructions to get active output signals using a provided configuration file

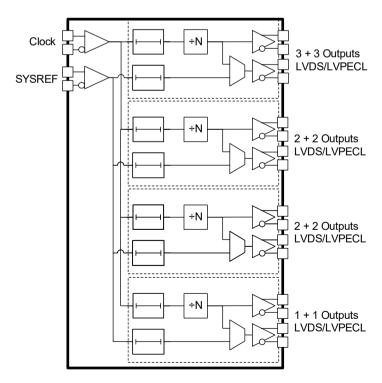

A simplified block diagram for an 8V79S68x device is shown in Figure 1.

#### **Board Contents**

- 8V79S680/8V79S683/RC18016 evaluation board

- EVB manual

- Configuration software (installable plugin for RICBox)

- Configuration example file for device settings

- Board schematic and BOM

#### **Features**

- Distribution, fanout, phase-delay of clock and SYSREF signals

- Four output channels with a total of 16 differential outputs

- CLK/nCLK and REF/nREF inputs can use laboratory signal generator or driven by an RF-PLL Clock and Sysref generator (for example, 8V19N49x-xx Evaluation Board)

- Laboratory power supply connectors

- USB-C power supply

- Serial port for register configuration and register read back

# **Computer Requirements**

- USB 2.0 or USB 3.0 interface

- Processor: minimum 1GHz

- Memory: minimum 512MB; recommended 1GB

- Available disk space: minimum 600MB (1.5GB 64bit); recommended 1GB (2GB 64-bit)

Figure 1. 8V79S68x Simplified Block Diagram

# **Contents**

| 1.   | Functional Description           |                                                           |    |  |  |  |

|------|----------------------------------|-----------------------------------------------------------|----|--|--|--|

|      | 1.1 Hardw                        | vare Setup and Configuration                              | 3  |  |  |  |

|      | 1.1.1.                           | Power and USB-C Connections to Computer Host              | 5  |  |  |  |

|      | 1.1.2.                           | Clock Inputs (CLK/nCLK) and SysRef Input (REF/nREF)       | 6  |  |  |  |

|      | 1.1.3.                           | Clock (QCLKx) and Sysref (QREFx) Outputs                  | 8  |  |  |  |

|      | 1.1.4.                           | Serial Connection                                         | 9  |  |  |  |

| 2.   | Software Setup and Configuration |                                                           |    |  |  |  |

|      | 2.1.1.                           | Prepare the Software                                      | 10 |  |  |  |

|      | 2.1.2.                           | Launch the GUI                                            | 10 |  |  |  |

|      | 2.1.3.                           | Configure the Evaluation Board                            | 15 |  |  |  |

| 3.   | Board Desig                      | gn                                                        | 17 |  |  |  |

| 4.   | Ordering Inf                     | formation                                                 | 19 |  |  |  |

| 5.   | Revision His                     | story                                                     | 19 |  |  |  |

|      |                                  |                                                           |    |  |  |  |

| Fi   | gures                            |                                                           |    |  |  |  |

| Figu | ure 1. 8V79S6                    | 8x Simplified Block Diagram                               | 1  |  |  |  |

| Figu | ure 2. Evaluati                  | on Board – General Setup                                  | 4  |  |  |  |

| Figu | ure 3. USB Po                    | wer/External Power Select Jumpers J49                     | 5  |  |  |  |

| Figu | ıre 4. USB Po                    | wer/External Power Select Jumpers J48                     | 6  |  |  |  |

| Figu | ure 5. Externa                   | I 5V Board Input                                          | 6  |  |  |  |

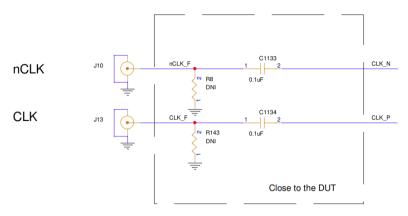

| Figu | ure 6. Input AC                  | C Coupling                                                | 7  |  |  |  |

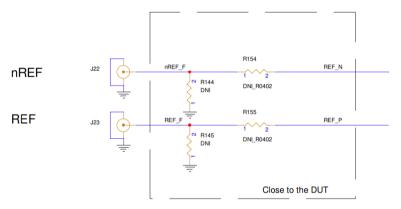

| Figu | ure 7. Input D0                  | C Coupling                                                | 7  |  |  |  |

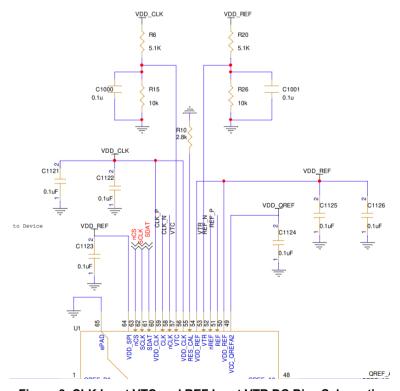

| Figu | ıre 8. CLK Inp                   | out VTC and REF Input VTR DC Bias Schematic               | 7  |  |  |  |

| Figu | ure 9. CLK/nC                    | LK and REF/nREF Input Signal Requirements                 | 8  |  |  |  |

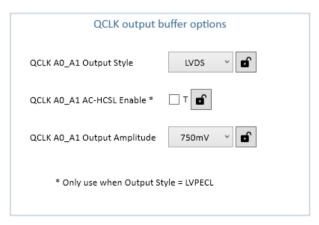

| Figu | ure 10. Output                   | Type Options                                              | 8  |  |  |  |

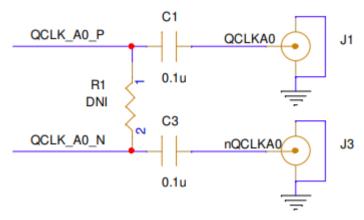

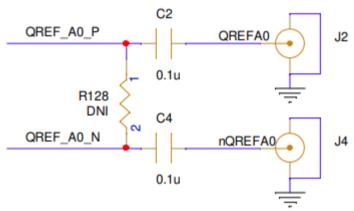

| Figu | ure 11. Output                   | Clock AC-Coupling                                         | 9  |  |  |  |

| Figu | ure 12. Output                   | QREFx AC-Coupling                                         | 9  |  |  |  |

| Figu | ure 13. Create                   | New Project in RICBox                                     | 10 |  |  |  |

| Figu | ure 14. Selecti                  | ng 8V79S683 Device GUI in RICBox                          | 10 |  |  |  |

| Figu | ure 15. RICBo                    | x GUI Menu Buttons                                        | 11 |  |  |  |

| Figu | ure 16. CLK/no                   | CLK (Clock) and REF/nREF (Sysref) Input Frequency Setting | 12 |  |  |  |

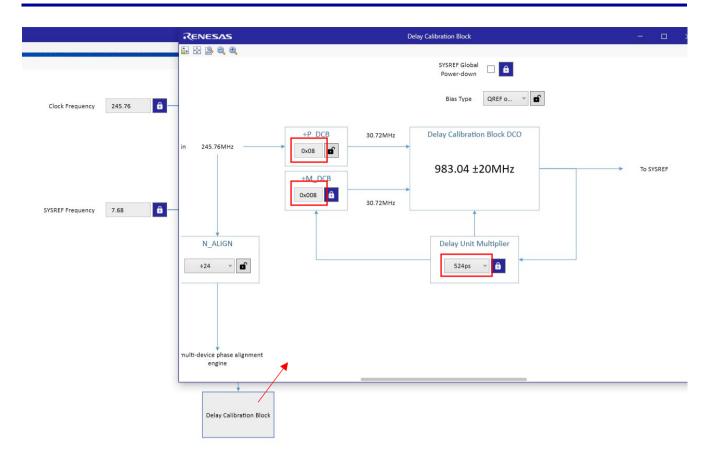

| Figu | ure 17. Delay (                  | Calibration Block                                         | 13 |  |  |  |

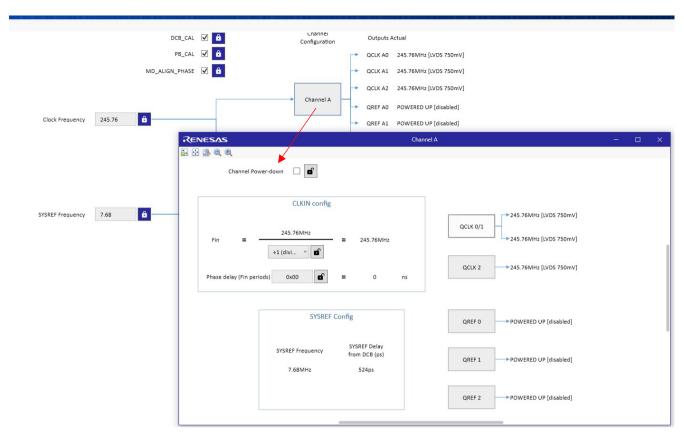

| Figu | ure 18. Activat                  | e DCB_CAL and Check DAC_CODE Value                        | 13 |  |  |  |

| Figu | ure 19. Output                   | Channel Frequency and Phase Delay Setting                 | 14 |  |  |  |

| Figu | ure 20. QCLK                     | COutput Driver Type and Amplitude Setting                 | 14 |  |  |  |

| Figu | ure 21. QREF                     | x Output Driver Type and Phase Delay Setting              | 15 |  |  |  |

| Figu | ure 22. Conne                    | ct to the Device in RICBox                                | 15 |  |  |  |

| _    |                                  | cted Button                                               |    |  |  |  |

| Figu | ure 24. Progra                   | m Button                                                  | 16 |  |  |  |

| Figu | ure 25. 8V79S                    | 680/8V79S683/RC18016 Evaluation Board (top)               | 17 |  |  |  |

| Figu | ure 26. 8V79S                    | 680/8V79S683/RC18016 Evaluation Board (bottom)            | 18 |  |  |  |

# 1. Functional Description

The evaluation kit is used for demonstrating the 8V79S680, 8V79S683 and RC18016, an integrated, clock and JESD204B SYSREF signal fanout buffer for JESD204B/C applications. The kit can be used to evaluate major parameters including phase noise, clock frequency, output skew, phase alignment, device timing, and the signal waveform. The device on the board accepts any input frequency up to 3GHz for clock input. The device under test distributes the input clock (CLK/nCLK) and JESD204B SYSREF signals (REF/nREF) to four fanout channels. Input clock signals can be frequency divided and are fanned-out to multiple clock (QCLKx) and SYSREF (QREFx) outputs. Configurable phase-delay circuits are available for both clock and SYSREF signals. The propagation delays in all signal paths are fully deterministic to support fixed phase relationships between clock and SYSREF signals within one device.

The board is equipped with on-board LDOs that require a 5V supply. If connecting to a USB C interface, the evaluation board may be powered directly from the USB 3.0 connection. The board is designed to operate over the industrial temperature range from -40°C to +85°C, ambient temperature.

It is recommended to use proper grounding during board operations to avoid ESD damage to the EVB.

## 1.1 Hardware Setup and Configuration

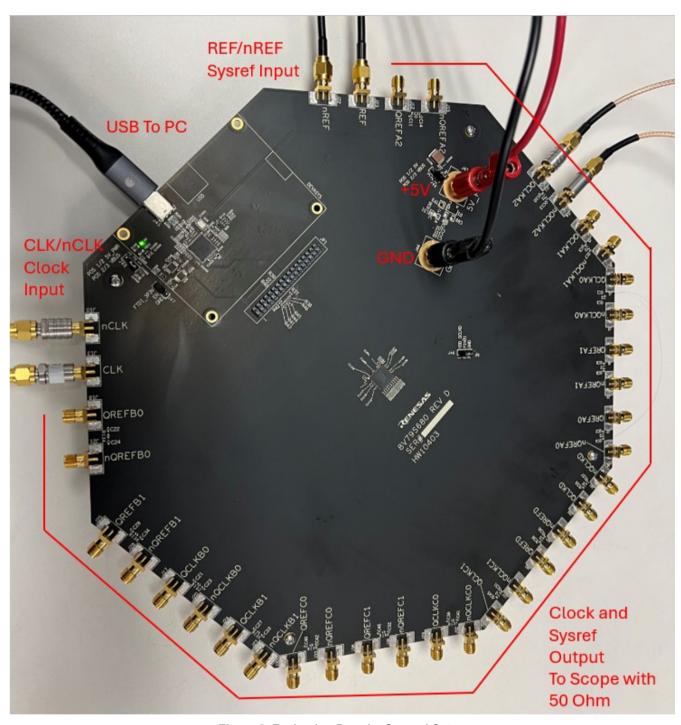

The following sections describe the crystal, input clock, serial, and output and power functions used for setting up device testing. The setup example is shown in Figure 2.

#### SPI Interface

SPI 3-wire interface in this example.

#### Power Supply

Use 5V from a Power Supply or USB 3.0 with on-board LDO to generate 3.3V power rail. See Figure 3 for power select jumper settings.

#### CLKx Inputs

The CLK/nCLK inputs can be AC-coupled or DC coupling and can accept differential input.

Assume the signal source (for example, lab equipment requires  $50\Omega$  to GND termination at the receiver); the **CLK/nCLK** inputs have on-chip terminations of  $50\Omega$  to VTC DC bias with AC-coupling.

**REF/nREF** is SYSREF differential signal DC coupling with on chip termination.

#### Outputs

The outputs are AC-coupled without on-board pull-down or pull-up resistors.

Figure 2. Evaluation Board – General Setup

### 1.1.1. Power and USB-C Connections to Computer Host

The EVB is connected to a computer host via the USB3.0 to USB-C cable. It is recommended that the cable is connected to a USB3.0 port. However, a USB2.0 port is acceptable for the DUT (8V79S680, 8V79S683 and RC18016) to SPI communications only. The USB 3.0 or external power supply provides +5V as power source to the on-board regulators. The on-board regulators support 3.3V voltages to the EVB.

The DUT voltage source is derived from the on-board voltage regulators for 3.3V. The USB connection will still be required to connect to RICBox.

- Power Connection:

- Set the power supply voltage to +5V and the current limit to 1A

- +5V (J43) = +5V

- GND (J44) = GND

- Expected Current Draw:

- ~ 0.7 to ~0.8A for 8V79S683 and RC18016

- ~0.3A to 0.4A for 8V79S680

- After programming the device, the current can be varied ~0.3A to ~1A during normal operation (device configuration dependent)

#### 1.1.1.1. Power the Device with USB Connection

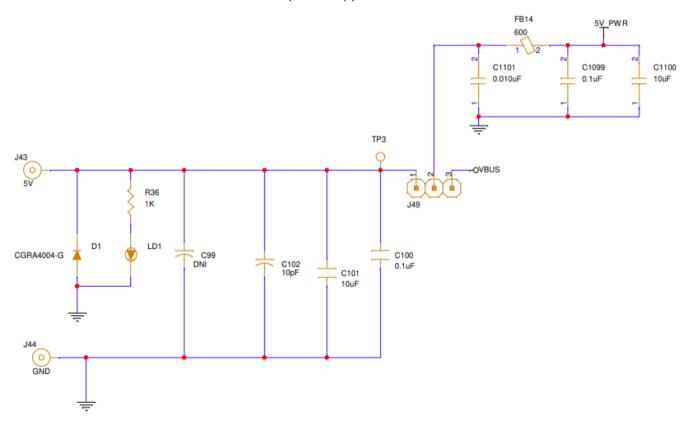

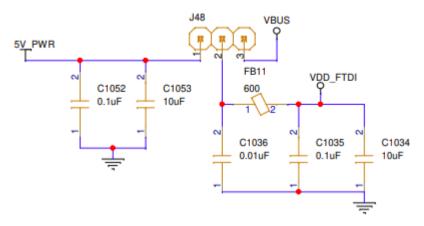

- Jumper J49 and J48 is used for selecting a +5V power supply from an external power supply or from USB 3.0.

Figure 3 and Figure 4 show the schematics of jumper J49 and J48.

- Set jumper on J49 between pins 2 and 3

- Set jumper on J48 between pin 2 and 3

- Ensure that the EVB connects to a USB 3.0 (or newer) port

Figure 3. USB Power/External Power Select Jumpers J49

Figure 4. USB Power/External Power Select Jumpers J48

#### 1.1.1.2. Power the Device with External Power Supply Connection and On-board Voltage Regulators

- Set jumper on J49 between pins 1 and 2

- Set jumper on J48 between pins 1 and 2

- Ensure 5V at banana jack J43 (5V) and J44 (GND) connection

Figure 5. External 5V Board Input

Note: Allow for up to 1A of current with direct power supply.

## 1.1.2. Clock Inputs (CLK/nCLK) and SysRef Input (REF/nREF)

The Clock input CLK/nCLK and Sysref input REF/nREF can accept differential signals. The input can be AC coupling or DC coupling as shown in Figure 6 and Figure 7. For AC coupling, the DUT has built-in  $50\Omega$  to VTC and VTR. The board provides DC bias to VTC/VTR pin as shown in Figure 8.

Figure 6. Input AC Coupling

Figure 7. Input DC Coupling

Figure 8. CLK Input VTC and REF Input VTR DC Bias Schematic

The input signal requirement for CLK/nCLK and REF/nREF is provided in the datasheet and is shown in Figure 9. For DC coupling, both amplitude (VIN or VDIFF\_IN) and DC offset (VCMR) requirement need to be met. For AC coupling, the DC offset is handled by on-board DC re-bias. Only the input amplitude requirement needs to be met.

| W                | put voltage                                               | CLK, nCLK<br>REF, nREF | 0.15 | - | 1.2                                       | V |

|------------------|-----------------------------------------------------------|------------------------|------|---|-------------------------------------------|---|

| VDIFF IN         | Differential Input<br>Voltage<br>Amplitude <sup>d e</sup> | CLK, nCLK<br>REF, nREF | 0.3  | - | 2.4                                       | V |

| V <sub>CMR</sub> | Common Mode Input Voltage                                 |                        | 1    | - | V <sub>DD_V</sub> - (V <sub>IN</sub> / 2) | V |

Figure 9. CLK/nCLK and REF/nREF Input Signal Requirements

### 1.1.3. Clock (QCLKx) and Sysref (QREFx) Outputs

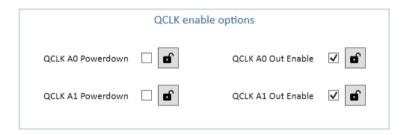

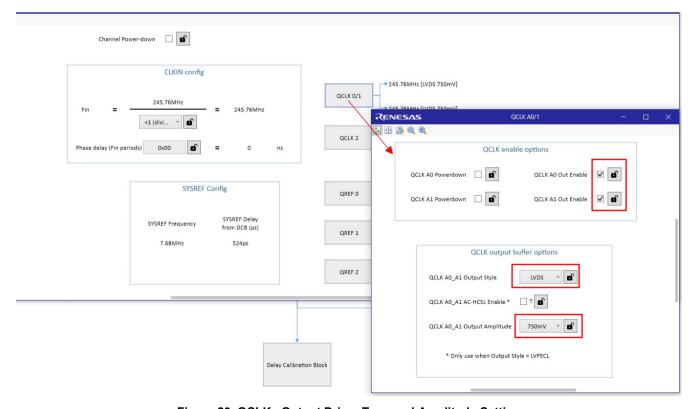

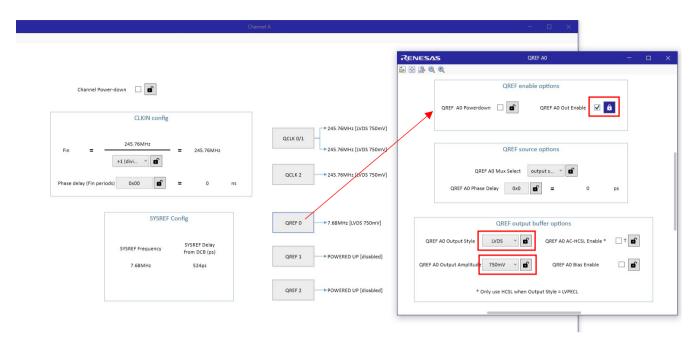

The 8V79S680, 8V79S683 and RC18016 differential output pairs can be programmed to LVDS or LVPECL logic type as shown in Figure 10. In addition, RC18016 output pairs can also be programmed to AC-HCSL.

- The board's output pairs, by default, are AC-coupling as shown in Figure 11 and Figure 12.

- The LVPECL and AC-HCSL driver requires DC current path to switch. This board does not have pull-down resistors before AC-coupling to provide DC current path, therefore LVPECL and AC-HCSL driver cannot be used in this board as is.

- For an LVDS driver, the output will switch without board level termination. After the onboard AC-coupling, it only requires 50Ω termination to GND at the monitor equipment.

- LVDS outputs can be configured to 350mV or 750mV swing.

- Each output can also be disabled when not used.

Figure 10. Output Type Options

Figure 11. Output Clock AC-Coupling

Figure 12. Output QREFx AC-Coupling

## 1.1.4. Serial Connection

The EVB can be connected to a computer via a USB3.0 to USB-C connector J45. The on-board USB-to-MPSSE Bridge (FTDI FT232HQ) handles the data communication. The bus will be 3-wire SPI.

# 2. Software Setup and Configuration

#### 2.1.1. Prepare the Software

For software installation instructions, see the Renesas IC Toolbox Software Manual, sections 1 and 11.

#### 2.1.2. Launch the GUI

After installing the Renesas IC Toolbox software, launch the software from the Windows *Start* menu at the bottom-left corner of the screen.

- 1. Click Start > RICBox to open the initial RICBox window (see Figure 13).

- 2. The GUI can create new register configuration from scratch or Open a previously saved existing configuration. In the example below, a new configuration is created for 8V79S683

- 3. Click Create new project.

Figure 13. Create New Project in RICBox

- 4. Select RC180xx from the "Select a Product Family" list (see Figure 14).

- 5. Select the product variant to evaluate, then click OK. In this example, the 8V79S683 is selected.

Figure 14. Selecting 8V79S683 Device GUI in RICBox

6. Click *Finish* and then the Block Diagram logo at side panel to go straight to the Block Diagram (see Figure 15).

Figure 15. RICBox GUI Menu Buttons

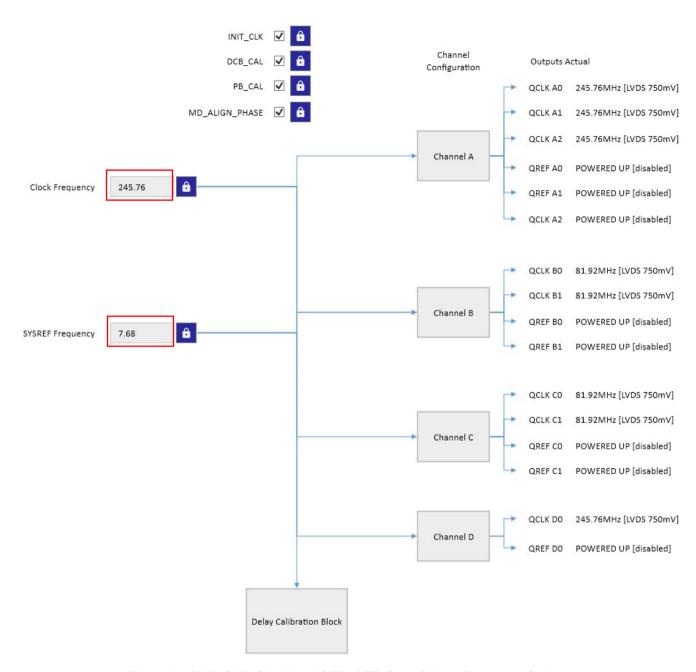

- 7. Enter the Clock and Sysref Input frequencies as shown in Figure 16.

- 8. Enter the values in the Delay Calibration Block (see Figure 17 for an example). This block is for setting Sysref delay step unit. For more details on setting the Delay Unit Multiplier, M\_DCB, P\_DCB and other parameters, refer to the <a href="https://example.com/8V79S680">8V79S680</a> datasheet Delay Calibration Block (DCB) section.

- DCB\_CAL setting: Activate DCB\_CAL = 1 and check the DAC\_CODE status for indicate successful calibration. Figure 18 displays the DAC\_CODE on the GUI.

- 9. Set the clock output QCLKx output frequency and phase delay (see Figure 19 for an example). INIT\_CLK is required to activate QCLKx divider and Phase Delay.

- 10. Set the clock output QCLKx output driver type and amplitude (see Figure 20 for an example).

- 11. Set the SysRef output QREFx output driver type, amplitude and phase delay (see Figure 21 for an example). For more details, refer to the 8V79S680 datasheet.

Figure 16. CLK/nCLK (Clock) and REF/nREF (Sysref) Input Frequency Setting

Figure 17. Delay Calibration Block

Note: Activate DCB\_CAL to take effect.

Figure 18. Activate DCB\_CAL and Check DAC\_CODE Value

Figure 19. Output Channel Frequency and Phase Delay Setting

Note: Activate INIT\_CLK to take effect.

Figure 20. QCLKx Output Driver Type and Amplitude Setting

Figure 21. QREFx Output Driver Type and Phase Delay Setting

Note: QREF Phase Delay Adjust does not need to activate INIT\_CLK to take effect.

## 2.1.3. Configure the Evaluation Board

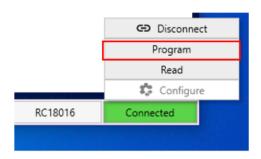

1. To establish communication between the EVB and the GUI, click the *Not Connected* button (1) in the lower right corner, then click *Connect* (2) (see Figure 22).

Figure 22. Connect to the Device in RICBox

2. Once the RICBox connection is established to the EVB, the *Not Connected* button will change to *Connected* (see Figure 23).

Figure 23. Connected Button

3. Click the *Program* button to write all the changed registers from the GUI to the on-board device. Any register changes made after clicking the *Program* button will occur in real-time and the device will update (see Figure 24).

Figure 24. Program Button

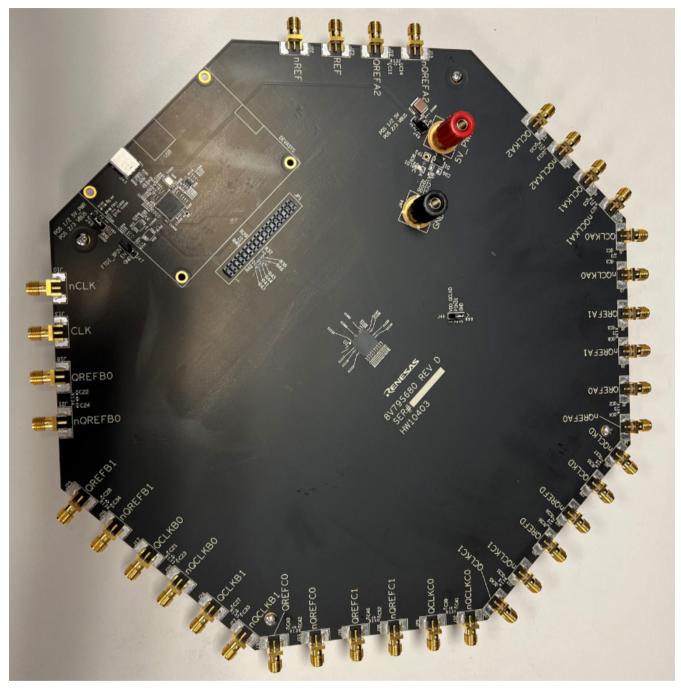

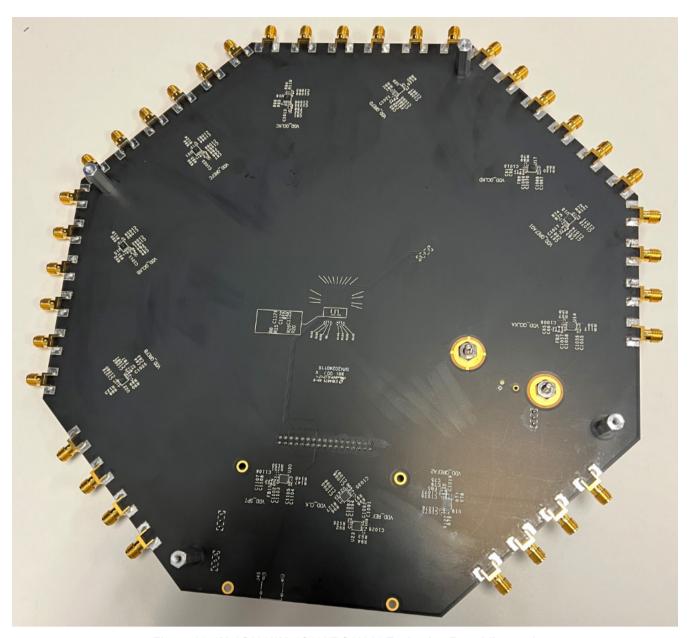

# 3. Board Design

Note: The 8V79S680 EVB schematic and BOM is available upon request.

Figure 25. 8V79S680/8V79S683/RC18016 Evaluation Board (top)

Figure 26. 8V79S680/8V79S683/RC18016 Evaluation Board (bottom)

# 4. Ordering Information

| Part Number  | Description               |

|--------------|---------------------------|

| 8V79S680-EVK | 8V79S680 Evaluation Board |

| 8V79S683-EVK | 8V79S683 Evaluation Board |

| RC18016-EVK  | RC18016 Evaluation Board  |

# 5. Revision History

| Revision | Date        | Description      |  |

|----------|-------------|------------------|--|

| 1.00     | Jul 5, 2024 | Initial release. |  |