## RC38312A

**Description**

The RC38312A Evaluation Board (EVB) is designed to support users evaluating high performance synthesizer and jitter attenuator applications. This document describes the following:

- Basic hardware and GUI setup using Renesas IC Toolbox (RICBox™) software

- Board power-up instructions

- Instructions to get active output signals using a provided configuration file

- Hardware modifications required for different conditions

**Board Contents**

- RC38312A evaluation board

- EVB manual

- Configuration software (installable plugin for RICBox)

- Configuration example file for four built-in device settings

- Board schematic and BOM

**Features**

- Four differential clock inputs

- Twelve differential clock outputs

- On-board EEPROM stores startup-configuration data

- XIN terminal can use laboratory signal generator or OCXO/TCXO/XO components and board

- Laboratory power supply connectors

- USB-C power supply

- Serial port for configuration and register read out

**Computer Requirements**

- USB 2.0 or USB 3.0 interface

- Processor: minimum 1GHz

- Memory: minimum 512MB; recommended 1GB

- Available disk space: minimum 600MB (1.5GB 64-bit); recommended 1GB (2GB 64-bit)

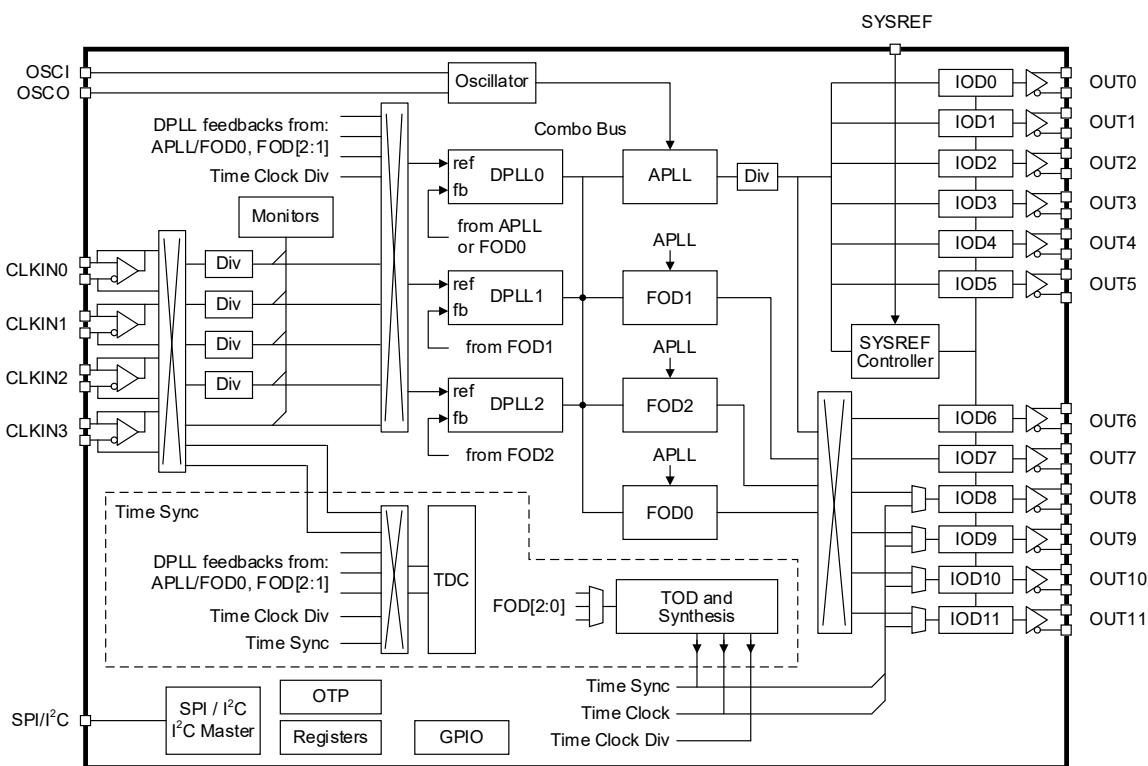

Figure 1. RC38312A Block Diagram

## Contents

|                                                           |           |

|-----------------------------------------------------------|-----------|

| <b>1. Functional Description.....</b>                     | <b>4</b>  |

| 1.1 Operational Characteristics .....                     | 4         |

| 1.2 Hardware Setup and Configuration .....                | 4         |

| 1.2.1. Power and USB-C Connections to Computer Host ..... | 6         |

| 1.2.2. Overdrive the XIN with an External Signal .....    | 9         |

| 1.2.3. On-board Crystal Mount.....                        | 9         |

| 1.2.4. On-board XO Mount.....                             | 10        |

| 1.2.5. Clock Inputs.....                                  | 12        |

| 1.2.6. Clock Outputs.....                                 | 13        |

| 1.2.7. Serial Connection.....                             | 14        |

| 1.2.8. On-board EEPROM.....                               | 15        |

| 1.2.9. GPIO DIP Switch Selectors.....                     | 16        |

| 1.2.10. Dash Code Configuration Serial Interface.....     | 17        |

| <b>2. Software Setup and Configuration.....</b>           | <b>18</b> |

| 2.1.1. Prepare the Software .....                         | 18        |

| 2.1.2. Launch the GUI .....                               | 18        |

| 2.1.3. Configure the Evaluation Board.....                | 20        |

| <b>3. Board Design .....</b>                              | <b>21</b> |

| <b>4. Typical Performance Graphs.....</b>                 | <b>23</b> |

| <b>5. Ordering Information.....</b>                       | <b>23</b> |

| <b>6. Revision History .....</b>                          | <b>23</b> |

## Figures

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| Figure 1. RC38312A Block Diagram.....                                       | 1  |

| Figure 2. Evaluation Board (Rev E) – Top Side.....                          | 5  |

| Figure 3. Evaluation Board (Rev E) – Bottom Side.....                       | 6  |

| Figure 4. USB Power Jumpers .....                                           | 7  |

| Figure 5. External 5V Board Input .....                                     | 7  |

| Figure 6. External 5V Schematic .....                                       | 7  |

| Figure 7. J90 Board Input.....                                              | 8  |

| Figure 8. V <sub>DD</sub> Jumper Bypass Schematic with Jumper .....         | 8  |

| Figure 9. V <sub>DD</sub> Jumper Bypass Schematic with Resistor Rework..... | 8  |

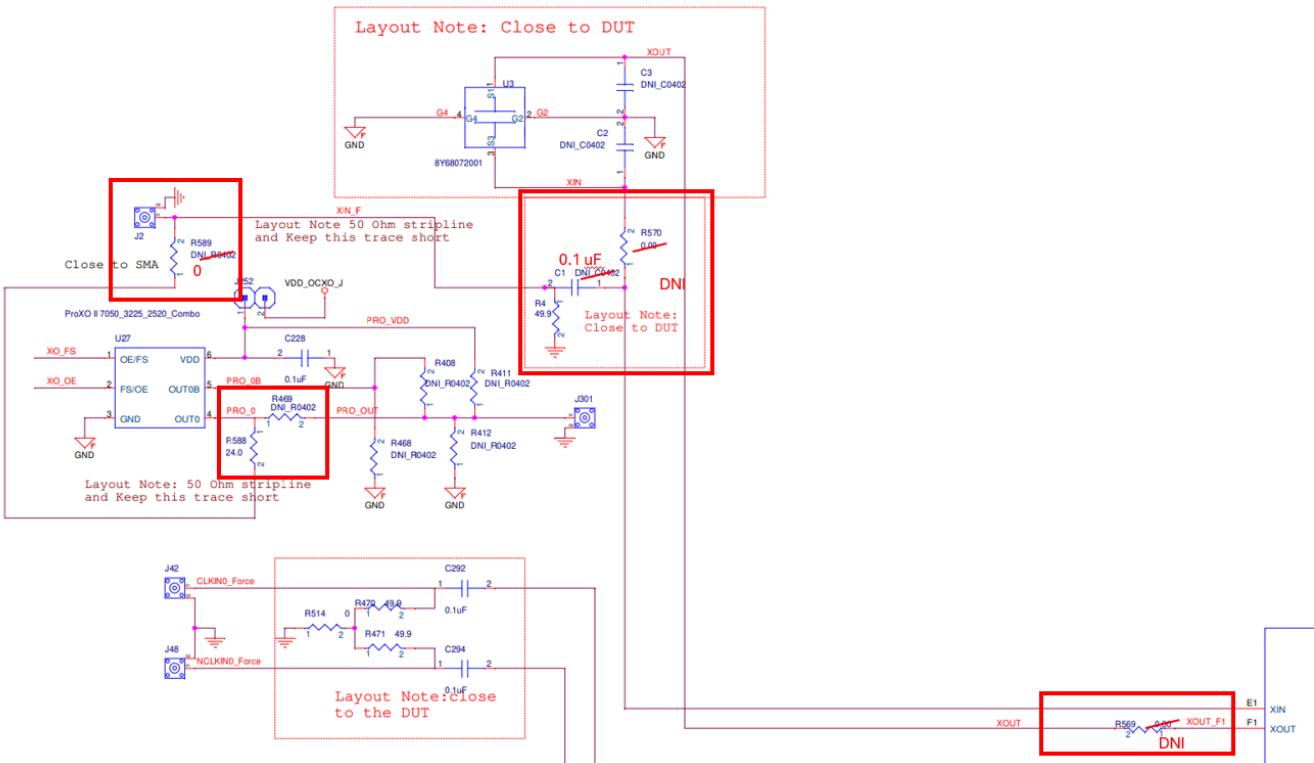

| Figure 10. XIN Pin Overdrive Schematic .....                                | 9  |

| Figure 11. Crystal Mount Schematic.....                                     | 10 |

| Figure 12. EVB XO Pads .....                                                | 10 |

| Figure 13. LDO Power Supply for XO and OCXO Connection Schematic .....      | 11 |

| Figure 14. XO Schematic .....                                               | 11 |

| Figure 15. XO_OE and XO_FS Pins DIP Switch Schematic .....                  | 12 |

| Figure 16. Input Clock Termination Schematic .....                          | 12 |

| Figure 17. Output Type Options .....                                        | 13 |

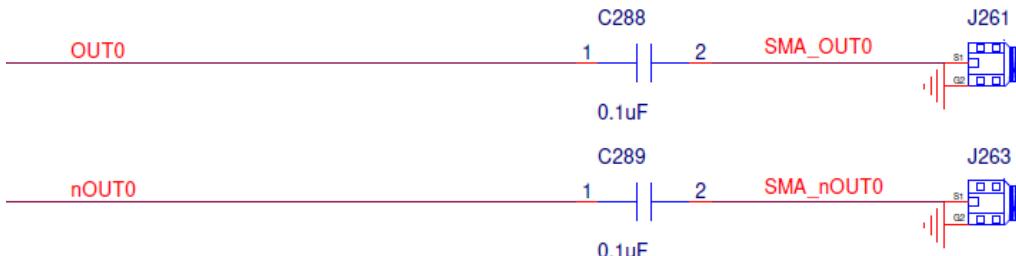

| Figure 18. Output Clock AC-Coupling .....                                   | 13 |

| Figure 19. Communication Setup .....                                        | 14 |

|                                                                |    |

|----------------------------------------------------------------|----|

| Figure 20. EEPROM in Socket .....                              | 15 |

| Figure 21. EEPROM Pin Description .....                        | 15 |

| Figure 22. EEPROM Schematic 1 .....                            | 15 |

| Figure 23. EEPROM Schematic 2 .....                            | 16 |

| Figure 24. GPIO Schematic and EVB DIP Switches .....           | 16 |

| Figure 25. Create New Project in RICBox .....                  | 18 |

| Figure 26. Selecting RC3832A Device GUI in RICBox .....        | 18 |

| Figure 27. RICBox Wizard Navigation .....                      | 19 |

| Figure 28. RICBox GUI Menu Buttons .....                       | 19 |

| Figure 29. Connect to the Device in RICBox .....               | 20 |

| Figure 30. Connected Button .....                              | 20 |

| Figure 31. Program Button .....                                | 20 |

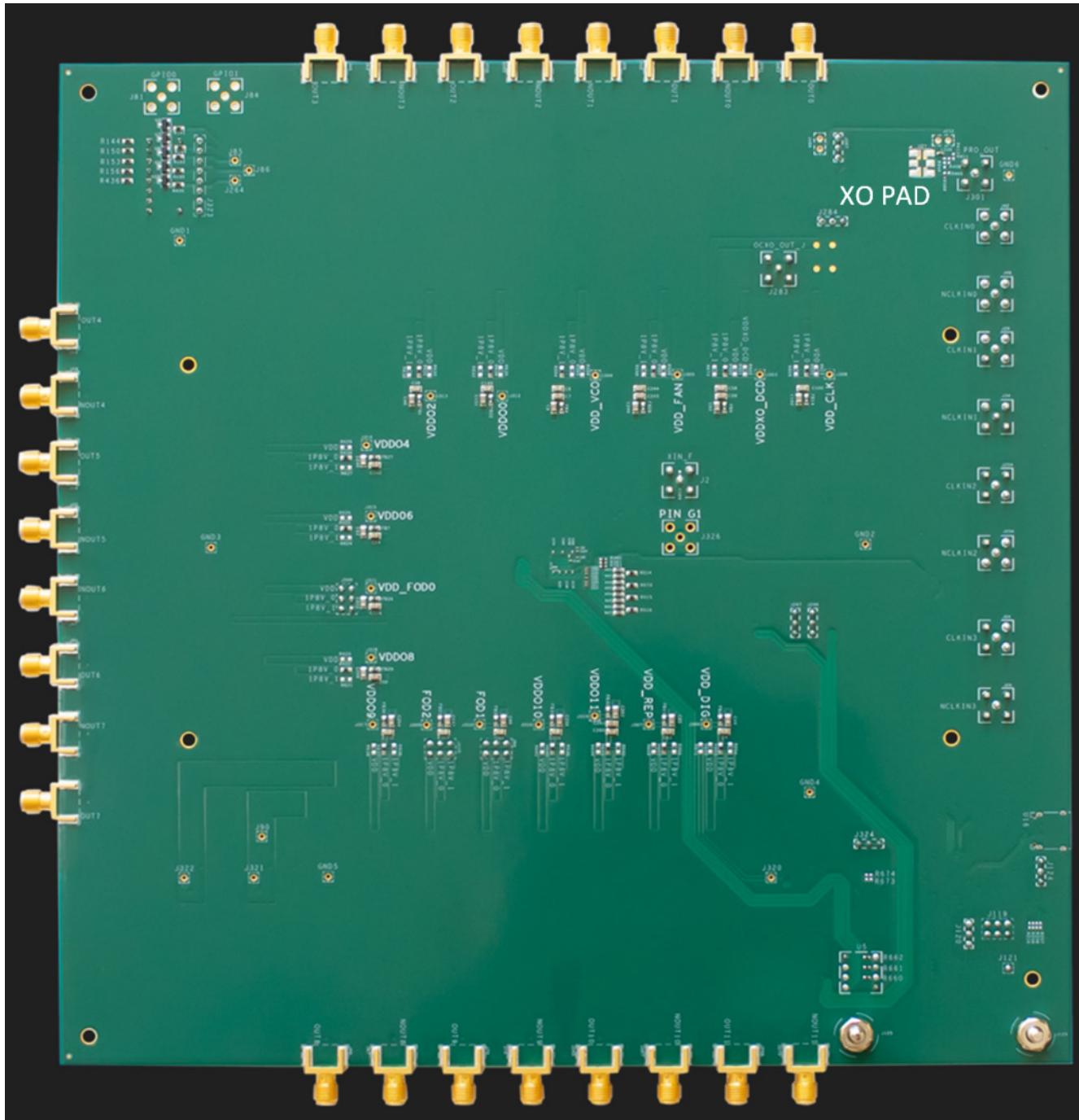

| Figure 32. RC38312A Evaluation Board Rev E (top) .....         | 21 |

| Figure 33. RC38312A Evaluation Board Rev E (bottom) .....      | 22 |

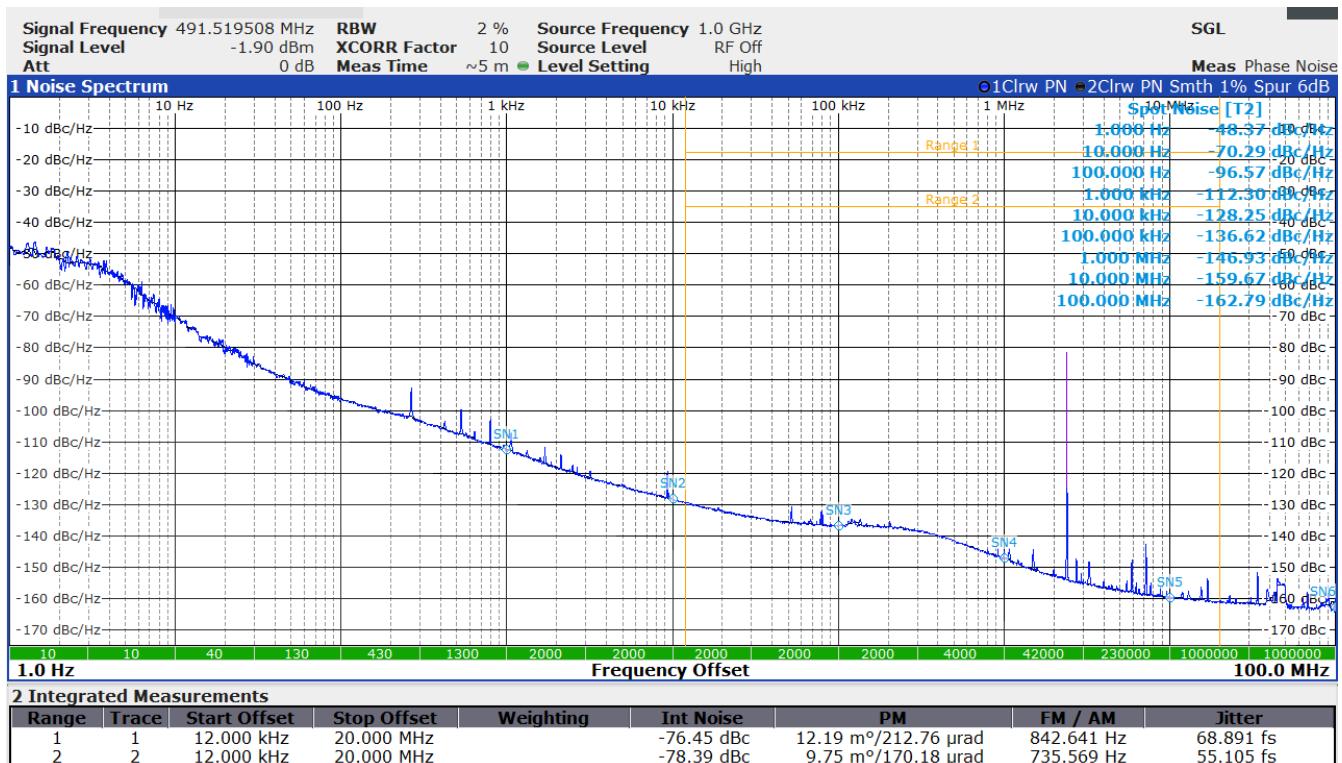

| Figure 34. Phase Noise 491.52MHz Output Synthesizer Mode ..... | 23 |

# 1. Functional Description

The evaluation kit is used to demonstrate the RC38312A, a fully integrated clock synthesizer/generator and clock jitter attenuator. The kit can be used to evaluate major parameters including phase noise, spurious attenuation, clock frequency, output skew, phase alignment, device timing, and the signal waveform. The device on the board accepts any input frequency from 1kHz to 1GHz.

The RC38312A consists of a single APLL and three DPLLs design that allows for multiple separate frequency domains. The APLL can be used independently of the DPLL to generate synthesized clocks at the outputs that track the frequency of the input at the XIN pin. The DPLL can be used for jitter attenuation, clock filtering, and frequency translation while tracking clocks from the CLKIN pins. The DPLLs provide a programmable bandwidth and a DCO function for real-time frequency/phase adjustment.

## 1.1 Operational Characteristics

The board is equipped with on-board LDOs that require a 5V supply. If connecting to a high-speed USB interface, the evaluation board may be powered directly from the USB connection. The board is designed to operate over the industrial temperature range from -40°C to +85°C, ambient temperature.

It is recommended to use proper grounding during board operations to avoid ESD damage to the EVB.

## 1.2 Hardware Setup and Configuration

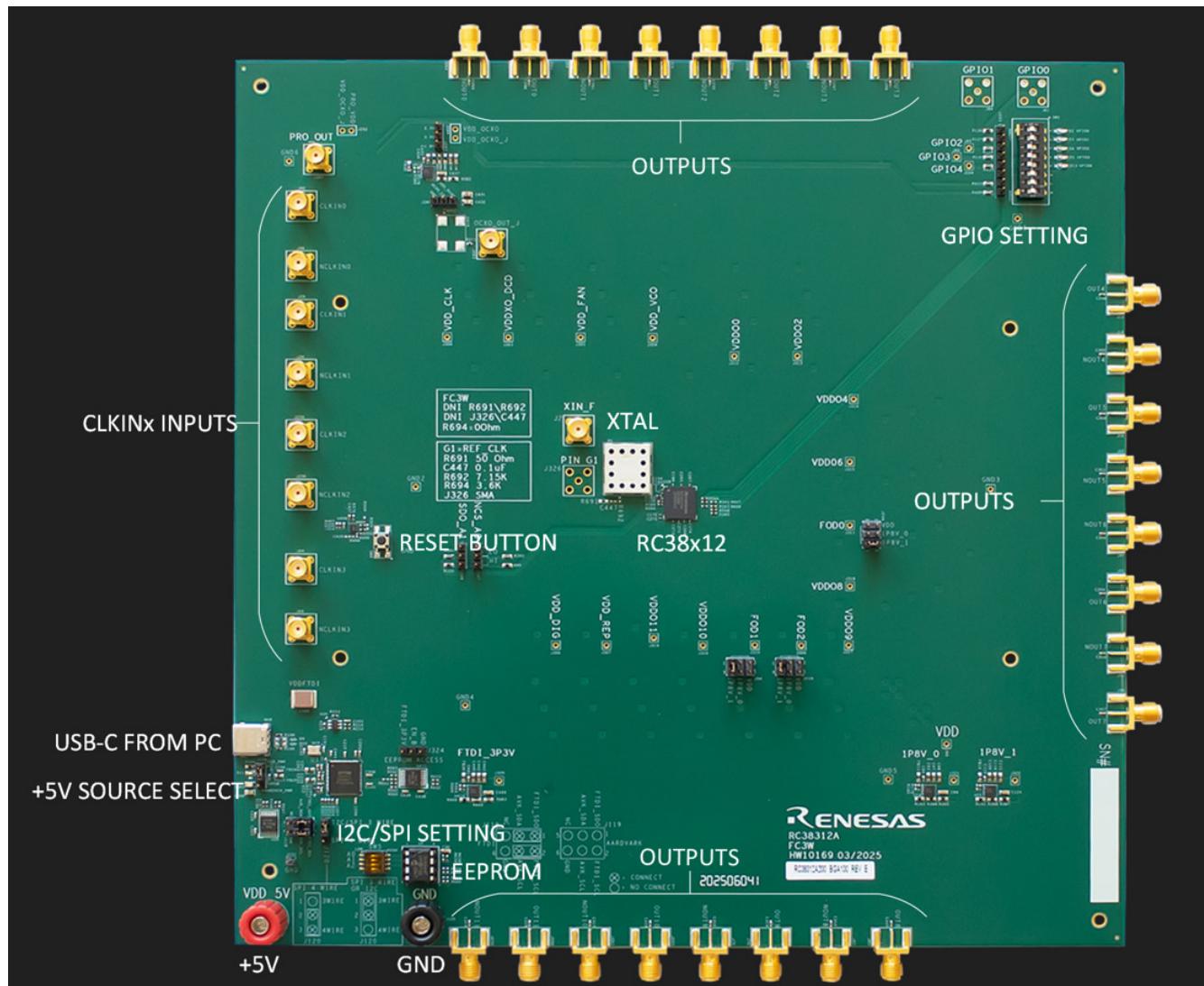

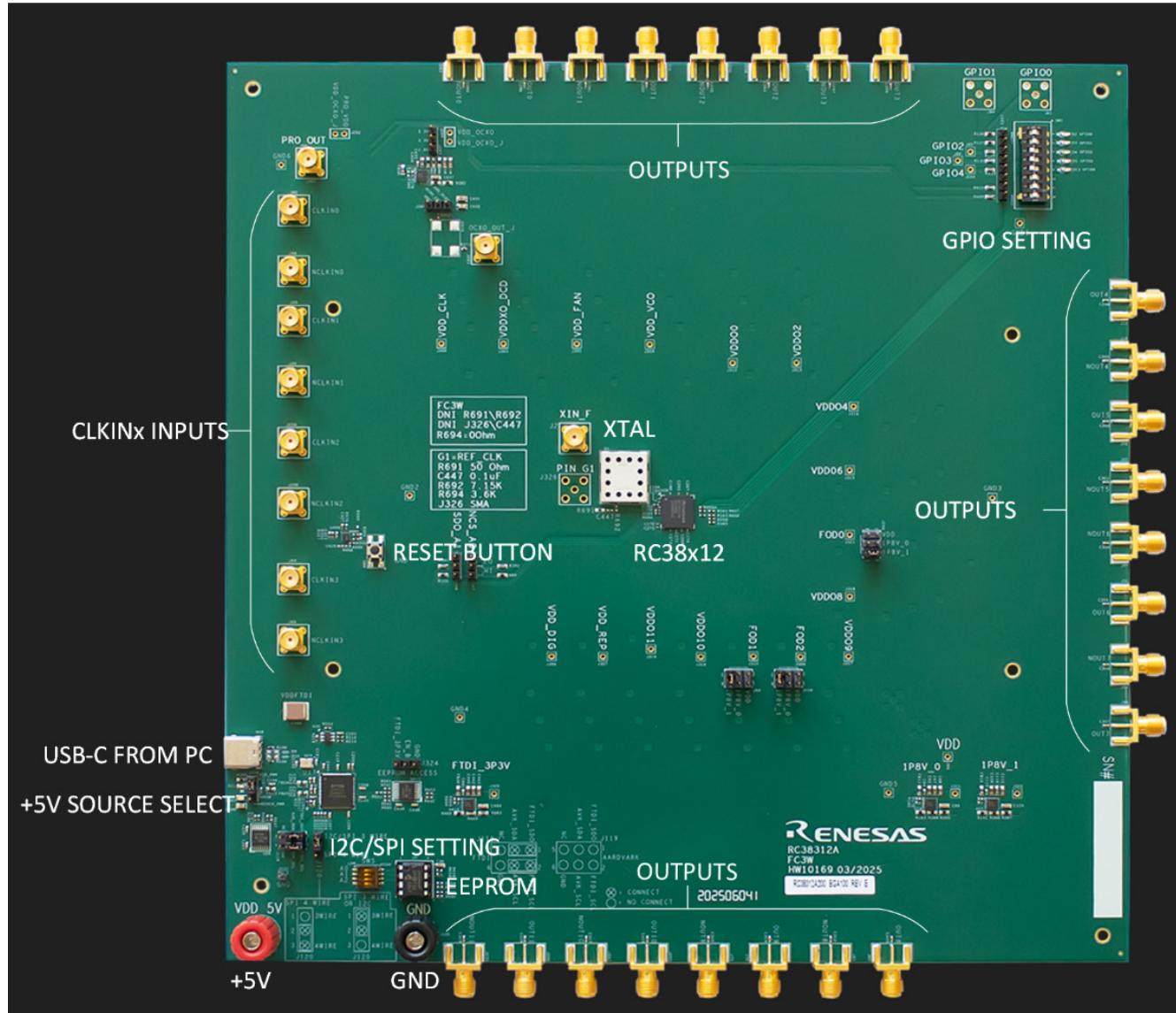

The following sections describe the crystal, input clock, serial, GPIO, and output and power functions used for setting up device testing. The jumper setup example is shown in [Figure 2](#).

- **I<sup>2</sup>C/SPI Interface**

SPI 4 wire interface in this example.

- **Power Supply**

Use 5V\_VDD with on-board LDO to generate 1.8V power rail. See [Figure 2](#) for power select jumper settings

- **CLKx Inputs**

The CLKx inputs are AC-coupled by default and can accept either differential input or single-ended input.

Assume the signal source (for example, lab equipment requires 50Ω to GND termination at the receiver), the CLKx inputs have on-board terminations of 50Ω to GND with AC-coupling.

- **Outputs**

The outputs are AC-coupled without on-board pull-down or pull-up terminations. When setting the output to an HCSL driver, the on-chip pull-down internal termination needs to be enabled. If setting the CML, the on-chip pull-up internal termination needs to be enabled. Otherwise, the outputs will not present a signal.

Figure 2. Evaluation Board (Rev E) – Top Side

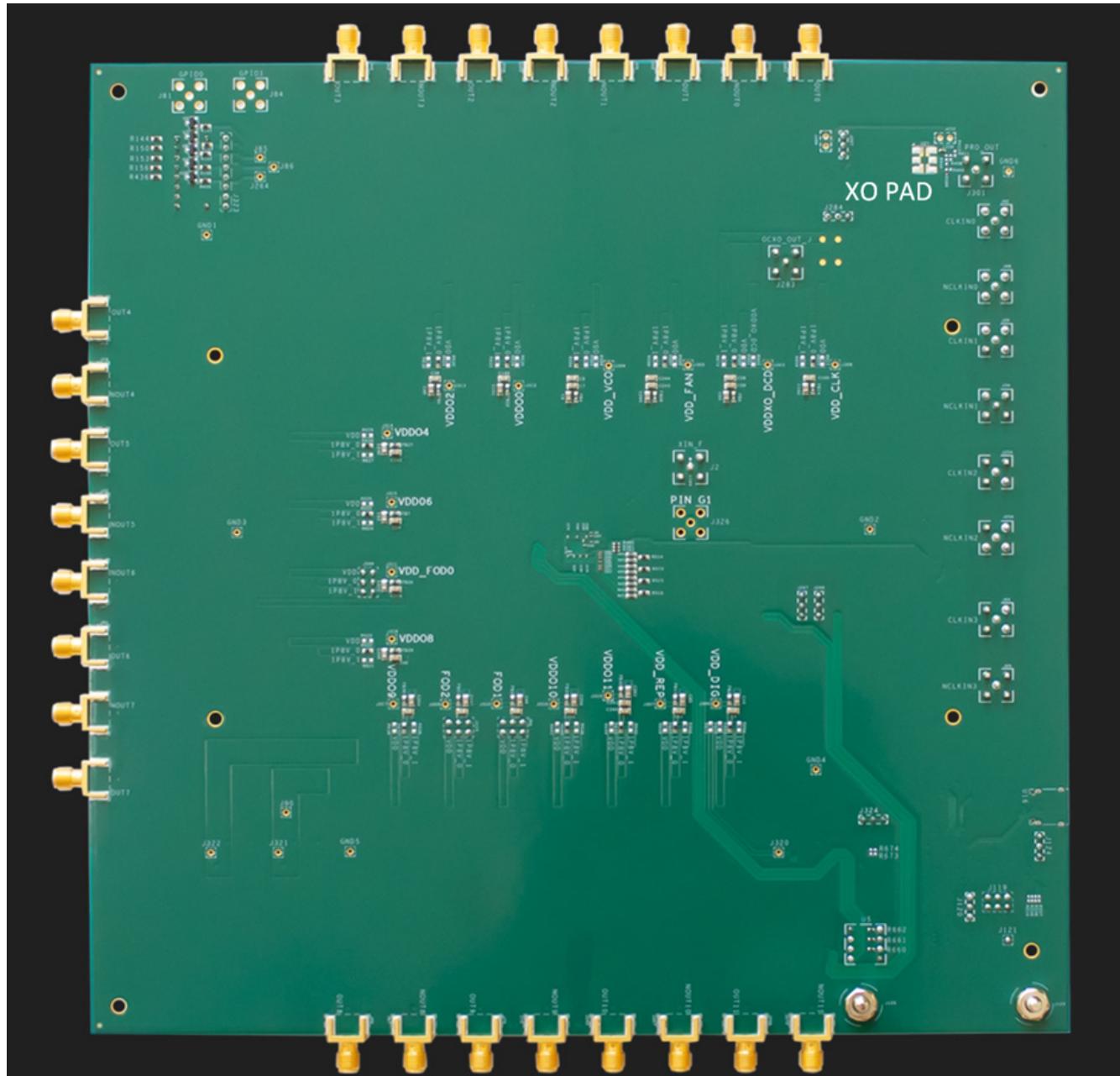

**Figure 3. Evaluation Board (Rev E) – Bottom Side**

*Note:* 1P8V\_0, 1P8V\_1, 1P8\_VDDXO\_DCD and 1P8\_VCO refer to separate LDO's supply on the board. They can be used to isolate pin supplies from each other for performance optimization.

### 1.2.1. Power and USB-C Connections to Computer Host

The EVB is connected to a computer host via the USB3.0 to USB-C cable. It is recommended that the cable is connected to a USB3.0 port. However, a USB2.0 port is acceptable for the RC38312A to I<sup>2</sup>C/SPI communications only. The USB-C provides +5V as power source to the on-board regulators. The on-board regulators support 1.8V voltages to the entire EVB.

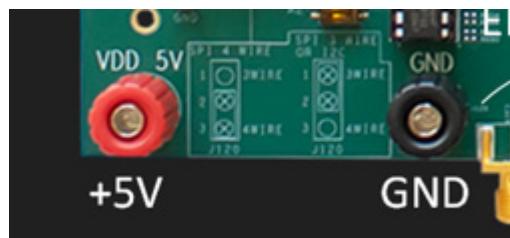

- Power Connection

- Set the power supply voltage to 5V and the current limit to 1.5A

- +5V (J123) = +5V, 2A

- GND (J125) = GND

- Expected Current Draw: ~ 0.7A

- After programming the device ~0.6A to ~1A during normal operation (device configuration dependent)

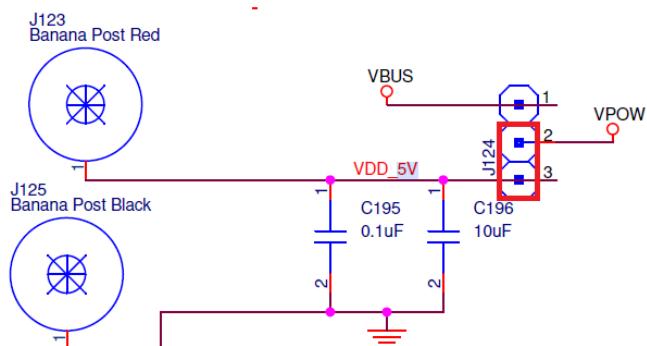

### 1.2.1.1. Power the Device with USB Connection

- Set jumper on J124 between pins 1 and 2

- Ensure that the EVB connects to a USB 3.0 (or newer) port

Figure 4. USB Power Jumpers

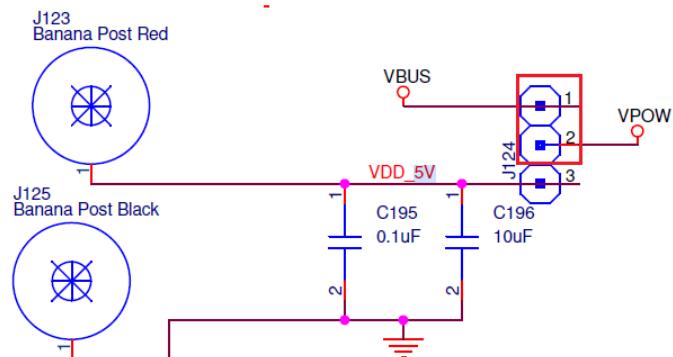

### 1.2.1.2. Power the Device with External Power Supply Connection and On-board Voltage Regulators

- Set jumper on J124 between pins 2 and 3

- Ensure 5V at banana jack J123 and GND at J125 connection

Figure 5. External 5V Board Input

Figure 6. External 5V Schematic

**Note:** Allow for up to 2A of current with the power supply. The device current will be increased during register write and calibration.

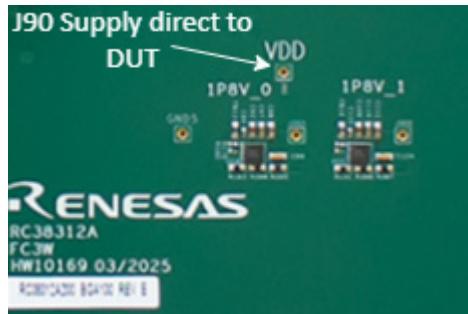

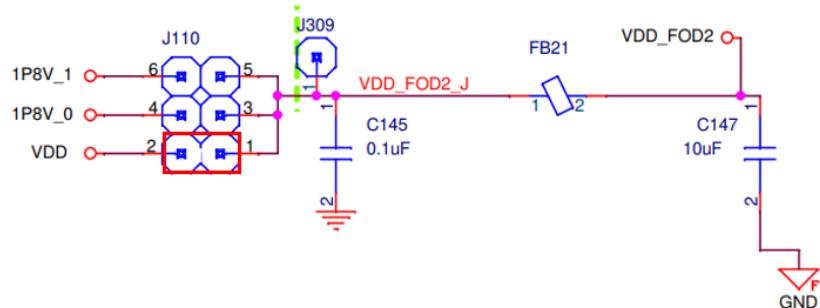

### 1.2.1.3. Power the Device Pins with External Power Supply Connection J90

- Ensure 1.8V at J90 and GND connection depending on the power pin

- Change the corresponding domain jumper or resistor selection to V<sub>DD</sub>

Figure 7. J90 Board Input

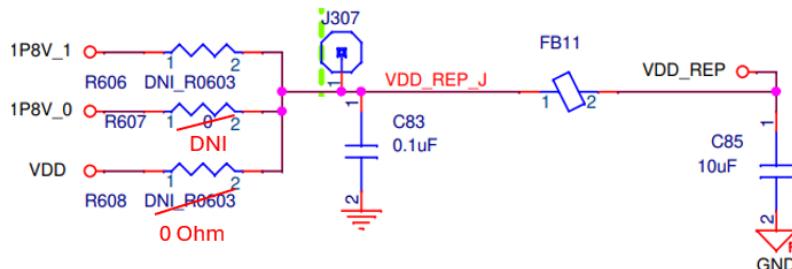

Figure 8. V<sub>DD</sub> Jumper Bypass Schematic with JumperFigure 9. V<sub>DD</sub> Jumper Bypass Schematic with Resistor Rework

*Note:* J90 can supply voltage for the entire device if all voltage pin jumper settings are configured for V<sub>DD</sub> and the input voltage is 1.8V.

**Important:** All individual voltage domains run at 1.8V. Only VDD\_DIG compatible with 3.3V. Supplying 3.3V to any other domain may cause damage to the RC38312A device.

## 1.2.2. Overdrive the XIN with an External Signal

The RC38312A device can support between 25MHz–80MHz on the XIN (crystal oscillator input) pin. There are several options for providing an input signal to the device XIN pin:

- An external signal (J2 SMA connector) typically from a signal generator

- An on-board crystal mount (U3); see section 1.2.3

- Two on-board XO mounts (U27, U29); see section 1.2.4

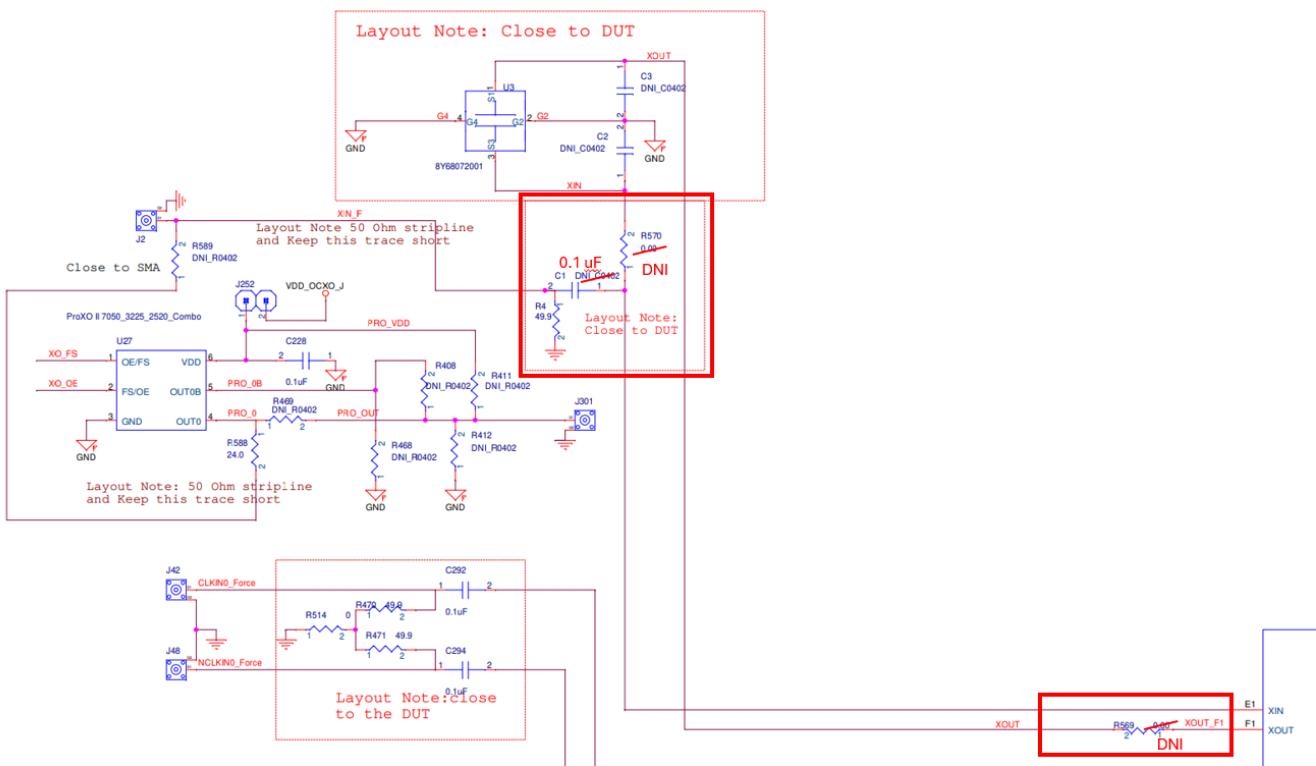

The following steps and Figure 10 describe how to overdrive XIN with an external signal:

1. Populate C1 with  $0.1\mu\text{F}$  capacitor to ensure that J2 has a connected path to the RC38312A device.

2. Depopulate R570 and R569 (near DUT XOUT pin) to ensure that excess trace is not used.

3. Populate R4 with  $50\Omega$  for input termination (ensure signal is less than 1.3V amplitude).

4. Place input clock signal at J2 and ensure that the signal is within specification for the XIN pin.

Figure 10. XIN Pin Overdrive Schematic

## 1.2.3. On-board Crystal Mount

The crystal mounting position can only be used if there is no other signal present on the XIN path (see Figure 11). To setup the evaluation board for crystal input:

1. Depopulate C1 to ensure there is no excess trace in the XIN pin.

2. Populate 0 Ohm to R570 and R569

3. Populate C2 and C3 to externally tune the input crystal frequency (if needed).

*Note:* The EVB stray capacitance is measured to be  $\sim 8.24\text{pF}$ .

4. Mount the crystal to U3.

*Note:* Crystal pin assignment can be varied. Check the pin assignment of the crystal being used. Remove R452 and R454 if needed.

**Figure 11. Crystal Mount Schematic**

#### 1.2.4. On-board XO Mount

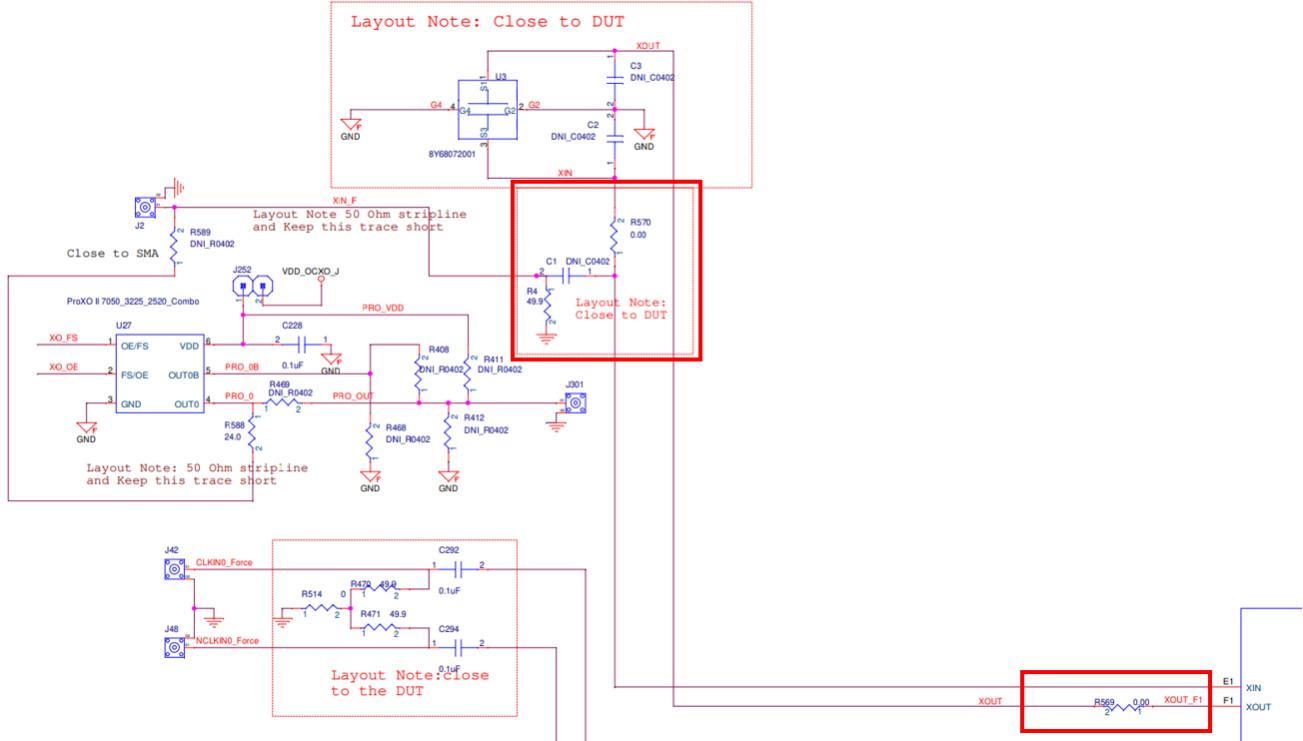

The evaluation board contains an independent XO circuit with an SMA connector output. The U27 XO footprint located at the bottom of the board can be either 4-pin or 6-pin. The footprints are in parallel and should only be used one at a time. The J301 SMA connector is the output of the XO. Connect this output to overdrive the J2 XIN through a  $50\Omega$  coax cable. To ensure the proper operation of the XO, use the following steps and refer to [Figure 12](#), [Figure 13](#), [Figure 14](#), and [Figure 15](#).

**Figure 12. EVB XO Pads**

1. Set J287 to proper LDO power supply voltage for the XO (3.3V, 2.5V or 1.8V)

2. Install jumper J252 and J288 to power-up the XO.

3. Set to Overdrive XIN.

**Figure 13. LDO Power Supply for XO and OCXO Connection Schematic**

4. If the XO is a single-ended LVCMS driver, ensure that the XO output is below 1.2V amplitude signal in order to support proper XIN pin characteristics. R588 can be populated with a resistor. The R588 resistor value depends on the output impedance of the XO driver  $R_o$ . Suggest  $R_o + R588 = 90$  Ohm. With  $R4 = 50$  Ohm to GND termination, this should result  $\sim 1.17$ V amplitude at the OSC1 pin. For example, an XO with output impedance  $R_o = 17$  Ohm, suggest  $R588 = 83$  Ohm.

**Figure 14. XO Schematic**

5. Set the DIP switch SW1 S7 and S8 to pull the XO output enable pin high or low depending on the XO datasheet.

6. If the XO is a differential output driver, check the termination requirement of the XO. The spare footprints can be used for LVPECL, LVDS, HCSL drivers. In most cases, only one side of the differential driver is required to overdrive the XIN.

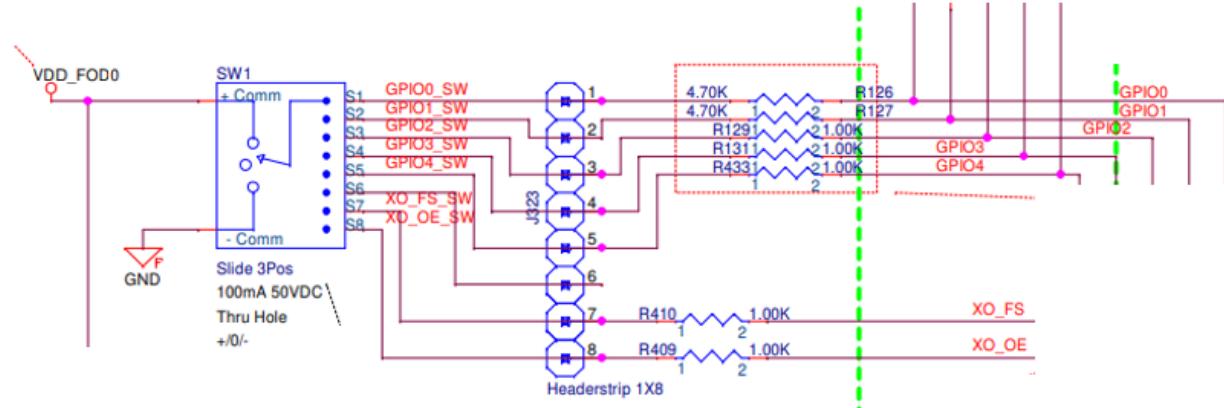

Figure 15. XO\_OE and XO\_FS Pins DIP Switch Schematic

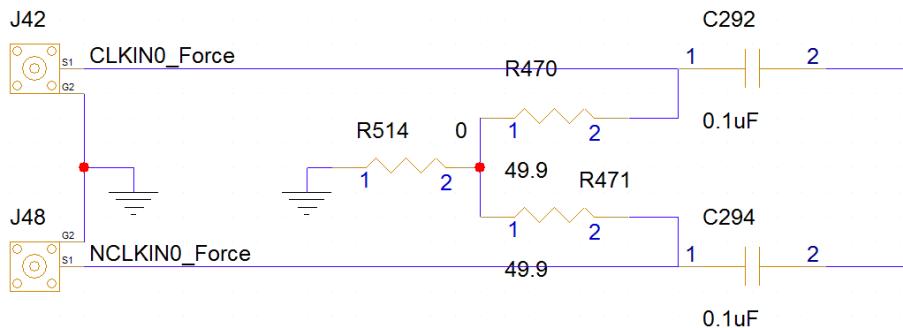

### 1.2.5. Clock Inputs

The RC38312A can accept four differential clock inputs to be used as a jitter attenuator source. To enable proper connection, ensure the input termination resistor setup corresponds to the input signal that is connected. The evaluation board CLKx/nCLKx, default termination setup has  $50\Omega$  to GND at each leg and AC coupling shown in [Figure 16](#).

Figure 16. Input Clock Termination Schematic

The RC38312A CLKx/nCLKx when configured to AC coupling, contains internal DC -bias for proper VCMR. The CLKx/nCLKx inputs supported frequency ranges of the clock inputs are 1kHz to 1GHz in differential mode, and 1kHz to 250MHz in single-ended mode.

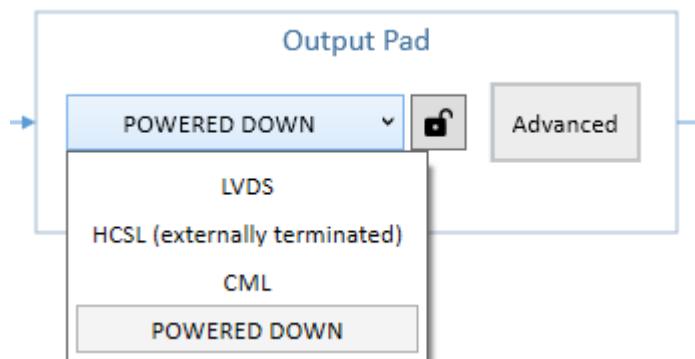

## 1.2.6. Clock Outputs

Each of the 12 differential output pairs can be programmed to LVDS, HCSL or CML logic type. The OUT8 to OUT11 can also be programmed to CMOS logic type.

- The HCSL mode supports HCSL by default and can be modified to support other modes by changing the amplitude and enabling/disabling the internal termination.

- The CML mode supports CML signal. The driver can be configured to enabling/disabling the internal termination and changing the amplitude.

- LVDS outputs can be configured to 350mV or 400mV swing up to 1V common mode voltage.

- Each output can also be tri-stated when not being used.

- For CMOS output type, output phase of each pin can be programmed to be 180 degrees out-of-phase, in-phase, or single-pin output.

The evaluation board does not provide an on-board pull-up for a CML driver or a pull-down for an HCSL driver.

Figure 17. Output Type Options

The clock outputs of the evaluation board are AC-coupled without board level termination before the AC-coupling (see [Figure 18](#)). To achieve the output signal, the HCSL outputs need to enable the <Internal pull-down> through the registers. For evaluation, the monitor equipment (scope, phase noise system, etc.) receivers normally have 50Ω to GND for end termination.

For a CML driver, the driver can also be set to External Termination or Internal Termination. To achieve the output signal, the CML outputs need to enable the <Internal pull-up> through the registers.

For an LVDS driver, there is no option of Internal or External termination. The output will switch without board level termination. It only requires 50Ω termination to GND at the monitor equipment.

Figure 18. Output Clock AC-Coupling

### 1.2.7. Serial Connection

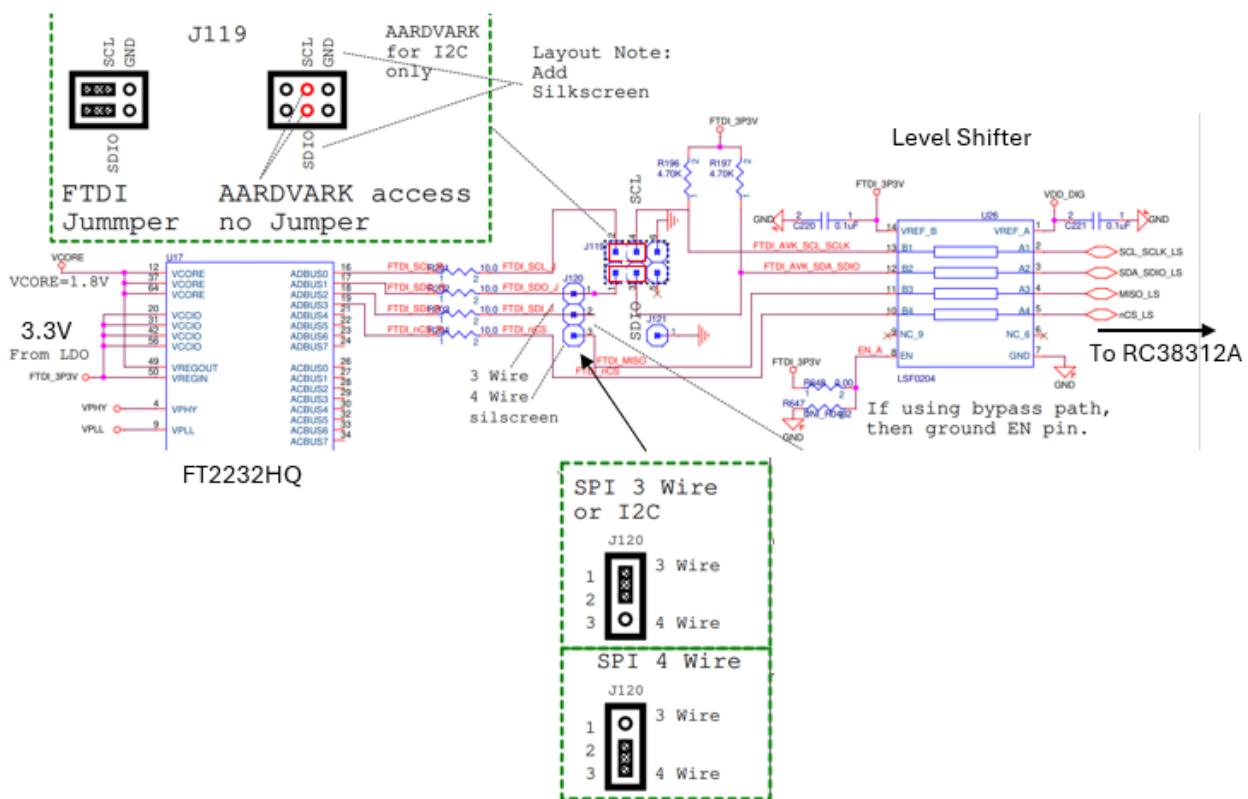

The EVB can be connected to a computer via a USB3.0 to USB-C connector. The on-board USB-to-MPSSE Bridge (FTDI FT2232HQ) can handle the data communication. The +3.3V is from the on-board LDO.

The Bus Source connector J119 is used to select the source of the communication bus. The bus can be either 3-wire or 4-wire SPI and can also be I<sup>2</sup>C for specific tests. Pins 1 and 2 in J119 are SDA and SCL from the FTDI chip. Pins 3 and 4 pass the SDA and SCL to the I<sup>2</sup>C level shifter. To use the on-board FTDI chip, install jumpers on pins 1–3 and 2–4. The board will be shipped with these jumpers installed. Theoretically, any I<sup>2</sup>C adapter can be connected to pins 3 and 4 for SDA and SCL. Pin 6 can be used as the ground connection for the I<sup>2</sup>C connection. Pins 3, 4, 5 and 6 are arranged such that a Total Phase I<sup>2</sup>C Host Adapter (part number: TP240141) can be plugged onto pins 3, 4, 5 and 6 only (see [Figure 19](#)).

For default I<sup>2</sup>C operation, jumpers are installed on pins 1–3 and 2–4 (see jumper J119).

J120 is used for setting 4-wire SPI, 3-wire SPI or I<sup>2</sup>C.

Figure 19. Communication Setup

Note: For I<sup>2</sup>C operation instructions, contact [Renesas support](#).

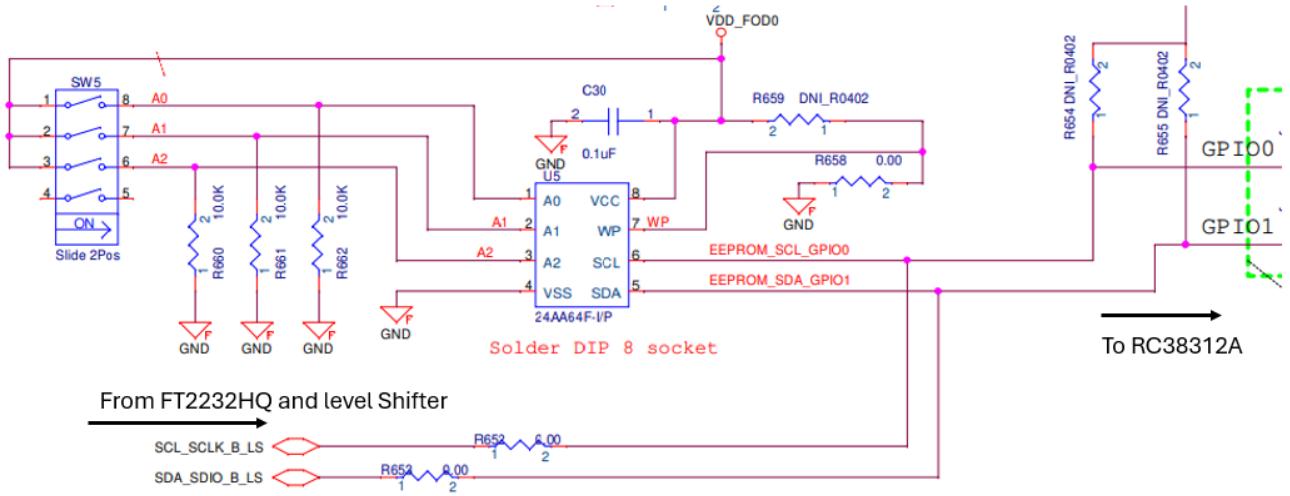

### 1.2.8. On-board EEPROM

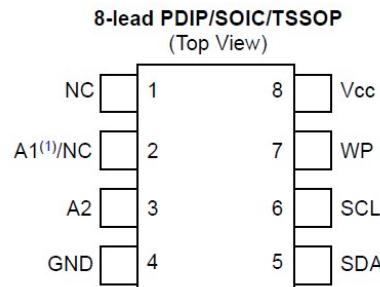

The EVB also supports an external EEPROM IC for loading of an RC38312A configuration programmed into the EEPROM as an option. To load the configurations from EEPROM, the EEPROM load enable bit must be set in device OTP. If the enable bit is not set, the EEPROM load will be skipped.

The EVB provides a socket of 8-lead DIP8 socket (see [Figure 20](#)) so other EEPROM devices of different memory size can be tested.

**Figure 20. EEPROM in Socket**

**Figure 21. EEPROM Pin Description**

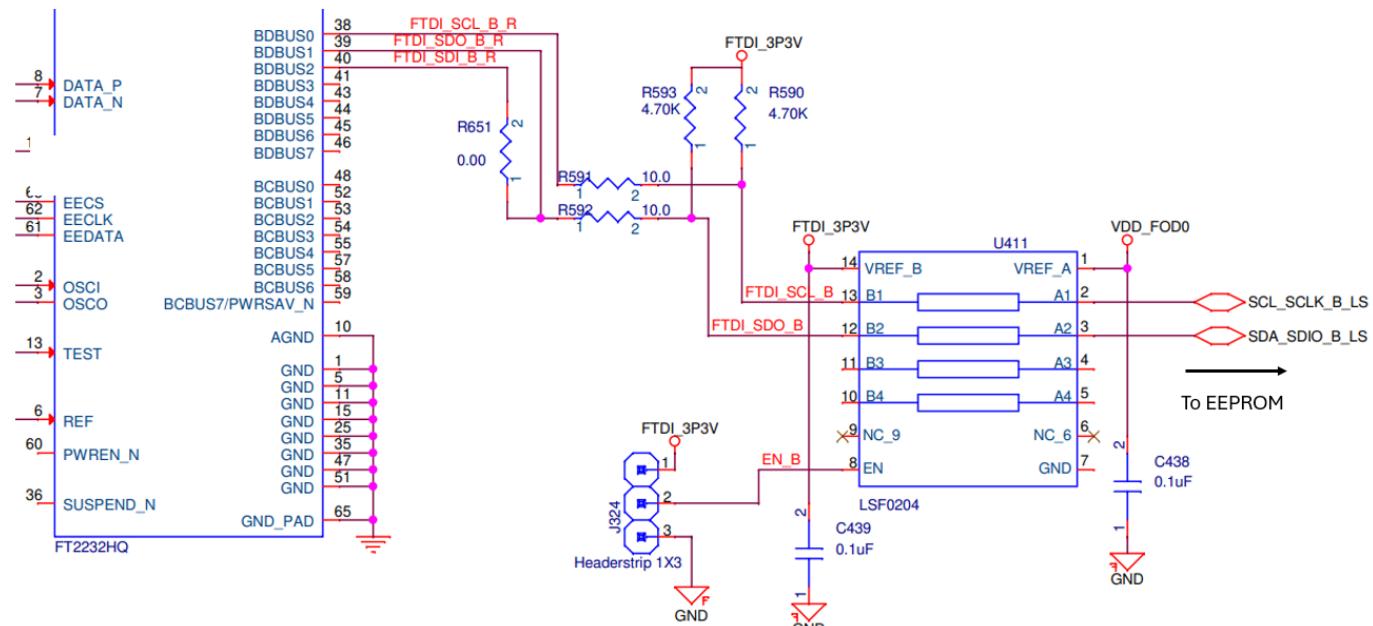

The EEPROM SCL and SDA are connected to a dedicate port B of FT2232HQ through level shifter for EEPROM programming. The EEPROM SCL and SDA also connected to RC38312A GPIO0 and GPIO1 for EEPROM data loading. See [Figure 22](#) and [Figure 23](#). If the EEPROM contents are to be loaded to the FC3 device via GPIO0 and GPIO1, then GPIO0 and GPIO1 must be pulled high via the GPIO DIP switch.

Figure 22. EEPROM Schematic 1

Figure 23. EEPROM Schematic 2

The SW5 switches are the EEPROM address inputs that can be set either high or low to define the device address.

The WP pin is the write-protect input. When the WP pin is pulled down to GND (Low), the EEPROM can have normal write operations. When it is pulled up directly to V<sub>CC</sub> (High), all write operations are inhibited. By default The WP pin is set to low to allow EEPROM rewrite.

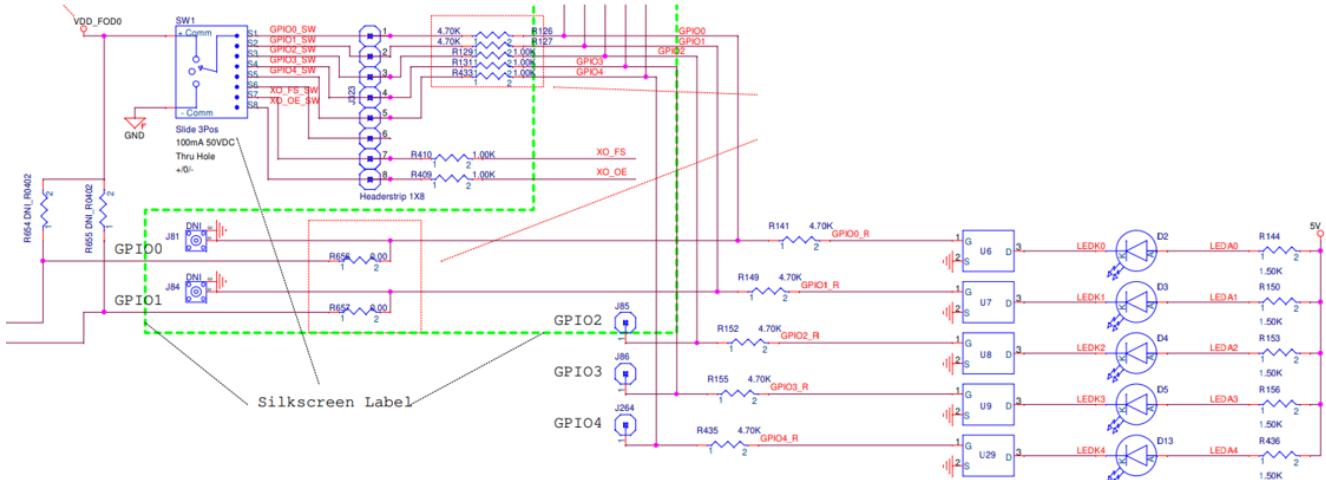

### 1.2.9. GPIO DIP Switch Selectors

The EVB has one DIP switch set (SW1) to support GPIO pins on RC38312A device. GPIOs 0–6 can support a two-level input (low/high). The middle position of the DIP switches leaves the pin open so GPIOs can be controlled with internal pull-up and pull-down resistors. Move to the '+' side to pull the pin high and move to the '-' side to pull the pin low. LEDs correspond to each GPIO to show the pin state.

Figure 24. GPIO Schematic and EVB DIP Switches

### 1.2.10. Dash Code Configuration Serial Interface

Each part can be OTP (One Time Programmed) to different Dash Code. The serial interface depends on the Dash Code configuration. Refer to the Datasheet Addendum of each dash code. [Table 1](#) is example of configuration of RC38312A200. In this example, if the GPIO1 and GPIO0 pins are set to 00 at power-up, the part is set to configure 0, hence the serial interface is SPI 4-wire.

**Table 1. RC38312A200 Configuration Example**

| Configuration | Name                         | GPIO1 | GPIO0 |

|---------------|------------------------------|-------|-------|

| Configure 0   | SPI 4 Wire                   | 0     | 0     |

| Configure 1   | SPI 3 Wire                   | 0     | 1     |

| Configure 2   | I <sup>2</sup> C             | 1     | 0     |

| Configure 3   | I <sup>2</sup> C with EEPROM | 1     | 1     |

## 2. Software Setup and Configuration

### 2.1.1. Prepare the Software

For software installation instructions, see the [Renesas IC Toolbox Software Manual](#), sections 1 and 11.

### 2.1.2. Launch the GUI

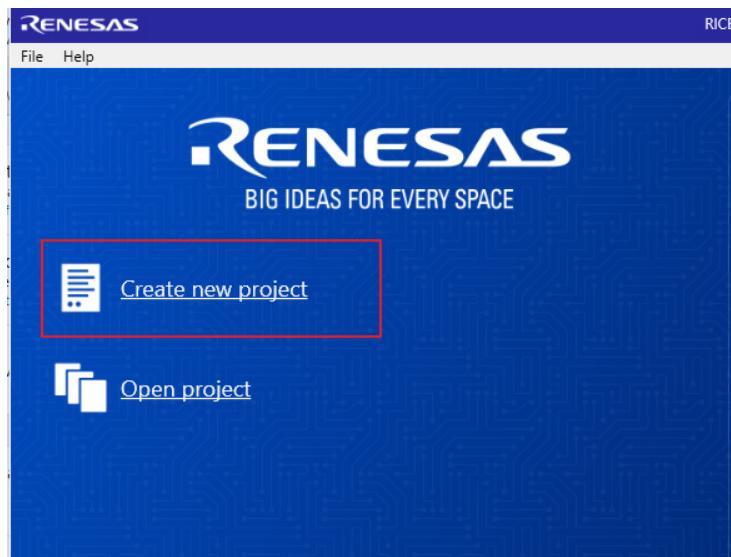

After installing the Renesas IC Toolbox software, launch the software from the Windows *Start* menu at the bottom-left corner of the screen.

1. Click *Start* > *RICBox* to open the initial RICBox window.

2. Click *Create new project*.

Figure 25. Create New Project in RICBox

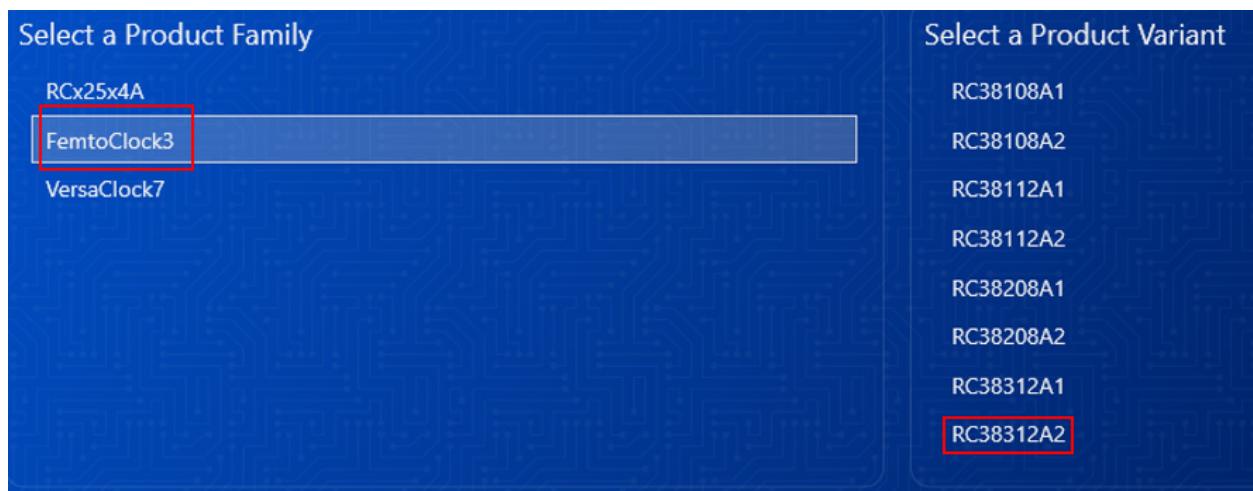

3. Select *FemtoClock3* from the "Select a Product Family" list.

4. Select the product variant to evaluate, then click *OK*. In this example, the *RC38312A2* is selected.

Figure 26. Selecting RC3832A Device GUI in RICBox

5. Follow the on-screen wizard (see [Figure 27](#)) to configure the device for general evaluation starting from "Inputs", then "DPLL", and finally "Outputs".

Figure 27. RICBox Wizard Navigation

6. Click on the *Finish* button after the settings are decided and to review the control panel page.

7. Use the side panel menu buttons (see [Figure 28](#)) to navigate through the GUI for all five separate pages.

Figure 28. RICBox GUI Menu Buttons

### 2.1.3. Configure the Evaluation Board

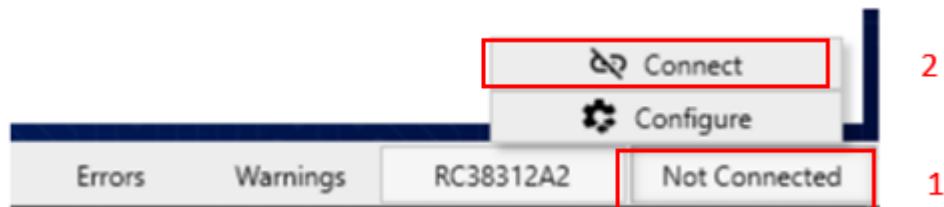

1. To establish communication between the EVB and the GUI, click the *Not Connected* button (1) in the lower right corner, then click *Connect* (2).

Figure 29. Connect to the Device in RICBox

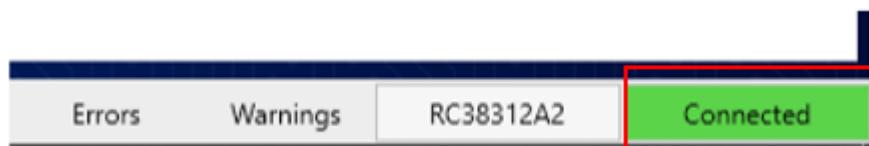

2. Once the RICBox connection is established to the EVB, the *Not Connected* button will change to *Connected*.

Figure 30. Connected Button

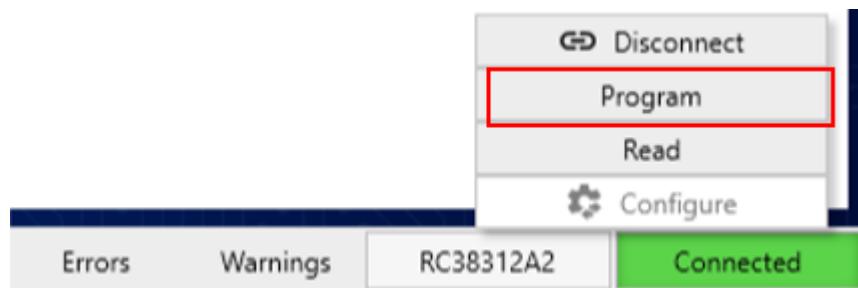

3. Click the *Program* button to write all the changed registers from the GUI to the on-board device. Any register changes made after clicking the *Program* button will occur in real-time and the device will update.

Figure 31. Program Button

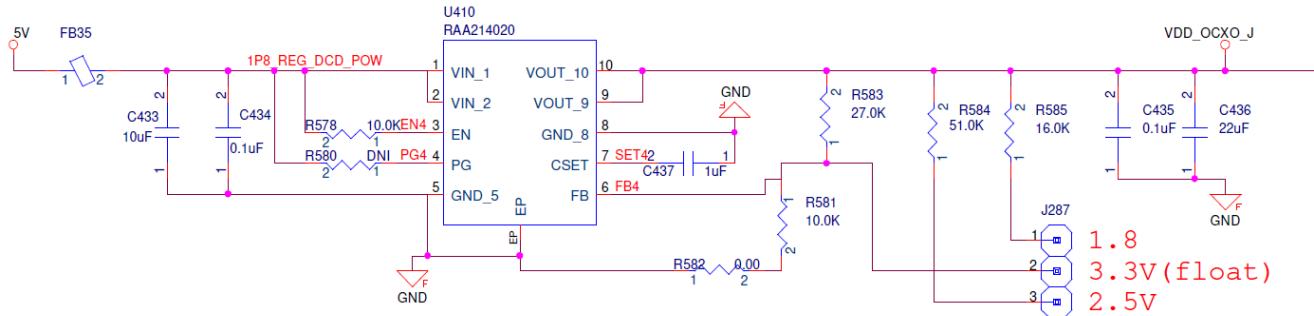

### 3. Board Design

The RC38312A EVB schematic and BOM is available upon request.

**Figure 32. RC38312A Evaluation Board Rev E (top)**

**Figure 33. RC38312A Evaluation Board Rev E (bottom)**

## 4. Typical Performance Graphs

Figure 34. Phase Noise 491.52MHz Output Synthesizer Mode

## 5. Ordering Information

| Part Number  | Description               |

|--------------|---------------------------|

| RC38312A-EVK | RC38312A Evaluation Board |

## 6. Revision History

| Revision | Date         | Description                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.02     | Oct 21, 2025 | <ul style="list-style-type: none"> <li>Added section 1.2.10 and Figure 9.</li> <li>Updated sections 1.2, 1.2.1, 1.2.1.2, 1.2.1.3, 1.2.4, 1.2.5, 1.2.7, 1.2.8.</li> <li>Updated Figure 3, Figure 5, Figure 7, Figure 10, Figure 11, Figure 12, Figure 14, Figure 15, Figure 19, Figure 20, Figure 22, Figure 24, Figure 32, Figure 33.</li> </ul> |

| 1.01     | Mar 3, 2025  | Updated bullet text in section 1.2.1.2 to “Set jumper on J250 between pins 2 and 3” from “Set jumper on J259 between pins 2 and 3”.                                                                                                                                                                                                              |

| 1.00     | Sep 12, 2023 | Initial release                                                                                                                                                                                                                                                                                                                                  |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).