# RA8E2 Group

Evaluation Kit for RA8E2 Microcontroller Group EK-RA8E2 v1 User's Manual

Renesas RA Family RA8 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (https://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### Contact information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.

## General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

#### Renesas EK-RA8E2 Disclaimer

By using this EK-RA8E2, the User accepts the following terms, which are in addition to, and control in the event of disagreement, with Renesas' General Terms and Conditions available at <a href="renesas.com/legal-notices">renesas.com/legal-notices</a>.

The EK-RA8E2 is not guaranteed to be error free, and the entire risk as to the results and performance of the EK-RA8E2 is assumed by the User. The EK-RA8E2 is provided by Renesas on an "as is" basis without warranty of any kind whether express or implied, including but not limited to the implied warranties of good workmanship, fitness for a particular purpose, title, merchantability, and non-infringement of intellectual property rights. Renesas expressly disclaims any implied warranty.

Renesas does not consider the EK-RA8E2 to be a finished product and therefore the EK-RA8E2 may not comply with some requirements applicable to finished products, including, but not limited to recycling, restricted substances and electromagnetic compatibility regulations. Refer to Certifications section, for information about certifications and compliance information for the EK-RA8E2. It is the kit User's responsibility to make sure the kit meets any local requirements applicable to their region.

Renesas or its affiliates shall in no event be liable for any loss of profit, loss of data, loss of contract, loss of business, damage to reputation or goodwill, any economic loss, any reprogramming or recall costs (whether the foregoing losses are direct or indirect) nor shall Renesas or its affiliates be liable for any other direct or indirect special, incidental or consequential damages arising out of or in relation to the use of this EK-RA8E2, even if Renesas or its affiliates have been advised of the possibility of such damages.

Renesas has used reasonable care in preparing the information included in this document, but Renesas does not warrant that such information is error free nor does Renesas guarantee an exact match for every application or parameter to part numbers designated by other vendors listed herein. The information provided in this document is intended solely to enable the use of Renesas products. No express or implied license to any intellectual property right is granted by this document or in connection with the sale of Renesas products. Renesas reserves the right to make changes to specifications and product descriptions at any time without notice. Renesas assumes no liability for any damages incurred by you resulting from errors in or omissions from the information included herein. Renesas cannot verify, and assumes no liability for, the accuracy of information available on another company's website.

#### **Precautions**

This Evaluation Kit is only intended for use in a laboratory environment under ambient temperature and humidity conditions. A safe separation distance should be used between this and any sensitive equipment. Its use outside the laboratory, classroom, study area, or similar such area invalidates conformity with the protection requirements of the Electromagnetic Compatibility Directive and could lead to prosecution.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- Ensure attached cables do not lie across the equipment.

- · Reorient the receiving antenna.

- Increase the distance between the equipment and the receiver.

- · Connect the equipment into an outlet on a circuit different from that which the receiver is connected.

- Power down the equipment when not in use.

- Consult the dealer or an experienced radio/TV technician for help.

Note: It is recommended that wherever possible shielded interface cables are used.

The product is potentially susceptible to certain EMC phenomena. To mitigate against them it is recommended that the following measures be undertaken:

- The user is advised that mobile phones should not be used within 10 m of the product when in use.

- The user is advised to take ESD precautions when handling the equipment.

The Evaluation Kit does not represent an ideal reference design for an end product and does not fulfill the regulatory standards for an end product.

## Renesas RA Family

## EK-RA8E2 v1

## **Contents**

| 1.    | Kit Overview                                    | 5  |

|-------|-------------------------------------------------|----|

| 1.1   | Assumptions and Advisory Notes                  | 8  |

| 2.    | Kit Contents                                    | 9  |

| 3.    | Ordering Information                            | 10 |

| 4.    | Hardware Architecture and Default Configuration | 10 |

| 4.1   | Kit Architecture                                | 10 |

| 4.2   | System Block Diagram                            | 12 |

| 4.3   | Jumper Configuration                            | 13 |

| 4.3.  | 1 Copper Jumpers                                | 13 |

| 4.3.2 | 2 Traditional Pin Header Jumpers                | 13 |

| 4.3.3 | 3 Default Jumper Configuration                  | 13 |

| 4.3.4 | 4 Default Switch Configuration                  | 15 |

| 5.    | System Control and Ecosystem Access Area        | 16 |

| 5.1   | Power                                           | 17 |

| 5.1.  | 1 Power Supply Options                          | 17 |

| 5.1.2 | 2 Power Supply Considerations                   | 18 |

| 5.1.3 | 3 Power-up Behavior                             | 18 |

| 5.2   | Debug and Trace                                 | 19 |

| 5.2.  | 1 Debug On-Board                                | 19 |

| 5.2.2 | 2 Debug In                                      | 21 |

| 5.2.3 | 3 Debug Out                                     | 22 |

| 5.3   | Ecosystem                                       | 22 |

| 5.3.  | 1 Seeed Grove® Connectors                       | 22 |

| 5.3.2 | 2 SparkFun® Qwiic® Connector                    | 23 |

| 5.3.3 | 3 Digilent Pmod <sup>™</sup> Connectors         | 23 |

| 5.3.4 | 4 Arduino™ Connector                            | 25 |

| 5.3.5 | 5 MikroElektronika™ mikroBUS Connector          | 26 |

| 5.4   | Connectivity                                    | 27 |

| 5.4.  | 1 USB Full Speed                                | 27 |

| 5.5   | Miscellaneous                                   | 28 |

| 5.5.  | 1 User and Power LEDs                           | 28 |

| 5.5.2 | 2 User and Reset Switches                       | 29 |

| 5.5.3 | 3 MCU Boot Mode                                 | 29 |

| 6. Spe     | cial Feature Access Area                                                | 30 |

|------------|-------------------------------------------------------------------------|----|

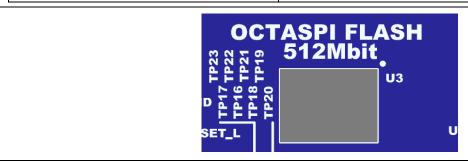

| 6.1 Oct    | o-SPI Flash                                                             | 30 |

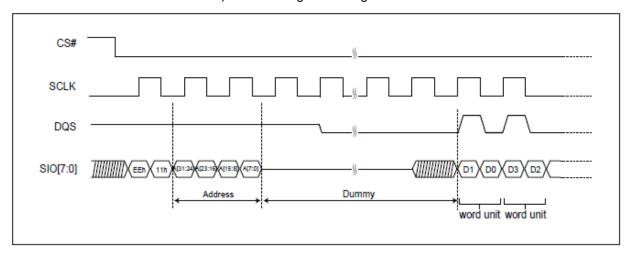

| 6.1.1 O    | SPI Flash Read / Write Byte Order                                       | 31 |

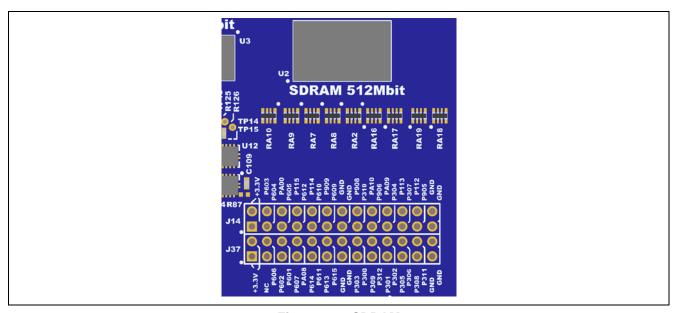

| 6.2 SDI    | RAM                                                                     | 31 |

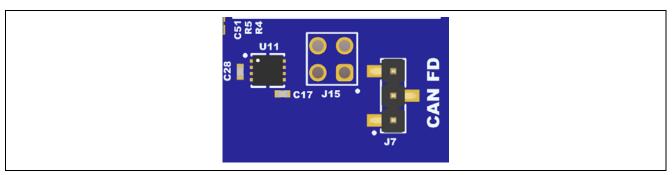

| 6.3 CAI    | N-FD Bus                                                                | 33 |

| 7. MCl     | J Native Pin Access Area                                                | 34 |

| 7.1 Bre    | akout Pin Headers (not populated)                                       | 34 |

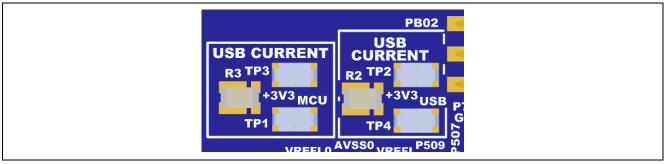

| 7.2 MC     | U and USB Current Measurement                                           | 34 |

| 8. Expa    | ansion Boards                                                           | 36 |

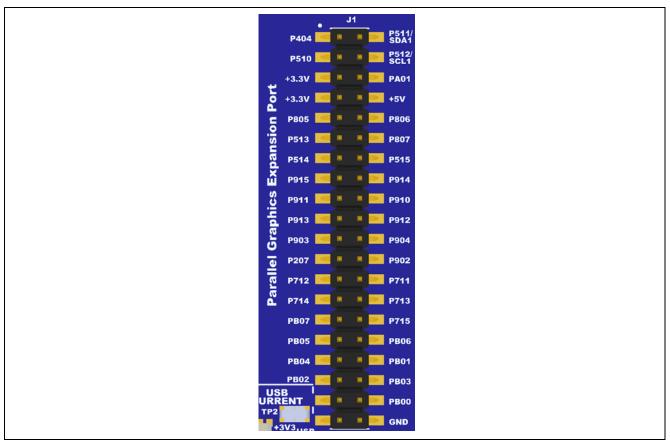

| 8.1 Par    | allel Graphics Expansion Board 2                                        | 36 |

| 8.1.1 Co   | onnecting the Parallel Graphics Expansion Board 2 to the EK-RA8E2 Board | 36 |

| 8.1.2 Pa   | arallel Graphics Expansion Port                                         | 37 |

| 9. Cert    | ifications                                                              | 39 |

| 9.1 EM     | C/EMI Standards                                                         | 39 |

| 9.2 Mat    | terial Selection, Waste, Recycling and Disposal Standards               | 39 |

| 9.3 Saf    | ety Standards                                                           | 39 |

| 10. Desi   | ign and Manufacturing Information                                       | 40 |

| 11. Web    | osite and Support                                                       | 40 |

| Revision   | History                                                                 | 41 |

| Figures    |                                                                         |    |

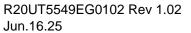

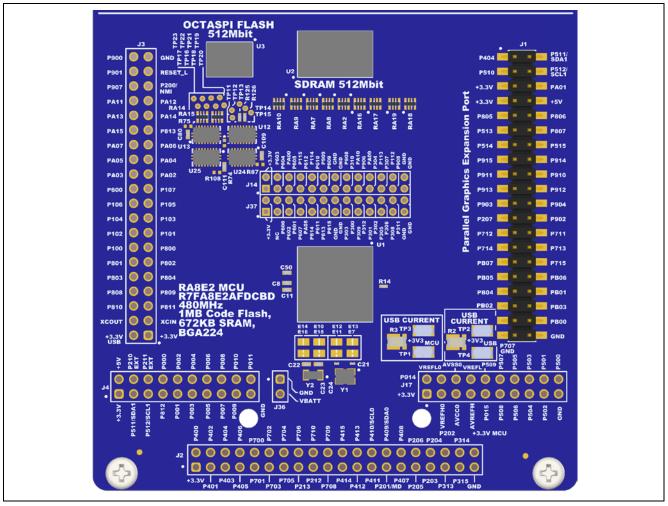

| Figure 1.  | EK-RA8E2 Board Top Side                                                 | 6  |

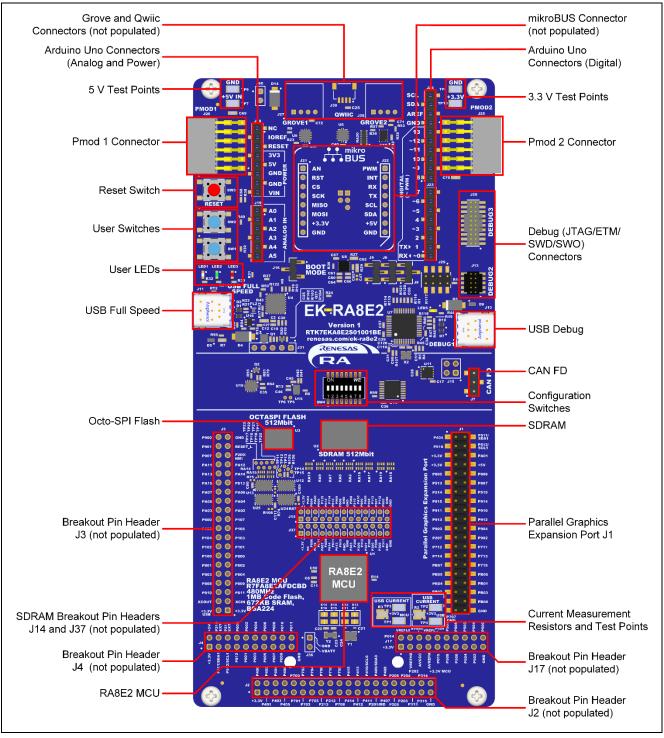

| Figure 2.  | EK-RA8E2 Board Bottom Side                                              | 7  |

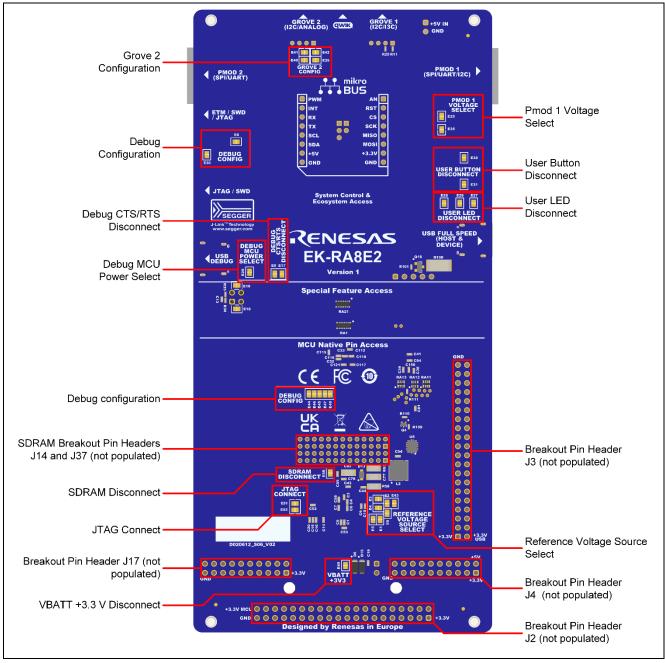

| Figure 3.  | EK-RA8E2 Kit Contents                                                   | 9  |

| Figure 4.  | EK-RA8E2 Board Functional Area Definitions                              | 11 |

| Figure 5.  | EK-RA8E2 Board Block Diagram                                            | 12 |

| Figure 6.  | Copper Jumpers                                                          | 13 |

| Figure 7.  | System Control and Ecosystem Access Area                                | 16 |

| Figure 8.  | Power Supply Options                                                    | 17 |

| Figure 9.  | Test Point Location                                                     | 18 |

| Figure 10  | VBATT supply (J36) Location                                             | 18 |

| Figure 11. | . EK-RA8E2 Debug Interface                                              | 20 |

| Figure 12  | Seeed Grove® and SparkFun® Qwiic® Connector Footprints                  | 23 |

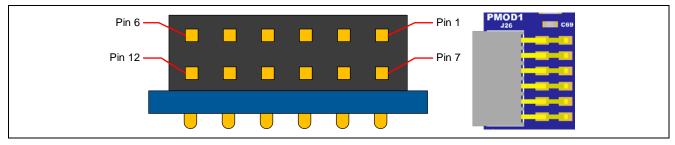

| Figure 13. | Pmod 1 Connector                                                        | 24 |

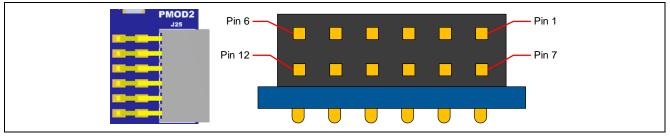

| Figure 14  | Pmod 2 Connector                                                        | 25 |

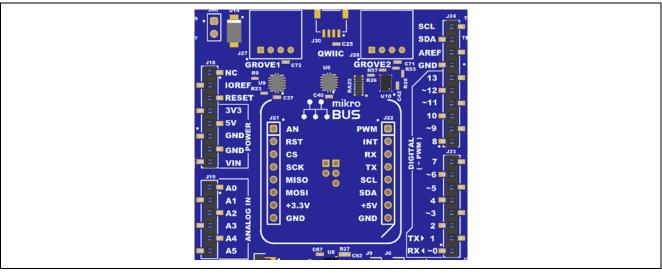

| Figure 15  | . Arduino Uno Connectors                                                | 26 |

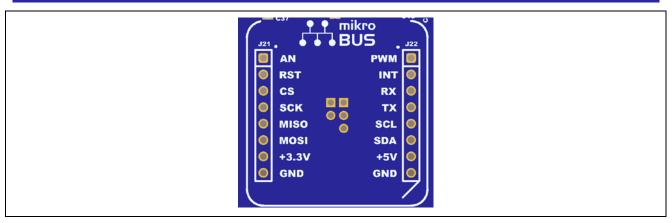

| Figure 16  | . mikroBUS Connector                                                    | 27 |

| Figure 17. | USB Full Speed Connector                                          | 28 |

|------------|-------------------------------------------------------------------|----|

| Figure 18. | User LEDs                                                         | 28 |

| Figure 19. | Power LED                                                         | 28 |

| Figure 20. | Debug LED                                                         | 29 |

| Figure 21. | Reset and User Switches                                           | 29 |

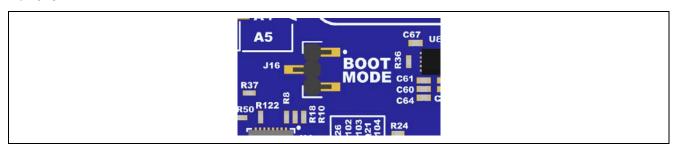

| Figure 22. | Boot Mode                                                         | 29 |

| Figure 23. | Special Feature Access Area                                       | 30 |

| Figure 24. | Octo-SPI Flash                                                    | 30 |

| Figure 25. | Octo-SPI Flash Read Write Byte Order in DOPI mode                 | 31 |

| Figure 26. | SDRAM                                                             | 32 |

| Figure 27. | CAN FD Connector and Chip                                         | 33 |

| Figure 28. | Native Pin Access Area                                            | 34 |

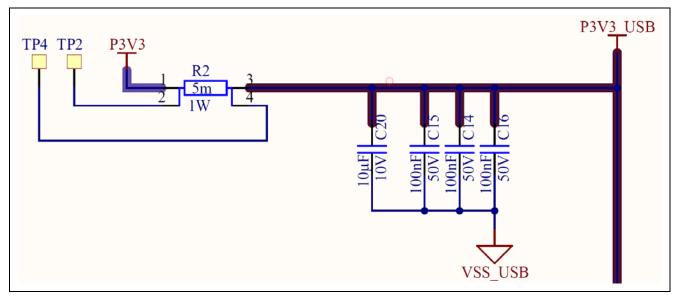

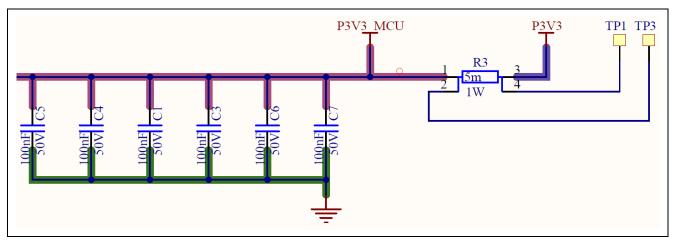

| Figure 29. | RA USB Current Measurement Circuit                                | 35 |

| Figure 30. | RA +3.3 V Current Measurement Circuit                             | 35 |

| Figure 31. | RA MCU and USB Current Measurement                                | 35 |

| Figure 32. | EK-RA8E2 Board Connected with Parallel Graphics Expansion Board 2 | 36 |

| Figure 33. | Parallel Graphics Expansion Port                                  | 38 |

| Tables     |                                                                   |    |

| Table 1.   | Kit Architecture                                                  | 10 |

| Table 2.   | Default Jumper Configuration                                      | 13 |

| Table 3.   | Switch Configuration Definitions (SW4)                            | 15 |

| Table 4.   | Debug Modes                                                       | 19 |

| Table 5.   | Jumper Connection Summary for Different Debug Modes               | 19 |

| Table 6.   | Debug USB Port Assignments                                        | 19 |

| Table 7.   | Debug On-Board Jumper Configuration                               | 20 |

| Table 8.   | Debug In Mode Jumper Configuration                                | 21 |

| Table 9.   | JTAG/SWO/SWD/ETM Debug Port Assignments                           | 21 |

| Table 10.  | JTAG/SWO/SWD Debug Port Assignments                               | 21 |

| Table 11.  | Debug Out Jumper Configuration                                    | 22 |

| Table 12.  | Grove 1 Port Assignments                                          | 22 |

| Table 13.  | Grove 2 Port Assignments                                          | 22 |

| Table 14.  | Qwiic Port Assignments                                            | 23 |

| Table 15.  | Pmod 1 Port Assignments                                           | 23 |

| Table 16.  | Pmod 1 Function Selection                                         | 24 |

| Table 17.  | Pmod 2 Port Assignments                                           | 24 |

| Table 18.  | Arduino Uno Port Assignments                                      | 25 |

| Table 19.  | mikroBUS Assignments                                              | 26 |

| Table 20.  | USB Full Speed Port Assignments                                   | 27 |

| Table 21.  | EK-RA8E2 Board LED Functions                                      | 28 |

| Table 22. | EK-RA8E2 Board Switches                                     | 29 |

|-----------|-------------------------------------------------------------|----|

| Table 23. | Octo-SPI Flash Assignments                                  | 30 |

| Table 24. | SDRAM Assignments                                           | 31 |

| Table 25. | CAN FD Bus Connections Between U11 and RA8E2                | 33 |

| Table 26. | CAN FD Port Assignments                                     | 33 |

| Table 27. | Parallel Graphics Expansion Port Assignments                | 37 |

| Table 28. | EK-RA8E2 Board Design Package Contents                      | 40 |

| Table 29. | Parallel Graphics Expansion Board 2 Design Package Contents | 40 |

#### 1. Kit Overview

The EK-RA8E2, an Evaluation Kit for RA8E2 MCU Group, enables users to seamlessly evaluate the features of the RA8E2 MCU group and develop embedded systems applications using Flexible Software Package (FSP) and e<sup>2</sup> studio IDE. The users can utilize rich on-board features along with their choice of popular ecosystems add-ons to bring their big ideas to life.

The EK-RA8E2 board features the RA8E2 MCU, OSPI Flash, SDRAM, CAN-FD and a Parallel Graphics Expansion Port.

The key features of the EK-RA8E2 board are categorized in three groups (consistent with the architecture of the kit, with a few exceptions) as follows:

#### **MCU Native Pin Access**

- R7FA8E2AFDCBD MCU (referred to as RA MCU)

- 480 MHz, Arm<sup>®</sup> Cortex<sup>®</sup>-M85 core

- 1 MB Code Flash, 672 kB SRAM

- 224 pins, BGA package

- Native pin access through 2 x 20-pin, and 2 x 40-pin headers (not populated)

- MCU current measurement points for precision current consumption measurement

- Multiple clock sources RA MCU oscillator and sub-clock oscillator crystals, providing precision 24.000 MHz and 32,768 Hz reference clocks. Additional low-precision clocks are available internal to the RA MCU

#### System Control and Ecosystem Access

- USB Full Speed Host and Device (USB-C connector)

- Three 5 V input sources

- USB (Debug, Full Speed)

- External power supply (using surface mount clamp test points and power input vias)

- Three Debug modes

- Debug on-board (SWD and JTAG)

- Debug in (ETM, SWD, SWO, and JTAG)

- Debug out (SWD, SWO, and JTAG)

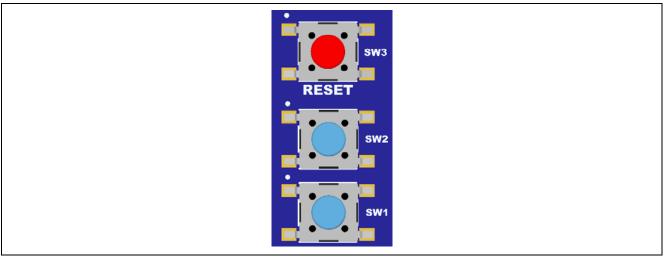

- User LEDs and buttons

- Three User LEDs (Red, Blue, Green)

- Power LED (white) indicating availability of regulated power

- Debug LED (yellow) indicating the debug connection

- Two User buttons

- One Reset button

- Five most popular ecosystems expansions

- Two Seeed Grove<sup>®</sup> system (I<sup>2</sup>C/Analog) connectors (not populated)

- SparkFun<sup>®</sup> Qwiic<sup>®</sup> connector (not populated)

- Two Digilent Pmod<sup>™</sup> (SPI, UART and I<sup>2</sup>C) connectors

- Arduino™ (Uno R3) connector

- MikroElektronika<sup>TM</sup> mikroBUS connector (not populated)

- MCU boot configuration jumper

#### Special Feature Access

- 64 MB (512 Mb) External Octo-SPI NOR Flash (present in the MCU Native Pin Access area)

- 64 MB (512 Mb) SDRAM (present in the MCU Native Pin Access area)

- Parallel Graphics Expansion Port (present in the MCU Native Pin Access area)

- CAN-FD

- Configuration Switch (SW4)

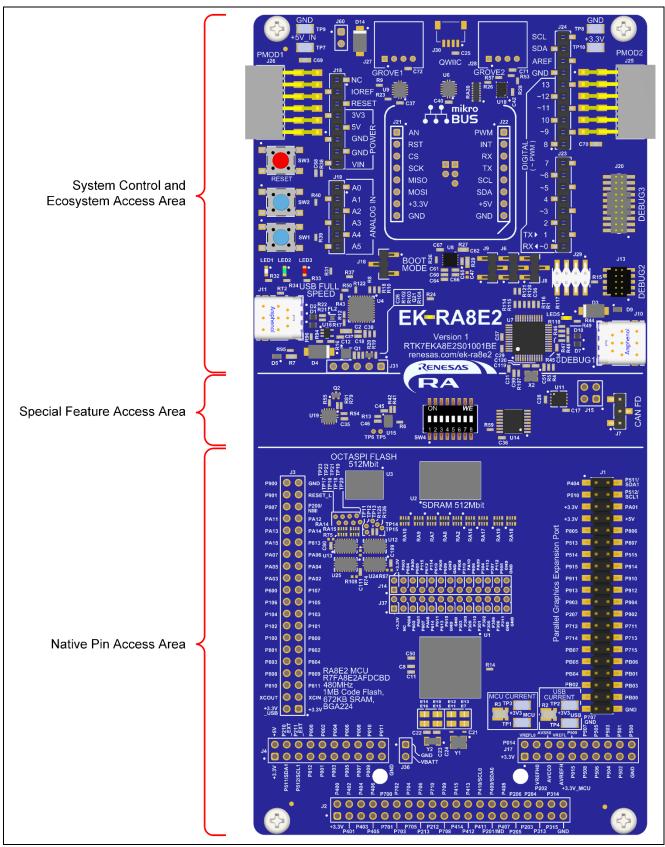

Figure 1. EK-RA8E2 Board Top Side

Figure 2. EK-RA8E2 Board Bottom Side

## 1.1 Assumptions and Advisory Notes

- 1. It is assumed that the user has a basic understanding of microcontrollers and embedded systems hardware.

- 2. It is recommended that the user refers to the *EK-RA8E2 Quick Start Guide* to get acquainted with the kit and the Quick Start example project that EK-RA8E2 board comes pre-programmed with.

- 3. Flexible Software Package (FSP) and Integrated Development Environment (IDE) such as e<sup>2</sup> studio are required to develop embedded applications on EK-RA8E2 kit.

- 4. Instructions to download and install software, import example projects, build them and program the EK-RA8E2 board are provided in the quick start guide.

- 5. The MCU fitted to the EK board may not contain the latest version of the on-chip boot firmware.

#### 2. Kit Contents

The following components are included in the kit:

- 1. EK-RA8E2 v1 board

- 2. USB-C to USB-C cable

- 3. USB-A to USB-C cable

- 4. USB-C to USB-A female host cable

- 5. Parallel Graphics Expansion Board 2

- 6. Display mounting hardware (spacers and fixing screws)

Figure 3. EK-RA8E2 Kit Contents

## 3. Ordering Information

EK-RA8E2 v1 kit orderable part number: RTK7EKA8E2S01001BE

Note: 1. The underlined character in the orderable part number represents the kit version.

2. The Parallel Graphics Expansion Board 2 orderable part number: RTKAPPLCDPS02001BE

#### Dimensions:

- 1. EK-RA8E2 board: 84 mm (width) x 175 mm (length)

- 2. Parallel Graphics Expansion Board 2: 95mm (width) x 140mm (length)

## 4. Hardware Architecture and Default Configuration

#### 4.1 Kit Architecture

The EK-RA8E2 board is designed with three sections or areas to help shorten the learning curve of users and maximize the design and knowledge reuse among similar kits. The contents of these three areas are conceptually standardized among similar kits.

Table 1. Kit Architecture

| Kit area                                       | Area features                                                                                                                           | Area present on all similar kits | Functionality is:                   |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|

| MCU Native Pin<br>Access Area                  | RA MCU, breakout pin headers for all MCU I/O and power, current measurement Parallel Graphics Expansion Port, Octo-SPI Flash, and SDRAM | Yes                              | MCU dependent                       |

| Special Feature<br>Access Area                 | Configuration Switches MCU special features: CAN-FD                                                                                     | No                               | MCU dependent                       |

| System Control<br>and Ecosystem<br>Access Area | Power, Debug MCU, User LEDs and buttons, reset, ecosystem connectors, USB Full Speed Host and Device, and Boot configuration            | Yes                              | Same or similar across similar kits |

**Note:** The Octo-SPI Flash, SDRAM and Parallel Graphics Expansion Port are among the Special Feature Access features. Normally, they would be in the Special Feature Access Area, however, to optimize the layout, routing, and performance, they are placed in the MCU Native Pin Access area.

Figure 4. EK-RA8E2 Board Functional Area Definitions

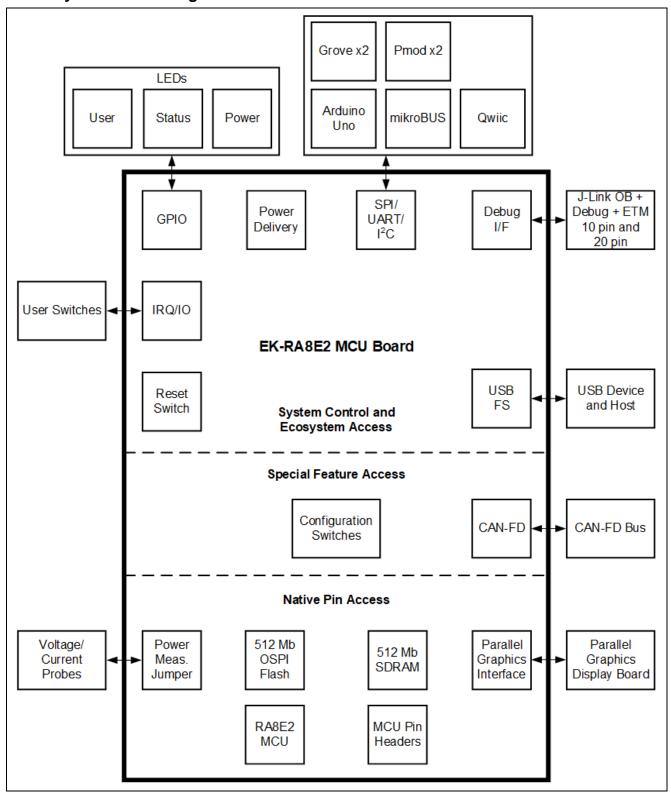

## 4.2 System Block Diagram

Figure 5. EK-RA8E2 Board Block Diagram

#### 4.3 Jumper Configuration

Two types of jumpers are provided on the EK-RA8E2 board.

- 1. Copper jumpers (trace-cut type and solder bridge type)

- 2. Traditional pin header jumpers

The following sections describe each type and their default configuration.

#### 4.3.1 Copper Jumpers

Copper jumpers are of two types, designated trace-cut and solder-bridge.

A **trace-cut jumper** is provided with a narrow copper trace connecting its pads. The silk screen overlay printing around a trace-cut jumper is a solid box. To isolate the pads, cut the trace between pads adjacent to each pad, then remove the connecting copper foil either mechanically or with the assistance of heat. Once the etched copper trace is removed, the trace-cut jumper is turned into a solder-bridge jumper for any later changes.

A **solder-bridge** jumper is provided with two isolated pads that may be joined together by one of three methods:

- Solder may be applied to both pads to develop a bulge on each and the bulges joined by touching a soldering iron across the two pads.

- A small wire may be placed across the two pads and soldered in place.

- A SMT resistor, size 0805, 0603, or 0402, may be placed across the two pads and soldered in place. A zero-ohm resistor shorts the pads together.

For any copper jumper, the connection is considered **closed** if there is an electrical connection between the pads (default for trace-cut jumpers.) The connection is considered **open** if there is no electrical connection between the pads (default for the solder-bridge jumpers.)

Figure 6. Copper Jumpers

#### 4.3.2 Traditional Pin Header Jumpers

These jumpers are traditional small pitch jumpers that require an external shunt to open/close them. The traditional pin jumpers on the EK-RA8E2 board are 2 mm pitch headers and require compatible 2 mm shunt jumpers.

#### 4.3.3 Default Jumper Configuration

The following table describes the default configuration for each jumper on the EK-RA8E2 board. This includes copper jumpers (Ex designation) and traditional pin jumpers (Jx designation).

The Circuit Group for each jumper is the designation found in the board schematic (available in the Design Package). Functional details for many of the listed jumpers may be found in sections associated with each functional area of the kits.

**Table 2. Default Jumper Configuration**

| Location | Circuit Group | Default Open/Closed | Function                                    |

|----------|---------------|---------------------|---------------------------------------------|

| J6       | J-Link OB     | Jumper on pins 2-3  | Configures J-Link OB connection to MCU mode |

| J8       | J-Link OB     | Jumper on pins 1-2  | Configures the MCU for normal operation     |

| J9       | J-Link OB     | Jumper on pins 2-3  | Configures RA4M2 RESET_L for on-board       |

|          |               |                     | debugger mode                               |

| J15      | CAN-FD        | Not Fitted          | Replacement for E18 and E19 when both cut   |

| J16      | MCU Boot Mode | Jumper on pins 2-3  | Configures the MCU for normal boot mode     |

| Location | Circuit Group              | Default Open/Closed | Function                                               |

|----------|----------------------------|---------------------|--------------------------------------------------------|

| J29      | J-Link OB                  | Jumper on pins 1-2  | Connects the J-Link OB debugger to the RA MCU          |

|          |                            | Jumper on pins 3-4  |                                                        |

|          |                            | Jumper on pins 5-6  |                                                        |

|          |                            | Jumper on pins 7-8  |                                                        |

| E1       | MCU Power                  | Closed              | Connects VREFL to GND                                  |

| E2       | MCU Power                  | Closed              | Connects VREFH to +3.3 V                               |

| E3       | MCU Power                  | Closed              | Connects AVCC0 to +3.3 V                               |

| E4       | MCU Power                  | Closed              | Connects AVSS0 to GND                                  |

| E5       | MCU Power                  | Closed              | Connects VREFL0 to GND                                 |

| E6       | MCU Power                  | Closed              | Connects VREFH0 to +3.3 V                              |

| E7       | MCU Clock                  | Closed              | Connects P212/EXTAL to 24 MHz crystal                  |

| E8       | Debug                      | Closed              | Connects debugger JLOB_TRST to JTAG connectors         |

| E9       | J-Link Virtual<br>COM Port | Closed              | Connects P709 (RTS) to Debugger P408                   |

| E10      | MCU Clock                  | Open                | Connects XCIN to J3 pin 3                              |

| E11      | MCU Clock                  | Closed              | Connects P213/XTAL to 24 MHz crystal                   |

| E12      | MCU Clock                  | Open                | Connects P213/XTAL to J2 pin 15                        |

| E13      | MCU Clock                  | Open                | Connects P212/EXTAL J2 pin 17                          |

| E14      | MCU Clock                  | Open                | Connects XCOUT to J3 pin 4                             |

| E15      | MCU Clock                  | Closed              | Connects XCIN/P215 to 32.768 KHz crystal               |

| E16      | MCU Clock                  | Closed              | Connects XCOUT/P214 to 32.768 KHz crystal              |

| E17      | J-Link Virtual<br>COM Port | Closed              | Connects P710 (CTS) to Debugger P409                   |

| E18      | CAN-FD                     | Closed              | Connects to CAN-FD L to terminating network            |

| E19      | CAN-FD                     | Closed              | Connects to CAN-FD H to terminating network            |

| E25      | Pmod1                      | Closed              | Connects PMOD1 +3.3V to pins 6 and 12                  |

| E26      | User LED                   | Closed              | Connects P406 to User LED2                             |

| E27      | User LED                   | Closed              | Connects P205 to User LED1                             |

| E28      | User LED                   | Closed              | Connects P405 to User LED3                             |

| E29      | Debug MCU<br>Power         | Closed              | Connects the Debug MCU power to +3.3 V                 |

| E30      | Debugger                   | Closed              | Connects the JTAG GND Detect pin on J20 and J13 to GND |

| E31      | User Switch                | Closed              | Connects P001 to User Switch SW1                       |

| E32      | User Switch                | Closed              | Connects P008 to User Switch SW2                       |

| E35      | Pmod1                      | Open                | Connects PMOD1 +5V pins 6 and 12                       |

| E39      | Grove 2                    | Closed              | Connects I <sup>2</sup> C SCL1 to Grove 2 pin 1        |

| E40      | Grove 2                    | Closed              | Connects I <sup>2</sup> C SDA1 to Grove 2 pin 2        |

| E41      | Grove 2                    | Open                | Connects P005 (AN001) to Grove 2 pin 2                 |

| E42      | Grove 2                    | Open                | Connects P002 (AN102) to Grove 2 pin 1                 |

| E43      | Arduino                    | Closed              | Connects VREFH to the Arduino AREF pin                 |

| E44      | Debugger                   | Open                | Connects P304 to J20 pin 20                            |

| E45      | Debugger                   | Open                | Connects P305 to J20 pin 18                            |

| E46      | Debugger                   | Open                | Connects P306 to J20 pin 16                            |

| E47      | Debugger                   | Open                | Connects P307 to J20 pin 14                            |

| E48      | Debugger                   | Open                | Connects P308 to J20 pin 12                            |

| E49      | MCU Power                  | Closed              | Connects VBATT to +3.3_MCU                             |

| E50      | SDRAM                      | Closed              | Connects P115 to SDRAM_CS_L                            |

| E51      | Pin Headers                | Open                | Connects P210 to J4 pin 4                              |

| E52      | Pin Headers                | Open                | Connects P211 to J4 pin 6                              |

## 4.3.4 Default Switch Configuration

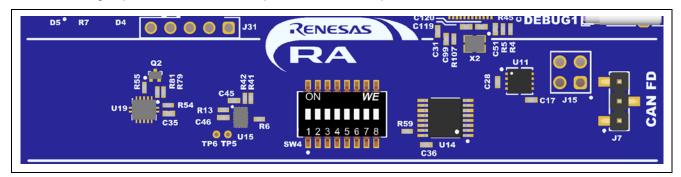

The EK-RA8E2 features an  $I^2C$  I/O Port Expander (PI4IOE5V6408) at U15 and has the  $I^2C$  address 0x43. The port expander is connected to the configuration switches SW4.

The following table describes the function and default configuration for each switch that selects the operational peripheral pins on the EK-RA8E2 board.

The Circuit Group for each switch is the designation found in the board schematic (available in the Design Package). Functional details for many of the listed switches may be found in sections associated with each functional area of the kits.

Table 3. Switch Configuration Definitions (SW4)

| Switch | Switch<br>Definition | Position<br>(Default) | Function                       | Conflict              |

|--------|----------------------|-----------------------|--------------------------------|-----------------------|

| SW4-1  | Pmod 1 Mode          | OFF                   | Please see Table 16            | Please see Table 16   |

|        | Select 1             | ON                    |                                |                       |

| SW4-2  | Pmod 1 Mode          | OFF                   |                                |                       |

|        | Select 2             | ON                    |                                |                       |

| SW4-3  | Octo-SPI             | OFF                   | Octo-SPI Active                | Pmod 1 (SPI and UART) |

|        | Select               | ON                    | Octo-SPI Inactive              | -                     |

| SW4-4  | Pmod 2 Mode          | OFF                   | SPI mode selected              | -                     |

|        | Select               | ON                    | UART mode selected             | -                     |

| SW4-5  | Test Point 5         | OFF                   | Connect Test Point 5 to +3.3 V | -                     |

|        |                      | ON                    | Connect Test Point 5 to GND    | -                     |

| SW4-6  | Test Point 6         | OFF                   | Connect Test Point 6 to +3.3 V | -                     |

|        |                      | ON                    | Connect Test Point 6 to GND    | -                     |

| SW4-7  | USBFS Role<br>Toggle | OFF                   | Toggles USBFS between Host and | -                     |

|        |                      | ON                    | Device mode                    | -                     |

| SW4-8  | Not<br>Connected     | OFF                   | -                              | -                     |

|        |                      | ON                    |                                | -                     |

Note: There are no conflicting settings for SW4.

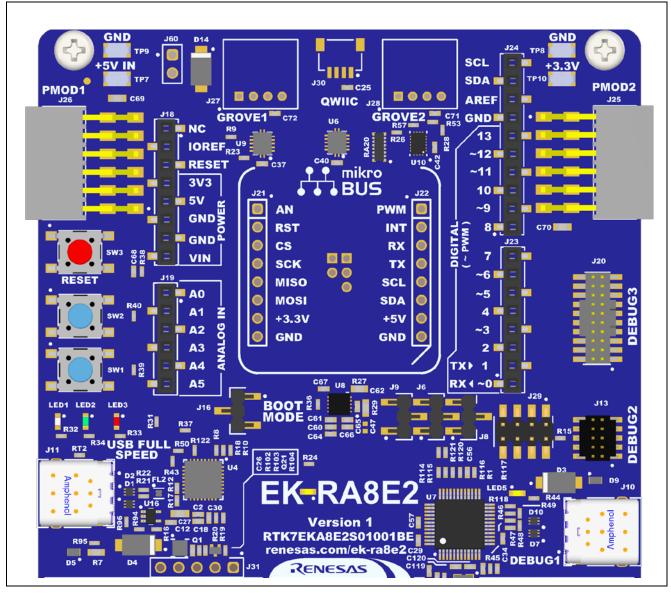

## 5. System Control and Ecosystem Access Area

The following figure shows the System Control and Ecosystem Access area on the EK-RA8E2 board. Subsequent sections detail the features and functionality provided in the area.

Figure 7. System Control and Ecosystem Access Area

#### 5.1 Power

The EK-RA8E2 kit is designed for +5 V operation. An on-board Low Dropout Regulator (ISL80103IRAJZ) is used to convert the 5 V supply to a 3.3 V supply. The +3.3 V supply is used to power the RA MCU and other peripheral features.

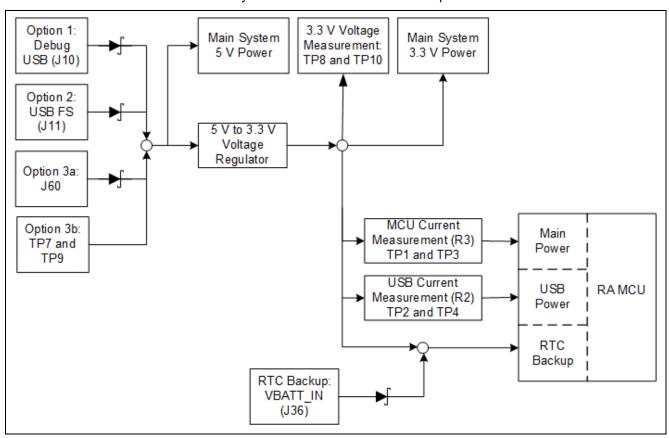

## 5.1.1 Power Supply Options

This section describes the different ways in which EK-RA8E2 kit can be powered.

Figure 8. Power Supply Options

#### 5.1.1.1 Option 1: Debug USB

5 V may be supplied from an external USB host to the USB Debug connector (J10) labelled DEBUG1 on the board. Power from this source is connected to the main system 5 V power. Reverse current protection is provided between this connector and the main system 5 V power.

#### 5.1.1.2 Option 2: USB Full Speed

5 V may be supplied from an external USB host to the USB Full Speed connector (J11) labelled USB FULL SPEED on the board. Power from this source is connected to the main system 5 V power. Reverse current protection is provided between this connector and the main system 5 V power.

#### 5.1.1.3 Option 3: 5 V Test Points

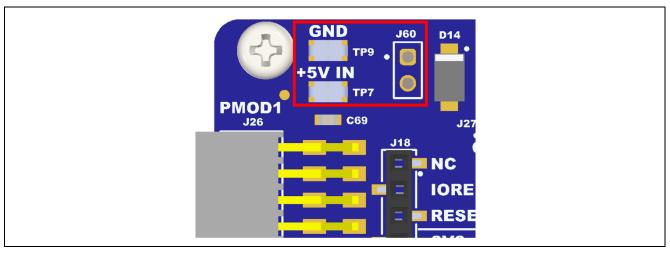

5 V may be supplied from an external power supply to test points on the board. TP7 (5 V) and TP9 (GND) are loop-style test points, and J60 provides large via style test points that can accommodate a 0.1" pin header or connector. The two types of test points are electrically equivalent, and both are provided for user convenience. Power from this source is connected to the main system 5 V power. These test points can be found at the top left of the board above Pmod1.

Reverse current protection is provided at J60-1, whereas TP7 directly connects to the 5V input pin of the voltage regulator U8 and to the Main System 5V Power. Care must be taken before applying an external supply to this test point to ensure that that the polarity is correct. Failure to do so could result in damage to components on the PCB.

Figure 9. Test Point Location

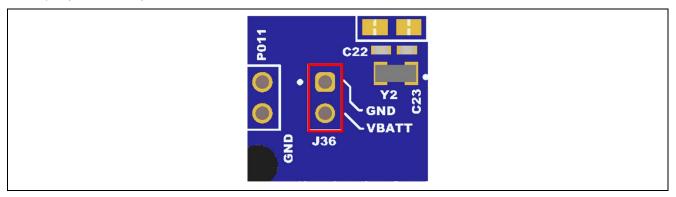

## 5.1.1.4 RTC Backup: VBATT Supply

The MCU provides a battery backup function that maintains power to certain MCU peripherals in the event of a power loss (for example the Real Time Clock). A battery (lithium coin cell etc.) can be connected to J36 (not fitted) to provide this power. For further details see the MCU hardware manual.

Figure 10. VBATT supply (J36) Location

#### 5.1.2 Power Supply Considerations

The on-board LDO regulator which supplies +3.3 V has a built-in current limit of 3.0 A. Make sure the total current required by the RA MCU, any active on-board features, and any connected peripheral devices does not exceed this limit.

Note: The total current available from a typical enumerated USB host is 500 mA maximum. Depending on the configuration of the kit, multiple power sources may be required.

#### 5.1.3 Power-up Behavior

When powered, the white LED near the center of the board (the "dash" in the EK-RA8E2 name) will light up. For more details on initial power up behavior, see the *EK-RA8E2 Quick Start Guide*.

## 5.2 Debug and Trace

The EK-RA8E2 board supports the following three debug modes.

Table 4. Debug Modes

| Debug Modes        | Debugger MCU<br>(the device that<br>connects to the<br>IDE on PC) | Target MCU<br>(the device that<br>is being<br>debugged) | Debugging<br>Interface/Protocol | Connector Used                                                                   |

|--------------------|-------------------------------------------------------------------|---------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|

| Debug on-<br>board | RA4M2<br>(on-board)                                               | RA8E2<br>(on-board)                                     | SWD, JTAG                       | USB-C (J10)                                                                      |

| Debug in           | External                                                          | RA8E2                                                   | SWD, SWO, ETM,                  | 20-pin connector (J20)                                                           |

|                    | debugging tools                                                   | (on-board)                                              | JTAG                            | or 10-pin connector (J13)                                                        |

| Debug out          | RA4M2<br>(on-board)                                               | Any external RA<br>MCU                                  | SWD, SWO, JTAG                  | USB-C (J10) plus either 20-<br>pin connector (J20) or 10-<br>pin connector (J13) |

#### Notes:

- See Table 6 for the Debug USB connector pin definition.

- See Table 9 for the 20-pin JTAG connector pin definition.

- See Table 10 for the 10-pin JTAG connector pin definition.

The following table summarizes the jumper configuration for each of the debug modes.

Table 5. Jumper Connection Summary for Different Debug Modes

| Debug Modes    | J8                 | J9                 | J29                |

|----------------|--------------------|--------------------|--------------------|

| Debug on-board | Jumper on pins 1-2 | Jumper on pins 2-3 | Jumpers on pins    |

|                |                    |                    | 1-2, 3-4, 5-6, 7-8 |

| Debug in       | Jumper on pins 1-2 | Jumper on pins 1-2 | Jumpers on pins    |

|                |                    |                    | 1-2, 3-4, 5-6, 7-8 |

| Debug out      | Jumper on pins 2-3 | Jumper on pins 2-3 | All pins open      |

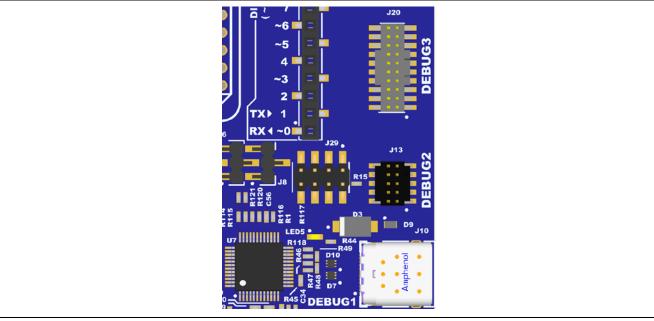

#### 5.2.1 Debug On-Board

The on-board debug functionality is provided using Renesas RA4M2 Debug MCU and SEGGER J-Link® firmware. Debug USB-C connector (J10) connects the RA4M2 Debug MCU to an external USB Full Speed Host, allowing re-programming and debugging of the target RA MCU firmware. This connection is the default debug mode for the EK-RA8E2 board.

The RA4M2 Debug MCU connects to the target RA MCU using the SWD interface or the JTAG interface.

Table 6. Debug USB Port Assignments

| Debug US | B Port Assignments | EK-RA8E2     |

|----------|--------------------|--------------|

| Pin      | Description        | Signal/Bus   |

| J10-A1   | GND                | GND          |

| J10-A2   | TX1+               | N.C.         |

| J10-A3   | TX1-               | N.C.         |

| J10-A4   | VBUS               | +5V_USB_DBG  |

| J10-A5   | CC1                | USB_JLOB_CC1 |

| J10-A6   | DA+                | USB_JLOB_P   |

| J10-A7   | DA-                | USB_JLOB_N   |

| J10-A8   | SBU1               | N.C.         |

| J10-A9   | VBUS               | +5V_USB_DBG  |

| J10-A10  | RX2-               | N.C.         |

| J10-A11  | RX2+               | N.C.         |

| J10-A12  | GND                | GND          |

| J10-B1   | GND                | GND          |

| Debug US | B Port Assignments | EK-RA8E2     |

|----------|--------------------|--------------|

| Pin      | Description        | Signal/Bus   |

| J10-B2   | TX2+               | N.C.         |

| J10-B3   | TX2-               | N.C.         |

| J10-B4   | VBUS               | +5V_USB_DBG  |

| J10-B5   | CC2                | USB_JLOB_CC2 |

| J10-B6   | DB+                | USB_JLOB_P   |

| J10-B7   | DB-                | USB_JLOB_N   |

| J10-B8   | SBU2               | N.C.         |

| J10-B9   | VBUS               | +5V_USB_DBG  |

| J10-B10  | RX1-               | N.C.         |

| J10-B11  | RX1+               | N.C.         |

| J10-B12  | GND                | GND          |

| J10-S1   | SHIELD             | GND          |

| J10-S2   | SHIELD             | GND          |

| J10-S3   | SHIELD             | GND          |

| J10-S4   | SHIELD             | GND          |

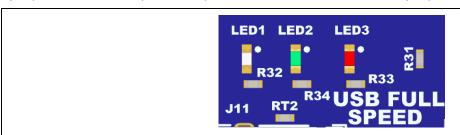

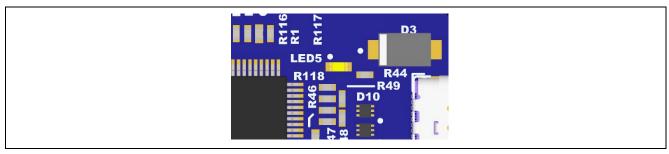

A yellow indicator, LED5, shows the visual status of the debug interface. When the EK-RA8E2 board is powered on, and LED5 is blinking, it indicates that the RA4M2 Debug MCU is not connected to a programming host. When LED5 is on solid, it indicates that the RA4M2 Debug MCU is connected to a programming interface.

To configure the EK-RA8E2 board to use the Debug On-Board mode, configure the jumpers using the following table.

Table 7. Debug On-Board Jumper Configuration

| Location | Default Open/Closed                | Function                                                        |

|----------|------------------------------------|-----------------------------------------------------------------|

| J8       | Jumper on pins 1-2                 | Target RA MCU RESET_L connected to debugger JTAG_RESET_L        |

| J9       | Jumper on pins 2-3                 | RA4M2 Debug MCU in normal operation mode                        |

| J29      | Jumpers on pins 1-2, 3-4, 5-6, 7-8 | Target RA MCU debug signals connected to the debugger interface |

Figure 11. EK-RA8E2 Debug Interface

## 5.2.2 Debug In

One 20-pin Cortex® Debug Connector at J20 supports JTAG, SWD, SWO and ETM (TRACE) debug. One 10-pin Cortex® Debug Connector at J13 supports JTAG, SWD and SWO. Either of these connectors may be used for external debug of the target RA MCU.

To configure the EK-RA8E2 board to use the Debug In mode, configure the jumpers as shown in Table 8.

Table 8. Debug In Mode Jumper Configuration

| Location | Default Open/Closed          | Function                                           |

|----------|------------------------------|----------------------------------------------------|

| J8       | Jumper on pins 1-2           | Target RA MCU RESET_L connected to debug RESET_L   |

| J9       | Jumper on pins 1-2           | RA4M2 Debug MCU is held in RESET                   |

| J29      | Jumpers on pins 1-2, 3-4, 5- | Target RA MCU debug signals connected to the debug |

|          | 6, 7-8                       | interface                                          |

Table 9. JTAG/SWO/SWD/ETM Debug Port Assignments

| JTAG Po | rt Assignments | EK-RA8E2     |              |                       |

|---------|----------------|--------------|--------------|-----------------------|

| Pin     | JTAG Pin Name  | SWD Pin Name | ETM Pin Name | Signal/Bus            |

| J20-1   | Vtref          | Vtref        | Vtref        | +3V3                  |

| J20-2   | TMS            | SWDIO        | TMS / SWDIO  | P210 / SWDIO / TMS    |

| J20-3   | GND            | GND          | GND          | GND                   |

| J20-4   | TCK            | SWCLK        | TCK / SWCLK  | P211 / SWCLK / TCK    |

| J20-5   | GND            | GND          | GND          | GND                   |

| J20-6   | TDO            | SWO          | TDO / SWO    | P209 / TDO            |

| J20-7   | Key            | Key          | Key          | N.C.                  |

| J20-8   | TDI            | N/A          | TDI / N/A    | P208 / TDI            |

| J20-9   | GNDDetect      | GNDDetect    | GNDDetect    | GND (cut E30 to open) |

| J20-10  | nSRST          | nSRST        | nSRST        | RESET_L               |

| J20-11  | GND            | GND          | GND          | GND                   |

| J20-12  | N/A            | N/A          | TCLK         | P308 / TCLK*          |

| J20-13  | GND            | GND          | GND          | GND                   |

| J20-14  | N/A            | N/A          | TDATA0       | P307 / TDATA0*        |

| J20-15  | GND            | GND          | GND          | GND                   |

| J20-16  | N/A            | N/A          | TDATA1       | P306 / TDATA1*        |

| J20-17  | GND            | GND          | GND          | GND                   |

| J20-18  | N/A            | N/A          | TDATA2       | P305 / TDATA2*        |

| J20-19  | GND            | GND          | GND          | GND                   |

| J20-20  | N/A            | N/A          | TDATA3       | P304 / TDATA3*        |

<sup>\*</sup> Option to Isolate with E pad

Table 10. JTAG/SWO/SWD Debug Port Assignments

| JTAG Port | t Assignments |              | EK-RA8E2              |

|-----------|---------------|--------------|-----------------------|

| Pin       | JTAG Pin Name | SWD Pin Name | Signal/Bus            |

| J13-1     | Vtref         | Vtref        | +3V3                  |

| J13-2     | TMS           | SWDIO        | P210/SWDIO/TMS        |

| J13-3     | GND           | GND          | GND                   |

| J13-4     | TCK           | SWCLK        | P211/SWCLK/TCK        |

| J13-5     | GND           | GND          | GND                   |

| J13-6     | TDO           | SWO          | P209/TDO              |

| J13-7     | Key           | Key          | N.C.                  |

| J13-8     | TDI           | N/A          | P208/TDI              |

| J13-9     | GNDDetect     | GNDDetect    | GND (cut E30 to open) |

| J13-10    | nSRST         | nSRST        | RESET_L               |

Note: The Cortex® Debug Connector is fully described in the Arm® CoreSight™ Architecture Specification.

#### 5.2.3 Debug Out

The EK-RA8E2 board can be configured to use the RA4M2 Debug MCU to debug target RA MCU on an external board.

A yellow indicator, LED5, shows the visual status of the debug interface. When the EK-RA8E2 board is powered on, and LED5 is blinking, this indicates that the RA4M2 Debug MCU is not connected to a programming host. When LED5 is on solid, this indicates that the RA4M2 Debug MCU is connected to a programming interface. When the debug interface is actively in use, the LED will flicker randomly.

To configure the EK-RA8E2 board to use the Debug Out mode, configure the jumpers according to the following table.

**Table 11. Debug Out Jumper Configuration**

| Location | Default Open/Closed | Function                                                               |

|----------|---------------------|------------------------------------------------------------------------|

| J8       | Jumper on pins 2-3  | On-board RA MCU is held in RESET                                       |

| J9       | Jumper on pins 2-3  | RA4M2 Debug MCU in normal operation mode                               |

| J29      | All jumpers removed | Disconnects the on-board RA MCU debug signals from the Debug Interface |

## 5.3 Ecosystem

The System Control and Ecosystem area provides users the option to simultaneously connect several third-party add-on modules compatible with five most popular ecosystems using the following connectors:

- 1. Two Seeed Grove® system (I<sup>2</sup>C /Analog) connectors (not populated)

- 2. SparkFun® Qwiic® connector (not populated)

- 3. Two Digilent Pmod™ (SPI, UART and I2C) connectors

- 4. Arduino™ (Uno R3) connector

- 5. MikroElektronika™ mikroBUS connector (not populated)

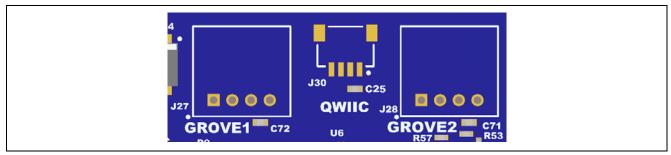

#### 5.3.1 Seeed Grove® Connectors

#### 5.3.1.1 Grove 1

A Seeed Grove<sup>®</sup> I<sup>2</sup>C connector footprint is provided at J27. The RA MCU acts as a two-wire serial master, and a connected module acts as a two-wire serial slave.

Table 12. Grove 1 Port Assignments

| Grove 1 Connector |     | EK-RA8E2    |

|-------------------|-----|-------------|

| Pin Description   |     | Signal/Bus  |

| J27-1             | SCL | P410 (SCL0) |

| J27-2             | SDA | P409 (SDA0) |

| J27-3             | VCC | +3.3 V      |

| J27-4             | GND | GND         |

#### 5.3.1.2 Grove 2

A Seeed Grove<sup>®</sup> I<sup>2</sup>C connector footprint is provided at J28. The RA MCU acts as a two-wire serial master, and a connected module acts as a two-wire serial slave.

Option links E39, E40, E41 and E42 provide the capability to convert this connector to an analog Seeed Grove® implementation.

Table 13. Grove 2 Port Assignments

| Grove 2 Connector          |         | EK-RA8E2       |                |

|----------------------------|---------|----------------|----------------|

| Pin Description Signal/Bus |         |                |                |

| J28-1                      | I2C_SCL | P512 (SCL1) *1 | P002(AN102) *2 |

| J28-2                      | I2C_SDA | P511 (SDA1)*1  | P005(AN001) *2 |

| J28-3                      | VCC     | +3.3 V         |                |

| J28-4                      | GND     | GND            |                |

- \*1 Jumpers E39 and E40 are closed, E41 and E42 are open

- \*2 Jumpers E39 and E40 are open, E41 and E42 are closed

Figure 12. Seeed Grove® and SparkFun® Qwiic® Connector Footprints

## 5.3.2 SparkFun® Qwiic® Connector

A SparkFun® Qwiic® connector footprint is provided at J30. The main MCU acts as a two-wire serial master, and a connected module acts as a two-wire serial slave (data lines shared with Grove 2).

**Table 14. Qwiic Port Assignments**

| Qwiic Connector |     | EK-RA8E2    |

|-----------------|-----|-------------|

| Pin Description |     | Signal/Bus  |

| J30-1           | GND | GND         |

| J30-2           | VCC | +3.3 V      |

| J30-3           | SDA | P409 (SDA0) |

| J30-4           | SCL | P410 (SCL0) |

## 5.3.3 Digilent Pmod™ Connectors

Two 12-pin connectors are provided to support Pmod modules where the RA MCU acts as the master, and the connected module acts as a slave device.

These interfaces may be configured in firmware to support several Pmod types such as Type-2A (expanded SPI), Type-3A (expanded UART) and Type-6A (I<sup>2</sup>C). Configured using SW4-1 and SW4-2 for Pmod 1 and SW4-4 for Pmod 2. These options are also configurable in software using the IO expander (U15).

The default 12-pin Pmod interface supports +3.3 V devices. Please ensure that any Pmod device installed is compatible with a +3.3 V supply.

Note: Both Pmods use the SCI peripheral in "Simple SPI" mode and so do not offer the full functionality of the SPI peripheral. Please see the hardware manual for full details of the SCI "Simple SPI" mode.

#### 5.3.3.1 Pmod 1

A 12-pin Pmod connector is provided at J26, Pmod 1.

Table 15. Pmod 1 Port Assignments

| Pmod 1 | Pmod 1 Connector              |                                |                                            | EK-RA8E2          |

|--------|-------------------------------|--------------------------------|--------------------------------------------|-------------------|

| Pin    | Option<br>Type-2A<br>(SPI) *1 | Option<br>Type-3A<br>(UART) *1 | Option<br>Type-6A<br>(I <sup>2</sup> C) *1 | Signal/Bus        |

| J26-1  | SS                            |                                |                                            | PA05 (SS2)        |

|        |                               | CTS                            |                                            | PA06 (CTS2)       |

|        |                               |                                | IRQ                                        | P206 (IRQ0-DS)    |

| J26-2  | MOSI                          | TXD                            |                                            | PA03 (MOSI2/TXD2) |

|        |                               |                                | RESET                                      | P408 (GPIO)       |

| J26-3  | MISO                          | RXD                            |                                            | PA02 (MISO2/RXD2) |

|        |                               |                                | SCL                                        | P512 (SCL1)       |

| Pmod 1 | Pmod 1 Connector        |     |     | EK-RA8E2                     |

|--------|-------------------------|-----|-----|------------------------------|

| J26-4  | SCK                     |     |     | PA04 (SCK2)                  |

|        |                         | RTS |     | PA05 (RTS2)                  |

|        |                         |     | SDA | P511 (SDA1)                  |

| J26-5  | GND                     |     |     | GND                          |

| J26-6  | VCC                     |     |     | +3.3 V (close E25, open E35) |

|        |                         |     |     | +5.0 V (close E35, open E25) |

| J26-7  | IRQ                     |     |     | P006 (IRQ11-DS)              |

| J26-8  | RESET (master to slave) |     |     | PA11                         |

| J26-9  | GPIO                    |     |     | PA12                         |

| J26-10 | GPIO                    |     |     | PA13                         |

| J26-11 | GND                     |     |     | GND                          |

| J26-12 | VCC                     | VCC |     | +3.3 V (close E25, open E35) |

|        |                         |     |     | +5.0 V (close E35, open E25) |

<sup>\*1</sup> Option is selected by setting switches SW4-1 and SW4-2 as follows:

Table 16. Pmod 1 Function Selection

| SW4-1 | SW4-2 | Selected function | Conflict |

|-------|-------|-------------------|----------|

| Off   | Off   | SPI               | Octo-SPI |

| On    | Off   | UART              | Octo-SPI |

| Off   | On    | I <sup>2</sup> C  | -        |

| On    | On    | Invalid           | Invalid  |

Caution: 5 V optional supply is provided (J26-6 and J26-12), however the interface must only be driven with 3.3 V signals from the Pmod 1. The EK-RA8E2 will only provide 3.3 V signal levels to the Pmod 1.

Figure 13. Pmod 1 Connector

#### 5.3.3.2 Pmod 2

A 12-pin Pmod connector is provided at J25, Pmod 2.

Table 17. Pmod 2 Port Assignments

| Pmod 2 C | onnector               |                            | EK-RA8E2          |

|----------|------------------------|----------------------------|-------------------|

| Pin      | Option Type-2A (SPI)*1 | Option Type-3A<br>(UART)*1 | Signal/Bus        |

| J25-1    | SS                     |                            | P314 (SS3)        |

| J25-1    |                        | CTS                        | P313 (CTS3)       |

| J25-2    | MOSI                   | TXD                        | P900 (MOSI3/TXD3) |

| J25-3    | MISO                   | RXD                        | P901(MISO3/RXD3)  |

| J25-4    | SCK                    |                            | P315 (SCK3)       |

| J25-4    |                        | RTS                        | P314 (RTS3)       |

| J25-5    | GND                    |                            | GND               |

| J25-6    | VCC                    |                            | +3.3 V            |

| J25-7    | IRQ                    |                            | P508 (IRQ1)       |

| Pmod 2 Connector |                            |                            | EK-RA8E2   |

|------------------|----------------------------|----------------------------|------------|

| Pin              | Option Type-2A<br>(SPI) *1 | Option Type-3A<br>(UART)*1 | Signal/Bus |

| J25-8            | GPIO                       |                            | P809       |

| J25-9            | GPIO                       |                            | P810       |

| J25-10           | GPIO                       |                            | P811       |

| J25-11           | GND                        |                            | GND        |

| J25-12           | VCC                        |                            | +3.3 V     |

<sup>\*1</sup> If using Type-2A (SPI), SW4-4 is OFF If using Type-3A (UART), SW4-4 is ON

Figure 14. Pmod 2 Connector

## 5.3.4 Arduino™ Connector

Near the center of the System Control and Ecosystem Access area is an Arduino™ Uno R3 compatible connector interface.

Table 18. Arduino Uno Port Assignments

| Arduino Compatible Connectors |            |      | EK-RA8E2 |                                  |

|-------------------------------|------------|------|----------|----------------------------------|

| Pin                           | Descriptio | n    |          | Signal/Bus                       |

| J18-1                         | N.C.       |      |          | N.C.                             |

| J18-2                         | IOREF      |      |          | +3.3 V                           |

| J18-3                         | RESET      |      |          | RESET_L (ARDUINO_RESET_L)        |

| J18-4                         | 3.3 V      |      |          | +3.3 V                           |

| J18-5                         | 5 V        |      |          | +5 V                             |

| J18-6                         | GND        |      |          | GND                              |

| J18-7                         | GND        |      |          | GND                              |

| J18-8                         | VIN        |      |          | N.C.                             |

| J19-1                         | A0         |      |          | P009 (AN006)                     |

| J19-2                         | A1         |      |          | P007 (AN004)                     |

| J19-3                         | A2         |      |          | P003 (AN104)                     |

| J19-4                         | A3         |      |          | P004 (AN000)                     |

| J19-5                         | A4         |      |          | P014 (AN007/DA0)                 |

| J19-6                         | A5         |      |          | P015 (AN015)                     |

| J23-1                         | D0         | RX   |          | P401 (RXD1/IRQ5-DS)              |

| J23-2                         | D1         | TX   |          | P400 (TXD1/IRQ0)                 |

| J23-3                         | D2         | INT0 |          | P509 (IRQ2)                      |

| J23-4                         | D3         | INT1 | PWM      | P202 (GPIO / IRQ3-DS / GTIOC5B)  |

| J23-5                         | D4         |      |          | P506 (GPIO)                      |

| J23-6                         | D5         |      | PWM      | P403 (GPIO / IRQ14-DS / GTIOC3A) |

| J23-7                         | D6         |      | PWM      | P203 (GPIO / IRQ2-DS / GTIOC5A)  |

| J23-8                         | D7         |      |          | P504 (GPIO)                      |

| J24-1                         | D8         |      | _        | P505 (GPIO)                      |

| J24-2                         | D9         |      | PWM      | P204 (GPIO / GTIOC4B)            |

| Arduino Compatible Connectors |             |          |     | EK-RA8E2             |

|-------------------------------|-------------|----------|-----|----------------------|

| Pin                           | Description |          |     | Signal/Bus           |

| J24-3                         | D10         | SPI_SS   |     | P703 (SSLA)          |

| J24-4                         | D11         | SPI_MOSI | PWM | P701 (MOSIA/GTIOC5B) |

| J24-5                         | D12         | SPI_MISO | PWM | P700 (MISOA/GTIOC5A) |

| J24-6                         | D13         | SPI_SCK  |     | P702 (RSPCKA)        |

| J24-7                         | GND         |          |     | GND                  |

| J24-8                         | ARDUIN      | O_AREF   |     | +3.3 V               |

| J24-9                         | SDA         |          |     | P409/SDA0 (SDA0)     |

| J24-10                        | SCL         |          |     | P410/SCL0 (SCL0)     |

Figure 15. Arduino Uno Connectors

## 5.3.5 MikroElektronika™ mikroBUS Connector

In the center of the System Control and Ecosystem Access area is a mikroBUS compatible connector footprint. This interface is compliant with mikroBUS Standard Specifications revision 2.00.

Table 19. mikroBUS Assignments

| mikroBUS Connectors |                          | EK-RA8E2                |

|---------------------|--------------------------|-------------------------|

| Pin                 | Description              | Signal/Bus              |

| J21-1               | AN (Analog)              | P004 (AN000)            |

| J21-2               | RST (Reset)              | P507 (MIKROBUS RESET_L) |

| J21-3               | CS (SPI Chip Select)     | P703 (SSLA0)            |

| J21-4               | SCK (SPI Clock)          | P702 (RSPCKA)           |

| J21-5               | MISO                     | P700 (MISOA)            |

| J21-6               | MOSI                     | P701 (MOSIA)            |

| J21-7               | +3.3 V                   | +3.3 V                  |

| J21-8               | GND                      | GND                     |

| J22-1               | PWM                      | P403 (GTIOC3A)          |

| J22-2               | INT (Hardware Interrupt) | P010 (IRQ14)            |

| J22-3               | RX (UART Receive)        | P401 (RXD1)             |

| J22-4               | TX (UART Transmit)       | P400 (TXD1)             |

| J22-5               | SCL                      | P410/SCL0 (SCL0)        |

| J22-6               | SDA                      | P409/SDA0 (SDA0)        |

| J22-7               | +5 V                     | +5 V                    |

| J22-8               | GND                      | GND                     |

Figure 16. mikroBUS Connector

## 5.4 Connectivity

#### 5.4.1 USB Full Speed

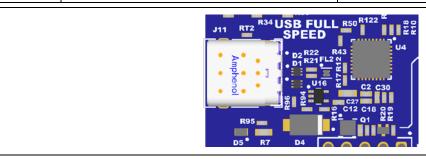

The USB-C connection jack (J11) connects the RA MCU USB Full Speed interface to an external USB interface, allowing communications for testing and use of the RA MCU firmware. This connection can be configured as either a USB device or a USB host interface.