### RENESAS

# ne GreenPAK<sup>TM</sup>

#### GreenPAK 简介

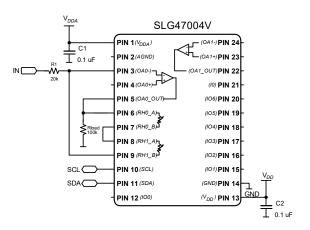

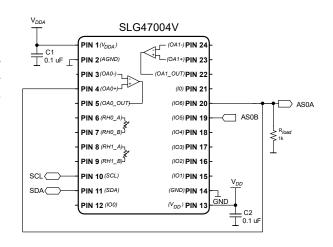

Renesas Electronics 的 GreenPAK IC 是一系列可配置混合信号 IC [CMIC],为系统级电路设计人员面临的常见问题提供小型、成本友好且个性化的解决方案。 GreenPAK 提供了一种显著降低 PCB 尺寸,BOM 成本和设计时间的方法。

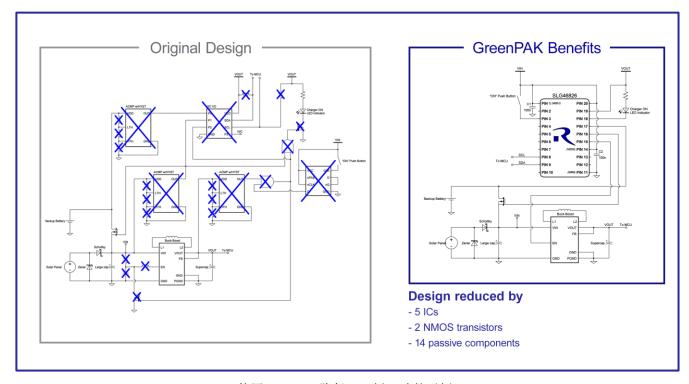

使用 GreenPAK 降低 PCB 板尺寸的示例

由于 GreenPAK 的各种功能和可配置性,所以 GreenPAK 的应用范围非常广,凭借对产品需求正确的认知,设计人员可以将 GreenPAK 应用到大多数行业的几乎任何的应用中。

本文档旨在加强这种认知和技术诀窍: 我们为设计人员提供应用示例手册,指出 GreenPAK 可以应用在项目中的那些地方。我们概述了不同的技巧,并提供了完整的应用示例,以帮助设计人员灵活使用 GreenPAK。

#### 本手册的结构

本文档中每个小节都包含两种类型的内容: 技巧和应用示例。 技巧专注于仅使用一个或几个宏单元来完成的任务。 应用示例部分描述了如何将这些技巧组合在一起以创建有实际价值的应用。 最简单的技巧和应用将放在第一章的开头。

每个应用对应的 GreenPAK Designer 设计文件,都可以查看、编辑。

#### Resources

Go Configure Software<sup>™</sup> Hub Download

The GreenPAK Cookbook GP Files Download

Product Selection Guide

The GreenPAK Cookbook EN

The GreenPAK Cookbook JP

#### 使用本手册构建你的设计

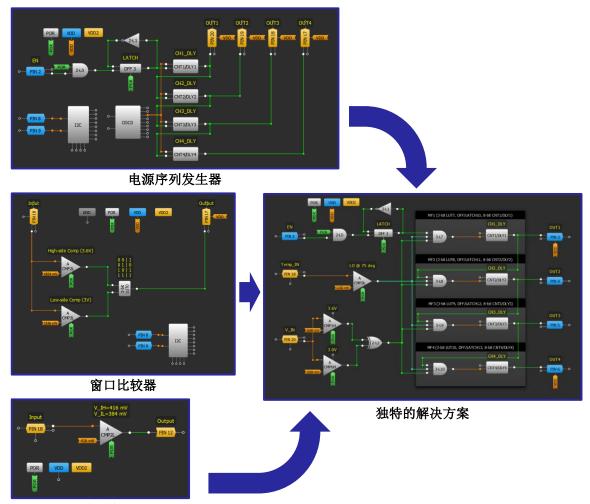

本手册列举的实例都是已经得到实际应用的工程案例。不仅如此,GreenPAK IC 还具有本手册实例中未使用到的更多宏单元和功能。Renesas Electronics 帮助工程师实现了数以千计的独特设计,这些设计或多或少与本手册中的案例相似或不同,但它们都是可扩展、可结合和可定制化的。

例如,电源序列发生器应用实例与第4章节的安全应用实例相结合,从而成为可调节的、定制化的序列发生器应用。

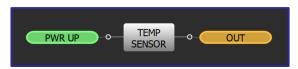

过温检测

如把上述实例中的几个方案整合在同一电路中,系统将变得十分复杂且造成宏单元的浪费。而使用 GreenPAK 系列 IC 及本手册中的技巧,可以助您轻松实现设计,并且可以随意置换和修改您的设计。您可以重复使用本手册中显示的设计,或者将本文中的一些技术融入您自己的设计中。因为,这是属于你的技巧。

#### 目录

| GreenPAN                                                   | 简介                                                                                                                                                                                                                                   |                            |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 本手册                                                        | 册的结构                                                                                                                                                                                                                                 | 2                          |

| 使用ス                                                        | 本手册构建你的设计                                                                                                                                                                                                                            | 3                          |

| 目录                                                         |                                                                                                                                                                                                                                      | 4                          |

| 第1章: 基                                                     | 上本功能模块                                                                                                                                                                                                                               | 8                          |

|                                                            | 如何了解宏单元的更多信息                                                                                                                                                                                                                         |                            |

|                                                            | 数字宏单元                                                                                                                                                                                                                                |                            |

| 技巧:                                                        | 配置标准逻辑                                                                                                                                                                                                                               | 10                         |

| 概述:                                                        | 振荡器                                                                                                                                                                                                                                  | 10                         |

| 概述:                                                        | 模拟比较器                                                                                                                                                                                                                                | 10                         |

| 概述:                                                        | I/O                                                                                                                                                                                                                                  | 11                         |

| 概述:                                                        | 连接                                                                                                                                                                                                                                   | 11                         |

| 技巧:                                                        | 使用 GreenPAK Designer 进行仿真                                                                                                                                                                                                            | 12                         |

| 技巧:                                                        | GreenPAK 烧录                                                                                                                                                                                                                          | 13                         |

| 技巧:                                                        | OE 脚                                                                                                                                                                                                                                 | 14                         |

| 应用:                                                        | 奇偶校验位发生器                                                                                                                                                                                                                             | 15                         |

| 应用:                                                        | 独热编码器(一位有效编码器)                                                                                                                                                                                                                       | 16                         |

| 应用:                                                        | 8 位多路复用器                                                                                                                                                                                                                             | 17                         |

| 应用:                                                        | 多路输出选择器                                                                                                                                                                                                                              | 18                         |

|                                                            |                                                                                                                                                                                                                                      |                            |

| 第 2 章:时                                                    | ·序逻辑                                                                                                                                                                                                                                 | 19                         |

|                                                            | · <b>序逻辑</b><br>优化 CNT/DLY 的精度                                                                                                                                                                                                       |                            |

| 技巧:                                                        |                                                                                                                                                                                                                                      | 20                         |

| 技巧:<br>技巧:                                                 | 优化 CNT/DLY 的精度                                                                                                                                                                                                                       | 20<br>21                   |

| 技巧:<br>技巧:<br>应用:                                          | 优化 CNT/DLY 的精度 CNT/DLY 的级联                                                                                                                                                                                                           | 20<br>21<br>22             |

| 技巧:<br>技巧:<br>应用:<br>应用:<br>应用:                            | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器                                                                                                                                                        | 20<br>21<br>22<br>23       |

| 技巧:<br>技巧:<br>应用:<br>应用:<br>应用:                            | 优化 CNT/DLY 的精度                                                                                                                                                                                                                       | 20<br>21<br>22<br>23       |

| 技巧:<br>技巧:<br>应用:<br>应用:<br>应用:                            | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器                                                                                                                                                        | 20<br>21<br>23<br>24<br>25 |

| 技巧: 应应应应应用: 用:                                             | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器                                                                                                                                        | 20<br>21<br>23<br>24<br>25 |

| 技巧 5                                                       | 优化 CNT/DLY 的精度                                                                                                                                                                                                                       |                            |

| 技巧 5 3 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                 | 优化 CNT/DLY 的精度 CNT/DLY 的级联 系统复位 多按钮复位 电源序列发生器 电源时序控制器 电压监测电源时序控制器 运输模式控制器 由异步状态机创建同步状态机                                                                                                                                              |                            |

| 技技应应应应应应技应技巧用用用用用用用用的形式                                    | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流                                                |                            |

| 技技应应应应应应技应技应对明用用用用用用的明明明明明明明明明明明明明明明明明明明明明明明明明明明明明明        | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流         10 年定时器                                |                            |

| 技技应应应应应应技应技应应应 应                                           | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流         10 年定时器         方波发生器                  |                            |

| 技技应应应应应应技应技应应应 应                                           | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流         10 年定时器                                |                            |

| 技技应应应应应拉应技应应应的方式,用用用用用用的用方用的用用用的                           | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流         10 年定时器         方波发生器                  |                            |

| 技技应应应应应应技应技应应应 章3节5年,用用用用用工工工工工工工工工工工工工工工工工工工工工工工工工工工工工工工工 | 优化 CNT/DLY 的精度         CNT/DLY 的级联         系统复位         多按钮复位         电源序列发生器         电源时序控制器         电压监测电源时序控制器         运输模式控制器         由异步状态机创建同步状态机         N 比特流         多路复用比特流         10 年定时器         方波发生器         按下多个事件按钮 |                            |

| 技技应应应应应应技应技应应应产 第3 技巧可用用用用用用的用的用的用用用用的 第3 计                | 优化 CNT/DLY 的精度                                                                                                                                                                                                                       |                            |

|   | 技巧:    | 构建一个双向计数器                           | 38 |

|---|--------|-------------------------------------|----|

|   | 应用:    | 编码器                                 | 39 |

|   | 应用:    | 距离感应器                               | 40 |

|   |        | 频率范围探测器                             |    |

|   | 应用:    | 分频器                                 | 42 |

|   | 技巧:    | 过零检测                                | 43 |

|   | 应用:    | 模拟存储元件                              | 44 |

| 第 | 4 章:安  | 全功能                                 | 45 |

|   | 技巧:    | 如何降低 ACMP 的功耗                       | 46 |

|   | 技巧:    | 唤醒与休眠                               | 47 |

|   | 应用:    | 窗口比较器                               | 48 |

|   | 应用:    | 过温保护                                | 49 |

|   | 应用:    | 充电指示器                               | 50 |

|   | 应用:    | 信息娱乐系统低压指示器                         | 51 |

|   | 应用:    | 看门狗定时器                              | 52 |

|   | 应用:    | 电压检测                                | 53 |

|   | 应用:    | 电源后备管理                              | 54 |

|   | 应用:    | N 脉冲看门狗                             | 55 |

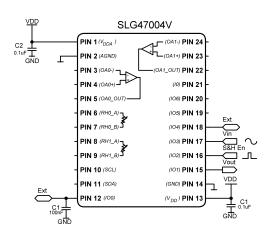

|   | 技巧:    | 温度传感器模块的应用                          | 56 |

|   |        | 通过外部采样电阻进行电流检测                      |    |

|   | 应用:    | 使用一个复用 ACMP 监控一个模拟量的四个电平            | 58 |

|   | 应用:    | 用一个 MS ACMP 监控四个独立模拟信号              | 59 |

| 第 | 5 章: 通 | 讯协议                                 | 60 |

|   | 技巧:    | 利用 I <sup>2</sup> C 更改设计            | 61 |

|   | 技巧:    | 创建一个 I <sup>2</sup> C 命令            | 62 |

|   | 技巧:    | 串行-并行接口 (SPI) 模块                    | 63 |

|   | 技巧:    | 电平转换                                | 64 |

|   | 技巧:    | 发送预设数量脉冲                            | 65 |

|   | 技巧:    | 移位寄存器                               | 66 |

|   | 应用:    | 通过  2C接口进行  0 扩展                    | 67 |

|   | 应用:    | 串口转并口(外部时钟)                         | 68 |

|   | 应用:    | 串口转并口(内部时钟)                         | 69 |

|   | 应用:    | 并口转串口                               | 70 |

|   | 应用:    | 双向通信 (发送优先)                         | 71 |

|   | 应用:    | 双向通信 (接收优先)                         | 72 |

|   | 应用:    | 采用 ASM 和 I <sup>2</sup> C 的 7 段数码显示 | 73 |

|   | 应用:    | 采用 I <sup>2</sup> C 的通讯多路复用器        | 74 |

|   |        | I <sup>2</sup> C 电平转换器              |    |

|   | 应用:    | 连接检测                                | 76 |

|   | 应用.    | 自定义模式发生器                            | 77 |

| 技巧:    | 使用占空比检测发送串行协议                        | 78  |

|--------|--------------------------------------|-----|

| 技巧:    | 使用移位寄存器读取串行协议                        | 79  |

| 技巧:    | 利用管道延时(Pipe Delay)读取串行协议             | 80  |

| 技巧:    | 数模转换器                                | 81  |

| 应用:    | 自定义模式发生器                             | 82  |

| 技巧:    | EPG                                  | 83  |

| 应用:    | 带 ACK 检查和数据比较的 I2C 主设备读指令            | 84  |

| 应用:    | 带 ACK 检查的 I <sup>2</sup> C 主设备写指令    | 85  |

| 应用:    | 移位寄存器构建 I <sup>2</sup> C 可编程模式发生器    | 86  |

| 应用:    | 固定长码发生器                              | 87  |

| 应用:    | 简单 SPI 主机                            | 88  |

| 第6章: 基 | 基于脉冲的控制                              | 89  |

| 技巧:    | 恒定占空比 PWM                            | 90  |

| 技巧:    | 输出一个高脉冲信号                            | 91  |

| 应用:    | LED 恒流驱动器                            | 92  |

| 应用:    | 用 I <sup>2</sup> C 控制 RGB LED        | 93  |

| 技巧:    | LED 呼吸模式                             | 94  |

| 应用:    | RGB LED 呼吸灯                          | 95  |

| 应用:    | 用 I <sup>2</sup> C 实现 RGB LED 呼吸灯的控制 | 96  |

| 技巧:    | DCMP/PWM 宏单元在 PWM 模式下的应用             | 97  |

| 应用:    | PWM 选择器                              | 98  |

| 应用:    | 采用 ACMP 和 DAC 的 PWM 发生器              | 99  |

| 应用:    | 采用 ADC 的 PWM 发生器                     | 100 |

| 技巧:    | 占空比检测                                | 101 |

| 应用:    | 频率/模拟电压转换器                           | 102 |

| 应用:    | 频率/占空比转换器                            | 103 |

| 应用:    | 线性调频                                 | 104 |

| 应用:    | 压控振荡器                                | 105 |

| 第7章:电  | 源管理                                  | 106 |

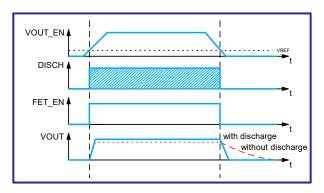

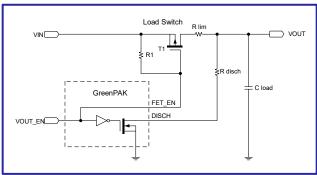

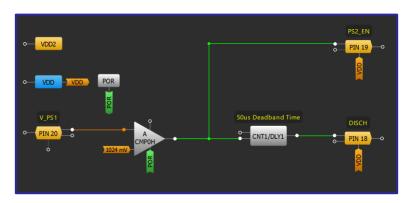

| 技巧:    | 输出放电                                 | 107 |

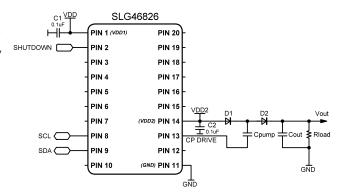

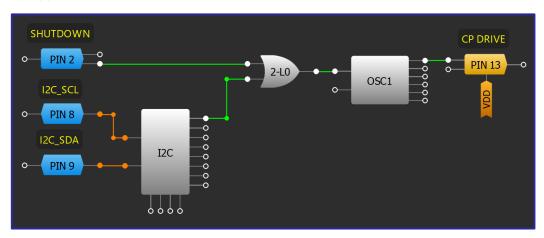

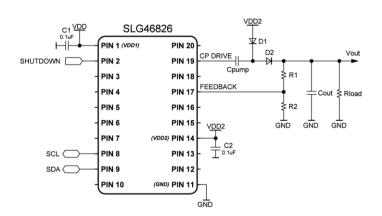

| 应用:    | 电荷泵                                  | 108 |

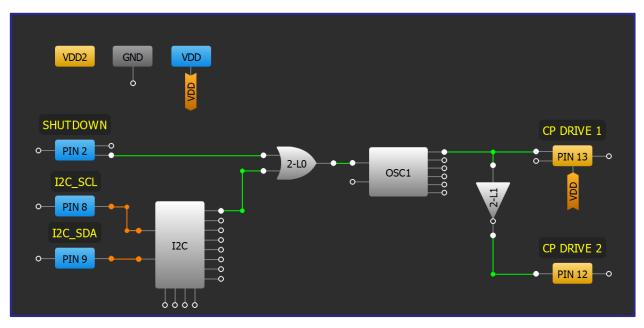

| 应用:    | 二级电荷泵                                | 109 |

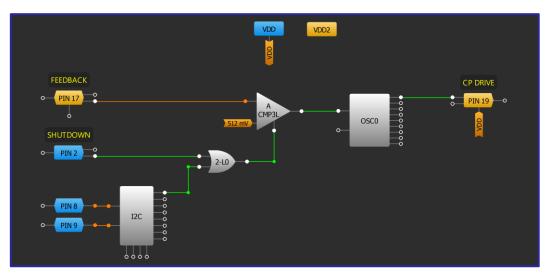

| 应用:    | 具有输出调节功能的电荷泵                         | 110 |

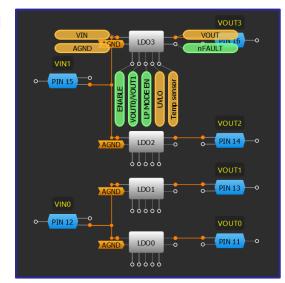

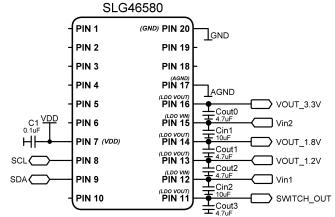

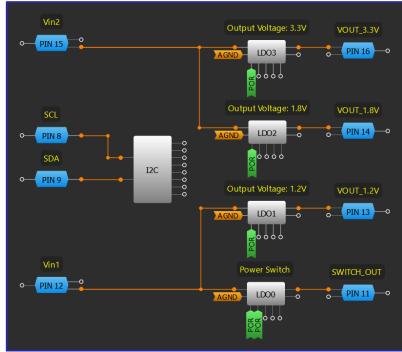

| 技巧:    | LDO 稳压器                              | 111 |

| 应用:    | 灵活的电源岛                               | 112 |

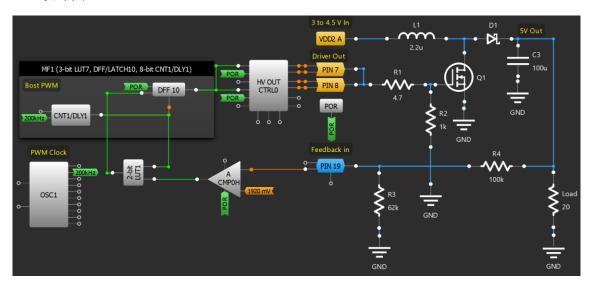

| 应用:    | 升压转换器                                | 113 |

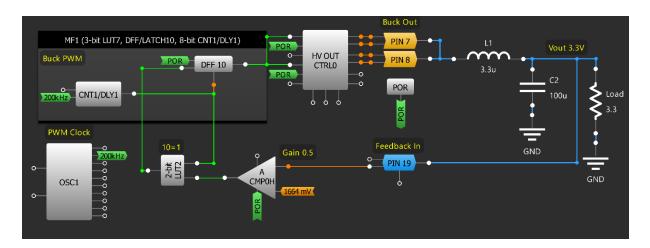

|        | 降压型转换器                               |     |

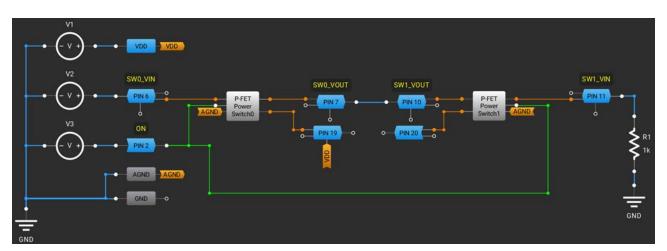

| 应用:    | 背对背的反向电流阻断                           | 115 |

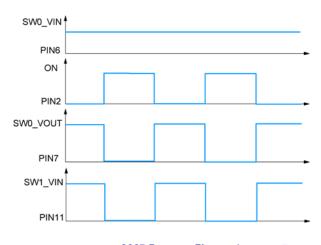

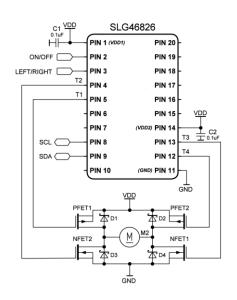

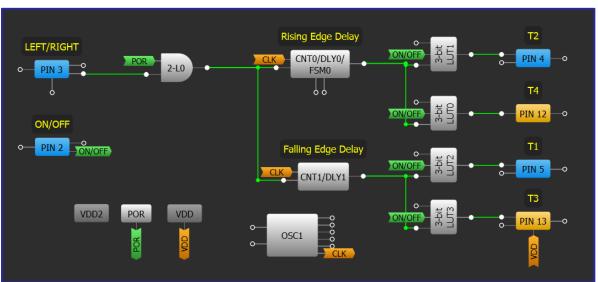

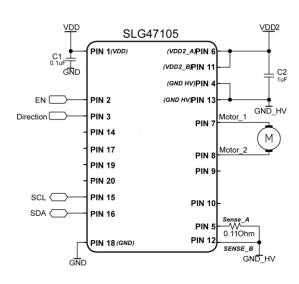

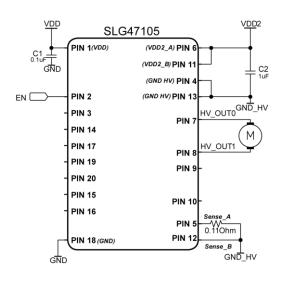

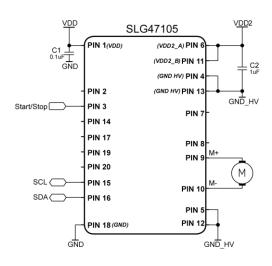

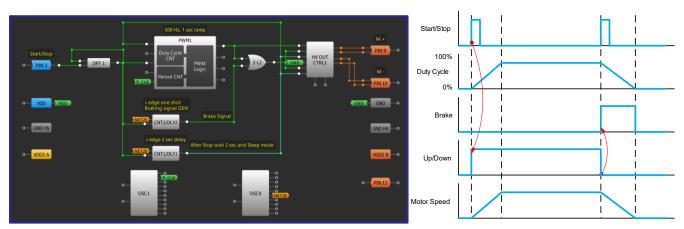

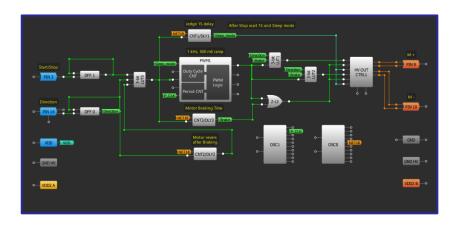

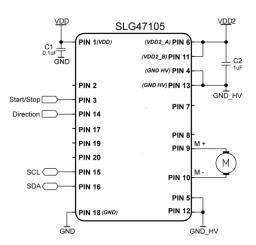

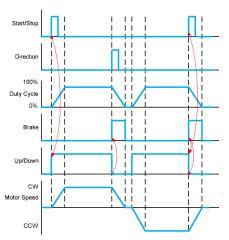

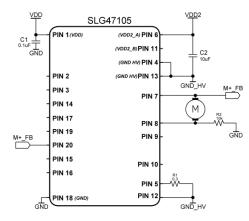

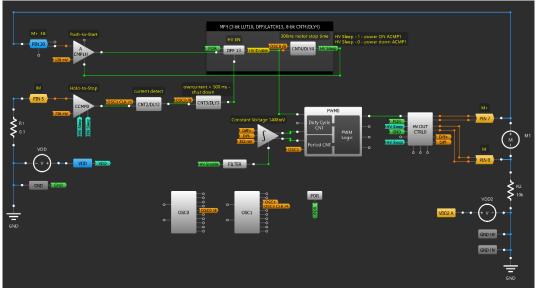

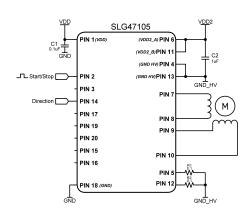

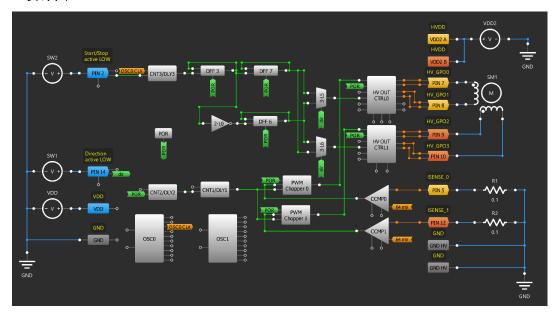

| 第8章:电  | .机控制                                 | 116 |

|        | H 桥控制                                |     |

|        |                                      |     |

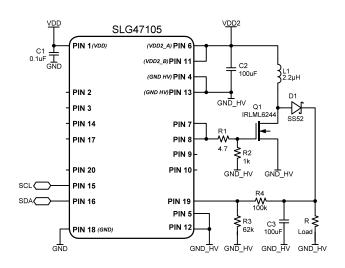

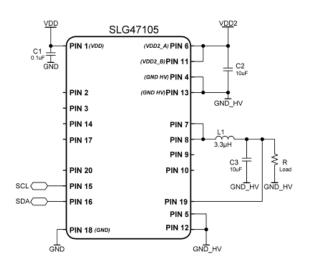

| 技巧   | : 使用 HV OUT CRTL 模块                  | 118 |

|------|--------------------------------------|-----|

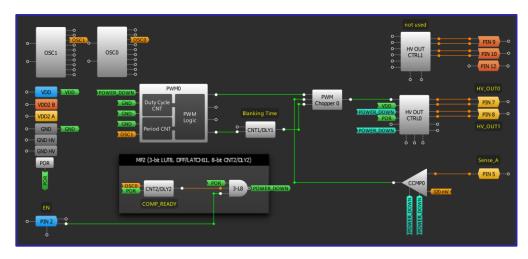

| 技巧   | : 在常规模式下使用 SLG47105 PWM 模块           | 119 |

| 技巧   | : 在预设寄存器模式下使用 SLG47105 PWM 模块        | 120 |

| 应用   | : 恒压有刷直流电机驱动器                        | 121 |

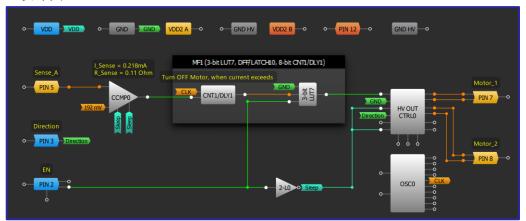

| 应用   | : 恒流有刷直流电机驱动器                        | 122 |

| 应用   | : PWM 恒流斩波器                          | 123 |

| 应用   | : 带有软开关的单向直流电机控制                     | 124 |

| 应用   | : 具有软开/关的双向直流电机控制                    | 125 |

| 应用   | : 助推启动/堵转停止                          | 126 |

| 应用   | : 双极步进电机驱动器                          | 127 |

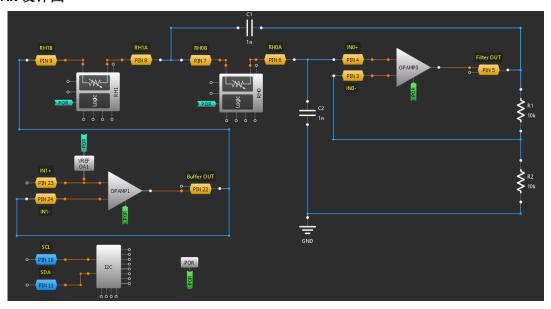

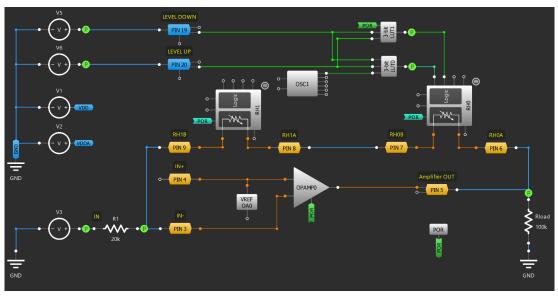

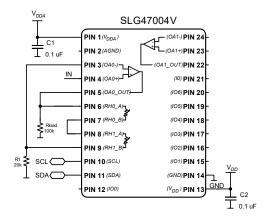

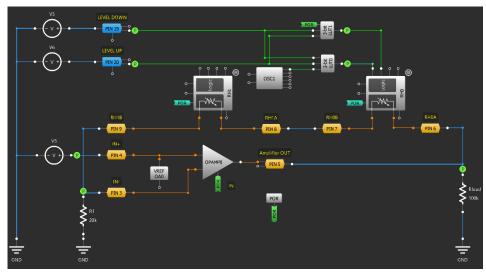

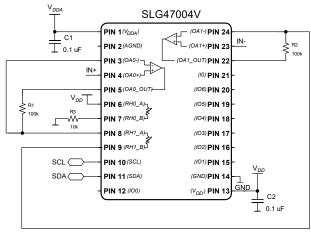

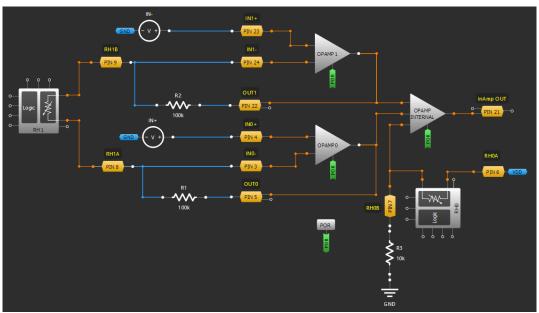

| 第九章: | 高级模拟功能                               | 128 |

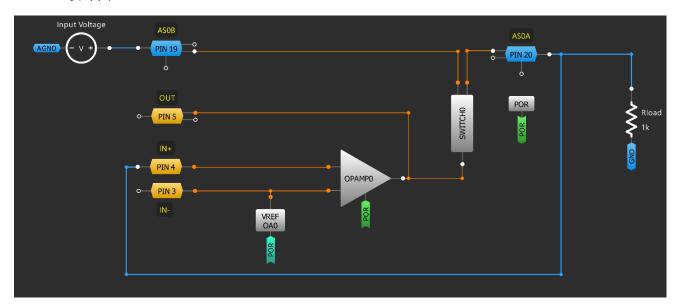

| 应用   | : 采用 OpAmp 可调有源滤波器                   | 129 |

|      | : 可调反相 OpAmp                         |     |

| 应用   | : 可调同相 OpAmp                         | 131 |

| 应用   | : 仪表放大器                              | 132 |

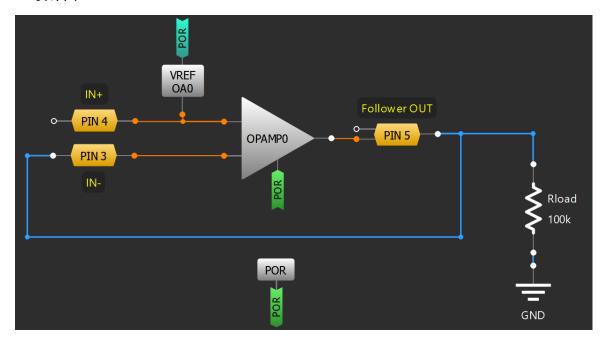

| 应用   | : 使用运放创建电压跟随器                        | 133 |

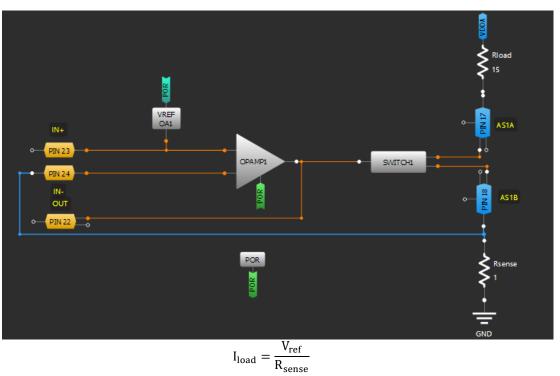

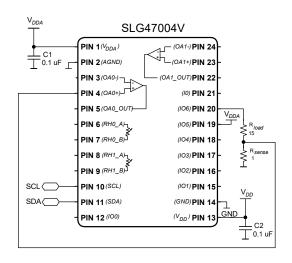

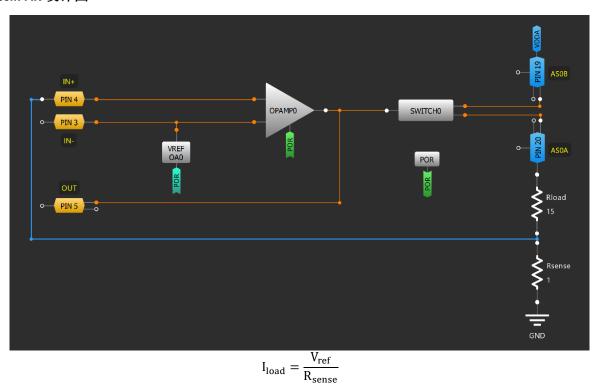

| 应用   | : 使用运放和 N 沟道 FET 创建电流阱(Current Sink) | 134 |

| 应用   | : 自动校准                               | 135 |

| 应用   | : 使用运放和 P 沟道 FET 创建电流源               | 136 |

| 应用   | : 使用运算放大器的稳压器                        | 137 |

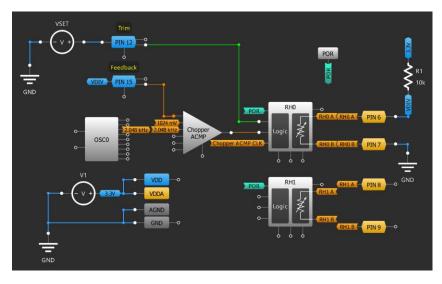

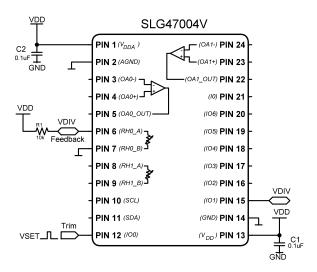

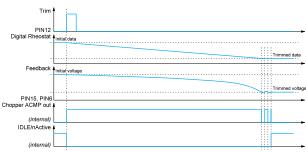

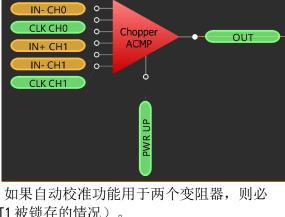

| 技巧   | : 带数字变阻器的斩波比较器                       | 138 |

| 田協   | <ul><li>取样保持由路</li></ul>             | 130 |

# 第1章:基本功能模块

本章介绍了许多在 GreenPAK 中发现的基本构建模块,它们将在整本 Cookbook 中使用。它还将介绍一些使用查找表 look-up tables (LUTs)的简单组合逻辑设计。

#### 技巧: 如何了解宏单元的更多信息

这个技巧适用于所有版本的GreenPAK Designer。

在使用 GreenPAK Designer 时,您可能希望了解有关特定宏单元的更多信息。你可以在 GreenPAK Designer 中选中该宏单元,然后点击 Properties 窗口左下角的 Information 按钮来查看。

Info Button

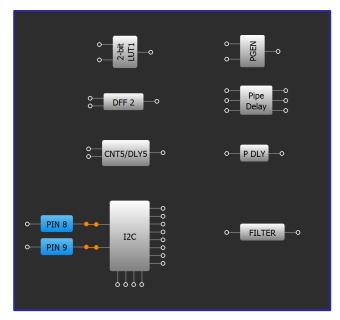

#### 概述: 数字宏单元

数字宏单元是 GreenPAK 的基本功能组件,包含以下几种类型:

#### 通用数字宏单元:

- 查找表 Look-Up Tables (LUTs)

- D 类触发器/锁存器 D Flip-Flop (DFF) / Latch

- 计数器/延时器 Counter / Delay (CNT/DLY)

#### 通讯:

- I2C (大部分器件包含该单元)

- SPI (少数器件包含该单元)

#### 少见:

- 模式发生器 Pattern Generator (PGEN)

- 管道延时 Pipe Delay

- 可设定延时 Programmable delay (PDLY)

- 滤波器/边沿检测器 Filter / Edge Detector

Digital Macrocells 数字宏单元

在 GreenPAK Designer 中很多的宏单元都是多用途的,你可以配置其中的一种功能作为该宏单元的功能,宏单元有哪些可供选择的功能可以从该宏单元的名字得知,比如 2-bit LUT0/DFF/LATCH0 暗示它可以被配置成查找表、D 类触发器或者锁存器,使用 Properties 窗口中的 Type 选项来选择宏单元的功能。

#### 技巧: 配置标准逻辑

此技巧适用于所有GreenPAK 芯片。

查找表[LUT]是在 GreenPAK Designer 中可配置的两输入、三输入或者四输入逻辑宏单元,可以在 **Properties** 窗口中编辑逻辑配置。

大多数的标准化逻辑已经在 GreenPAK Designs 中实现,比如 MUX、AND、OR 等,为了加快这些常见逻辑的配置,在 Properties 窗口中有一个 Standard gates 选项可以自动将查找表转换成标准逻辑门配置。如果 Regular shape 选项没有被选中,查找表的形状将会以标准的逻辑门符号显示。

# | Properties | Defended | Defended

配置 3-bit LUT0

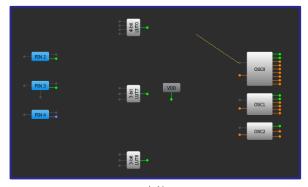

#### 概述:振荡器

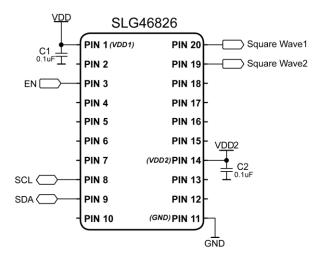

GreenPAK IC 至少包含 2 个振荡器[OSC], 很多 GreenPAK 芯片, 比如 SLG46826 包含 3 个振荡器, 常见的未分频频率有:

- 2KHz 低速低功耗振荡器

- 2MHz 中速振荡器

- 25MHz 高速振荡器

每一个振荡器都有几个可选择预分频系数的输出。通过配置 **Auto-power on** 可以让你在不需要时钟的时候自动关闭振荡器以降低功耗。

更多关于振荡器的信息,可以在组件被选中时,通过在 **Properties** 窗口中点击 **Information** 按钮来查看。

振荡器

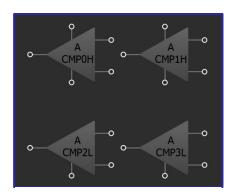

#### 概述: 模拟比较器

大多数 GreenPAK 都包含 2 个或者更多的模拟比较器 [ACMP],每个比较器都有一个 IN+和一个 IN-输入源,可以在 Properties 窗口中选择输入源。

更多关于模拟比较器的信息,可以在组件被选中时,通过在 Properties 窗口中点击 Information 按钮来查看。

模拟比较器

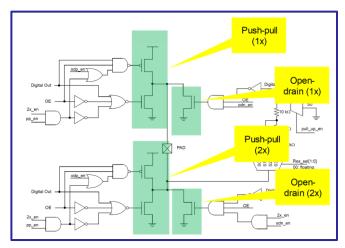

#### 概述: I/0

GreenPAK的 I/O 是非常灵活的。无论是在同一个芯片内或是不同芯片之间,每个输入输出脚的属性均不相同,因此选型时必须先考虑输入输出脚可以实现的功能与所需要的数量。

输出可以配置成推挽输出、N 型或 P 型开漏输出,可以选择不同的输出能力,比如 2x,表示两倍的输出驱动能力,还可以选择上拉电阻或者下拉电阻,有  $10k\Omega$ 、 $100k\Omega$  和  $1M\Omega$  可选。

输入也有多种配置可选:数字输入、施密特数字输入、 低电平数字输入和模拟输入。模拟输入可以作为模拟比 较器的输入源。

典型的 I/O 结构

#### 概述:连接

在 GreenPAK Designer 中连接非常容易,软件会自动指示你那些连接是允许的,当你点击一个连接点时:

- 会绿色高亮所有可以连接的连接点。

- 给你一根类似橡皮筋的线,你可以拉伸到任何一个被绿色高亮的连接点。

- 如果一个连接已完成会用一根绿色的线来指示。

连接

#### 技巧: 使用 GreenPAK Designer 进行仿真

Emulation 适用于所有GreenPAK 芯片, Simulation 适用于大部分GreenPAK 芯片。

GreenPAK Designer 中的工具栏

当进行一项设计时,非常重要的一点是可以快速进行功能测试。

可通过以下两种方式检验你的设计:

- 1. Simulation

- 2. Emulation

Simulation 在没有芯片的情况下,使用 GreenPAK Designe 模拟电路的实际性能。需要注意的是软件模拟不能完全识别真实系统的所有细节(极少数特殊条件下会存在细微差异,需要使用芯片实际测试确认)。

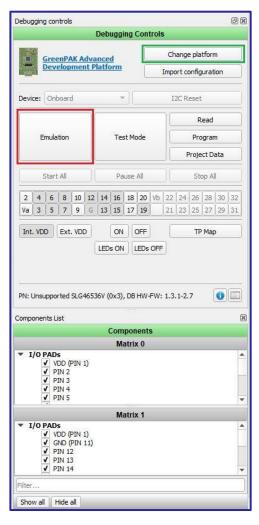

Emulation 使用 GreenPAK 芯片和相应的演示板,提前检验设计中的问题,避免量产中因永久性烧录造成的损失。这可以让您快速地对项目进行更改,并使用仿真来验证您的猜测。

- 1. 当设计完成后,单击 Debug 按钮(上图中的红色按钮),进入仿真/模拟界面。

- 2. 选择将要使用的验证平台。

- 3. 完成平台设置后, 将出现 Debug 菜单, 根据您选择的平台, 将提示 进一步的操作。

- 4. 如果需要更改仿真平台,您可以随时通过单击 Change Platorm 按钮来进行更改。

平台选择菜单

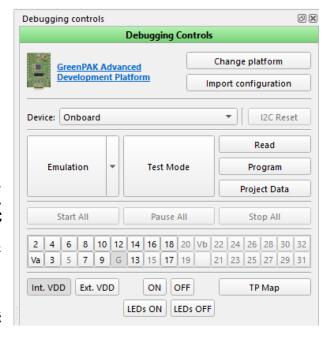

Debugging 菜单

#### 技巧: GreenPAK 烧录

Debugging control 适用于所有 GreenPAK 芯片。

GreenPAK Designer 软件的工具栏

当进行一项设计时,非常重要的一点是可以快速进行功能验证。GreenPAK Designer 软件使调试变得更加高效便捷。

#### Change platform

选择对应功能的硬件平台。

#### Import configuration

从其他硬件平台导入仿真配置。

#### Device

允许用户在指定的设备地址上使用外部芯片。

#### I<sup>2</sup>C Reset

假设与设备建立了 I<sup>2</sup>C 串行通信。在这种情况下,可以将设备重置为初始上电条件,包括所有宏单元的配置以及 Connection Matrix 提供的所有连接。通过将寄存器 I<sup>2</sup>C Reset 位设置为"1"来实现复位,复位时芯片将重新启用 Power-On Reset (POR) 序列,包括从 NVM 重新加载所有寄存器数据。

#### **Emulation**

- Emulation, 当前设计将加载到芯片中(但未烧录),并准备好在硬件板上进行测试。

- Emulation (sync), 除了 Emulation(仿真)之外,项目中所做的每个更改都将立即加载到芯片上。

#### Test mode

Test mode(测试模式)用于连接或断开芯片的输入/输出引脚与用户配置的 TP controls。打开 Test mode 和内部 VDD 按钮,用户可以使用测试模式来检查已烧录的芯片,而无需仿真。测试模式可以在芯片不上电的情况下工作,用户可以手动控制电源开关。

#### Read

通过硬件开发板读取芯片数据。

#### **Program**

将当前设计烧录到芯片中。对于某些芯片型号,用户可以通过点击 Program 按钮中的 Programming 选项来设置烧录过程。可以选择的烧录选项有:

- Program NVM (对芯片的 NVM 进行烧录)

- Program EEPROM (对芯片的 EEPROM 进行烧录)

#### **Project Data**

NVM 和 EEPROM 数据表(适用于特定芯片版本)。

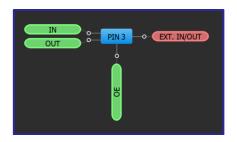

#### 技巧: OE 脚

此技巧适用于所有带有OE 引脚的GreenPAK 芯片。

通常,GreenPAK IC 的 I/O 脚可被配置为输入或输出脚。大多数的带有**输出使能 OE** 端子的引脚的 GreenPAK IC 都可以被设置为 Digital Input 和 Digital Output 两个状态的动态转换,带有输出使能 OE 端子的引脚 GPIO, 当 GPIO 配置为输入时,OE 脚接地(或逻辑低电平);当 GPIO 配置为输出时,OE 脚接 VDD (或逻辑高电平)。可以通过内部逻辑单元矩阵连接到 OE 脚,控制 GPIO 在 Digital Input 和 Output 两个状态间动态切换。

GPIO 脚可被配置为 Digital Input/Output 双向工作模式。此外,GPIO 脚还可设置为高阻态。

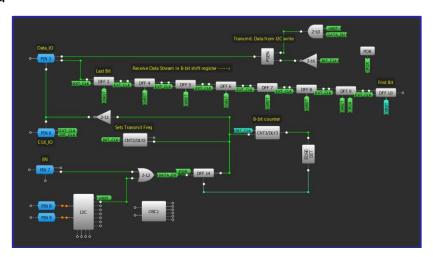

如果 GPIO 被配置为 Digital Input/Digital Output 双向工作模式,需要为 OE 提供一个模式切换的时序电路。在如下所示的电路中,CLK\_IO 和 Data\_IO 的 OE 脚在 CNT2 收到 8 个时钟周期后,由低电平切换为高电平,即 GPIO 被配置为输出脚进而输出内部信号。再经过 8 个时钟周期后,OE 转为低电平,重新设置 GPIO 为输入脚从而接收外部信号。

GND

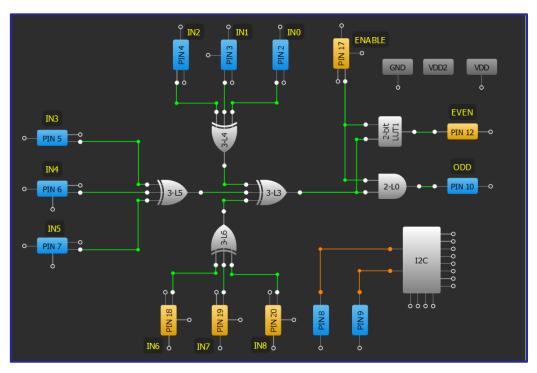

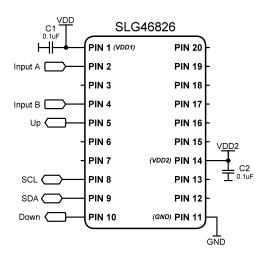

#### 应用: 奇偶校验位发生器

奇偶校验位生成器可以用来校验信息的完整性,是循环冗余校验最简单的实现,奇偶校验位在将数据提交给MCU或其他控制单元之前使用,以确保输入数据未被干扰破坏。

#### SLG46826 PIN 1 (VDD1) **PIN 20** PIN 2 **PIN 19** INO [ PIN 3 ] IN6 **PIN 18** PIN 4 **PIN 17** ] ENABLE IN2 PIN 5 **PIN 16** IN3 PIN 6 IN4 [ **PIN 15** PIN 7 (VDD2) PIN 14 IN5 PIN 8 **PIN 13** SCL ( PIN 9 **PIN 12** > EVEN ODD 🔂 **PIN 10** (GND) PIN 11

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 使用技巧:配置标准逻辑将所有输入通过 XOR 门来连接,XOR 门被用来计算 1 的个数。

- 2. 添加 ENABLE 信号逻辑。

#### 应用: 独热编码器(一位有效编码器)

One-Hot 编码,一组数位中仅有一位为高电平(1)其他数位皆为低电平(0),例如0001。与之相反,一组数位中仅有一位为低电平(0),其他数位皆为高电平(1),称为One-cold编码。本设计是一个基于输入的两位编码从而输出一个特定的独热编码的编码器。

#### SLG46826 PIN 1 (VDD1) **PIN 20** PIN 2 **PIN 19 PIN 18** IN1 [ PIN<sub>3</sub> INO [ PIN 4 **PIN 17** PIN 5 **PIN 16** CTUO C PIN 6 **PIN 15** OUT2 PIN 7 (VDD2) PIN 14 SCL ( PIN 8 **PIN 13** OUT1 PIN 9 **PIN 12** OUT0 SDA ( **PIN 10** (GND) PIN 11 GND

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

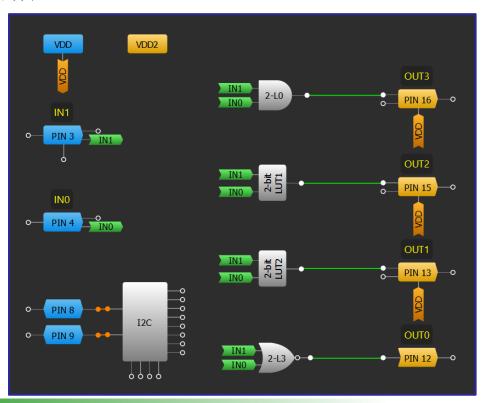

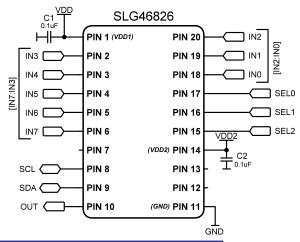

- 1. 将 2 个输入脚配置为 Digital Input(INx), 4 个输出脚配置为 Digital Output(OUTx)。

- 2. 将 4 个 2-bit LUT/DFF/LATCH 配置为每个 IN 信号组合只有其中一个 LUT 输出高, 例如当 INO 和 IN1 都为 0 时,只有 2-L3 输出才为 1,其他 LUT 均输出 0。

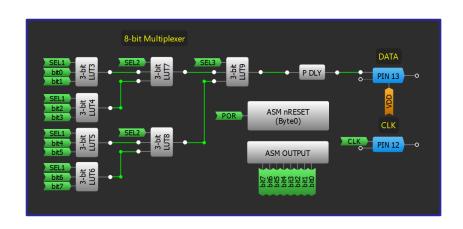

#### 应用: 8位多路复用器

多路复用器[MUX]用于从多路输入信号中选择一个作为输出,用 GreenPAK 实现的MUX 传输延时可以和分立式逻辑 IC 相当,为纳 秒级别。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

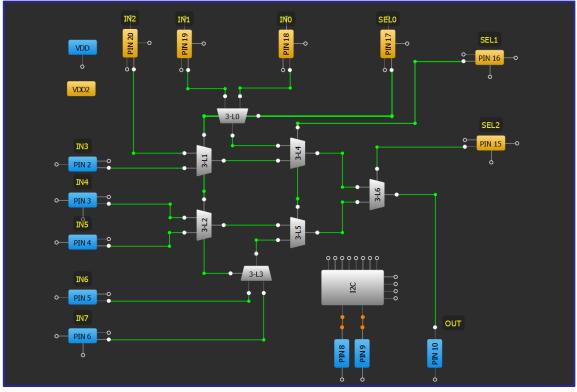

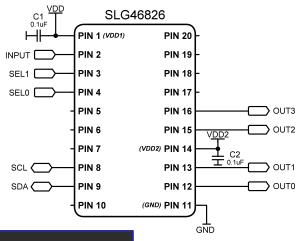

#### GreenPAK 设计图

- 1. 使用 技巧: 配置标准逻辑 将 4 个 3-bit LUTO/DFF/LATCH 配置为 Multiplexer, 然后将 Multiplexer 的 A 输入或 B 输入与各路输入相连接, 最后将 4 个 Multiplexer 的 S 都连接到 SELO 位。

- 2. 添加第二级和第三级 Multiplexer 以创建更高位的 SEL 位[SEL1 和 SEL2]。

- 3. 将最后一级 Multiplexer 的输出信号连接至输出脚。

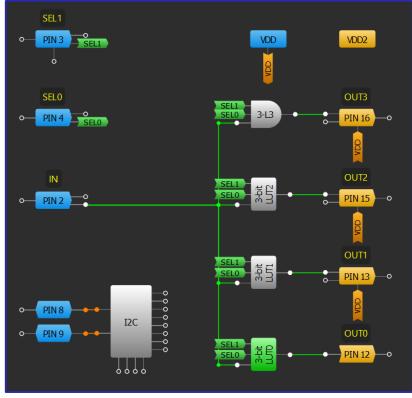

#### 应用: 多路输出选择器

多路输出选择器用于从几个通道中选择其中一个(或几个)作为一个输入信号的输出通道。在需要通过单根线发送几种不同类型的数据应用中,多路输出选择器被使用。这在通信系统中很常见。

#### 所需元器件

- 任意 GreenPAK IC

- 无需其他元器件

#### GeenPAK 设计图

- 1. 配置输入脚为 1 个信号输入(IN), 2 个选择线(SELx)及 4 个输出脚(OUTx)配置输入引脚。

- 2. 将 LUT 配置为每个通过选择线上的特定逻辑输入传递来自 IN 的信号。 例如,当 SELO、SEL1 和 IN 为 HIGH 时,3-L3 输出为 HIGH。

# 第2章:时序逻辑

本章会介绍涉及时序逻辑的应用。一些时序逻辑应用程序是指计数器、 系统复位电路、电源时序器和状态机。

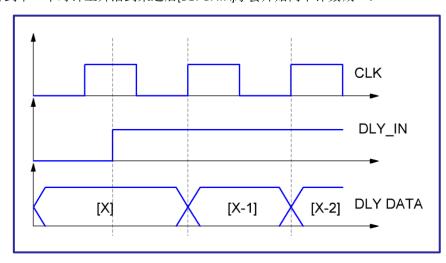

#### 技巧: 优化 CNT/DLY 的精度

此技巧适用于所有GreenPAK,振荡器和CNT/DLY 的精度因器件而异。

和所有带内部振荡器的芯片一样,GreenPAK 在时序上也带有固有的偏差,这归因于制造、温度以及用户设计等因素。通过遵循一些简单的设计规则,可以提高 GreenPAK 中 Counter 和 Delay 的精度。

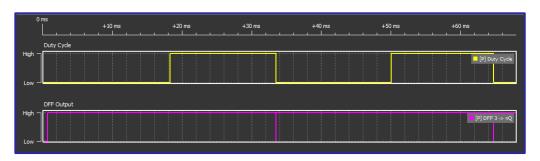

应当考虑振荡器和 CNT/DLY 之间的联系,振荡器是全局的,可以用在所有的 CNT/DLY 中,而且不会和 counter 和 delay 的起始和结束信号同步,因此 counter 或者 delay 在使能信号到来之后,只有等到振荡器的下一个时钟沿到来之后才会真的开始,就如下图所示,一个 delay 的使能信号[DLY\_IN]的上升沿发生在时钟电平[CLK]的中间,所以只会等到下一个时钟上升沿到来之后[DLY DATA]才会开始向下计数减一。

上升沿延时时序

将这个因素考虑进去之后, CNT/DLY 延时时间计算公式如下:

$$Delay_{time}(typical) = \frac{(Counter\_Data + 1) + t}{clock}$$

, where t is between 0 and 1

因此随着 Counter data 值的增大,t 对延时时间的影响将会减小,使用了更大的 Counter data 之后,如果要保持延时时间不变,就需要使用一个更快的时钟 [更大的F Clock],在 **Properties** 窗口,可以为 CNT/DLY 配置 **Counter data** 和**时钟源**。

此外,参考各个 GreenPAK 数据表内关于时序的特性时,应当考虑 Power-ON 时间、频率稳定时间、温度变化等因素所造成的偏差。

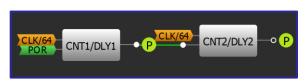

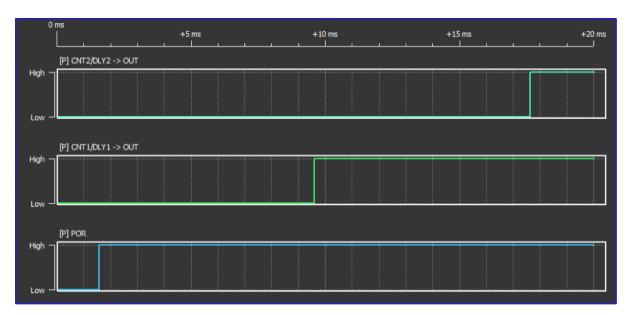

#### 技巧: CNT/DLY 的级联

此技巧适用于所有GreenPAK。

DLY可以进行级联,通过把前一个DLY的OUT连接到后一个DLY的DLY\_IN的方式可以将一连串的DLY连接起来,也就是DLY的级联。

级联上升沿延时

先在 Properties 窗口的 Mode 选项里选择 Delay 模式,通常

还需要将所有 DLY 的 Edge select 设置为一样, 下图显示了将 2 个设置为上升沿延时 8ms 的 CNT/DLY 级联作用于 Power-ON-Reset (POR) 信号上的效果。

级联延时仿真

CNT 同样可以级联以获得更长的计时,CNT 是通过将前一个 CNT 的 OUT 连接到后一个 CNT 的 CLK 上来实现级联的,先用鼠标选择后一个 CNT,然后在 **Properties** 窗口的 Connections 栏的 **Clock** 选项里选择前一个 CNTx/DLYx 的 OUT 作为时钟源。

级联计数器

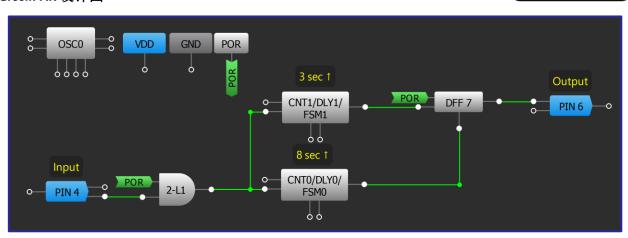

#### 应用:系统复位

复位 IC 被用在故障、手动复位、欠压等情况下为微处理器提供一个复位信号。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 将输入信号的 I/O 配置为 Digital input。

- 2. 添加 LUT 逻辑单元以在任何复位信号激活时发出正确的复位信号,逻辑关系取决于高电平有效还是低电平有效。

- 3. 配置一个 CNT/DLY 模块为 One shot 模式, Edge select 为 Rising, 根据所需的脉冲宽度设置相应的 Counter data, 对于低电平有效的脉冲,将 Output polarity 选择为 Inverted(nOUT)。

- 4. 将 CNT/DLY 模块的 OUT 连接至输出引脚。

#### 应用:多按钮复位

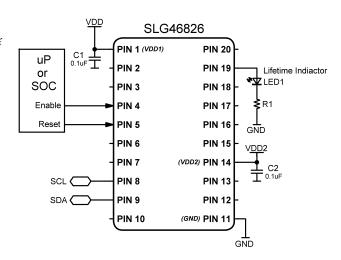

同时按住多个按钮来触发复位是许多设备常见的交互方式,用一个独立的IC 实现此功能是为了确保系统中的其他部分遇到一个或者多个软件、固件或者硬件故障时,复位仍然能够得到确认和响应。

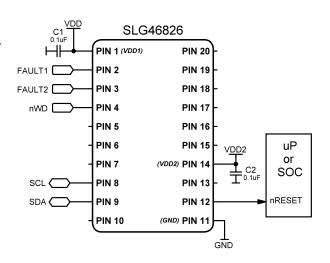

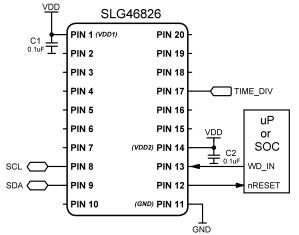

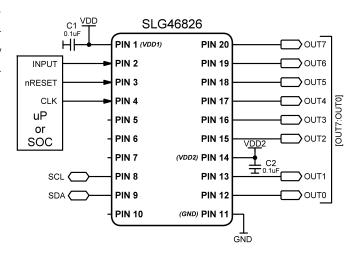

#### C1 T SLG46826 PIN 1 (VDD1) **PIN 20** PIN 2 **PIN 19** BUTTON1 ( PIN 3 **PIN 18** BUTTON2 PIN 4 **PIN 17** PIN 5 **PIN 16** PIN 6 **PIN 15** uΡ or PIN 7 (VDD2) PIN 14 SOC PIN 8 **PIN 13** SCL ( nRESET PIN 9 SDA C **PIN 12 PIN 10** (GND) PIN 11 GND

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

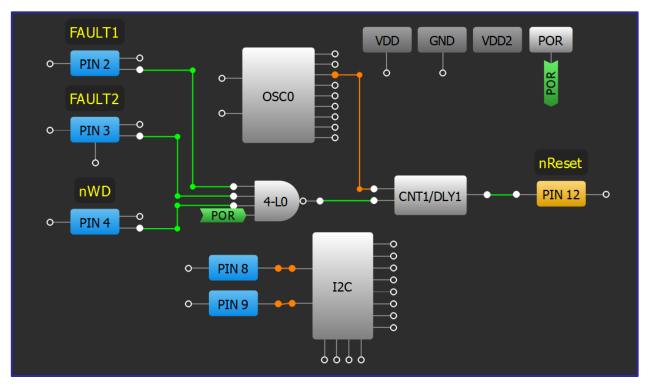

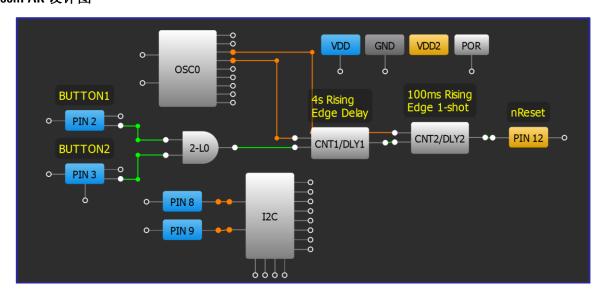

#### GreenPAK 设计图

- 1. 将每个按钮对应的 I/O 配置为 Digital input。

- 2. 添加 LUT 逻辑单元以在所有按钮都处于活动状态时发出正确的复位信号,逻辑关系取决于高电平有效还 是低电平有效。

- 3. 将一个 CNT/DLY 模块配置为 Delay 模式,Edge select 选为 Rising,根据按钮所要求按下的时间长度设置相应的 Counter data,对于低电平有效的脉冲,将 Output polarity 选择为 Non-inverted (OUT)。

- 4. 将一个 CNT/DLY 模块配置为 One shot 模式, Edge select 选为 Rising, 根据复位信号所需的脉冲宽度设置相应的 Counter data, 对于低电平有效的脉冲, Output polarity 选择 Inverted( nOUT )

- 5. 将 CNT / DLY 模块的 OUT 连接至输出引脚。

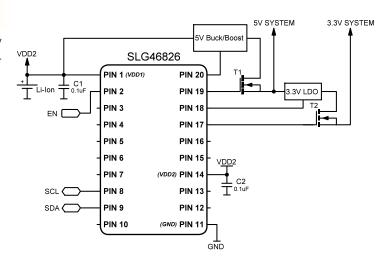

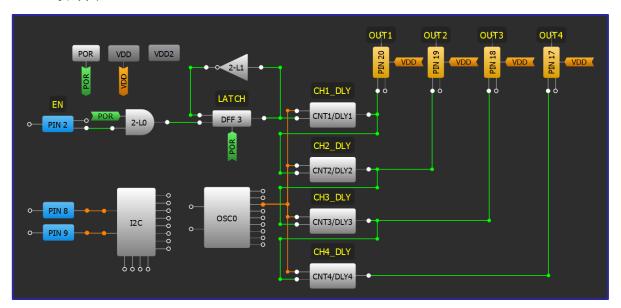

#### 应用: 电源序列发生器

当设计人员需要按顺序激活系统的不同部分时会用到 电源序列发生器。这对于有多个电源轨的系统来说至 关重要。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 按照所需的启动条件配置 LUT。

- 使用一个锁存器或 DFF 来维持启动信号,以便 DLY 模块可以读取它。

- 3. 使用 技巧: CNT/DLY 的级联 将各个 DLY 模块级联。

- 4. 将各个 DLY 模块的 OUT 连接到相应的输出引脚。

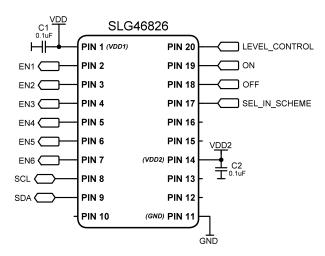

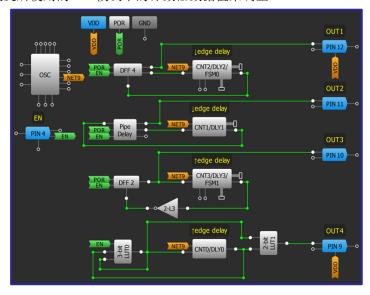

#### 应用: 电源时序控制器

当设计人员需要按顺序激活系统的不同部分时会用到电源序 列发生器。这是一种很典型的电源时序,只有当其他电源轨 关闭后,这个控制芯片的电源才会关闭。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 配置输入信号源,可以通过 PIN17 在 Level 和 Lactching 两个模式间进行选择。

- 2. 通过多路选择器 Multiplex 将控制信号输入给到 DLY 模块,使用这样一个多功能复用模块达到级联时序的效果。

- 3. 将各个 DLY 模块的 OUT 连接到相应的输出引脚。

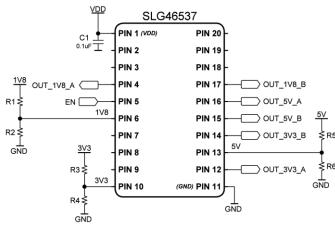

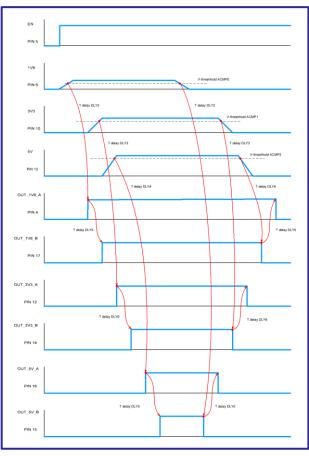

#### 应用: 电压监测电源时序控制器

设计人员可以通过序列时序来实现按顺序激活系统的各个 部分, 通过监控电源轨和故障条件来调整系统所需的时 序。

#### 所需元器件

- 任何带有 3 个模拟比较器的 GreenPAK IC(CMIC)

- 6个电阻

#### GreenPAK 设计图

- 1. 将 EN 和 Voltage Monitoring 的 PINs 脚配置为输入。

- 2. 将系统电源控制时序信号的 PINs 脚配置为输出。

- 3. 启动 ACMP, 将 POR 连接到 PWR UP, 并将每个 ACMP 的 IN- 端配置到所需的电压阈值(比较器反转电压 阈值)。

- 4. 根据需要的延时时间配置 DLY 的 Counter data。

- 5. 根据需要的逻辑功能配置 LUT。

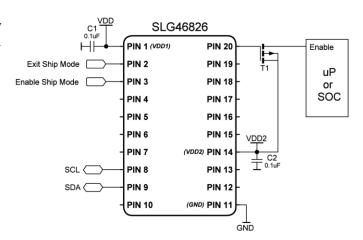

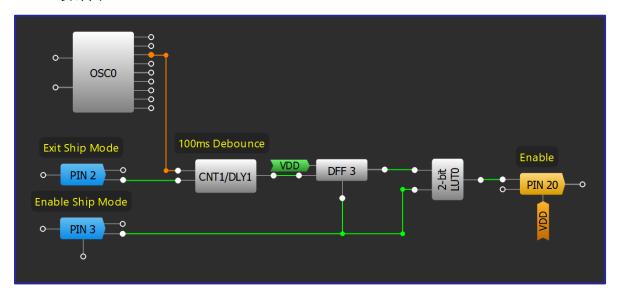

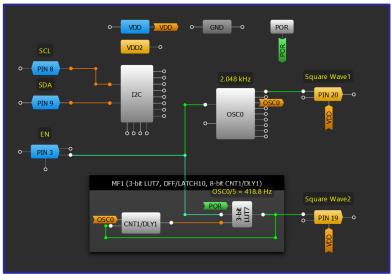

#### 应用:运输模式控制器

在产品还未交付到用户手上之前,使用一个超低功耗的 按钮监视器能够延长电池放电时间,可以给用户提供一 个更好的上手体验。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 外部 PMOS 负载开关

#### GreenPAK 设计图

- 1. 配置 PIN2 为带 1MΩ 上拉电阻的输入引脚。

- 2. 根据需要的去抖动时间配置 CNT1/DLY1 的 Counter data。

- 3. 根据进入运输模式和退出运输模式对应的输出电平配置 LUT 的逻辑。

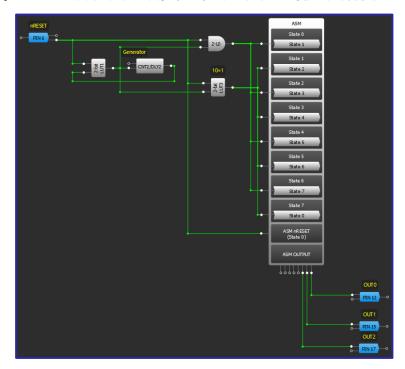

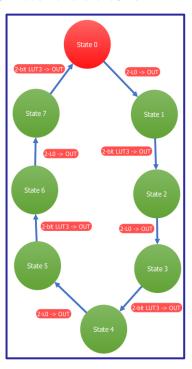

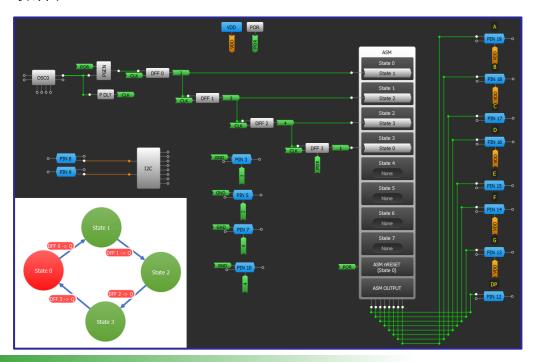

#### 技巧: 由异步状态机创建同步状态机

同步状态机 (SSM) 是在转换条件满足的情况下在时钟沿到达时进行状态转移。把 GreenPAK 芯片中的 **异步状态** 机(ASM)宏单元转换成同步状态机的通常方法是使用脉冲宽度大于 ASM 状态转换时间的时钟信号。

上图展示了 SSM 在 3 位计数器中的应用。 CNT2 和 2-bit LUT1 用于生成时钟信号。 ASM 的 8 个状态位串联连接。 2-bit LUT0 和 2-bit LUT3 用于防止一个逻辑高电平信号使两个相邻状态位同时发生状态转换。 ASM 输出的状态值如下表所示。

|               |      | Con  | nectio | n Mat | rix Ou | ıtput l | RAM  |      |

|---------------|------|------|--------|-------|--------|---------|------|------|

| State<br>name | OUT7 | OUT6 | OUTS   | OUT4  | OUT3   | OUT2    | OUT1 | OUTO |

| State 0       | 0    | 0    | 0      | 0     | 0      | 0       | 0    | 0    |

| State 1       | 0    | 0    | 0      | 0     | 0      | 0       | 0    | 1    |

| State 2       | 0    | 0    | 0      | 0     | 0      | 0       | 1    | 0    |

| State 3       | 0    | 0    | 0      | 0     | 0      | 0       | 1    | 1    |

| State 4       | 0    | 0    | 0      | 0     | 0      | 1       | 0    | 0    |

| State 5       | 0    | 0    | 0      | 0     | 0      | 1       | 0    | 1    |

| State 6       | 0    | 0    | 0      | 0     | 0      | 1       | 1    | 0    |

| State 7       | 0    | 0    | 0      | 0     | 0      | 1       | 1    | 1    |

当 **6 脚**变为高电平时,ASM 由复位状态 (State 0) 转移为下一状态 (State 1)。 以下状态转换是随着时钟信号 **CNT2** 不断切换为高低电平而完成的。

更多关于异步状态机转换为同步状态机的信息,请参考 "AN-1126 ASM 到同步状态机转换"

#### 应用: N 比特流

比特流是在通信路径上连续传输的比特序列。GreenPAK 能够创建多达64 位的重复字符串。

#### 所需元器件

• 任意带有 ASM 模块的 GreenPAK IC(CMIC)

#### GreenPAK 设计图

- 1. 使用应用: 8位多路复用器配置信号发生器和8位多路复用器。

- 2. 配置 CNT1 定义比特流的长度。

- 3. 使用 技巧: 由异步状态机创建同步状态机 配置 ASM。

- 4. 将8位多路复用器和信号发生器的输出连接至输出脚。

- 5. 可以通过 I<sup>2</sup>C 改变比特流的长度 (CNT1 的 counter data)。

- 6. 也可以通过 I<sup>2</sup>C 改变 ASM 输出 RAM 中的数据。

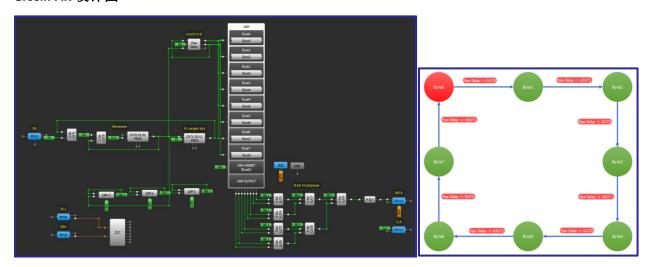

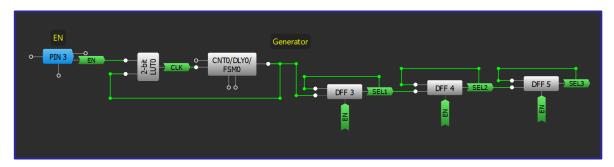

#### 技巧: 多路复用比特流

此技巧适用于所有GreenPAK 芯片。

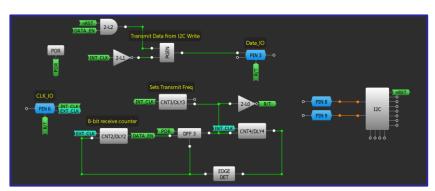

GreenPAK 常用于数据传输。 通过 GreenPAK 传输数据 或 从 SoC 传输多路数据, 必须将数据合并从而在一条线路上进行传输。以下是 GreenPAK 传输源自 ASM 输出 RAM 的多路数据的一个示例。

**发生**电路如上图所示。由 **EN** 信号控制,发生器可实现由 CLK 产生,可实现数据的同步传输。发生器设定了将传输数据复合到一条线上的操作规则。

| IN3 | IN2 | IN1     | INO                      | OUT |

|-----|-----|---------|--------------------------|-----|

| 0   | 0   | 0       | 0                        | 0   |

| 0   | 0   | 0       | 0 1<br>1 0<br>1 1<br>0 0 |     |

| 0   | 0   | 1       |                          |     |

| 0   | 0   | 1       |                          |     |

| 0   | 1   | 0       |                          |     |

| 0   | 1   | 0 1 1 0 |                          | 0   |

| 0   | 1   |         |                          | 1   |

| 0   | 1   | 1       | 1 1                      |     |

| 1   | 0   | 0       |                          |     |

| 1   | 0   | 0 1     |                          | 0   |

| 1   | 0   | 1       | 1 0                      |     |

| 1   | 0   | 1 1 0 0 |                          | 0   |

| 1   | 1   |         |                          | 0   |

| 1   | 1   | 0       | 0 1                      |     |

| 1   | 1   | 1       | 0                        | 0   |

| 1   | 1   | 1       | 1                        | 0   |

8位多路复用器如上图所示。将7个3-bit LUT 配置为8位多路复用器(参考 AN-1003)。多路复用[MUX]真值表如右上所示。多路复用器按照发生器设定的复合规则将 ASM 模块输出的数据组合在一起后传输到 DATA。当 EN为低电平时,DATA 的输出结果与 ASM 输出 RAM 的最高有效位一致。ASM 输出 RAM 可以通过 I<sup>2</sup>C 改变,也可以通过触发 ASM 的状态改变来改变数据的各个位。 如果 ASM 不可用也可以通过手动将输入拉高或拉低来修改数据位。

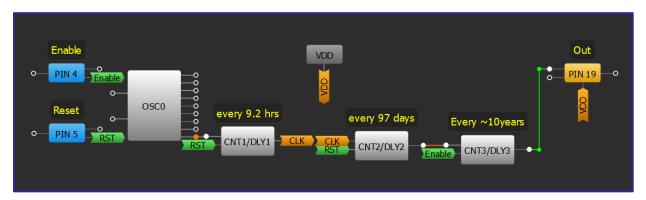

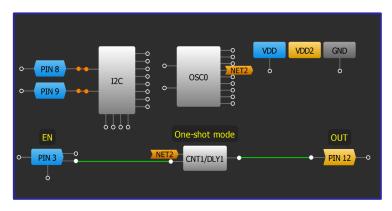

#### 应用: 10年定时器

超长定时器用于确定产品的使用寿命,而无需占用太多功耗预算。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 使用 技巧: CNT/DLY 的级联 将各个 Counter 模块级联。

- 2. 连接输入引脚和输出引脚。

- 3. 配置 CNT 的 Properties。

#### 应用:方波发生器

方波对于数字时钟系统是必不可少的。它们可以通过使用振荡器 块或定制频率的延迟逻辑,从而很容易地在GreenPAK 中实现。

#### 所需元器件

- 任意 GreenPAK IC

- 无需其他元器件

#### GreenPAK 设计图

#### 设计步骤

- 1. 配置 EN 输入和方波输出。

- 2. 使用内部振荡器在 PIN20 上产生一个方波。 "CLK" 预分频器和 "OUTO" 二次分频器可以更改以自定义频率。

- 3. 使用边缘延迟(CNT1)和 LUT 在 PIN19 上产生一个方波。 这种配置允许用户通过更精细的调整来分割方波的频率。

$Division\ Coefficient = Counter\ Data + 2$

PIN 20

**PIN 19**

PIN 18

**PIN 17**

**PIN 16**

**PIN 15**

**PIN 14**

**PIN 13**

PIN 12

GND

(GND) PIN 11

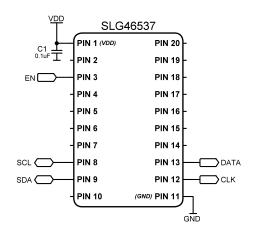

SLG46537

PIN 1 (VDD)

PIN 2

PIN 3 PIN 4

PIN 5

PIN 6

PIN 7

PIN 8

PIN 9

**PIN 10**

<u>VDD</u>

0.1uFT

Input[

R1≱

GND

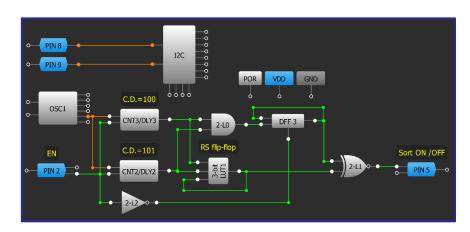

#### 应用:按下多个事件按钮

使用单个按钮生成多个事件是节省外部控制组件的常见解决方案。 使用一个按钮和预定的时间间隔,您可自定义控制一个LED 手电筒。

#### 所需元器件

- 任意 Green PAK IC

- 1个LED

- 1个电阻器

#### GreenPAK 设计图

- 1. 将 GPIO 引脚配置为按钮的输入和 LED 控制的输出。

- 2. 添加 CNTO/DLYO, CNT1/DLY1 和一个 DFF 来记住最后的状态。

- 3. 将 CNT/DLY 模块配置为"延迟"模式, Edge select 选为"Rising"。

- 4. 将 CNTO/DLYO 的输出配置为"nOUT"。

# 第3章:信号调理

本章通过详细讲解外部信号并使其成为对系统操作有用的应用。涉及到这 方面的一些应用包括分频/倍增、滤波器和传感器控制器。

#### 技巧:利用 CNT/DLY 滤除毛刺

此技巧适用于所有GreenPAK 芯片。

去毛刺/去抖动过滤器用于消除毛刺[虚假的信号暂态]。毛刺可以在很多情况下产生,比如,按钮的按压、释放或电压非常接近不带迟滞的引脚阈值的时候。

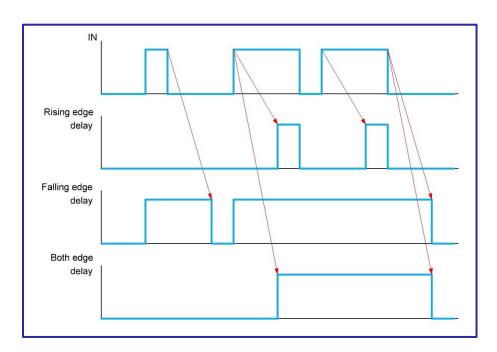

有 3 种可选的边沿触发选项来抑制毛刺: 上升沿、下降沿和双边沿,Delay 将会滤除短于 Delay 值的脉冲,3 种不同配置的影响见下图:

防抖延时示例

不同边沿延时时序

#### 技巧: 边沿检测器

此技巧适用于所有GreenPAK 芯片。

边沿检测器在数字电路中是非常重要的组件。它是一种单路输入和单路输出的简单电路。边沿检测器在检测到边沿信号时(上升沿,下降沿,或者两者兼具的双边沿)产生一个短的脉冲信号。通常用于实现复位功能、看门狗定时器或者其他需要边沿触发的应用。有以下几种方法实现边沿检测(见下图)。了解更详细的如何建立一个边沿触发器以及更多的应用案例请参考 AN-1046 多种边沿检测电路。

边沿检测器示例

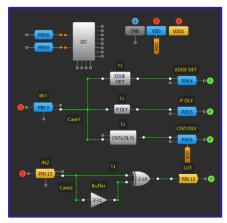

方法 1 使用边沿检测(EDGE DET)、可设定延时器(P DLY)和计数器/延时器(CNT/DLY)模块来获得边沿检测器。与方法 2 (如下图) 相比,这些模块可产生一个持续时间更长的脉冲。

不同的边沿检测器时序

方法 2 利用信号经由缓冲器传输的短暂延迟。这个延迟信号通过一个 2 位的 XOR(异或)与初始输入信号进行逻辑异或,原始输入信号的传输时间非常短。通过缓冲器的短暂延迟会导致 XOR 输入之间的差异,从而在其输出上生成一个短脉冲。由于查找表的内部结构,它们的每个输入具有不同的传输延迟时间。

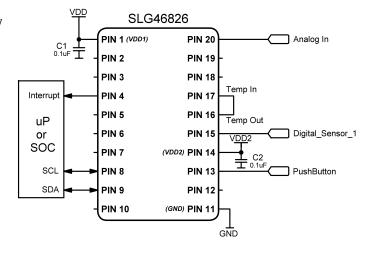

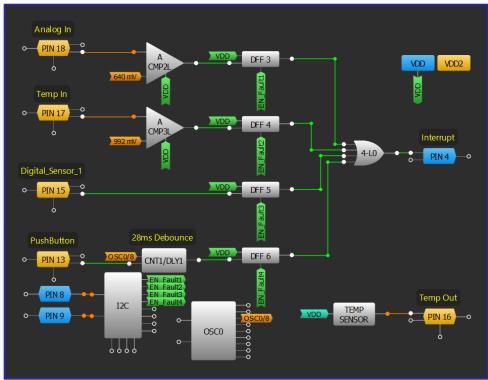

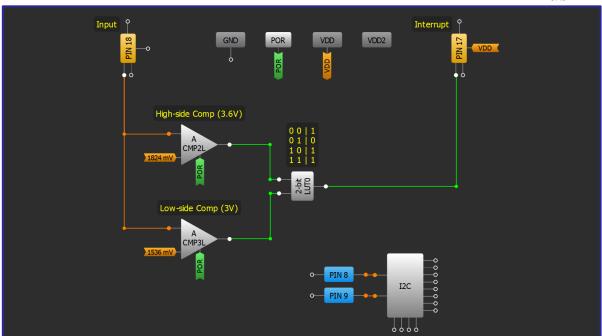

# 应用:中断控制器

GreenPAK 可以配置为监控多个不同中断信号,并将这些不同的中断信号整合为一个中断信号以通知处理器进行处理,微处理器或者 SOC 可以通过 I<sup>2</sup>C 接口读取每个 DFF 的输出值来确定中断源。

### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 配置 PIN16、PIN17、PIN18 为 Analog Input/Output。

- 2. 根据需求为 ACMP 配置合适的阈值。

- 3. 将所有 DFF 的输出连接到 OR 门,并将 PIN4 配置为 Digital output。

- 4. 根据需要的去抖时间配置 DLY1 的 Counter data。

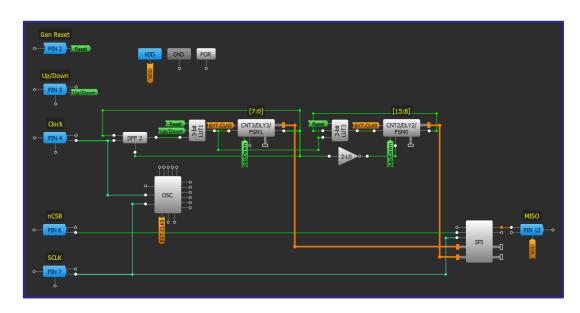

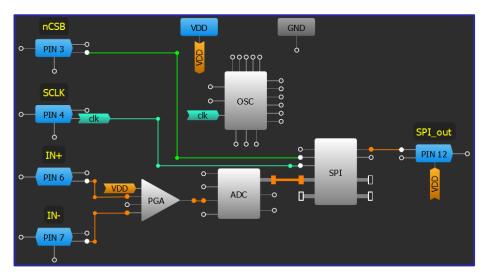

# 技巧: 构建一个双向计数器

此技巧适用于所有带有SPI接口的GreenPAK 芯片。另外一种方法是使用其他带有FSM 模块的GreenPAK 芯片,使用PC 读取命令、并行输出或其他方式存储计数器信息。

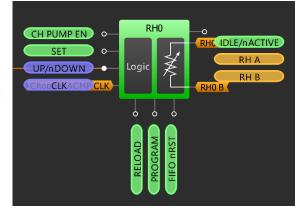

计数器是用于记录事件(脉冲、边沿)数量的基本电路,它主要由具有记忆功能的触发器构成。 GreenPAK 芯片中,CNT/DLY 模块的功能非常强大,可用作有限状态机(FSM),进行向上计数、向下计数或保持当前值,具体由 GreenPAK 电路的连接方式而定。此技巧通过使用 GreenPAK 芯片中的 2 个 FSM 模块,监测脉冲输入(时钟)数量和利用 SLG46140V 的 SPI 宏单元输出 16 位脉冲序列。

带有 SPI 输出 的 16 位 FSM

"16 位 FSM 输出连接至 SPI"通过一个 16 位寄存器 (FSM0, FSM1) 对输入时钟脉冲计数。 用户可以随时通过 SPI 读取该数值,复位 16 位寄存器或者改变计数方式。

该 16 位计数器使用 2 个计数模块 (FSM0 和 FSM1 模块) 和一些额外的逻辑单元。 高位 [15:8] 存储在 FSM0,低位 [7:0] 存储在 FSM1。两个 FSM 均连接到 SPI 模块转换成串行数据输出。计数模式由连接到 FSM 模块的 Up/Down 脚控制,直接连接到 FSM 模块的 UP 脚。 当该脚为高电平时,系统向上计数;当该脚为低电平时,系统向下计数。 Gen Reset 脚用于复位两个计数器的值(高电平有效)。

时钟输入脚同时连接到 FSM1 和 FSM0 的 CLK。 FSM1 对每个时钟周期进行计数;当 FSM1 的数值达到计数上限值 255 且 Up/Down 信号为高电平或者当 FSM1 的数值达到计数下限值 0 且 Up/Down 信号为低电平时,FSM0 开始进行计数。 上述控制通过 FSM0 的 Keep 脚实现。 当该信号为高电平时, 无论是否有时钟信号输入,FSM0 的计数值不变。 FSM1 的输出信号通过一个反相器连接到 FSM0 的 KEEP 脚。 FSM1 计数时,输出信号为低电平;只有当 FSM1 的数值达到计数上限值 255 且 Up/Down 信号为高电平或者当 FSM1 的数值达到计数下限值 0 且 Up/Down 信号为低电平时,FSM1 输出信号为高电平。

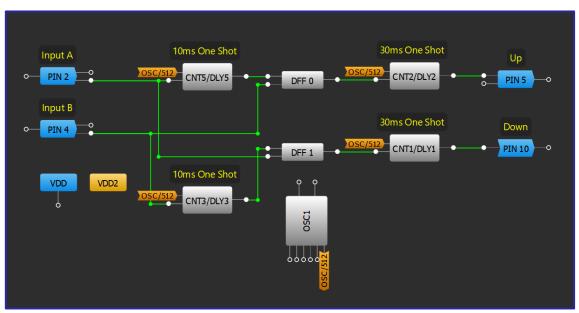

# 应用: 编码器

编码器用来将旋转运动或者线性运动转换为数字信号,下面的设计非常适合鼠标滚轮和耳机音量控制这类应用。

# 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 将A和B信号输入脚配置为 Digital input。

- 2. 将两个引脚配置为输出来指定编码器的运动方向。

- 3. 根据滤波需要,将 CNT3/DLY3 和 CNT5/DLY5 配置为 One shot 模式并设置相应的 Counter data。

- 4. 配置 DFF 以检测运动方向 (上或下)。

- 5. 根据需要输出的脉冲宽度,将 CNT1/DLY1 和 CNT2/DLY2 配置为 One shot 模式,并设置相应的 Counter data。

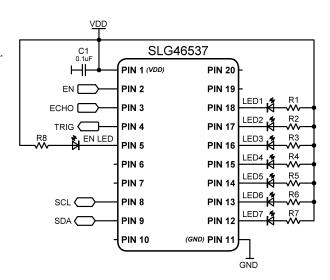

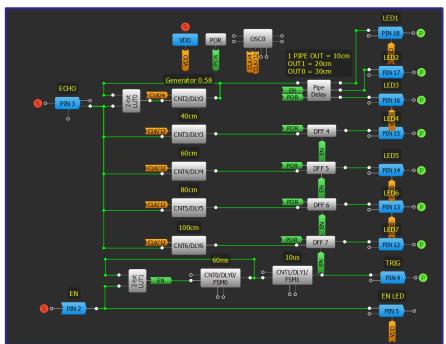

# 应用: 距离感应器

超声波测距模块可提供非接触式距离感测功能。本设计是一种基于HC-SR04的超声波测距仪控制器。

# 所需元器件

- 任意 GreenPAK IC(CMIC)

- 每个距离测量所需的 LED

- 每个距离测量所需的电阻

### GreenPAK 设计图

- 1. 配置 **ECHO** 对应的 I/O 为 Digital input, **TRIG** 对应的 I/O 为 Digital output。

- 2. 添加 LUT 逻辑单元和 CNT/DLYO 以创建一个带有 ENABLE 信号的发生器。

- 3. 添加 Pipe Delay 和 CNT/DLY2 以创建一个距离探测发生器。

- 4. 将 CNT/DLY 模块配置为 rising edge delay 模式以测量不同的距离。

- 5. 添加并配置 DFFs 来保存距离信息。

- 6. 将各个 DFF 模块的 OUT 连接到相应的输出引脚并配置为 open drain。

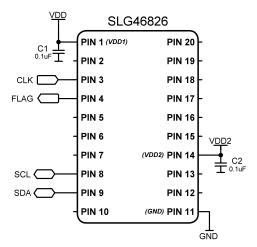

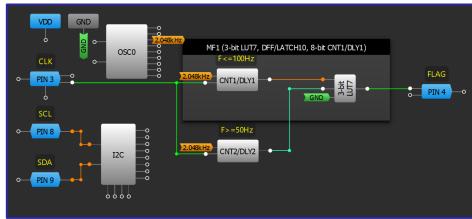

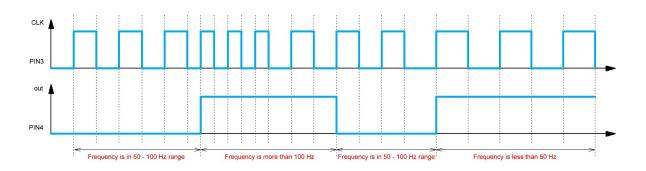

# 应用:频率范围探测器

许多设备都有特定的工作频率范围,这要求它们运行并要求对输入时钟 信号进行检测,确保此时钟频率符合要求。本设计可用于检测输入时钟 频率是否在所需的频率范围内。

# 所需元器件

任意 GreenPAK IC(CMIC)

### GreenPAK 设计图

- 1. 配置时钟信号对应的 I/O 为 Digital input, 标志位对应的 I/O 为 Digital output。

- 2. 将 CNT/DLY 模块配置为 Frequency detect 模式,Edge detect 选为 rising。

- 3. 将每个 CNT/DLY 模块分别设置为最小和最大频率值。

- 4. 把一个 LUT 配置成如果频率在所需范围之外将会输出高。

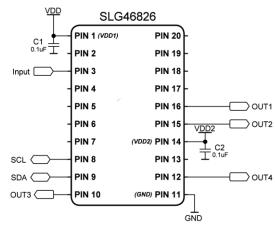

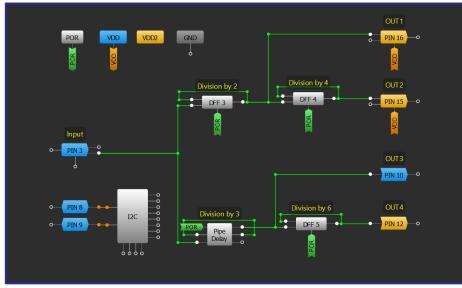

# 应用:分频器

分频器用于按不同的系数降低输入信号源频率,可用于提高电子对抗设备、通信系统和实验室仪器的性能。

# 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 配置信号输入源对应的 I/O 为 Digital input

- 2. 利用 DFF 和 Pipe Delay 分割一次频率。

- 3. 利用另外一个 DFF 将信号频率又分割一次。

- 4. 为各个输出添加并配置 LUT。

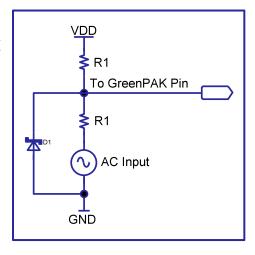

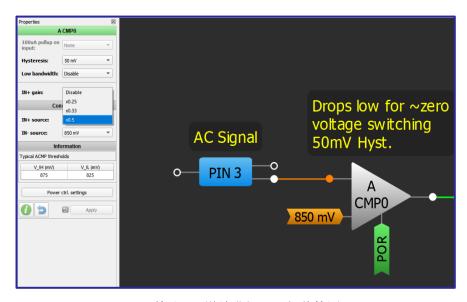

# 技巧: 过零检测

此技巧适用于包含ACMP 的GreenPAK。

过零检测通常应用于检测准确的交流特性,比如频率和相位。

GreenPAK 的输入电压范围为 0V 到 VDD,VDD 最大为 5.5V,利用 GreenPAK 检测一个交流信号的过零点,需要先将一个直流偏置信号叠加到交流信号上,如 右图 - 基本的直流偏置电路 所示的那样,通过在 VDD 和交流信号中间添加一个 1:1 的分压电阻来实现。

过零检测至少需要一个或者两个比较器和一个计数器,比较器根据参考电压检测交流输入信号,参考电压既可以是 GreenPAK 内部的参考电压也可以是外部参考电压, 如果所需的过零检测阈值电压大于 GreenPAK 内部所有的参考电压,可通过在 Properties 窗口中设置 IN+ gain 以降低交流信号幅值。

基本的直流偏置电路

利用 IN+增益进行 1.7V 阈值检测

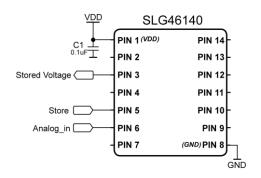

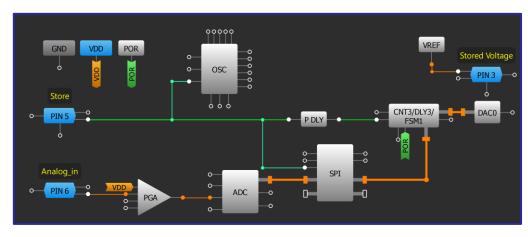

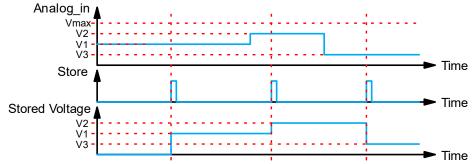

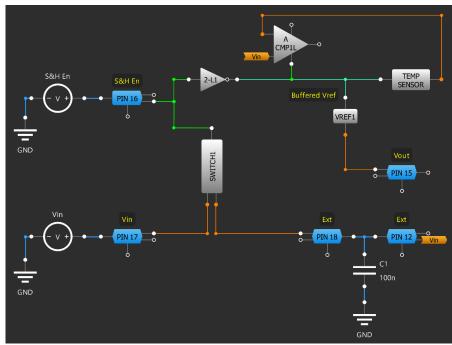

# 应用:模拟存储元件

该应用可用于在输出上存储模拟电压,直到上升沿被应用到 Store 输入。输入输出模拟电压在 0-1V 范围内。

# 所需元器件

• 任意带有 ADC, SPI, 和 DAC 模块的 GreenPAK IC

### GreenPAK 设计图

- 1. 配置 SPI 为"ADC/FSM buffer"模式,修改 PAR input data source 为"ADC"。

- 2. 配置 FSMO 为"Set (counter value = FSM data)", 修改 FSM data source 为"SPI[7:0]"。

- 3. 配置 DAC Input selection 为"From DCMP1's input", VREF Source selector 为"DACO out"。

- 4. 将 Store 输入直接连接到 SPI SCLK,通过 P DLY(设置为)边缘延迟后连到 FSM1 SET IN。

# 第 4 章:安全功能

本章介绍了一些应用程序,这些应用程序旨在响应系统中的故障条件,并 保护系统免受损坏。一些为电子系统提供安全性的应用是指充电量示器、 看门狗定时器和温度传感器。

# 技巧:如何降低 ACMP 的功耗

此技巧适用于包含 ACMP 的 GreenPAK,但是不同芯片功耗降低的多少会有所不同。

GreenPAK 通常用来降低系统功耗,然而 GreenPAK 内有几种组件在启用时会显著增大功 耗,其中最明显的就是模拟比较器,表1截取 自 SLG46826 的数据手册,并用红框突出显示了 ACMP 在各种条件下的电流消耗值。

幸运的是,ACMP可以在不使用时关闭,这可以通过2种方式来实现:

- 1. 通过控制 ACMP 的 PWR UP 脚。

- 2. 为 ACMP 启用唤醒-休眠定时器(WS Ctrl)。

唤醒-休眠控制需要将一个专用的定时器配置在 "Wake sleep controller"模式,许多(但不是所有) GreenPAK 都包含此功能。PWR UP 的控制方式可以应用于所有带 ACMP 的 GreenPAK 芯片中,当信号为高时 ACMP 启用,通过使用逻

表 1 SLG46826 电流消耗值

| Note                                                                                                      | V <sub>DD</sub> = 2.5 V | V <sub>DD</sub> = 3.3 V | V <sub>DD</sub> = 5.0 V | Unit |

|-----------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|------|

| Chip Quiescent                                                                                            | 0.39                    | 0.43                    | 0.53                    | μА   |

| Vref OUT0 (Source none, Source Temp<br>Sensor, Buffer On)                                                 | 12.79                   | 12.95                   | 13.57                   | μА   |

| Vref OUT0 (Source none, Source Temp<br>Sensor, Buffer Off)                                                | 7.62                    | 7.67                    | 7.87                    | μА   |

| Vref OUT1 (Source none, Buffer On)                                                                        | 6.53                    | 6.61                    | 7.02                    | μΑ   |

| Vref OUT1 (Source none, Buffer Off)                                                                       | 1.40                    | 1.44                    | 1.54                    | μА   |

| Vref (ACMPxH, 0.32 mV, Buffer On)                                                                         | 12.24                   | 12.59                   | 12.21                   | μΑ   |

| Vref (ACMPxL, 0.32 mV, Buffer On)                                                                         | 6.93                    | 7.01                    | 7.43                    | μΑ   |

| ACMP0H, 1H, 2L, 3L,hysteresis<br>disabled, gain = 1, +IN - IO11, 12, 13, 14<br>Pull Up 1M, Vref = 32 mV   | 65.86                   | 67.12                   | 70.77                   | μА   |

| ACMP0H, 1H, 2L, 3L,hysteresis<br>disabled, gain = 1, +IN - IO11, 12, 13, 14<br>Pull Down 1M, Vref = 32 mV | 37.34                   | 38.05                   | 40.29                   | μА   |

| ACMP0H, 1H, 100 µA disabled,<br>hysteresis disabled, gain = 1, +IN - IO13,<br>14 Pull Up 1M               | 63.85                   | 65.11                   | 68.71                   | μА   |

| ACMP0H, 1H, 100 µA disabled,<br>hysteresis disabled, gain = 1, +IN - IO13,<br>14 Pull Down 1M             | 35.97                   | 36.68                   | 38.87                   | μА   |

| ACMP0H, 100 μA disabled,<br>hysteresis disabled, gain = 1, +IN - VDD,<br>Vref = 32 mV                     | 36.30                   | 36.96                   | 38.85                   | μА   |

| ACMP0H, 100 μA enabled, hysteresis<br>disabled, gain = 1, +IN - IO14 Pull Up 1M,<br>Vref = 32 mV          | 46.77                   | 47.31                   | 49.23                   | μΑ   |

| ACMP0H, 100 μA enabled, hysteresis<br>disabled, gain = 1, +IN - IO14<br>Pull Down 1M, Vref = 32 mV        | 49.02                   | 50.29                   | 53.75                   | μΑ   |

辑、计数器或者其他组件去关闭 ACMP,这样可以显著降低功耗,例如如果需要 2 个不同的电压比较阈值,则高阈值的比较器可以只等低阈值的比较器达到阈值之后,才启用。

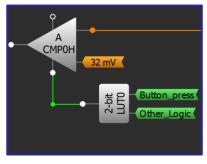

(a) Logic

(b) Duty Cycle

(c) Cascaded

常见的 PWR UP 配置

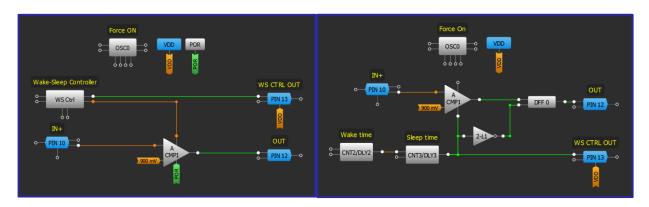

# 技巧:唤醒与休眠

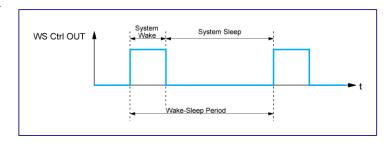

让宏单元进行休眠与唤醒可以有效降低系统功耗。模拟宏单元如ACMP 和ADC 均可进行唤醒 休眠控制。

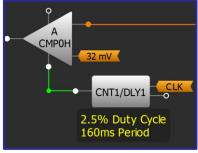

唤醒-休眠控制,允许周期性地打开和关闭这些宏单元。对于带有 WS Ctrl 模块的 GreenPAK 芯片,可利用 WS Ctrl 模块实现唤醒-休眠控制。 对于没含有此模块的 GreenPAK 芯片, 可以使用 2 个计数器, 1 个 D 类触发器和 1个反相器来实现该功能。下图中展示了上述方法的实例。

WS Ctrl 方式

2个计数器方式

没有唤醒/休眠功能时, 电路消耗的总电流由以下 两部分构成:

- 静态电流

- ACMP 电流

唤醒-休眠 时序

增加唤醒/休眠控制后,静态电流近似计算如下:

$$I_{WS} = \frac{System \ Wake}{System \ Wake + System \ Sleep} * I_{without \ WS} = \frac{System \ Wake}{WS \ Period} * I_{without \ WS}$$

带有唤醒/休眠功能时, 电路的总电流为:

$$Total\ Current = I_{Ouiescent} + I_{OSC} + I_{Wake\ Sleep}$$

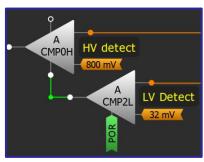

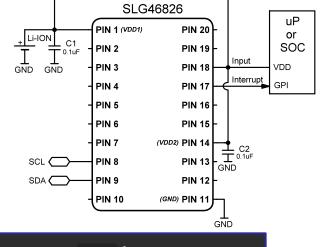

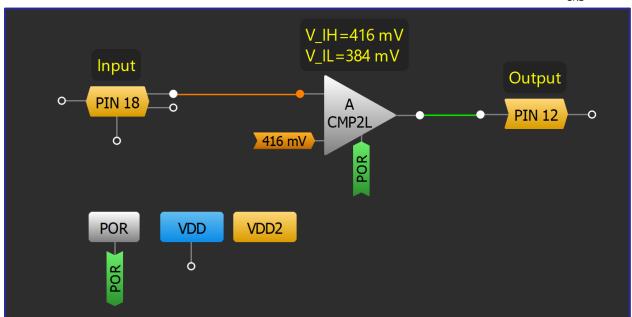

# 应用:窗口比较器

在一个利用电池或者超级电容等存储型电源来供电的设计中,窗口比较器是必须的,通过监测电池电压,设备可以在低电池电量下停止使用不必要的资源,以防止造成设备的永久性损坏。

# 所需元器件

- 任意带有 ACMP 的 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 配置比较器 ACMP2L 的 IN- source 和 IN+ gain 选项,以满足窗口需要的高侧阈值。

- 2. 重复步骤 1 配置比较器 ACMP3L,以满足窗口需要的低侧阈值。

- 3. 将 ACMP3L 的 IN+ source 配置为 ACMP2L IN+ source, 使得比较的是同一个输入源。

- 4. 添加 LUT 逻辑使得当窗口低侧阈值的比较器输出低或者高侧阈值的比较器输出高时,触发中断。

# 应用: 过温保护

过温保护电路广泛应用于高温状态提醒系统,当内部温度超过安全阈值时,该电路可以防止系统过热。

# 所需元器件

- 任意带有 ACMP 的 GreenPAK IC(CMIC)

- 1个电阻

- 1个 NTC 型热敏电阻

#### SLG46826 PIN 1 (VDD1) **PIN 20** R1**≷** PIN 2 **PIN 19** Input PIN 3 **PIN 18** PIN 4 **PIN 17** PIN 5 **PIN 16** PIN 6 **PIN 15** PIN 7 (VDD2) PIN 14 SCL ( PIN 8 **PIN 13** SDA PIN 9 **PIN 12** Output **PIN 10** (GND) PIN 11 GND

### GreenPAK 设计图

- 1. 配置 ACMP2L 的 IN+ source 为 Pin18 , IN- source 为所需的安全阈值。

- 2. 将一个电阻的一端连到 VDD 另一端连到 Pin18。

- 3. 将 NTC 电阻一端连接到 Pin18 另一端连接到 GND。

# 应用: 充电指示器

充电指示器用于指示电池供电设备的充电状态,该设计适 用于锂电池供电设备。

# 所需元器件

- 任意带有 ACMP 的 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 将 ENABLE 信号连接到所有 ACMP 的 PWR UP 脚。

- 2. 将所有 ACMP 的 IN+ source 设置为 VDD/PIN20,并将每个 ACMP 的 IN- source 设置为所需的阈值电压。

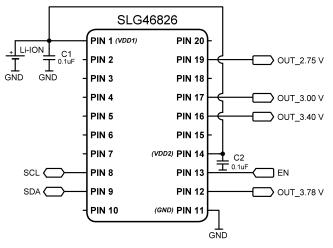

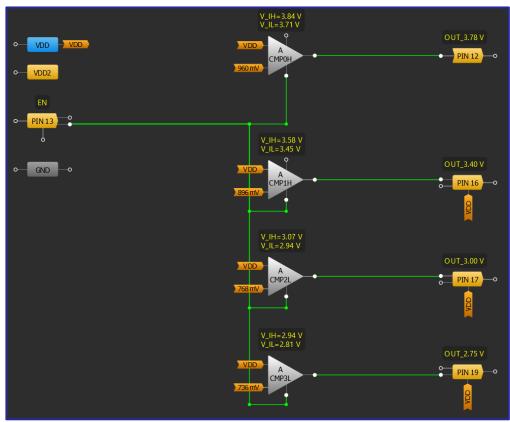

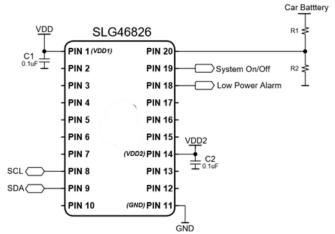

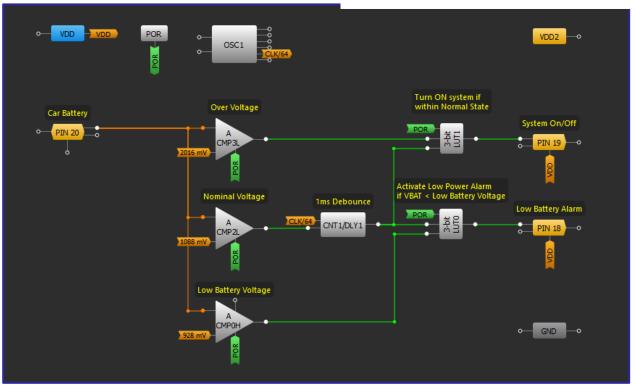

# 应用:信息娱乐系统低压指示器

电压指示器用于电池供电设备,用来指示充电状态。该设备 可以监测汽车电池的电压水平,并根据需要调整信息娱乐活 动以节省电力。

# 所需元器件

- 任意 GreenPAK IC(CMIC)

- 两个分压电阻

### GreenPAK 设计图

- 1. 将 ACMPOH IN+端配置为 PIN 20, 其它 ACMPs 的 ACMPOH IN+端配置为 ACMPOH IN+ source。

- 2. 为 PIN 20 添加一个电压分压器以处理来自汽车电池的高电压。

- 3. 将 IN- source 配置为所需的电压阈值。

- 4. 配置逻辑单元以确定输出的电压窗口。

- 5. 在 ACMP2L 和 3-bit LUT0 之间添加去抖延迟。

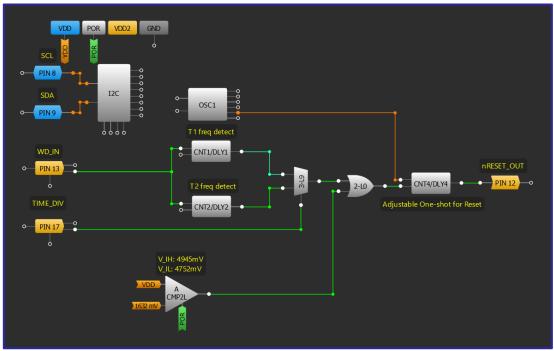

# 应用:看门狗定时器

如果微控制器或者微处理器没有周期性发送喂狗信号,看门 狗定时器将产生一个系统复位信号,看门狗芯片一般还附带 监测系统电压的功能。

### 所需元器件

- 任意带有 ACMP 的 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 用 ACMP 设置看门狗的欠压阈值。

- 2. 将一个 CNT 配置为 Frequency detects 模式。

- 3. 设置数字逻辑,以组合欠压和看门狗超时的有效信号。

- 4. 添加一个 One-shot 模式的 CNT 以输出所需脉冲宽度的复位信号,可以反转为低电平有效的输出。

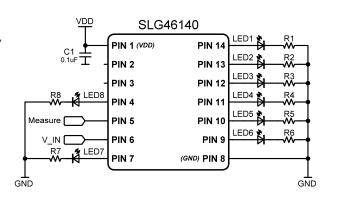

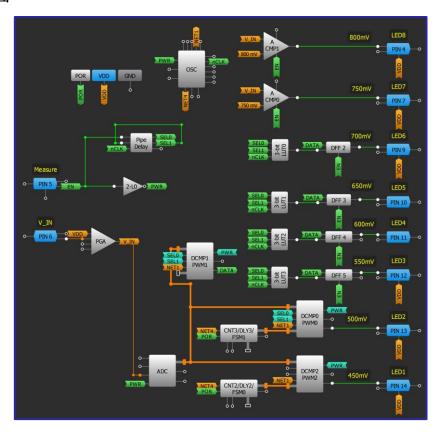

# 应用: 电压检测

在某些设计中,系统需要区分开/监控电压多种阈值等级, 而不仅仅是极少数几个不同电压等级。本设计阐述了使用 带有ACMP、DCMP 和ADC 的GreenPAK 进行电压幅值检测。

# 所需元器件

- 任意带有 ACMP, DCMP 和 1 个 ADC 的 GreenPAK IC(CMIC)

- 8个 LED 和电阻

# GreenPAK 设计图

- 1. 启用 ADC, DCMP 和 ACMP 模块。

- 2. 使用 技巧: PWM 模式下的 DCMP PWM 模块应用 配置 DCMP。

- 3. 将每个 ACMP 和 DCMP 的 IN-source 设置为所需的阈值电压。

- 4. 添加 LUT 和 DFF 逻辑单元,用以选择和写入来自于 DCMP1 中电压幅值,从而区分开不同幅值的电压等级,并将对应等级用 GPO 输出。

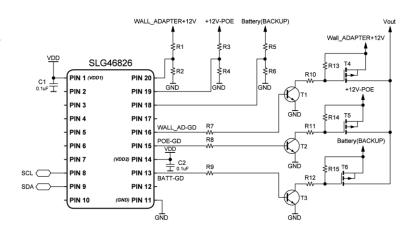

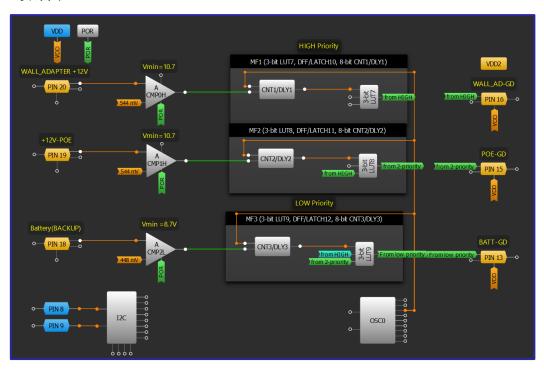

# 应用: 电源后备管理

电源后备管理用于单一电源输入的设备使用多 路电源供电时,需要为设备提供不间断供电的 系统,防止因为某一路电源异常而造成设备掉 电的情况。

# 所需元器件

- 任意带有 3 个 ACMP 的 GreenPAK IC(CMIC)

- 外接电阻分压器以将输入电压调整至 ACMP 的工作电压范围

### GreenPAK 设计图

- 1. 使用 3 个 ACMP 以检测不同的电源输入信号。

- 2. 配置一个 CNT/DLY 模块为 delay 模式以建立去抖滤波。

- 3. 添加逻辑单元以建立不同电源系统的切换优先顺序。

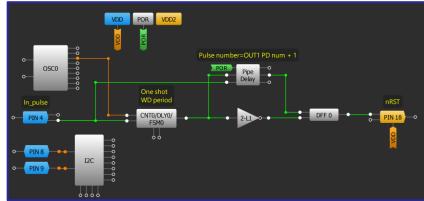

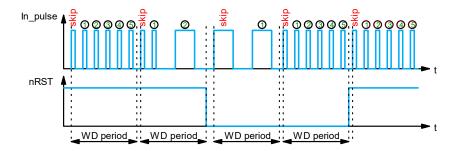

# 应用: N 脉冲看门狗

看门狗定时器用于在微控制器或微处理器无法定期发送脉冲时自动 产生系统复位信号。此应用可监测在看门狗周期内进入 GreenPAK 的 脉冲数。如果脉冲数量小于预定义的脉冲数,将触发系统复位。

# 所需元器件

任意 GreenPAK IC(CMIC)

#### SLG46826 PIN 1 (VDD1) **PIN 20** C1 <u>I</u> PIN 2 **PIN 19** PIN 3 **PIN 18** nRST PIN 4 **PIN 17** In\_pulse [ PIN 5 **PIN 16** PIN 6 **PIN 15** PIN 7 (VDD2) PIN 14 PIN 8 **PIN 13** SCL ( PIN 9 **PIN 12** SDA C **PIN 10** (GND) PIN 11 GND

### GreenPAK 设计图

- 1. 将 CNTO/DLYO/FSMO 配置为在所需的看门狗周期内的一个单脉冲发生器。

- 2. 在 Pipe Delay 中定义脉冲数量(注意: *Pulse number = OUT1 PD num + 1*)。

- 3. 将单脉冲发生器(CNT0/DLY0/FSM0)的输出反相并连接到 DFF0 的 CLK 输入端。

- 4. 将 Pipe Delay 的 nOUT1 连接到 DFFO 的 D 输入端。

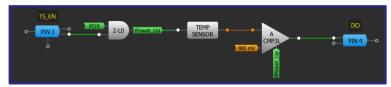

# 技巧: 温度传感器模块的应用

此技巧适用于所有带有温度传感器宏单元的 GreenPAK 芯片。

某些 IC 包含一个模拟**温度传感器 (TS)**,其输出电压与摄氏温度成线性比例。**温度传感器**的额定工作温度范围为 -40°C 至 85°C。整个温度范围内的误差不超过±0.85%。**温度传感器**的输出可以直接连接到**模拟输出**或模拟比较器的正输入端。**温度传感器**可以有两个输出电压范围和一个上电(使能)输入端子(PWR UP)。上电(使能)输入可以选择使用(芯片内部)矩阵输入或使用寄存器激活(使能)。温度传感器也可以通过 I<sup>2</sup>C 激活并更改温度范围。在恒定温度下温度传感器输出电压随 VDD 变化的变化非常小(例如,在 SLG46826 中,输出电压误差在所有温度下均小于 ±0.08%)。

温度传感器宏单元

温度传感器的输出电压可以通过以下公式计算:

$Vts = K \times T + V0$

其中:

Vts-温度传感器输出电压

K - 系数

T-摄氏温度

V0-0℃ 时的输出电压

温度传感器连接到模拟输出

温度比例电压信号可以作为到**模拟输出(16 脚)。Power down source** 配置应设置为 "From register"。

温度传感器输出的信号可以与模拟比较器模块中的参考电压进行比较(见下图),在离散输出处产生双态信号。为了降低功耗,启用了 TS\_EN。TS\_EN 使能温度传感器,打开 ACMP3L。Power down source 应设置为"From matrix"。

温度比较器

带有温度传感器宏单元的 GreenPAK 芯片可以实现:

- 测量 PCB 元件的温度

- 测量 FET 或晶体管外壳温度

- 为 SoC 或在闭环应用中创建报警信号

- 最小化 adc, dac, OpAmps 和其他温度相关器件的误差

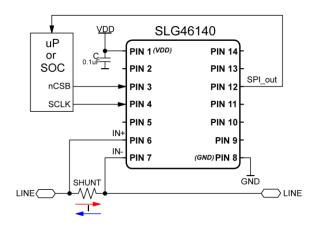

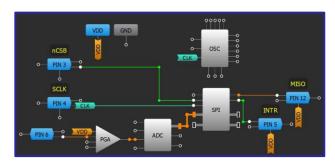

# 应用: 通过外部采样电阻进行电流检测

GreenPAK 可应用于通过检测电阻的电压来检测通过设备的电流。此应用输出一个串行代码来表示它的采样值。

# 所需元器件

- 任意带 PGA, ADC 和 SPI 的 GreenPAK IC

- 1个电阻

### GreenPAK 设计图

- 1. 通过移除 PWR DOWN 输入端子上的 VDD 来启动 ADC。

- 2. 将 PGA 配置为"Differential"差分模式。 它将自动连接 ADC 相应输入端子到 PIN6 和 PIN7。

- 3. 将 SPI 设置为"P2S"模式,将 PAR input data source 设置为"ADC"。

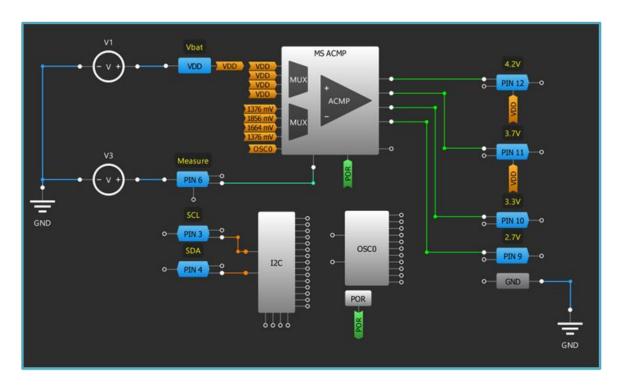

# 应用: 使用一个复用 ACMP 监控一个模拟量的四个电平

用 GreenPAK 监测一个模拟信号的四个电平在各种应用中都被广泛使用。例如,它可以用于电池电源管理、液位控制、温度/亮度/距离/压力/湿度检测等。

#### VDD (Battery) SLG46811 PIN 1 (VDD) PIN 2 **PIN 11** SCL( PIN 3 **PIN 10** 3.3V SDA PIN 4 PIN 9 → 2.7V PIN 5 PIN 8 PIN 6 (GND) PIN 7 Measure[ GND

### 所需元器件

● SLG46811V 或带有相应数量 ACMPs 的任一 GPAK

### GreenPAK 设计图

- 1. 配置 MS ACMP 的 ACMP Mode 为 Multi-channel 模式, Number of Channels 选择 4。

- 2. 选择 Enable mode 为 Rising Edge Activation, 使能 MS ACMP。

- 3. 为 Channel 0 Channel 3 调整适当 IN-source 参数。

- 4. 配置 PIN6 为数字输入(digital input), 连接到 MS ACMP 的 Enable 引脚。每当 PIN6 脚出现上升沿时, MS ACMP 都将 VDD 电压与 4 个阈值相比较, 其结果输出到对应端口 PIN9-PIN12。

- 5. **I**<sup>2</sup>**C** 可以重写 ACMP 的阈值。

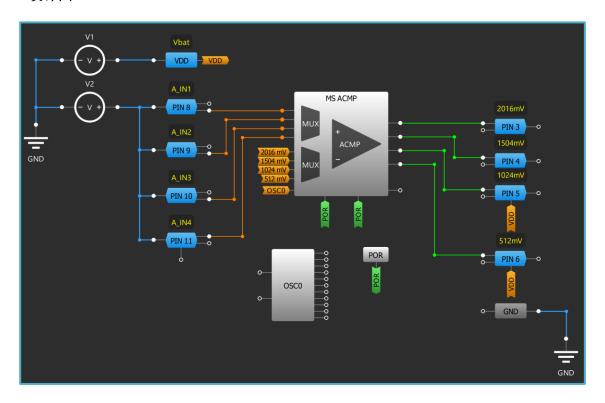

# 应用:用一个MS ACMP 监控四个独立模拟信号

使用SLG46811V 中的MS ACMP 宏单元或其他GreenPAK 芯片中4 个单独的ACMP 来监控四个不同的模拟信号。

#### SLG46811 PIN 1 (VDD) PIN 2 **PIN 1**1 \_\_\_ A\_IN4 PIN 3 **PIN 10** 2016mV⊂ \_\_\_ A\_IN3 PIN 4 PIN 9 1504mV \_\_\_\_ A\_IN2 1024mV( PIN 5 \_\_\_ A\_IN1 512mV( PIN 6 (GND) PIN 7 GND

### 所需元器件

• SLG46811V 或带有相应数量 ACMPs 的任一 GPAK

### GreenPAK 设计图

- 1. 配置 MS ACMP 为 ACMP Mode 为 Multi-channel 模式, Number of Channels 选择 4。

- 2. 选择 Enable mode 为 High-Level Activation, 并连接到 POR (MS ACMP 将连续采样)使能 MS ACMP。

- 为 Channel 0 Channel 3 调整适当 IN- source 参数。将 PIN8 PIN11 的电压与参考电压进行比较,并相应地 将比较结果输出到 PIN3-PIN6。

- 4. I<sup>2</sup>C 可以重写 ACMP 的阈值。

# 第5章:通讯协议

本章介绍了器件之间的通讯应用。涉及到以下应用和技术: I2C、串行、并行通讯协议。

本节中提供的许多技巧和应用都依赖于GreenPAK的PC功能,要了解GreenPAK中PC的详细信息,请查阅芯片的数据手册。

# 技巧: 利用 I2C 更改设计

该技巧可以应用于任何包含 I<sup>2</sup>C 接口的 Green PAK 中。

如果该 GreenPAK 带有 I<sup>2</sup>C 接口,那么在芯片烧录之后,还可以通过 I<sup>2</sup>C 接口实时编辑芯片的功能,但是如果需要在掉电后保存设计更改,需要设备支持 MTP 和 ISP[In-System Programming],该技巧提供了一种快速了解更改设计所需  $I^2C$  命令的方法。

- 1. 利用 GreenPAK Designer 完成你的初始设计,该设计将会在上电时装载并运行。

- 2. GreenPAK Designer 中, 选择 I<sup>2</sup>C Tools 按钮以打开 I<sup>2</sup>C Reconfigurator 窗口(新版软件,需要先点开 debug)。

I<sup>2</sup>C 工具按钮

- 3. 在 I<sup>2</sup>C Reconfigurator 窗口点击 snapshot 快照按钮 (右图红框), 或者按下快捷键 SHIFT+A, 这将产生一个对应当前设计的 I<sup>2</sup>C 命令行表快照。

- 4. 将您的设计更改为下一个配置。

- 5. 利用步骤3的方法为第二个设计产生一个快照。

- 6. 点击 **Snapshot Diffs** 快照差异按钮(右图绿框),这将显示创建此设计需要的 I<sup>2</sup>C 命令。

- 7. 向下滚动 Snapshot diffs 命令行,找到第二个快照,这将仅显示第一个设计快照和第二个设计快照之间的差异。

- 8. 这些差异如右图红框所示,显示了改变 ACMP 的阈值(或者其他可能的 更改)需要通过 I<sup>2</sup>C 接口发送的地址和数据信息,以十六进制显示。

**I2C Reconfigurator**

**Snapshot Diffs**

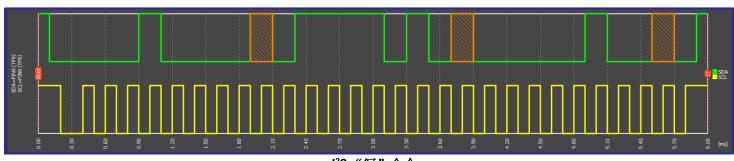

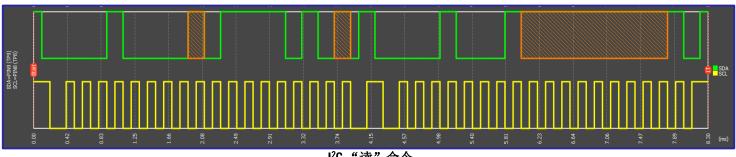

# 技巧: 创建一个 I2C 命令

此技巧可以应用于任何包含IPC 宏单元的GreenPAK 芯片。

利用 I<sup>2</sup>C generator,通过逻辑信号生成器,设计者可以生成 I<sup>2</sup>C 信号。 它由 SDA 和 SCL 两组逻辑信号构成。 设计者可以通过将预先定义的 I<sup>2</sup>C 信号进行组合而产生需要的信号波形,并选择 SCL 的频率:

对于 GreenPAK Advanced Development 平台,可选频率为 1k, 2.5k 和 5k Hz

对于 GreenPAK Pro Development 平台,可选频率为 1k, 2.5k, 5k, 10k, 20k, 50k, 100k, 200k, 400k, 1000 kHz.

使用 I<sup>2</sup>C generator 通过以下步骤生成一个 I<sup>2</sup>C 信号:

- 1. 选择 Debug 按钮。

- 2. 选择" I<sup>2</sup>C generator"仿真信号并添加到 I<sup>2</sup>C 模块的 SDA 引脚的外部 输入端。

- 3. 单击 EDIT 转到信号配置向导。

- 4. 选择 PIN8 作为 SCL 输入 并设置时钟频率。

- 5. 选择 Read 或 Write 复合命令。

- 6. 展开复合命令并设定 Slave address(设备地址)和 Word address(字地址)。对于"读"命令,设置字节 数。对于"写"命令,设置需要写入的数据。

I2C "写"命令

I<sup>2</sup>C"读"命令

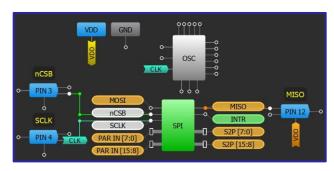

# 技巧: 串行-并行接口 (SPI) 模块

此技巧介绍了**串行转并行接口 (SPI)** 模块, 适用于 SLG46140, SLG46620 和SLG46621。

SPI 模块是一种特殊的宏单元,可用于 GreenPAK 和 SOC (系统级芯片)之间的通讯。 它可以将串行数据转换为并行数据,也可以将并行数据转换为 串行数据。 其输入是标准的 SPI I/O 接口 (MOSI, MISO, nCSB, SCLK, and INTR)。 nCSB 是低电平有效片选信号。 SCLK 是 SPI 宏单元的串行时钟信号。

SPI 可以传输数据到如下模块:

- FSM

- DCMP

- DAC (through DCMP)

同样地, SPI 可以传输来自以下模块的数据:

- ADC

- FSM

SPI 可以和其他宏单元组合实现如下功能:

- 脉宽调制

- 模数比较

- 数模比较

- 结合 DCMP, 比较两种结果

- SDIO和LCD

SPI 可工作于 8 位或 16 位模式。需要注意的是 SPI 宏单不能在同一个程序文件中发送和接收 串行数据。必须设置为 "S2P"或 "P2S"模式。

SPI 宏单元

SPI 宏单元将串行数据转换为并行数据

SPI 宏单元将并行数据转换为串行数据

在 P2S 模式下,每次数据传输完成后,INTR

脚将输出一个周期高电平。此外,GreenPAK芯片中的SPI模块符合通用标准。其时钟频率最高可达2MHz。CPOL决定时钟脉冲的有效脉冲方式(正脉冲、负脉冲),CPHA定义数据传输和串行时钟间的相位关系。当CPHA=0,数据仅允许从串行到并行传输,不允许从并行到串行传输。当CPHA=1,数据既可以从串行到并行传输,也可以从并行到串行传输。

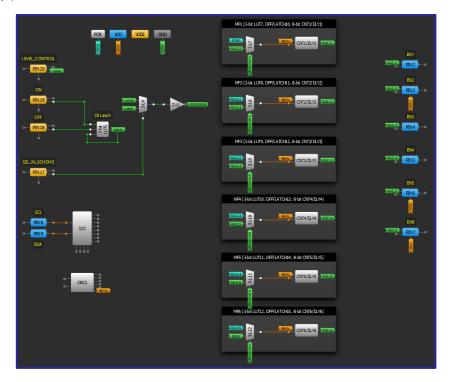

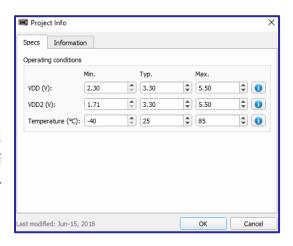

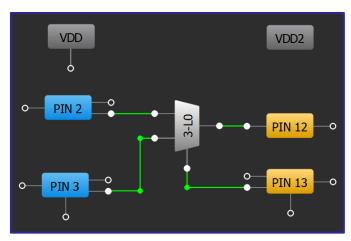

# 技巧: 电平转换

该技巧适用于任何具有双电压轨的GreenPAK,例如SLG46826V。

通常在系统级设计中,需要组合来自两个不同电平的信号,例如模拟电压轨工作在5V,而数字电压轨工作在3.3V。

许多 GreenPAK 通过使用双电压轨来解决这个问题,来自不同电平的信号都可以输入到 GreenPAK,进行处理,然后从任意电压轨输出。

当使用双电压轨的器件来开始进行一个设计的时候,需要如右图所示的那样,分别输入 2 个电压轨的电压范围,两个电压轨的工作范围随不同器件而有所不同,但是 VDD 轨总是电压较高的轨,而不是 VDD2 轨。

双电压轨项目信息

双电压轨逻辑示例

如左边的图所示,在 GreenPAK Designer 中处在不同电压轨的 GPIO 使用不同的颜色来表示,处在 VDD轨的 GPIO 用蓝色显示,处在 VDD2 轨的 GPIO 用琥珀色来显示,不同电平的信号在进入 GreenPAK 矩阵后都将表现一致。

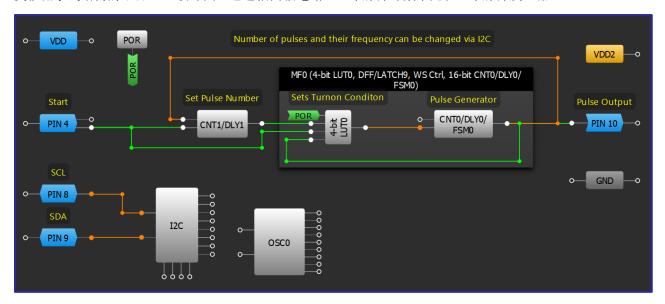

# 技巧: 发送预设数量脉冲

此技巧适用于所有GreenPAK,但是含有Multi-Function 组件的GreenPAK 可以降低设计复杂度。

在许多通信协议中都需要由一个 IC 发送或者接收一定位数的比特数据,这通常意味着 GreenPAK 需要实时跟踪发送或者接收到的脉冲个数,例如利用一个移位寄存器来接收数据的时候,需要监测接收到的位数,而不会错误地偏移和失控地不停移位,以确保寄存器中存放的是正确的数据。

在 GreenPAK 中设置预定数量的脉冲有很多办法。此技巧描述了一种有效的并且方便扩展位数的方法。此方法还通过每次传输完成后都重置时钟偏差来限制 GreenPAK 和其他芯片之间累积的时钟偏差。下图显示了此方法类似流水线结构的 GreenPAK 设计图。它包括两级电路:一个脉冲计数单元和一个脉冲发生器。

预设脉冲发生器设计图

脉冲计数单元由一个单次脉冲模块组成,该模块由脉冲发生器的输出脉冲提供时钟源。在 PIN 4(Start)的上升沿,CNT1/DLY1 输出将设置为高电平,直到输入时钟达到 Counter data 设置的脉冲数量。在达到设定的脉冲数后,它将返回 LOW。

脉冲发生器采用 MF0。在 MF0 中,CNT0/DLY0 是一个带有反相输出的双沿延迟。它的延迟时间即是设置脉冲发生器的周期。其输出反馈到 4 位 LUT0,该 LUT0 配置为仅在 CNT/DLY1 的输出为高电平时反转来自 CNT0/DLY0 的信号。(CNT0/DLY0) 单次脉冲完成后,脉冲发生器将停止发送脉冲。

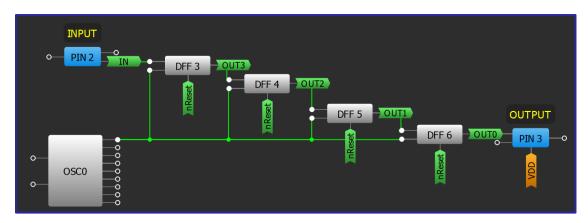

# 技巧:移位寄存器

此技巧适用于任意 GreenPAK IC (CMIC), 能够配置成多少位数的移位寄存器取决于 GreenPAK 中可用的组件。

移位寄存器是串行器和解串器关键的组成部分,移位寄存器就是一串触发器的集合,并且每个触发器的输出都可以单独访问,所有触发器都共享一个时钟,在这个时钟的上升沿,寄存器按顺序将数据移位到下一个触发器,下图显示了一个基本的4位大小的移位寄存器,并且可以通过一个共享的复位信号进行全局复位。

基本移位寄存器

通常,移位寄存器需要能够装载初始值,所以需要在每个 DFF 之前加一个 MUX,当预载数据已经准备好时,切换 MUX 的输入通道(GreenPAK Designer 中的 S),然后触发 DFF 的时钟,完成装载,下图显示了如何从 上述设计中的基本移位移位寄存器添加 MUX 形成可以装载的移位寄存器,Load\_EN 被用来切换 MUX 的输入外,还用来触发 DFF3 和 DFF4 以完成装载。

可以装载的移位寄存器

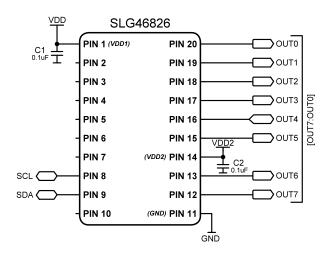

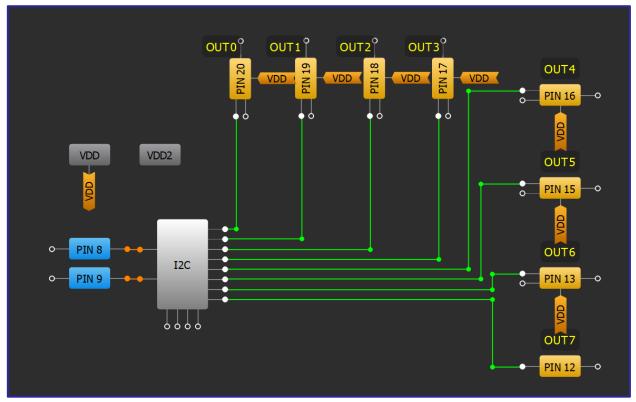

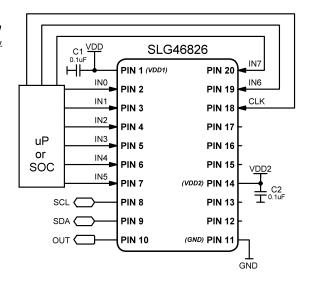

# 应用:通过 I<sup>2</sup>C 接口进行 IO 扩展

10 扩展器用于使用较少的线控制更多的10,因为1<sup>2</sup>C 可以通过 使用不同的地址将扩展器连接在同一条总线上以扩展更多的 10,所以是10 扩展器中一种常见的输入接口。

### 所需元器件

- 任意带 I<sup>2</sup>C 接口的 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 将 GPIO 配置为 Digital output。

- 2. 将配置好的 GPIO 连接到 I<sup>2</sup>C virtual inputs。

- 3. 通过访问 **I<sup>2</sup>C Virtual inputs** 对应的寄存器[寄存器地址参见特定 GreenPAK 数据手册的 Connection Matrix Virtual Inputs 部分],每个 I<sup>2</sup>C Virtual Input 都可以单独更改或者同时更改。

# 应用: 串口转并口(外部时钟)

解串器[串口转并口]是将单线发送的串行多位数据由接收器解码为并行数据,通常还需要添加一条时钟线以避免不正确的数据移位。

# 所需元器件

- 任意 GreenPAK IC (CMIC)

- 1颗可以输出时钟信号的芯片

### GreenPAK 设计图

- 1. 使用 技巧:移位寄存器 将移位寄存器配置成 GreenPAK 设计图那样。

- 2. 为时钟信号配置一个 Digtal input 引脚,并将其连接到移位寄存器 CK[组成寄存器 DFF 的 CK]。

- 3. 为复位信号配置一个 Digital input 引脚,并将其连接到移位寄存器 nRESET[组成寄存器 DFF 的 nRESET]。

# 应用: 串口转并口(内部时钟)

解串器。串口转并口是将单线发送的串行多位数据由接收器解码为并行数据。当现实无法添加额外一条时钟线的时候,解串器可以作用为单线传输的功能。例如利用外部一个长达特定时间的低电平信号来触发GreenPAK内部的振荡器。

### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

# GreenPAK 设计图

- 1. 使用 技巧:移位寄存器 配置好移位寄存器。

- 2. 为复位信号配置一个 Digital input 引脚,并将其连接到移位寄存器 nRESET [组成寄存器的 DFF nRESET]。

- 3. 使用 技巧:发送预设数量脉冲 配置好一个发送数量与移位寄存器位数相匹配的脉冲发生器。

# 应用: 并口转串口

串行器[并口转串口]一般用于芯片间通过一根或者两根线[Data和 Clock]进行数据传输,可以使用内部也可以使用外部时钟信号,并口的位数取决于GPAK 可用的I/O 和相关的内部资源。

### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 无需其他元器件

### GreenPAK 设计图

- 1. 使用 技巧:移位寄存器 配置好移位寄存器。

- 2. 使用 技巧:配置标准逻辑 为每个移位寄存器的 DFF添加一个 3-bit LUT 并配置为 MUX。

- 3. 配置装载/移位切换功能,并将并行输入引脚和串行输出引脚连接到内部模块。

# 应用:双向通信(发送优先)

在主板空间不足或设备间(如可穿戴设备或充电器)相连的端口数目有限的设计中,双向通信系统显得尤为重要。发送优先设计中发送设备将始终在通讯事件中按第一优先级启用。

# 所需元器件

- 任意包含 OE 脚的 GreenPAK IC(CMIC)

- 无需其他元器件

#### SLG46826 SLG46826 PIN 20 PIN 1 (VDD1) PIN 20 C3 + PIN 19 PIN 2 **PIN 19** PIN Data\_IO PIN 18 PIN PIN 3 **PIN 18** PIN 17 PIN -PIN 4 PIN 1 PIN 16 PIN PIN 5 CLK\_IO PIN 15 PIN PIN 6 PIN 14 (VDD2) PIN 7 ⊃ EN PIN 7 PIN 13 PIN 8 SCL SCL PIN 8 **PIN 13** PIN 12 PIN SDA SDA PIN 9 PIN 12 PIN 11 (GND PIN 10 **PIN 10** (GND) PIN 11

### GreenPAK 设计图

- 将2个GPIO配置为Digital Input/Output, 1个为数据信号,1个为时钟信号。

- 2. 将一个 CNT/DLY 模块配置为 Reset counter 以建立一个内部时钟信号。

- 3. 使用 技巧:移位寄存器 配置一个移位寄存器以存储传入数据。 I<sup>2</sup>C 可以读取移位寄存器的数据。

- 4. 添加 PGEN 以发送传出数据。I<sup>2</sup>C 可以改变 PGEN 的内容。

- 5. 配置 DFF 以使能数据传送。 将输出连接至传送时钟信号,并连接 输入/输出 的 OE 脚。

- 6. 添加 CNT/DLY 模块并配置为 Reset counter 以终止传输,并选择内部时钟信号为 DFF 的输出。 其输出经过 Edge Det 模块后, 到达设定的时钟脉冲后将 DFF 复位。

- 7. 添加 CNT/DLY 模块并配置为 Reset counter, 并选择外部时钟信号作为输入, 其输出用于使能传输 DFF。

- 8. 将外部时钟信号连接至移位寄存器,并将内部时钟信号连接至 **PGEN** 和 输入/输出脚。

SLG46826

PIN 2

PIN 1 (VDD1

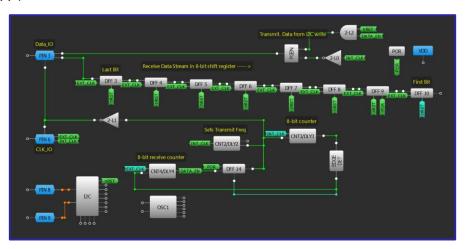

# 应用:双向通信(接收优先)

在主板空间不足或设备间(如可穿戴设备或充电器)相连的端口数目有限的设计中,双向通信系统显得尤为重要。接收优先设计中接收设备将始终在通讯事件中按第二优先级启用。

# 所需元器件

- 任意包含 OE 脚的 GreenPAK IC(CMIC)

- 无需其他元器件

#### PIN 19 PIN 2 PIN : PIN 1 Data IO **PIN 18** PIN 3 PIN 3 Transmit first **PIN 17** PIN 4 PIN 4 PIN 17 **PIN 16** PIN 5 PIN 5 CLK IO PIN 15 PIN 6 (VDD2) PIN 14 PIN 14 (VDD2) PIN 7 PIN 7 C2 + **PIN 13** PIN 8 SCL SCL PIN 8 **PIN 13** PIN 12 PIN 9 SDA SDA PIN 9 **PIN 12** PIN 11 (GND) **PIN 10 PIN 10** (GND) PIN 11

SLG46826

(VDD1) PIN

PIN 20

### GreenPAK 设计图

- 1. 将 2 个 GPIO 配置为 Digital Input/Output, 1 个为数据信号, 1 个为时钟信号。

- 2. 将一个 CNT/DLY 模块配置为 Reset counter 以建立一个内部时钟信号。

- 使用 技巧:移位寄存器 配置一个移位寄存器以存储传入数据。 № 可以读取移位寄存器的数据。

- 4. 添加 PGEN 以发送传出数据。I<sup>2</sup>C 可以改变 PGEN 的内容。

- 5. 配置 DFF 以使能数据传送。 将输出连接至传送时钟信号,并连接 输入/输出的 OE 脚。

- 6. 添加 CNT/DLY 模块并配置为 Reset counter 以终止传输, 并选择内部时钟信号为 DFF 的输出,其输 出经过 Edge Det 模块后,到达设定的时钟脉冲后将 DFF 复位。

- 7. 添加 CNT/DLY 模块并配置为 Reset counter, 并选择外部时钟信号作为输入, 其输出用于使能传输 DFF。

- 8. 将外部时钟信号连接至移位寄存器,并将内部时钟信号连接至 PGEN 和 输入/输出脚。

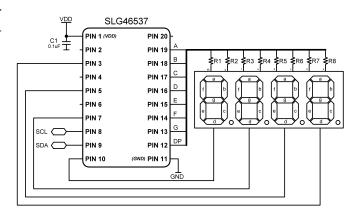

# 应用: 采用 ASM 和 I<sup>2</sup>C 的 7 段数码显示

七段数码指示器是一种常见的数值显示装置。 GreenPAK 的异步状态机和I<sup>2</sup>C 可用于控制数码管进行数值显示。本实例展示了4 位包含小数位的十进制数字显示。

#### 所需元器件

- 任意包含 I<sup>2</sup>C 和 ASM 的 GreenPAK IC(CMIC)

- 7段数码显示管

- 8个电阻

#### GreenPAK 设计图

- 1. 将 GPIO 配置为 Digital Output 并连接到 ASM 的输出。

- 2. 使用 技巧:移位寄存器添加一个移位寄存器。

- 3. 使用 PGEN 模块创建一个逻辑生成器,对应所需的位数。

- 4. 添加并配置异步状态机 (ASM) 以与初始数字序列相匹配。

- 5. 通过 I<sup>2</sup>C 将一个或多个数字更新到 ASM 状态中。

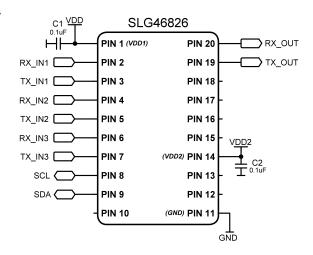

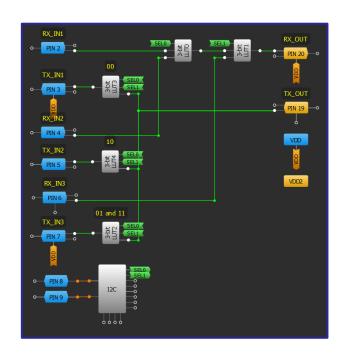

## 应用: 采用 I<sup>2</sup>C 的通讯多路复用器

当设计人员需要整合几个不同设备的输入信号并将它们转发到一条输出线时,或者将单路输入信号通过指定的单个或者多个输出时,需要用到PC 控制的通信多路复用器。

### 所需元器件

- 任意包含 I<sup>2</sup>C 的 GreenPAK IC(CMIC)

- 2个电阻

- 2个电容

#### GreenPAK 设计图

- 1. 用 LUT 配置 1:3 多路解复用器以共享来自 MCU 的 TX 信号,并发送至外部 UART 端口。

- 2. 用 LUT 配置 3: 1 多路复用器以接收从外部 UART 端口到 MCU 的 RX 信号。

- 3. 使用 I<sup>2</sup>C 进行输入端口的切换。

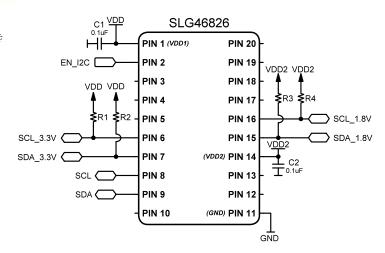

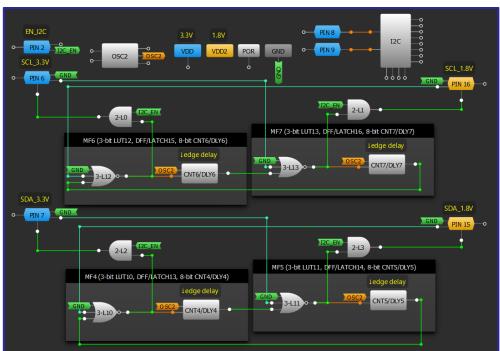

## 应用: I2C 电平转换器

PC 电平转换器允许两个含有PC 的设备在两个不同电压下进行通讯。本实例展示了电压由 3.3V 转换为1.8V。

#### 所需元器件

- 任意 GreenPAK IC(CMIC)

- 4个电阻

#### GreenPAK 设计图

- 1. 将 GPIO 配置为 Digital Input/Output 并将 Output mode 设置为 open drain NMOS。

- 2. 将一个引脚配置为 Digital Input 作为使能信号。

- 3. 为每个输入/输出添加一个 AND gate (逻辑与门)。

- 4. 将 4 个 Multi-function 组件(当缺少 Multi-function 组件时,可用 4 个 LUT 和 4 个 CNT/DLY 组件)配置为 Nor gate ,接上一个下降沿延时。

- 5. 选择 OSC2 作为 DLY 组件的时钟源并设置为 "Force Power On"。

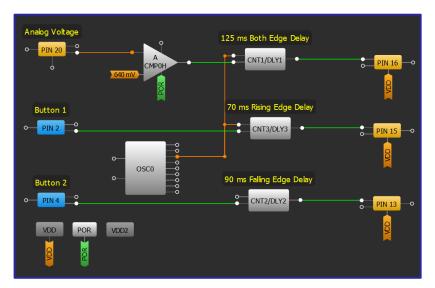

## 应用:连接检测

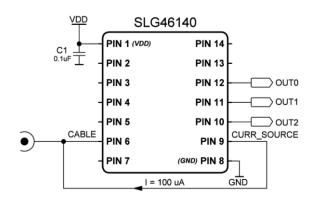

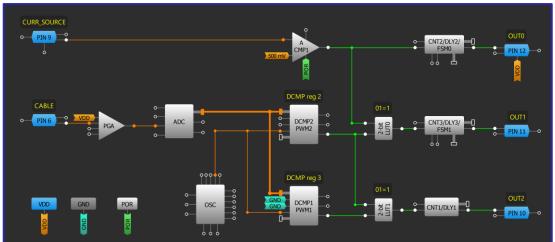

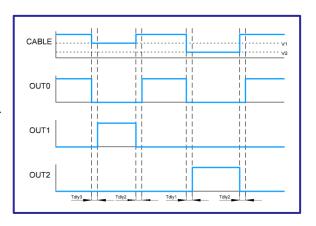

该应用程序通过测量与电阻成比例的电压来检测电缆的存在。 ACMP 的 100uA 电流源用于在电缆上产生电压降。这种配置还能 够根据不同的电线长度或连接负载来确定哪种类型的连接。

#### 所需元器件

• 带 ADC 功能 GreenPAK IC(CMIC)

#### GreenPAK 设计图

- 1. 启用 ACMP1 中的 input 100uA current source, 并配置 IN- source。

- 2. 配置 ADC 和 PGA 块。

- 3. 使 DCMP/PWM 模块(从 **SHARED PD** 输入端子上移 除 VDD)。将 DCMP/PWM Power 寄存器设置为 Power on。确保 **IN+ selector** 连接到 ADC, **IN- selector** 器连接到内部寄存器。

- 4. 在 DCMP/PWM 模块中设置寄存器所需的值,并配置 MTRX SEL 输入。

- 5. 配置 2-bit LUT0 和 2-bit LUT1。

- 6. 设置 CNT1-CNT3 为上升沿延时模式。

- 7. 配置 PIN10-PIN12 为数字输出 1x push pull。

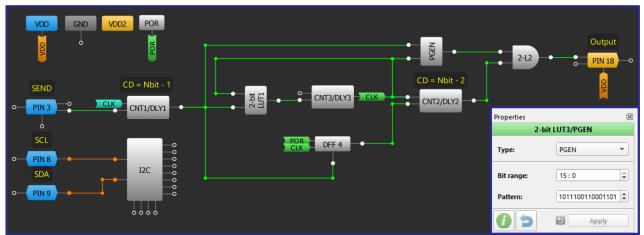

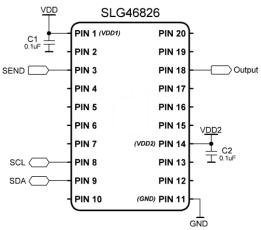

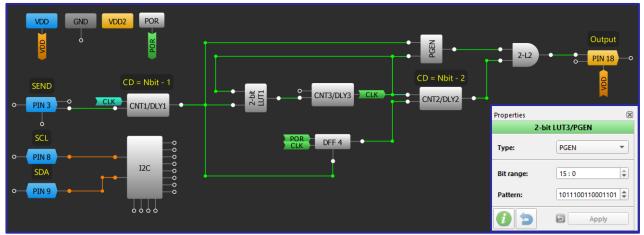

## 应用: 自定义模式发生器

GreePAK 中的模式发生器/PGEN)存储一组逻辑 1 和 0(最多 16 位)的数据组,该数据组可以串行地发送到内部矩阵。这个设计在输入上的上升沿之后输出一个 16 位的代码。它可以用于顺序逻辑。

#### 所需元器件

- 任意带 PGEN 的 GreenPAK IC(CMIC)

- 无需其他元器件

#### <u>VDD</u> SLG46826 PIN 1 (VDD1) **PIN 20** PIN 2 **PIN 19** SEND [ PIN 3 **PIN 18** Output PIN 4 **PIN 17** PIN 5 **PIN 16** PIN 6 **PIN 15** PIN 7 (VDD2) PIN 14 SCL ( PIN 8 **PIN 13** SDA ( PIN 9 **PIN 12 PIN 10** (GND) PIN 11 GND

#### GreenPAK 设计图

- 1. 在 PGEN 中配置自定义 N bits 模式。

- 2. 将 CNT1/DLY1 模式配置为 One Shot 模式。设置 Counter Data 为"Counter Data = N<sub>bits</sub> 1.

- 3. **"CNT2/DLY2**"模式配置为"One Shot"模式,"Counter Data" 设置为"Counter Data = N<sub>bits</sub> 2.

- 4. 将 CNT3/DLY3 配置为上升沿延迟,使用 2 位 LUT1 创建发生器。

- 通过使用带有 I<sup>2</sup>C 的 GreenPAK 来动态修改 PGEN 数据、时钟频率和计数器数据,这样可以改进设计。

## 技巧: 使用占空比检测发送串行协议

此技巧适用于任何带有模式发生器、计数器/延时器和PC 的 GreenPAK 芯片。请阅读 技巧: 使用移位寄存器读取串行协议 和 技巧: 使用管道延时(Pipe Delay) 读取串行协议 以了解此处所讨论的如何利用 GreenPAK 芯片读取协议。

串行数据传输具有非常广泛的通讯应用包括电力线、无线系统和单片机系统。单线数据传输可以使用不同的占空比来传输数据,以供另一个 GreenPAK 或 MCU 读取。

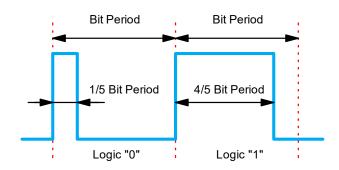

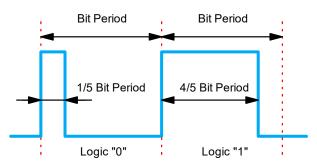

占空比检测技术如下图所示。每一个数据位由一个特定占空比的周期脉冲来表示。在此设计中,当脉冲持续时间≤整个周期的 1/5 时,传输位被设置为"0",当脉冲持续时间≥整个周期的 4/5 时,被设置为"1"。可以使用其他占空比范围,前提是逻辑"0"和逻辑"1"的占空比范围之间有足够的区分。

占空比检测技术 -- 逻辑 0 和逻辑 1

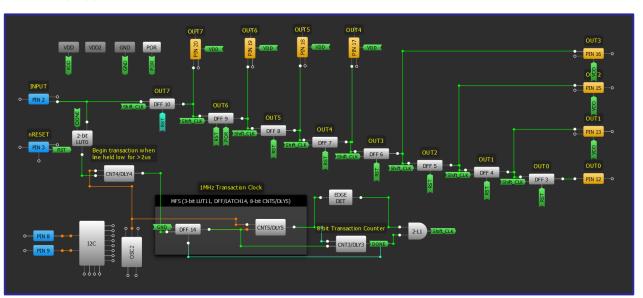

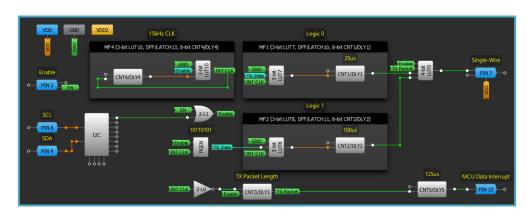

在如下所示的设计中,数据传输由 Enable 脚发起,这个操作可以通过一个外部的 GPIO 或者一个 I<sup>2</sup>C 虚拟输入 实现。CNT4/DLY4 设置数据传输的位周期。MF1 和 MF2 模块定义传输的占空比。传输的数据通过 I<sup>2</sup>C 或非易失性存储器写入 PGEN。PGEN 最多可传输 16 位数据,而该设计展示了单线输出上的 8 位数据传输。有关更多如何利用 I<sup>2</sup>C 通过 PGEN 生成不同的模式,请参阅应用:自定义模式发生器。

数据包长度由 CNT3/DLY3 确定,在本实例中它被设置为传输 8 位数据。数据嵌入到传输信号的占空比后,4 位 LUT0 通过 Single-Wire 输出脚传输数据。当数据传输完成后,可以通过 I<sup>2</sup>C 对 PGEN 重写。

如果用户希望中断传输, CNT5/DLY5 会产生一个中断信号, 向外部 MCU 表明传输包已经完成。

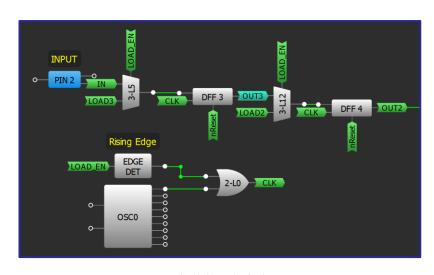

## 技巧: 使用移位寄存器读取串行协议

此技巧适用于所有带有足够的 D 类触发器、1 个 Ripple Counter 和 3 个计数器/延时器的 GreenPAK 芯片。请阅读技巧:使用占空比检测发送串行协议以了解一种读取单线协议的方法。

串行数据传输具有非常广泛的通讯应用包括电力线、无线系统和单片机系统。移位寄存器可以用作单线传输中高度通用的串行接收器。

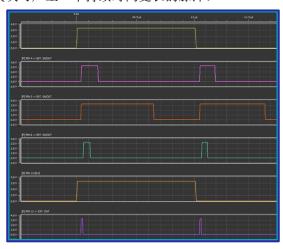

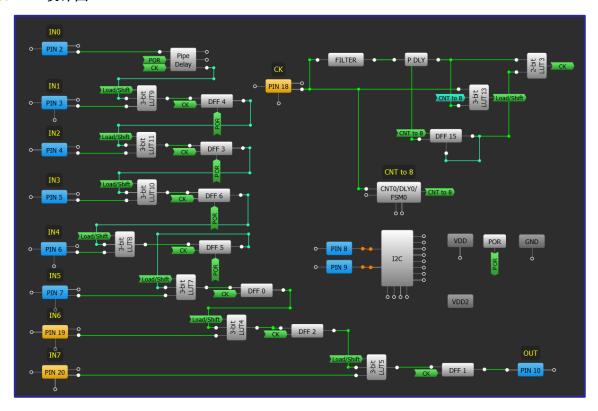

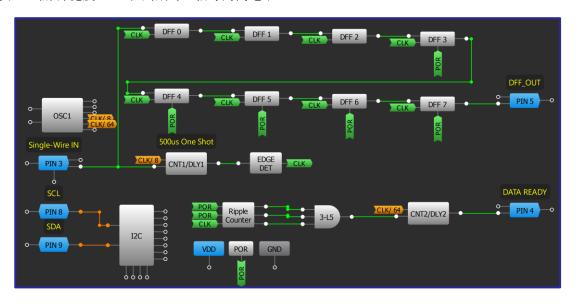

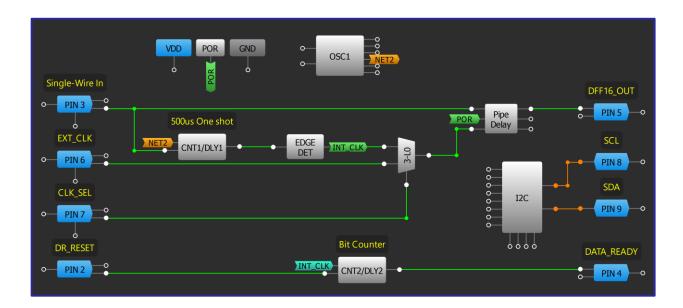

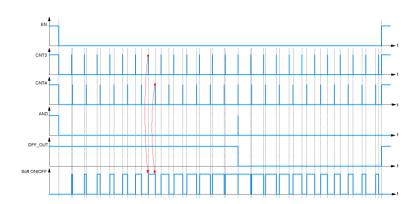

上图显示了在单线拓扑中所讨论的技巧:使用占空比检测发送串行协议。上升沿上的延迟边沿检测用于在信号周期(位长度)的一半进行采样。对这种特殊设计的移位寄存器记录数据时,当脉冲宽度≤1/5位周期时信号为低电平,当脉冲宽度≥4/5位周期时,信号为高电平。

上图显示了一种以 8 位增量获取单线数据的方法。每次对移位寄存器输入移位时钟,Ripple Counter 也会递增。 当 Ripple Counter 收到 8 个脉冲,CNT2/DLY2 在 DATA READY 脚输出一个高脉冲信号以通知 MCU 已读取完整的单线传输数据并准备好由 I<sup>2</sup>C 读取。本设计中,由于 CNT1/DLY1 将上升沿延迟 500μs,因此该设计以 1ms 周期读取传输数据,但这可以通过调整其计数器值轻松改变。

## 技巧: 利用管道延时(Pipe Delay)读取串行协议

此技巧适用于所有GreenPAK 芯片。在技巧: 使用占空比检测发送串行协议中介绍了一种读取单线协议的方法。

串行数据传输具有非常广泛的通讯应用,包括电力系统、无线系统和单片机系统。可以使用单个 Pipe Delay 模块代替资源繁重的移位寄存器,作为单线传输的串行接收器。但需要注意,与移位寄存器方式不同的是,这种 Pipe Delay 方式只能串行输出其数据,而不具备并行输出的能力。

可以把 Pipe Delay 想象成一个有 3 个可用输出的 16 位移位寄存器。其中 2 个输出可配置为 Pipe Delay 里 16 个内部 DEF 输出中的任何一个。对于这个 16 位的输出,如下图所示,Pipe Delay 的 **OUTO** 设置为代表第 16 个 DFF 输出。 MCU 用于为 Pipe Delay 提供外部时钟的输入与 **Single-Wire In** 输入复用,以允许它在不增加位计数器的情况下卸载 Pipe Delay 的数据。

本设计采用了与技巧:使用移位寄存器读取串行协议 相同的延时数据采样机制,但它使用计数器模块而不是异位计数器来跟踪其数据位。每检测到一个数据位时,该计数器都会递增。当达到 16 位时,它将 DATA\_READY 引脚设置为高电平,直到发送下一个数据位。很重要的一点是,在发送任何数据之前,必须重置这个计数器模块,以确保正确的操作,这可以由 POR 在内部完成,也可以由一个输入在外部完成(如本设计中所示)。

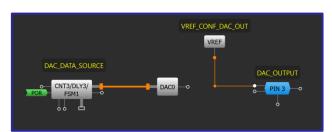

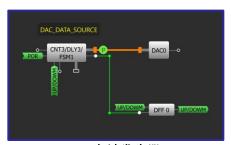

## 技巧: 数模转换器

此技巧适用于SLG46140,SLG46620 和SLG46621 GreenPAK 芯片。

有些 GreenPAK 芯片包含**数模转换器(DAC)**。它们是 8 位、最大采样速度为 100ksps 的数模转换器。其微分非线性 小于 1LSB,积分非线性小于 1LSB。DAC 输出至 pin 的电阻是 1 k $\Omega$ 。建议负载电阻不小于 10k $\Omega$ ,负载电容不大于 100pf。通常,DAC 输出范围为 0V ~ 1V,但在 SLG46620/1 中,DAC1 输出范围为 50mV ~ 1.05V。

寄存器、SPI或 FSM 均可配置为 DAC 的输入。 DAC 的输出可以配置为 VREF 的输出引脚、PGA或 ACMP。

在某些 IC 中,**DAC0** 用作 PGA 宏单元伪差分模式的一部分。因此,当 PGA 处于伪差分模式时,**DAC0** 不可用。此外,**DAC1** 与 ADC 宏单元复用。因此,使用 ADC 时不能使用 **DAC1**。要将 DAC 宏单元输出连接到 VREF 宏单元,必须将此引脚配置为 analog input/output,并将 VREF 的 **Source selector** 配置为 DAC。

锯齿波发生器

DAC 可用于创建如上所示的简单锯齿波发生器。在这种情况下,DACO 使用 FSM1 作为其 data source。DAC output 连接到 VREF,VREF 连接到 PIN3 (DAC\_OUTPUT)。输出信号周期和分辨率由 FSM1 的 counter data 和时钟频率设置。此外,您可以添加一个 toggling DFF 并将其连接到 FSM 的 UP 输入以产生如下所示的三角波发生器。counter data 值随时间上下变化,取决于 DFFO 的输出。

三角波发生器

DAC 可用作"差分"和"伪差分"模式下 ACMP 或 PGA 负输入端的基准。如果 ACMP 的基准使用 DAC,则用户可以将模拟信号与离散数据进行比较,而无需使用 ADC 模块。

#### GreenPAK DAC:

- 可用于创建波形发生器;

- 创建通过 SPI 控制的基准电压源;

- 可用于不同的转换器,因为它将温度、湿度和其他数字化值转换为模拟电压。

## 应用: 自定义模式发生器

GreePAK 中的模式发生器(PGEN)存储一组逻辑 1 和 0(最多 16 位)的数据组,该数据组可以串行地发送到内部矩阵。这个设计在输入上的上升沿之后输出一个 16 位的代码。它可以用于顺序逻辑。

#### 所需元器件

- 任意带 PGEN 的 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 在 PGEN 中配置自定义 N bits 模式。

- 2. 将 CNT1/DLY1 模式配置为 One Shot 模式。设置 Counter Data 为"Counter Data  $= N_{bits} 1$ .

- 3. "CNT2/DLY2"模式配置为"One Shot"模式,"Counter Data"设置为"Counter Data = N<sub>bits</sub> 2.

- 4. 将 CNT3/DLY3 配置为上升沿延迟,使用 2 位 LUT1 创建发生器。

- 5. 通过使用带有 I<sup>2</sup>C 的 GreenPAK 来动态修改 PGEN 数据、时钟频率和计数器数据,这样可以改进设计。

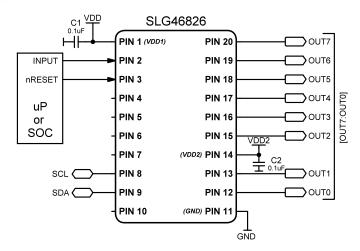

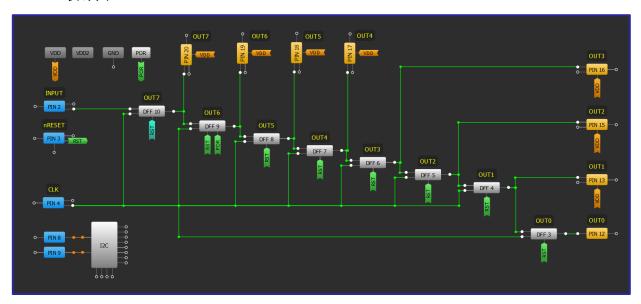

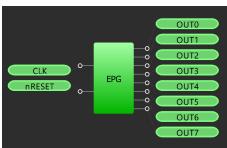

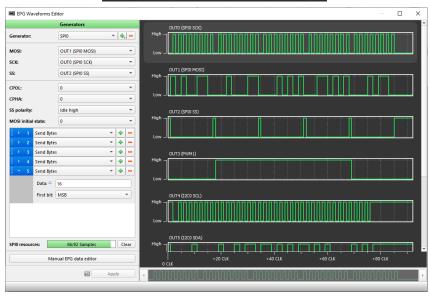

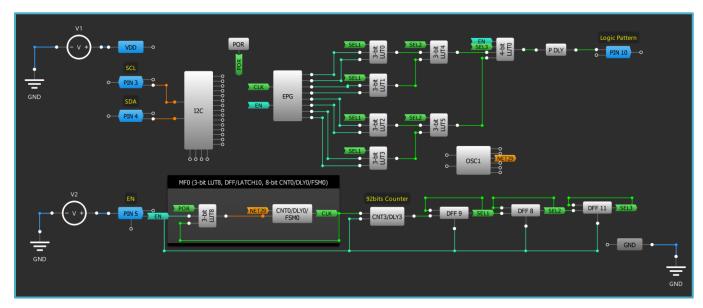

## 技巧: EPG

扩展模式/序列发生器 (EPG) 能够产生一系列 92 字节(92 Bytes)长度的输出。 它从非易失性存储器 (NVM) 检索数据,并在每个时钟输入信号的上升沿输出一个字节。此外,EPG 与 I<sup>2</sup>C Virtual Inputs 共享其输出端子(OUT0~7)。最大时钟频率可达 1 MHz。

系统上电后,EPG 根据 nReset 引脚收到的信号,呈现不同的行为。当 nReset 输入为有效低电平时,EPG 将输出初始值。相反地,当 nReset 输入为有效高电平时,EPG 将输出用户自定义的模式。此功能使用户能够根据自己的特定需求定制 EPG 的输出。

当 CLK(CNT overflow/keep) 设置为 Overflow 模式时,EPG 可以连续工作,或者在 Stop at boundary 模式下保持最后一个字节。

EPG 波形编辑器允许用户从各种预定义的发生器(Generator 下拉项目 SPI、I<sup>2</sup>C、PWM 或手动配置)中进行选择,并相应地配置输出。每个发生器的预定义配置都提供一系列可调设置,使用户更容易构建他们期望的模式。

资源栏呈现可视化展示,指示模式/序列中所使用的位数。它使用户可以清楚地了解已分配给当前模式/序列的内存和资源量。

I2C BUS

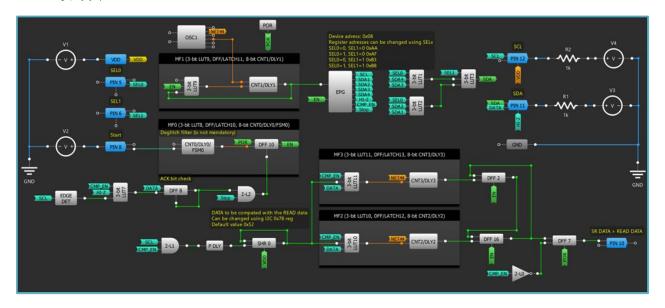

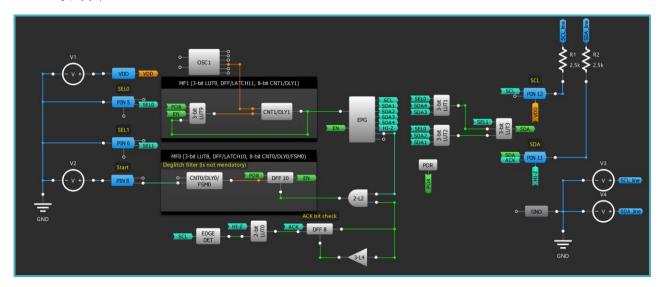

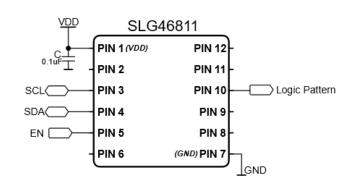

## 应用: 带 ACK 检查和数据比较的 I<sup>2</sup>C 主设备读指令

本实例展示了如何利用 SLG46811 构建一个简单的 I<sup>2</sup>C 主设备,该主设备可以读取从设备数据并将其与预设好的参考数据进行比较。

### 所需元器件

- SLG46811V

- 2个电阻器

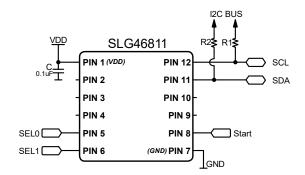

#### SLG46811 R2**≷** R1**≷** PIN 1 (VDD) PIN 12 SCL PIN 2 **PIN 11** SDA PIN 3 **PIN 10** SR DATA > READ DATA PIN 4 PIN 9 SEL0 PIN 5 PIN 8 Start PIN 6 (GND) PIN 7 SEL1 \_GND

#### GreenPAK 设计图

- 1. 配置 EPG 发生器 ( 请参阅 技巧: EPG ) 以创建 **I<sup>2</sup>C** 读命令并设置多种 SDA 和 SCL 模式。

- 在 EPG 中添加一个通道,用于每 9 个 SCL 时钟周期进行一次的 ACK 位校验。

- 3. 创建一个 4 位多路复用器,参考应用: 8 位多路复用器。SEL0 和 SEL1 用于选择要输出的数据(SDA)。

- 4. 基于 CNT1/DLY1 和 LUT9 创建一个由 EN 信号控制的时钟源,为 EPG 提供时钟。

- 5. 通过 CNTO/DLYO 去抖/滤波后的信号触发 EN 进入 I<sup>2</sup>C 模式。

- 6. DFF8 用于监控 I<sup>2</sup>C 指令传输期间是否存在 ACK 位,如果 I<sup>2</sup>C 从设备没有响应,则传输停止。

- 7. 当 **l**<sup>2</sup>**C** 从设备开始发回数据时,它们将与存储在 SHR 0 中的参考数据进行比较。在比较过程中,SHR0 中的数据会随着 SCL 移位并与接收到的数据逐位进行比较。 DFF7 存储比较结果直到接收到读命令为止。

## 应用: 带 ACK 检查的 I<sup>2</sup>C 主设备写指令

本案例展示了通过 SLG46811,构建一个简单的 PC 主设备。利用 该芯片创建的 PC 主设备能够重复写入一个或多个字节,这使其 成为无需复杂设计的系统的绝佳解决方案。

## 所需元器件

- SLG46811V

- 2个电阻器

#### GreenPAK 设计图

- 1. 配置 EPG 发生器(请参阅 技巧: EPG)以创建 I<sup>2</sup>C 写命令并设置多种 SDA 和 SCL 模式。

- 2. 在 EPG 中增加一个通道,用于 SCL 时钟的第 9 个时钟进行一次的 ACK 位校验。

- 3. 创建一个 4 位多路复用器,参考应用: 8 位多路复用器。SEL0 和 SEL1 选择要输出的数据(SDA)。

- 4. 基于 CNT1/DLY1 和 LUT9 创建时钟源,为 EPG 提供时钟。

- 5. 通过 CNTO/DLYO 去抖/滤波的信号可触发使能 I<sup>2</sup>C 模式。

- 6. DFF8 用于监控 I<sup>2</sup>C 指令传输期间是否存在 ACK 位,如果 I<sup>2</sup>C 从设备没有响应,则传输停止。

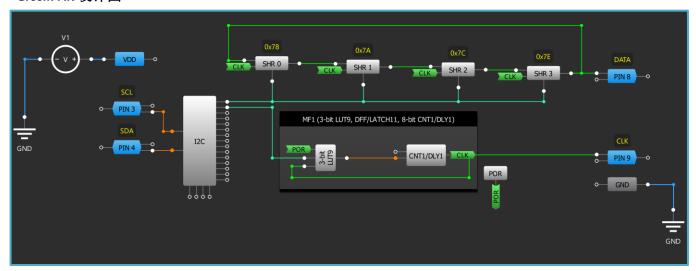

# 应用:移位寄存器构建 I2C 可编程模式发生器

本实例展示了利用 SLG46811 构建一个简单的、容量高达 32 位的移位模式发生器。这是一种经济高效的应用。

#### 所需元器件

• SLG46811V 或者任意带有移位寄存器的 GreenPAK 芯片

#### GreenPAK 设计图

- 1. 配置移位寄存器模块并将它们串行连接。

- 2. 将 SHR3 的输出连接到 SHR0 的 D 输入脚。

- 3. 使用 MF1 中 CNT1/DLY1 和 LUT9 创建时钟源。

- 4. 使用 I<sup>2</sup>C virtual inputs 清零 SHR0-SHR3, 之后再次写入 32bit 的移位数据并开始发送。

- 5. 增加 PIN9 并连接至 CLK 输出同步时钟用于识别数据。

## 应用: 固定长码发生器

利用 SLG46811 的 EPG 宏单元构造一个容量高达 736 位的模式发生器,低成本和低功耗的优点使其可以应用在许多实际场景下。

## 所需元器件

SLG46811V

#### GreenPAK 设计图

- 1. 配置 EPG 发生器(参见技巧: EPG),设置固定模式输出的数据。

- 2. 创建一个 8 位多路复用器,如参考应用: 8 位多路复用器,并连接到适当的 EPG 输出。

- 3. 创建一个基于 CNTO/DLYO 和 LUTO 的频率发生器,为 EPG 产生输入时钟。

- 4. 配置 CNT3/DLY3 用来计数频率发生器产生的 92 个时钟。

- 5. 基于 DFF8、DFF9 和 DFF11 的 3 位计数器用于选择从 EPG 输出的数据, 参见技巧: 多路复用比特流

- 6. 添加 EN 从 PIN5 输入, 高/低电平分别使能/关断 EPG。

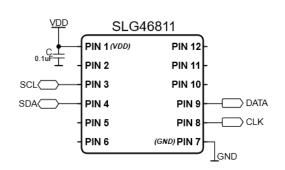

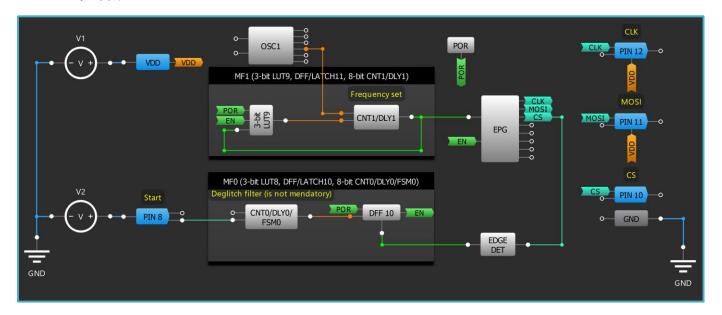

## 应用:简单 SPI 主机

这个应用演示了如何使用SLG46811 设备构建一个简单的SPI 主控器。使用该设备的SPI 主控器能够重复输出一个或多个字 节,对于一些不需要复杂功能的系统提供了有效的解决方 案。

#### I2C BUS SLG46811 R2≱ R1≱ PIN 1 (VDD) **PIN 12** → SCL PIN 2 **PIN 11** SDA PIN 3 **PIN 10** PIN 4 PIN 9 SEL0[ PIN 5 PIN 8 Start SEL1[ PIN 6 (GND) PIN 7 \_GND

#### 所需元器件

SLG46811V

#### GreenPAK 设计图

- 1. 配置 EPG 发生器(参见 EPG technique)来创建 SPI 发生器(Generator 选择为 SPI), 并选择相应的 MOSI, SCL, CS 信号输出。

- 2. 创建基于 CNT1/DLY1 和 LUT-9 的频率发生器,为 EPG 提供输入时钟。

- 3. CNTO/DLYO 构成 Deglitch 滤波器,被滤波的信号会通过 DFF10 产生 EN 信号使能 SPI 主机模式。

- 4. 使用 EDGE DET 为 Rising edge detect 并配置成 nOUT 模式以复位 DFF10。当 CS 重新变高时,EDGE DET 产生短暂的低电平以复位 DFF10,EN 信号因此变低。

# 第6章:基于脉冲的控制

本章介绍了控制信号脉冲宽度的应用。这些应用常常涉及 PWM 控制,通常 用于 LED 控制器, 电机控制器, 声音控制器。

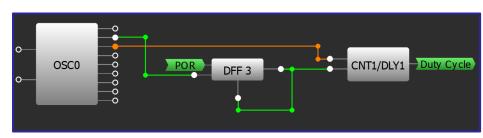

## 技巧: 恒定占空比 PWM

此技巧适用于所有GreenPAK。

设定一个固定占空比的 PWM 信号需要一个 CNT/DLY, 一个振荡器和一个 DFF, 设计图如下图所示。

简单的占空比设计图

DFF 作为一个上升沿检测器,DFF 的 CLK 信号(或者图中振荡器 OSC 的输出时钟)确定 PWM 信号的周期,CNT/DLY 如 Figure 26 所示配置为上升沿 Delay,决定 PWM 信号的占空比,当 DFF 的 CLK 接收到上升沿,将输出一个低电平的脉冲到 CNT1/DLY1,由于 CNT1/DLY1 配置为上升沿 Delay,CNT1/DLY1 将输出低电平,并在设定的延时时间后输出高。

将 DFF 的 **Q** output polarity 配置为 Inverted (n**Q**) ,并且连接 DFF 的 n**Q** 连到 nRESET,这样 DFF 将工作为一个上升沿检测器,除了 CLK 检测到上升沿时输出一个短时低电平脉冲外,其余时间将维持在高电平, FILTER/EDGE DET 组件也可以配置为类似的功能。

CNT/DLY 配置

可以用振荡器的 **OUTO** 或者 **OUT1** 作为 DFF 的 CLK 以确定输出 PWM 的周期,周期应当始终大于高电平时间,在这个例子当中, '**OUT1**' second divider by 设置为 **64**,因此周期为 Tosc\*64 CNT/DLY 的 **Counter data** 设定 PWM 低电平时间,PWM 的占空比计算公式:  $D = \frac{T_{period} - T_{delay}}{T_{model}}$

占空比 = 50% 的仿真结果

## 技巧:输出一个高脉冲信号

此技巧适用于所有GreenPAK 芯片。

单脉冲电路生成具有事先定义的持续时间长度的输出脉冲。在电路产生脉冲后,它会返回其稳定状态,并且在再次触发之前不再产生脉冲。它是复位功能、看门狗定时器和许多其他应用中一个非常重要的组件。在 GreenPAK 中可以轻松输出一个脉冲信号。下图显示了几种由输入 EN 上升沿触发建立一次性脉冲的方法。脉冲持续时间可以通过改变所使用的 DLY 模块中的计数器数据值来调整。

几种一次性脉冲信号实现方法

在许多 GreenPAK 芯片(见下图)中,实现一次性脉冲只需要一个 DLY 模块。用户唯一需要做的就是将模块属性窗口中的模式切换为 "One shot"并选择它将检测到的边沿。可以是上升沿、下降沿或两者兼而有之。

使用 SLG46826 实现一次性脉冲

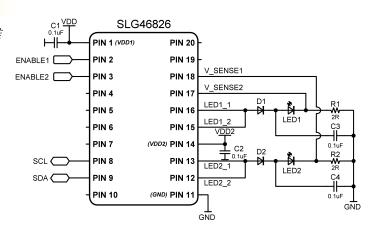

## 应用: LED 恒流驱动器

LED 驱动器为LED 提供恒定的电流,可以将输出功率维持在安全水平内,防止热失控。

## 所需元器件

- 任意 GreenPAK IC(CMIC)

- 2个电容

- 4个二极管 (2个 LED, 2个普通二极管)

- 2个电阻

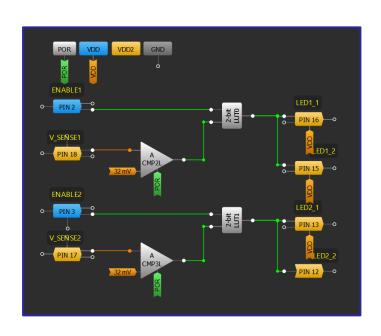

#### GreenPAK 设计图

- 1. 配置 2 个 ACMP, 并将每一个比较器的 IN- source 设置为所需的阈值。

- 2. 配置 LUT 逻辑以使能 LED 的输出。

- 3. 将引脚 LED1\_1 和 LED1\_2 连接到普通二极管的阳极,然后将普通二极管的阴极接到 LED 的阳极。

- 4. 在 LED 的阴极和 GND 之间插入一个电阻。

- 5. 在 LED 的阳极和 GND 之间并入一个电容。

- 6. 重复步骤 3 到 5 连接 LED2 的输出。

- 7. 将 V SENSE1 脚和 V SENSE2 脚分别连接到 LED1 和 LED2 的阴极。

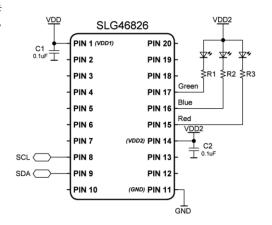

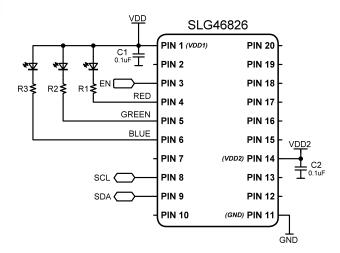

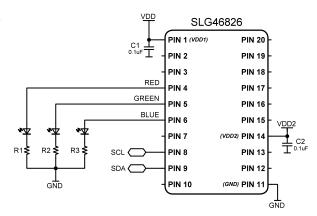

## 应用:用 I<sup>2</sup>C 控制 RGB LED

RGB LED 可用于多样化色彩输出 LED 显示系统,并可通过 GreenPAK 进行控制。在本实例中展示了一种利用 GreenPAK I<sup>P</sup>C, 通过改变占空比以实现 LED 显示不同颜色的简单方法。

#### 所需元器件

- 任意包含 I<sup>2</sup>C 的 GreenPAK IC(CMIC)

- RGB LED

- 3个电阻

#### GreenPAK 设计图

- 1. 将 RGB 阴极连接的 Pin 脚配置为 open-drain outputs。

- 2. 添加 LUT 逻辑单元和 CNT/DLY2 模块以创建一个包含 EN 使能信号的发生器。

- 3. 将 CNT/DLY 模块配置为 rising-edge delay。

- 4. 使用 技巧: 配置标准逻辑 为各个输出添加并配置 LUT。

- 5. 将各个 LUT 的输出连接至相应的输出脚。

- 6. 通过访问 I<sup>2</sup>C Virtual inputs 对应的寄存器,每个 I<sup>2</sup>C Virtual Input 都可以单独更改或者同时更改。

- 7. 通过 I<sup>2</sup>C,可以单独或同时更改 CNT/DLY 模块的 Counter data。

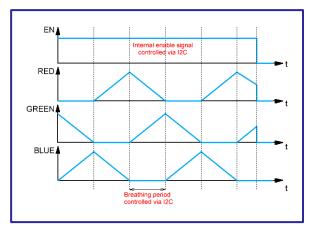

## 技巧: LED 呼吸模式

此技巧适用于所有GreenPAK。独立软开关通道的数量取决于特定芯片中可用的计数器数量。

呼吸 LED 模式可以利用两个计数器之间的恒定变化实现。在其编程周期内,每个计数器输出一个周期高电平。 使用不同的 counter data settings 将两个 CNT/DLY 模块配置成计数值不同的计数器,让它们的输出之间产生一个小的偏移量。这些输出信号用于设置和复位设备内的触发器。 下图展示了一个基本实例,其中 CNT2/DLY2 设置 ON period, CNT3/DLY3 设置占空比。

LED 呼吸模式实例

在上图的实例中,由 CNT2 所确定的 PWM 的频率可由以下等式计算:

$$f_{PWM} = \frac{fosc}{(Data_{CNT2} + 1)}$$

下图的波形显示了偏移量的影响。 当两个计数器的输出重合时,PWM 的周期结束。 这将导致在与门和 DFF 中出现一个很短的高电平脉冲。 或非门实现了 PWM 的反相,提供了一个软关断。 2 脚是使能信号,当其为高电平时,计数器将进行高电平复位。

## 应用: RGB LED 呼吸灯

RGB LED 可用于多样化色彩输出LED 显示系统,并可通过 GreenPAK 进行控制。也可以搭配一个软开关电路来实现 呼吸模式。

## 所需元器件

- 任意 GreenPAK IC(CMIC)

- RGB LED

- 3个电阻

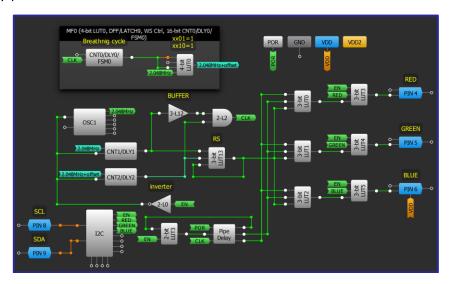

#### GreenPAK 设计图

- 1. 将 GPIO 配置为 open drain NMOS。

- 2. 参考 技巧: LED 呼吸模式 创建一个软开关电路。

- 3. 配置 Ripple Counter 的 Functionality mode 为: range: SV-EV cycles (SV=1, EV=3)。

- 4. 将 LUTs 配置为一个多路解复用器。

- 5. 添加使能 (EN) 信号以控制 RGB 呼吸灯的启动/停止。

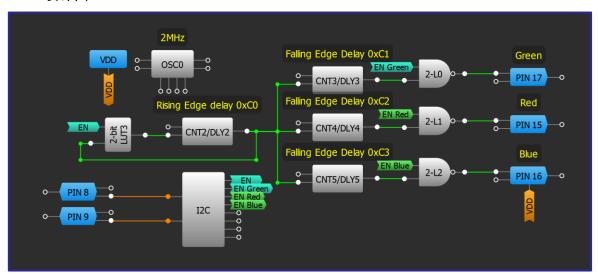

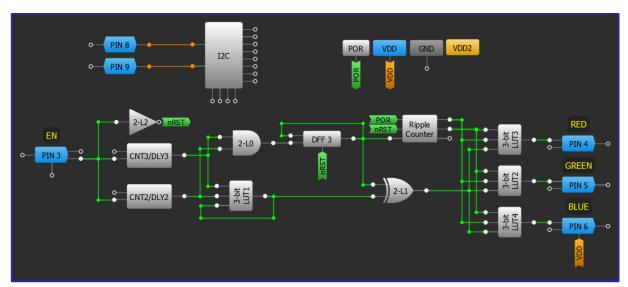

## 应用:用I<sup>2</sup>C 实现 RGB LED 呼吸灯的控制

RGB LED 可用于多样化色彩输出 LED 显示系统。也可以搭配一个软开关电路来实现呼吸模式,并可通过 GreenPAK PC 进行控制。改变 CNTO 的 counter data 可改变呼吸周期。

#### 所需元器件

- 任意包含 I<sup>2</sup>C 的 GreenPAK IC(CMIC)

- RGB LED

- 3个电阻

#### GreenPAK 设计图

- 1. 参考 技巧: LED 呼吸模式 创建一个软开关电路,需要将 CN1 和 CN2 的 counter data 设置为相同的值。

- 2. 添加 MF0 以建立 CN1 和 CN2 之间小的偏移量。

- 3. 将 **LUT3-LUT5** 配置为多路复用器,由 I<sup>2</sup>C 的 EN 信号进行切换控制。

- 4. 将 LUT0-LUT2 配置为一个多路解复用器,它根据右侧的时序图传递呼吸信号。

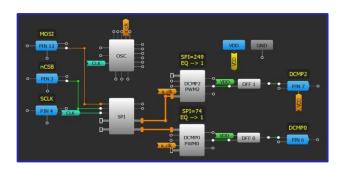

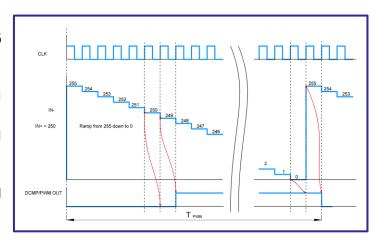

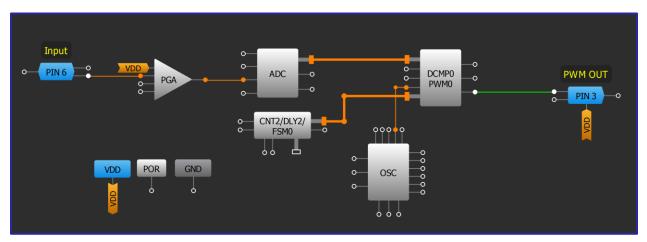

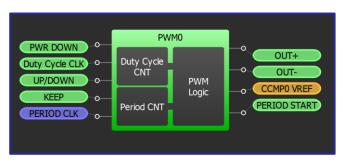

## 技巧: DCMP/PWM 宏单元在 PWM 模式下的应用

此技巧适用于DCMP 组件,可应用于SLG46140, SLG46620 和SLG46621。

#### DCMP/PWM 宏单元概述

DCMP/PWM 宏单元可用于两个 8 位数值的比较或生成 PWM 信号。每个 GreenPAK 芯片包含 3 个相互独立的 DCMP/PWM 组件,每个 DCMP/PWM 组件有两个 8 位输入端(IN+, IN-),可以生成一个 PWM 信号。输入脚 MTRX SEL#0 和 MTRX SEL#1 用于在静态 PWM 生成过程中在 4 个寄存器中进行切换。输入脚 SHARED PD 用于控制 DCMP/PWM 组件的启用或停用。PWM 输出占空比范围可配置为 0% 至 99.61% 或 0.39% 至 100%。

IN+

MTRX SEL#0

MTRX SEL#1

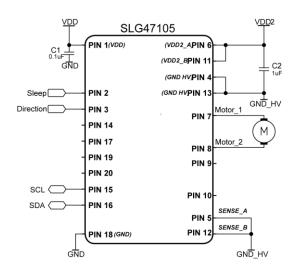

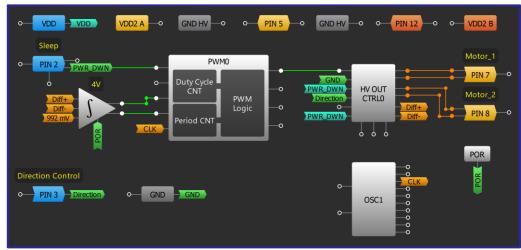

O

DCMP0

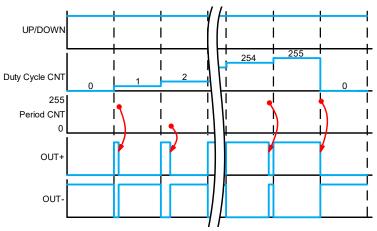

PWM0

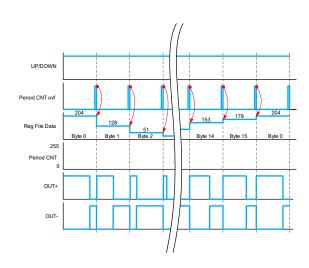

OUTIN

OUTOUT+

#### 创建 PWM 信号

PWM 发生器的一个输入信号来自于计数器,它能根据 PWM ramp 值线性循环,计数范围从 255 到 0,反之亦然。

另外一个输入至少在 1 个 PWM 信号周期内 (PWM 斜坡计数器周期) 是稳定的。它可以是来自 SPI、ADC、FSM 组件的数据,也可以是来自 DCMP/PWM 的内部寄存器的数据。

右图显示了当IN-连接到一个由255计数到0(PWM 斜坡计数器)的 CNT/DLY 组件, IN+ 是一个设置为250的内部寄存器时 DCMP/PWM 的工作波形。

IN+ 信号的配置是该宏单元配置的关键因素。可以通过内部寄存器设定静态 PWM 值,通过 ADC 监控 PWM 动态反馈,MCU 也可以通过 SPI 接口调节发出的 PWM。

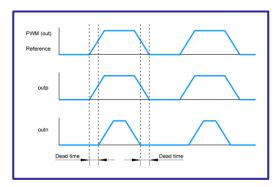

输出 **OUT-** 和 **OUT+** 的死区时间可以设定为 10 - 80 ns, 可以通过 DCMP/PWM 的属性面板进行设定。

DCMP/PWM 在 PWM 模式下的时序

OUT- 和 OUT+ 的死区时间

## 应用: PWM 选择器

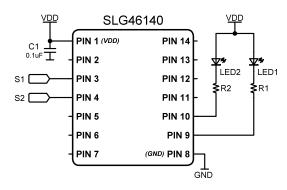

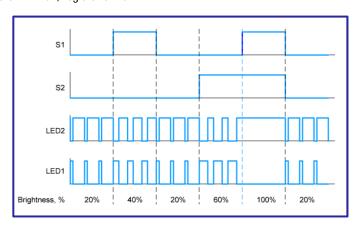

PWM 选择通常用于 LED 亮度调节和风扇转速控制等功能。在本实例中,基于两个按键的输入,可实现两颗 LED 的亮度调节。

#### 所需元器件

- 任意包含 DCMP 的 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

- 1. 断开 VDD 与 **SHARED PD** 的连接,启用 DCMP。将 DCMP/PWM 的 power register 设置为 **Power on**, 将 **IN+ selector** 配置为 **Register selected through from matrix**, **IN- selector** 配置为 **FSM1**[7:0]。将 DCMP0 的各个寄存器配置如下: register 0 51; register 1 102; register 2 154; register 3 0。

- 2. 添加 CNT/DLY 模块并配置 Counter/FSM, 设置 counter data 为 255。

- 3. 将 RC OSC power mode 配置为 Force power on

- 4. 将 PIN10 和 PIN9 配置为 open drain NMOS。

- 5. 添加 LUT 作为反相器。

- 6. 将输入脚连接到 DCMP/PWM 模块的 **MTRX SEL** 脚。

**PIN 14**

**PIN 13**

**PIN 12**

**PIN 11**

**PIN 10**

PIN 9

GND

(GND) PIN 8

☐ Input

SLG46140

PIN 1 (VDD)

PIN 2

PIN 3

PIN 4

PIN 5

PIN 6

PIN 7

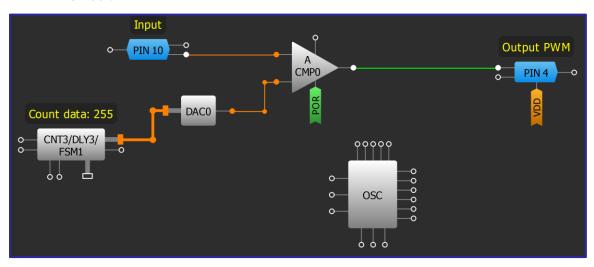

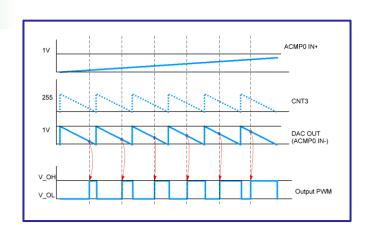

# 应用:采用 ACMP 和 DAC 的 PWM 发生器

PWM 发生器可以用来控制直流电机和 LED 等设备。本实例使用 ACMP 将输入的模拟信号和 DACO 输出信号进行比较,CNT3 用于 生成 DAC 的值。

## 所需元器件

- 任意包含 DAC 的 GreenPAK IC(CMIC)

- 无需其他元器件

#### GreenPAK 设计图

#### 设计步骤

- 1. 将 ACMPO 的 PWR UP 连接到 POR, IN-source 配置为 Ext. Vref (DACO out)。

- 2. 将 DACO 的 power on signal 配置为 Power on, input selection 选择为 From DCMP1's input。

- 3. 将兼容 FSM 的 CNT/DLY 配置为 **Counter/FSM** 模式, 设置 counter data = 255。

- 4. 将 RC OSC power mode 配置为 Force power on。

<u>VDD</u>

Output PWM (

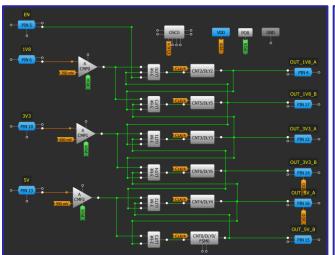

## 应用:采用 ADC 的 PWM 发生器

PWM 发生器可以用来控制直流电机和 LED 等设备。本实例使用连接到 ADC 的模拟信号与 PWM0 中的 CNT2 值进行比较。如果 CNT2 值小于被数 字化的模拟信号值, PWM0 输出高电平。 CNT2 值变为 0 后, PWM0 输出低电平。

#### 所需元器件

- 任意包含 ADC 的 GreenPAK IC(CMIC)

- 无需其他元器件

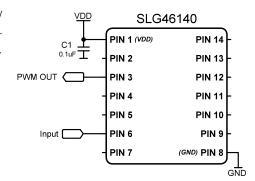

#### GreenPAK 设计图

- 1. 断开 VDD 与 ADC-PWR DOWN 的连接,将 PGA power on signal 配置为 Power on.

- 2. 将 PIN 6 配置为 Analog input/output。

- 3. 配置 DCMPO/PWMO, 断开 VDD 与 SHARED PD 的连接。DCMP/PWM power register 配置为 Power on。确认 IN+ selector 连接到 ADC [7:0]

- , IN- selector 连接到 FSM0 [7:0]。

- 4. 配置一个 4 位的 LUT1/ 14 位的 CNT2/DLY2/FSM0 作为 Counter/FSM,设置 counter data 为 255。

- 5. 将 DCMP0/PWM0 OUT+ 连接到输出脚。

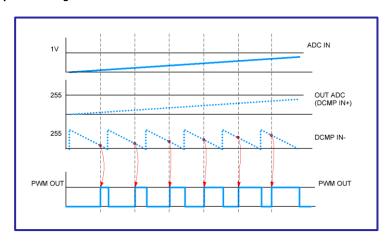

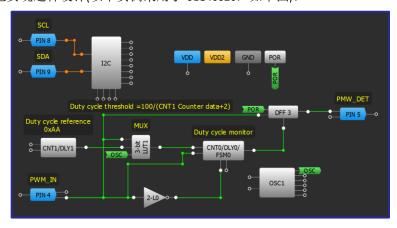

## 技巧: 占空比检测

此技巧适用于所有GreenPAK。 由于输入频率范围受到最大FSM 计数器数据的限制,所以最好使用16 位 FSM。PWM 检测输入频率应大大低于占空比参考频率,以提高精度。

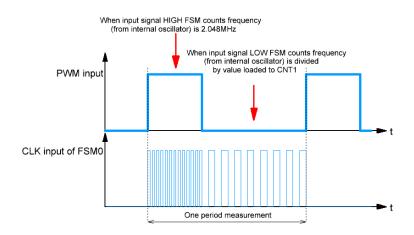

占空比检测对于过载保护、DC/DC 转换、伺服电机控制和协议检测等功能非常重要。使用包含 FSM 组件的 GreenPAK可以很容易地实现这种设计(以下实例采用了 SLG46826, 如下图)。

在上述实例中, 当 4 脚转为高电平, FSM0 根据内部振荡器时钟频率, 开始向下计数(减小计数值)。 在 4 脚脉冲 的上升沿, FSM0 被置为 65535。 当 4 脚转为低电平, FSM0 开始以内部振荡器除以 CNT1 的值为频率进行向上 计数。 如果 FSM0 计数值达到 65535, DFF3 将在 4 脚的下一个上升边沿转为低电平,这表示占空比低于设置的 阈值。

占空比的参考频率可通过利用 I<sup>2</sup>C 来改变 CNT1 的 counter data value 以进行调整。 使用以下公式计算占空比阈值 :

$$Duty \ Cycle \ Threshold = \frac{100}{\text{CNT1 Counter data} + 2} \ (\%)$$

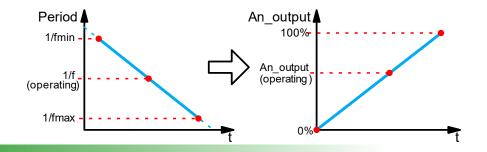

## 应用:频率/模拟电压转换器

该应用将输入频率转换为模拟电压。 输入频率在一定范围内可由设计元件选择和调节。输出模拟电压恒定并且可根据需要进行调整。

#### 所需元器件

• 任意带 SPI 和 DAC 功能的 GreenPAK IC (CMIC)

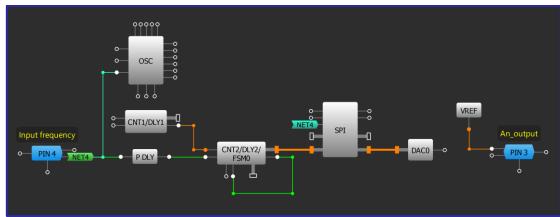

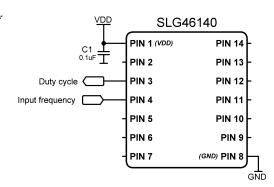

#### <u>VDD</u> SLG46140 PIN 1 (VDD) **PIN 14** PIN 2 **PIN 13** An\_output PIN 3 **PIN 12** PIN 4 **PIN 11** Input frequency PIN 5 **PIN 10** PIN 6 PIN 9 PIN 7 (GND) PIN 8

#### GreenPAK 设计图

- 1. 配置 SPI 为"ADC/FSM Buffer"模式,修改 PAR input data 源为"FSM0[15:8]。

- 2. 配置 **FSM0** 模块为"Set (counter value)",将时钟源修改为 **CNT1**。

- 3. 配置 DAC Input selector 为 "From DCMP1 's Input", VREF Source selector 为 "DACO out"。

- 4. 输入频率范围和输出模拟电压的计算公式如下:

$$f_{min} = \frac{f_{osc}}{{\scriptstyle (CNT1+1)\cdot FSM0}} \qquad f_{max} = \frac{f_{osc}}{{\scriptstyle (CNT1+1)}} \qquad An\_output_{operating} = V_{ref\_max} - \frac{f_{min} \cdot V_{ref\_max}}{f_{operating}}$$

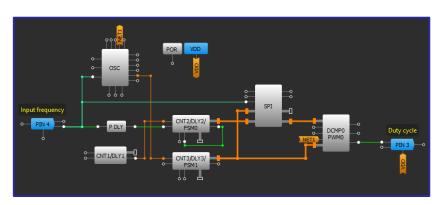

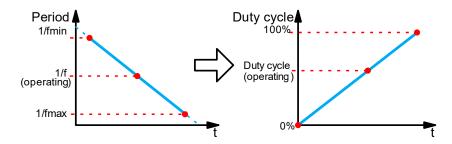

## 应用:频率/占空比转换器

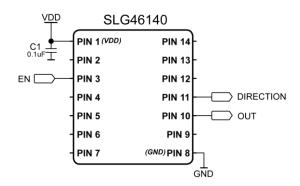

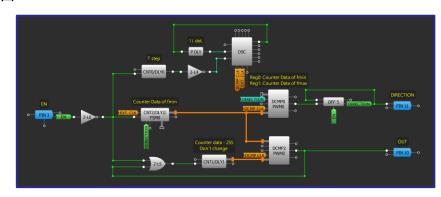

该应用可以用来将输入频率转换为一定的占空比。 输入频率在预定 的范围内,可以通过调整计数器来改变。输出PWM 频率是恒定的, 但可以根据给定的要求改变。

#### 所需元器件

任意带 SPI 跟 DCMP 的 GreenPAK IC (CMIC)

#### GreenPAK 设计图

- 配置 SPI 为"ADC/FSM buffer"模式, 修改 PAR 输入数据源为"FSM0[15:8] FSM1[7:0]"。

- 配置 FSMO 模块为"Set (counter value)",将时钟源修改为"8 位 CNT1/DLY1 (OUT)"。

- 配置 DCMP0 为比较"SPI[15:8]"数据和"FSM1[7:0]"数据。

- 使用以下公式计算输入频率范围和工作占空比:

$$f_{min} = \frac{f_{osc}}{(\textit{CNT1+1}) \cdot \textit{FSM1}} \qquad f_{max} = \frac{f_{osc}}{(\textit{CNT1+1})} \qquad \textit{Duty Cycle}_{operating} = \left(1 - \frac{f_{min}}{f_{operating}}\right) \cdot 100\%.$$

## 应用:线性调频

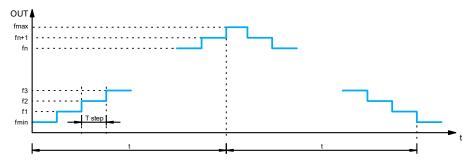

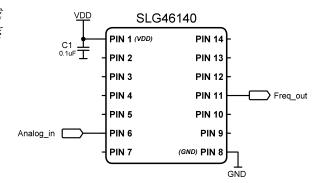

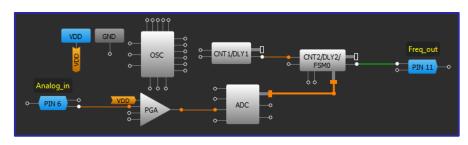

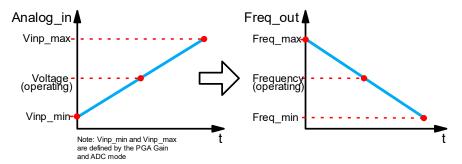

该应用可以用来产生一个频率, 它的频率可以在特定的时间内 从 fmin 逐渐改变为 fmax, 反之亦然。在较大的频率范围内, 频 率不会线性变化。

### 所需元器件