### RTKA788000DE0010BU

Stacked Sensor Board

Apr 19, 2024

The RTKA788000DE0010BU evaluation board allows the measurement of power line currents up to 80A.

The board includes two RAA788000 current sensor ICs in stacked sensor topology, for easy connection to a high-current source.

The output amplifiers of the two sensors are configured to a single differential amplifier to allow for differential current measurements with minimum noise.

#### **Features**

- Two current sensor ICs

- High-gain setting of 200V/V

- Stacked sensor topology

- Differential current measurement up to 80A

- Wide 2.7V to 3.6V supply voltage range

### **Specifications**

- $V_S = 3.3V$

- G<sub>DIFF</sub> = 201

- 4mm sensor pair

- Trendline error calculations use linear best fit for three decades of current

- 1A 80A: Trendline Error < 1%

Note: For power line current > 80A, see section Current Sensor Pairs & Passband Gain for current sensor pair selection and gain adjustment.

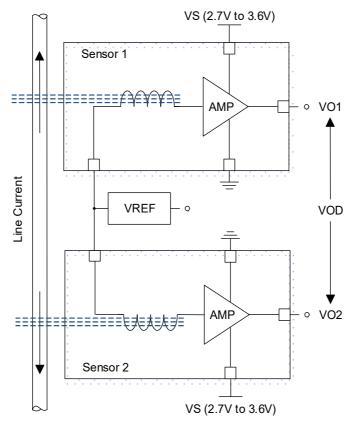

Figure 1. Block Diagram

### RTKA788000DE0010BU Evaluation Board Manual

# **Contents**

| 1. | Functional Description |            |                        |    |  |

|----|------------------------|------------|------------------------|----|--|

|    | 1.1                    | Operati    | tional Characteristics |    |  |

|    |                        | 1.1.1      | Supply Voltage         |    |  |

|    |                        | 1.1.2      | Passband Gain          |    |  |

|    | 1.2                    | Quick S    | Setup                  | 4  |  |

|    |                        | 1.2.1      | Current Sensor Pairs   |    |  |

|    |                        | 1.2.2      | Measurement Process    | 6  |  |

|    |                        | 1.2.3      | Best Fit Trendline     | 6  |  |

| 2. | Boai                   | rd Desig   | ın                     |    |  |

|    | 2.1                    | Layout     | Guidelines             |    |  |

|    | 2.2                    | Schem      | natic Diagrams         |    |  |

|    | 2.3 Bill of Materials  |            |                        |    |  |

|    | 2.4                    | Board I    | Layout                 |    |  |

| 3. | Турі                   | cal Perfo  | ormance Graphs         | 11 |  |

| 4. | Orde                   | ering Info | ormation               | 11 |  |

| 5  | Revision History       |            |                        | 11 |  |

## 1. Functional Description

The RAA788000 evaluation board allows for quick power-line current measurements by affixing the board to a power-line cable with zip ties. The current within the cable produces a magnetic field, which is picked up by the on-chip coil. The coil generates a voltage in the form of an electromotive force, EMF. The coil outputs are amplified and then made available as differential output voltage ( $V_{OD}$ ) between  $V_{O1}$  and  $V_{O2}$ . The main connection points on the board are the reference voltage supply (VCC, GND), enable (EN0 for the 16mm sensor pair and EN3 for the 4mm sensor pair) and outputs ( $C_{00}$  and  $C_{01}$  for the 16mm sensor pair and  $C_{30}$  and  $C_{31}$  for the 4mm sensor pair).

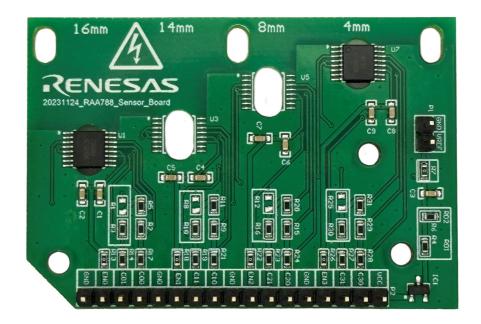

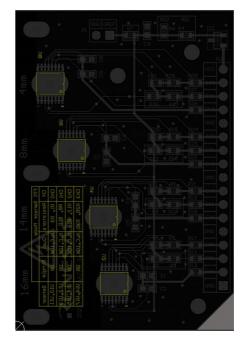

Figure 2. RTKA788000DE0010BU Evaluation Board

# 1.1 Operational Characteristics

The supply voltage and passband gain may be adjusted as necessary.

#### 1.1.1 Supply Voltage

The operating range for the RAA788000 is between 2.7V and 3.6V.

#### 1.1.2 Passband Gain

The gain can be adjusted through the  $R_G$  resistor within the differential amplifier depending on customer needs. Equation 1 is the differential passband gain equation.

(EQ. 1)

$$G_{PB(DIF)} = 1 + \frac{2R_F}{R_G}$$

Changing  $R_G$  has a ramification on the high-pass cut-off frequency created by the gain resistor and the DC blocking capacitor. If the gain needs to be changed, see the Band-Pass Filtering section in the datasheet.

### 1.2 Quick Setup

- 1. Strap a 2-AWG powerline cable to the evaluation board to test AC current up to 80A.

- Connect an external +5.0V DC supply voltage to VCC, an external +3.3V DC supply voltage to EN3 for the 4mm sensor pair and GND terminals (ENx pins can be powered by the MCU GPIO for other sensor pair enabling).

- 3. Apply an AC current through the powerline cable.

- 4. Differential output voltage ( $V_{OD}$ ) between  $C_{30}$  and  $C_{31}$  are recorded.

- 5. Voltage measurements are converted from V<sub>OD</sub> to current using a linear equation.

*Note*: For any AC current larger than 80A, select a proper gauge size of the cable and sensor pair for testing (see Current Sensor Pairs). The input voltage range on the MCU side determines the reference voltage. The default reference voltage is set to 0.25V and can be reconfigured on the evaluation board.

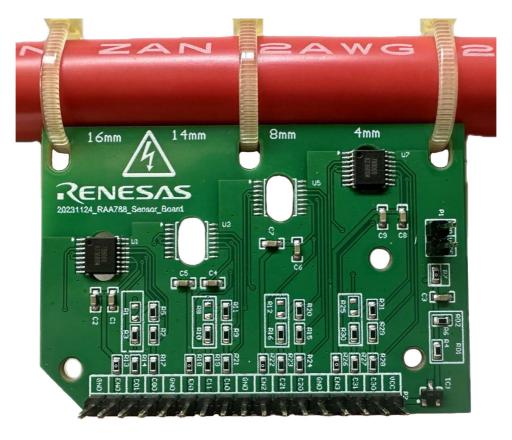

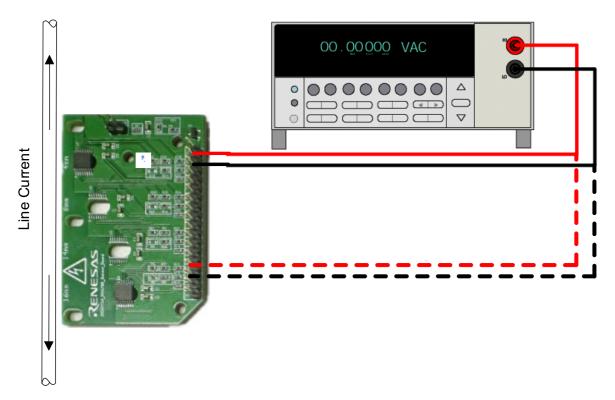

Figure 3. 2-AWG Cable Setup

#### 1.2.1 Current Sensor Pairs

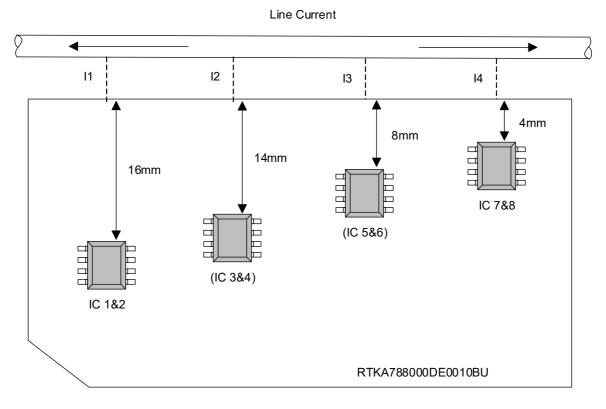

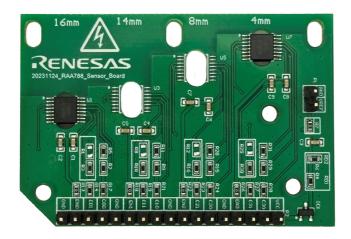

The RTKA788000DE0010BU evaluation board features four current sensor pairs (Figure 4). Each pair can be equipped with two RAA788000 chips in stacked topology. The distance for each sensor pair is respectively 4mm, 8mm, 14mm, and 16mm. Different sensor distributions are designed for different AC current ranges. Sensor pair I4 is recommended for AC current up to 80A. Sensor pair I2 and I3 are currently unmounted. Is there is a need, contact the FAE engineer to request evaluation boards for specific requirements.

Figure 4. Current Sensor Pair I1 to I4

Table 1 displays an example of the corresponding distances and AC current ranges for sensor pair I1, I2, I3, and I4.

| Sensor Pair | Distance | Current Range |

|-------------|----------|---------------|

| 14          | 4mm      | 1A to 200A    |

| 13          | 8mm      | 100A to 500A  |

| I2          | 14mm     | 400A to 800A  |

| I1          | 16mm     | 700A to 1200A |

Table 1. Example of AC Current Range vs. Sensor Distance

#### 1.2.2 Measurement Process

On the evaluation board, each sensor pair has two outputs  $C_{x0}$  and  $C_{x1}$  that make up the differential output voltage ( $V_{OD}$ ). These ( $V_{OD}$ ) measurements can be recorded using a multimeter on the AC voltage setting (Figure 5).

Figure 5. Example VOD Measurement with Multimeter

#### 1.2.3 Best Fit Trendline

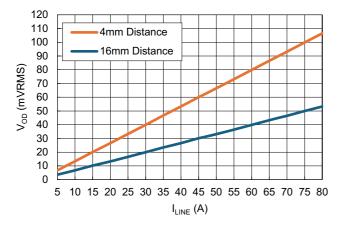

Small variations such as wire distance have a large effect on coil sensitivity, therefore Renesas recommends developing a setup-specific trendline for best accuracy. To create this trendline, perform a load current sweep using at least three data points for the range in which measurements are taken. For the range such as 1A-80A, these data points may be taken at 5A, 40A, and 80A. After the V<sub>OD</sub> measurements have been recorded, a best fit trend (Figure 14) is developed using a linear best fit equation.

**(EQ. 2)**

$$y = mx + b$$

With the load current on the x-axis and the V<sub>OD</sub> on the y-axis, Equation 2 can be represented as:

(EQ. 3)

$$V_{OD} = m \times I_{L(Estimated)} + b$$

Solving for I<sub>L(Estimated)</sub>, Equation 3 becomes Equation 4:

(EQ. 4)

$$I_{L(Estimated)} = \frac{V_{OD} - b}{m}$$

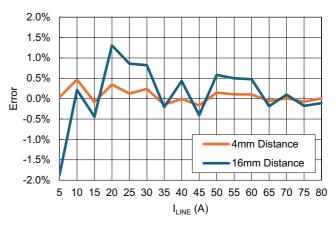

For each measured  $V_{OD}$ , an estimated load current is determined using Equation 4. The estimated load current is compared with the actual load current to determine its error percentage (Figure 15).

(EQ. 5) %Error =

$$\frac{I_{L(Actual)} - I_{L(Estimated)}}{I_{L(Actual)}} \times 100$$

## 2. Board Design

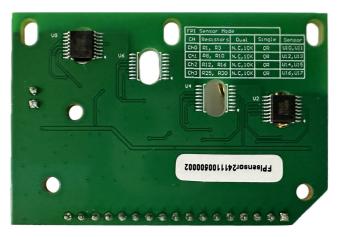

Figure 6. Evaluation Board (Top)

Figure 7. Evaluation Board (Bottom)

### 2.1 Layout Guidelines

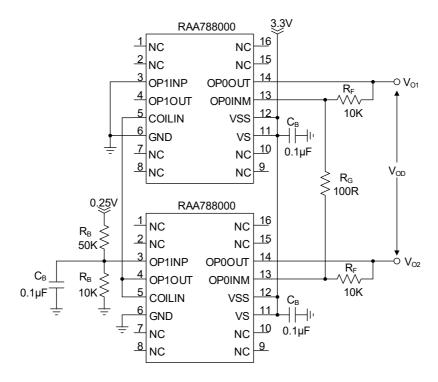

Place bypass capacitors (C<sub>B</sub>) as close as possible to the IC supplies to suppress high frequency noise (Figure 8).

Figure 8. Decoupling and DC Blocking Capacitor Placement

**IMPORTANT**: For stacked topology designs, such as this evaluation board, cut-out the PCB underneath the chips (Figure 6, Figure 7) to create an unobstructed magnetic field path. As well, select a proper sensor pair based on the diameter of the power-line cable for optimal sensitivity (Figure 4).

In addition, a DC blocking cap may be placed in series with  $R_G$  (Figure 8) to prevent the internal op-amps input offset from being amplified. Without this capacitor, in high gain applications such as a 2000V/V gain, the high input offset of the internal op-amp  $\pm 2$ mV (maximum) would drive the output into saturation.

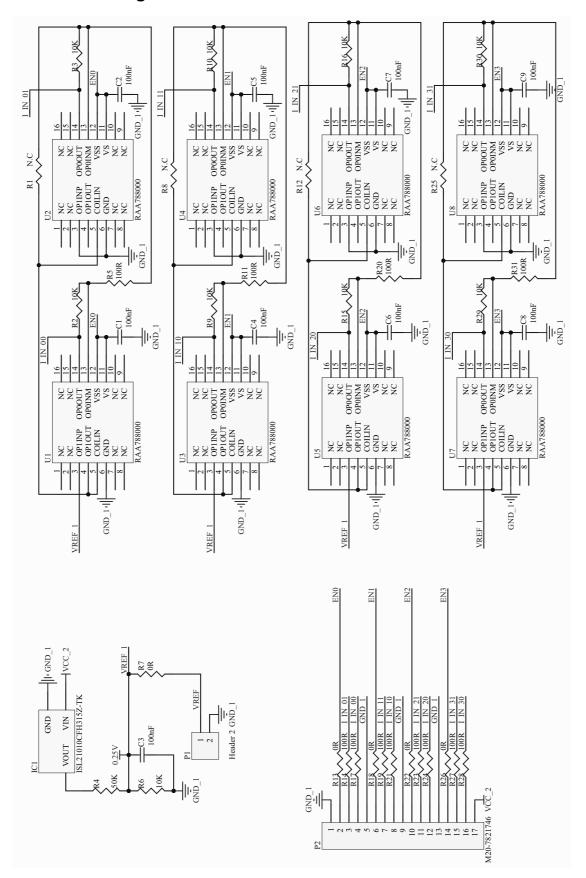

## 2.2 Schematic Diagrams

Figure 9. RTKA788000DE0000BU Schematic

## 2.3 Bill of Materials

|     | Reference                                                             |                                                                                                  |                     | Manufacturer       |

|-----|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|--------------------|

| Qty | Designator                                                            | Description                                                                                      | Manufacturer        | Part Number        |

| 9   | C1, C2, C3,<br>C4, C5, C6,<br>C7, C8, C9                              | Ceramic Capacitor, 0.1µF, 50V, ± 5%, X7R, 0603                                                   | Samsung             | CL10B104JB8NNNC    |

| 1   | IC1                                                                   | Micropower Voltage Reference, 1.5V, SMD SOT23-3                                                  | Renesas Electronics | ISL21010CFH315Z-TK |

| 1   | P1                                                                    | Male, PCB Receptacle, Board-to-Board,<br>2.54mm, 1 Rows, 2 Contacts, Through Hole<br>Mount       | ХКВ                 | X6511WV-02H-C60D30 |

| 1   | P2                                                                    | Male, PCB Receptacle, Board-to-Board,<br>2.54mm, 1 Rows, 17 Contacts, Through<br>Hole Mount, M20 | ХКВ                 | X6511WV-17H-C60D30 |

| 4   | R1, R8, R12,<br>R25                                                   | Do Not Populate                                                                                  | -                   | -                  |

| 9   | R2, R3, R6,<br>R9, R10, R15,<br>R16, R29, R30                         | Chip Resistor, 10k, ±1%, 0.1W, 0603                                                              | Panasonic           | ERJ-3EKF1002V      |

| 1   | R4                                                                    | Chip Resistor, 50k, ±1%, 0.1W, 0603                                                              | Panasonic           | ERJ-3EKF4992V      |

| 12  | R5, R11, R14,<br>R17, R19,<br>R20, R21,<br>R23, R24,<br>R27, R28, R31 | Chip Resistor, 100Ω, ±1%, 0.1W, 0603                                                             | Panasonic           | ERJ-3EKF1000V      |

| 5   | R7, R13, R18,<br>R22, R26                                             | CHIP RESISTOR, 0?, ±1%, 0.1W, SMD 0603                                                           | Panasonic           | ERJ-3GEY0R00V      |

| 4   | U1, U2, U7, U8                                                        | Renesas Analog Current Sensor,<br>TSSOP-16                                                       | Renesas Electronics | RAA788000GSP#HA0   |

| 4   | U3, U4, U5,<br>U6,                                                    | Do Not Populate                                                                                  | -                   | -                  |

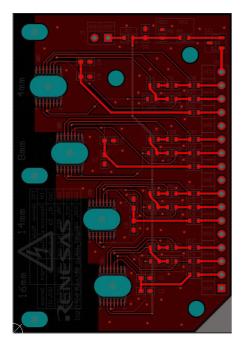

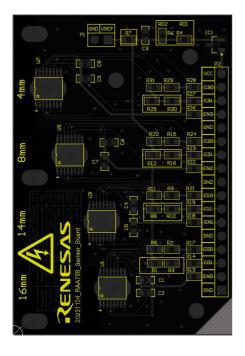

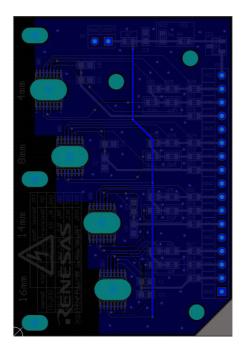

# 2.4 Board Layout

Figure 10. Top Layer

Figure 12. Top Silk Screen

Figure 11. Bottom Layer

Figure 13. Bottom Silk Screen

# 3. Typical Performance Graphs

Figure 14 and Figure 15 depict the linearity and trendline error for the current measurement range 5A - 80A. All trendlines represent the linear best fit. The applied operating conditions were,  $T_A = 25^{\circ}C$ ,  $V_S = 3.3V$ ,  $V_{IN} = 0.25V$ , AWG = 2, Distance from Cable to IC = 4mm and 16mm,  $G_{DIFF} = 201$ . The measurement error becomes larger with low line current when the distance from cable to IC increased from 4mm to 16mm.

Figure 14. Output Voltage vs Line Current, I<sub>LOAD</sub> = 0A

Figure 15. Trendline Error vs Line Current,  $I_{LOAD} = 0A$

## 4. Ordering Information

| Part Number        | Description                              |  |

|--------------------|------------------------------------------|--|

| RTKA788000DE0010BU | Stacked Sensor Topology Evaluation Board |  |

# 5. Revision History

| Revision | Date         | Description     |

|----------|--------------|-----------------|

| 1.00     | Apr 19, 2024 | Initial release |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.