#### RTKP51045DE0000BU

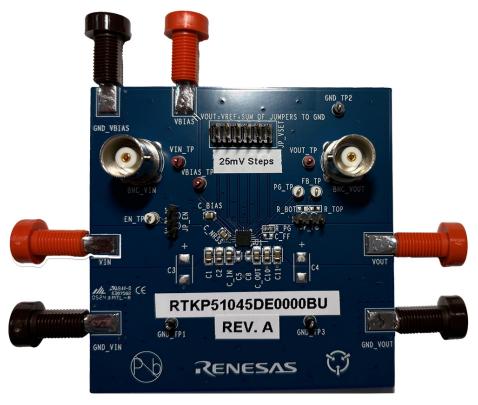

The RTKP51045DE0000BU evaluation board provides a simple platform to evaluate the 3.5×3.5mm 20-Ld QFN RRP51045 low-dropout linear regulator (LDO).

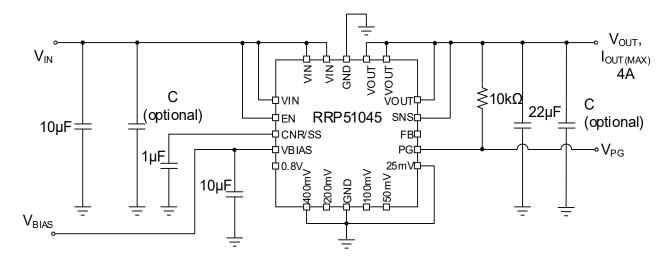

The RRP51045 is an ultra-low noise, high PSRR LDO regulator capable of sourcing up to 4A of load current with very low dropout. The output voltage can be programmed from 0.5V to 2.075V using voltage setting pins on the IC in 25mV steps. The evaluation board has convenient jumpers to exercise these pins. External feedback resistors can still be used for higher output voltage applications, allowing the output voltage to be programmed anywhere from 0.5V to 5.1V.

The LDO operates from an input voltage of 1.4V to 6.5V without VBIAS and 1.1V to 6.5V with VBIAS.

#### **Features**

- Output voltage set pins easily programmed with JP VSET

- Switch between voltage set pins or external resistor divider using jumper JP\_FB

- Convenient shutdown mode function using jumper JP EN

- Power-good (PG) indication test point

- V<sub>BIAS</sub> banana jack or turret for applications, where V<sub>IN</sub> < 1.4V</li>

- BNC\_VIN and BNC\_VOUT connections for PSRR and output noise testing

## **Specifications**

This evaluation board is specified for the following operating conditions:

- Input voltage range: 1.4V to 6.5V without VBIAS and 1.1V to 6.5V with VBIAS

- V<sub>BIAS</sub> voltage range: 3V to 6.5V ultra-low output noise: 7µVRMS

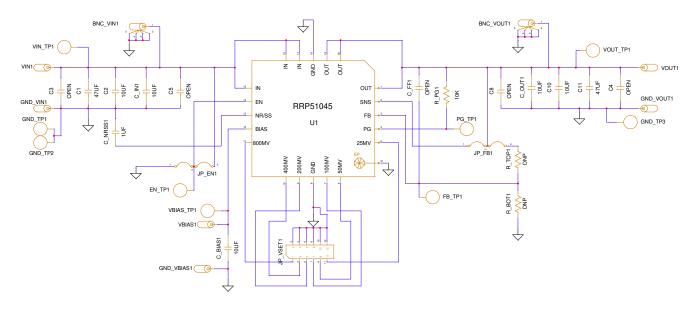

Figure 1. Typical Application Schematic

## RTKP51045DE0000BU Evaluation Board Manual

# **Contents**

| 1. | Fund | Functional Description  |     |  |  |  |  |  |  |

|----|------|-------------------------|-----|--|--|--|--|--|--|

|    | 1.2  | Setup and Configuration | . 6 |  |  |  |  |  |  |

| 2. | Boa  | rd Design               | . 8 |  |  |  |  |  |  |

|    | 2.1  | PCB Layout Guidelines   | . 8 |  |  |  |  |  |  |

|    | 2.2  | Schematic Diagrams      | . 9 |  |  |  |  |  |  |

|    | 2.3  | Bill of Materials       | . 9 |  |  |  |  |  |  |

|    | 2.4  | Board Layout            | 10  |  |  |  |  |  |  |

| 3. | Турі | cal Performance Graphs  | 11  |  |  |  |  |  |  |

| 4. | Orde | ering Information       | 12  |  |  |  |  |  |  |

| 5. | Revi | sion History            | 12  |  |  |  |  |  |  |

# 1. Functional Description

The RTKP51045DE0000BU evaluation board provides a simple platform for demonstrating the features of the RRP51045 low-noise, high-PSRR LDOs, helping design and system engineers evaluate critical performance parameters for their applications.

## 1.1 Setup and Configuration

### 1.1.1 Programming the Output Voltage

The output voltage can be programmed using the EVB PCB layout using convenient output voltage set pins (25mV, 50mV, 100mV, 200mV, 400mV, 800mV) or with traditional external feedback (FB) resistors. To switch between the two configurations, use the 3-pin JP FB jumper.

The RRP51045 has an output voltage range of 0.5V to 2.075V using internal FB resistors and an output voltage range of 0.5V to 5.1V using traditional external FB resistors.

## 1.1.2 Internal Feedback Resistors and Output Voltage Set Pins

The evaluation board can use the internal FB resistors by shorting the device VOUT pins to SNS using the JP\_FB jumper (short pins 1 and 2).

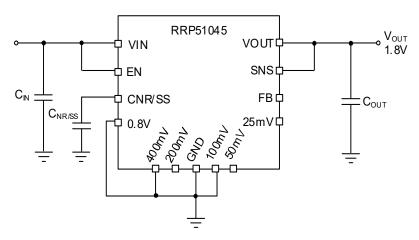

The output voltage set pins on the PCB are labeled 25mV, 50mV, 100mV, 200mV, 400mV, and 800mV. Grounding these pins adds the voltages assigned to each grounded pin to the reference voltage (V<sub>REF</sub>), and the total equals the required output voltage, as expressed in Equation 1. The V<sub>REF</sub> for the RRP51045 is 0.5V. The voltage set pins can be quickly grounded on the evaluation board using the J1 jumper.

(EQ. 1)

$$V_{OUT} = V_{RFF} + \Sigma$$

(Grounded Output Voltage Set Pins)

For example, to program the output voltage on the RRP51045 to 1.8V, ground the 100mV, 400mV, and 800mV pins using the J1 jumper. The sum of these three pins (1.3V) added to the 0.5V voltage reference gives 1.8V on the output of the LDO. The schematic in Figure 2 illustrates the proper connections.

Figure 2. RRP51045 Simplified Schematic Using the Internal FB Resistors (V<sub>OUT</sub> = 1.8V)

Table 1 provides a list of all the possible voltage set pin configurations and the corresponding output voltage for the RRP51045.

Table 1. Voltage Set Pin Configuration and Corresponding Output Voltages for RRP51045 ( $V_{REF} = 0.5V$ )

| V <sub>OUT</sub> (V) | 25mV | 50mV | 100mV | 200mV | 400mV | 800<br>mV | V <sub>OUT</sub> (V) | 25mV | 50mV | 100mV | 200mV | 400mV | 800<br>mV |

|----------------------|------|------|-------|-------|-------|-----------|----------------------|------|------|-------|-------|-------|-----------|

| 0.500                | Open | Open | Open  | Open  | Open  | Open      | 1.300                | Open | Open | Open  | Open  | Open  | GND       |

| 0.525                | GND  | Open | Open  | Open  | Open  | Open      | 1.325                | GND  | Open | Open  | Open  | Open  | GND       |

| 0.550                | Open | GND  | Open  | Open  | Open  | Open      | 1.350                | Open | GND  | Open  | Open  | Open  | GND       |

| 0.575                | GND  | GND  | Open  | Open  | Open  | Open      | 1.375                | GND  | GND  | Open  | Open  | Open  | GND       |

| 0.600                | Open | Open | GND   | Open  | Open  | Open      | 1.400                | Open | Open | GND   | Open  | Open  | GND       |

| 0.625                | GND  | Open | GND   | Open  | Open  | Open      | 1.425                | GND  | Open | GND   | Open  | Open  | GND       |

| 0.650                | Open | GND  | GND   | Open  | Open  | Open      | 1.450                | Open | GND  | GND   | Open  | Open  | GND       |

| 0.675                | GND  | GND  | GND   | Open  | Open  | Open      | 1.475                | GND  | GND  | GND   | Open  | Open  | GND       |

| 0.700                | Open | Open | Open  | GND   | Open  | Open      | 1.500                | Open | Open | Open  | GND   | Open  | GND       |

| 0.725                | GND  | Open | Open  | GND   | Open  | Open      | 1.525                | GND  | Open | Open  | GND   | Open  | GND       |

| 0.750                | Open | GND  | Open  | GND   | Open  | Open      | 1.550                | Open | GND  | Open  | GND   | Open  | GND       |

| 0.775                | GND  | GND  | Open  | GND   | Open  | Open      | 1.575                | GND  | GND  | Open  | GND   | Open  | GND       |

| 0.800                | Open | Open | GND   | GND   | Open  | Open      | 1.600                | Open | Open | GND   | GND   | Open  | GND       |

| 0.825                | GND  | Open | Open  | GND   | Open  | Open      | 1.625                | GND  | Open | GND   | GND   | Open  | GND       |

| 0.850                | Open | GND  | Open  | GND   | Open  | Open      | 1.650                | Open | GND  | GND   | GND   | Open  | GND       |

| 0.875                | GND  | GND  | Open  | GND   | Open  | Open      | 1.675                | GND  | GND  | GND   | GND   | Open  | GND       |

| 0.900                | Open | Open | Open  | Open  | GND   | Open      | 1.700                | Open | Open | Open  | Open  | GND   | GND       |

| 0.925                | GND  | Open | Open  | Open  | GND   | Open      | 1.725                | GND  | Open | Open  | Open  | GND   | GND       |

| 0.950                | Open | GND  | GND   | Open  | GND   | Open      | 1.750                | Open | GND  | Open  | Open  | GND   | GND       |

| 0.975                | GND  | GND  | GND   | Open  | GND   | Open      | 1.775                | GND  | GND  | Open  | Open  | GND   | GND       |

| 1.000                | Open | Open | GND   | GND   | GND   | Open      | 1.800                | Open | Open | GND   | Open  | GND   | GND       |

| 1.025                | GND  | Open | GND   | GND   | GND   | Open      | 1.825                | GND  | Open | GND   | Open  | GND   | GND       |

| 1.050                | Open | GND  | Open  | GND   | GND   | Open      | 1.850                | Open | GND  | GND   | Open  | GND   | GND       |

| 1.075                | GND  | GND  | Open  | GND   | GND   | Open      | 1.875                | GND  | GND  | GND   | Open  | GND   | GND       |

| 1.100                | Open | Open | Open  | Open  | GND   | Open      | 1.900                | Open | Open | Open  | GND   | GND   | GND       |

| 1.125                | GND  | Open | Open  | Open  | GND   | Open      | 1.925                | GND  | Open | Open  | GND   | GND   | GND       |

| 1.150                | Open | GND  | Open  | Open  | GND   | Open      | 1.950                | Open | GND  | Open  | GND   | GND   | GND       |

| 1.175                | GND  | GND  | GND   | Open  | GND   | Open      | 1.975                | GND  | GND  | Open  | GND   | GND   | GND       |

| 1.200                | Open | Open | GND   | GND   | GND   | Open      | 2.000                | Open | Open | GND   | GND   | GND   | GND       |

| 1.225                | GND  | Open | GND   | GND   | GND   | Open      | 2.025                | GND  | Open | GND   | GND   | GND   | GND       |

| 1.250                | Open | GND  | GND   | GND   | GND   | Open      | 2.050                | Open | GND  | GND   | GND   | GND   | GND       |

| 1.275                | GND  | GND  | Open  | GND   | GND   | Open      | 2.075                | GND  | GND  | GND   | GND   | GND   | GND       |

#### 1.1.3 External Feedback Resistors

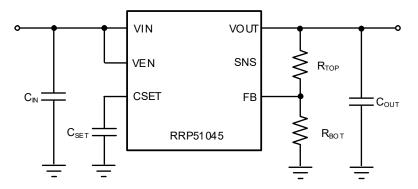

For applications with an output voltage exceeding 2.075V, use an external feedback resistor divider ( $R_{TOP}$  and  $R_{BOT}$ ) as shown in Figure 3. This layout extends the output voltage range up to 5.1V.

Figure 3. Simplified Schematic of LDO Using External FB resistors

The evaluation board can use external FB resistors by shorting the  $V_{OUT}$  to the top of  $R_{TOP}$  using the JP\_FB jumper (short pins 2 and 3).

$R_{BOT}$  can be easily calculated to program the output voltage by setting  $R_{TOP}$  to a required resistor value and solving Equation 2, where  $V_{OUT(TARGET)}$  is the ideal output voltage. The  $V_{REF}$  for RRP51045 is 0.5V.

(EQ. 2)

$$R_{BOT} = R_{TOP} \times \left( \frac{V_{REF}}{V_{OUT(TARGET)} - V_{REF}} \right)$$

Use Equation 3 to calculate the output voltage based on the  $R_{TOP}$  and  $R_{BOT}$  resistors.

(EQ. 3)

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

Table 2 provides a non-exhaustive list of recommended FB resistor values to obtain some common output voltages for RRP51045. The FB resistors are commercially available in 1% tolerances.

Table 2. Recommended FB Resistor Values for Common Output Voltages (V<sub>REF</sub> = 0.5V)

| V <sub>OUT(TARGET)</sub> (V) | R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | V <sub>OUT(CALCULATED)</sub> (V) | Accuracy |

|------------------------------|-----------------------|-----------------------|----------------------------------|----------|

| 0.5                          | 0                     | DNP                   | 0.500                            | 0.00%    |

| 0.6                          | 11.0                  | 54.9                  | 0.600                            | -0.03%   |

| 0.7                          | 10.2                  | 25.5                  | 0.700                            | 0.00%    |

| 0.75                         | 10.0                  | 20.0                  | 0.750                            | 0.00%    |

| 0.8                          | 10.7                  | 17.8                  | 0.801                            | -0.07%   |

| 0.9                          | 11.0                  | 13.7                  | 0.901                            | -0.16%   |

| 1                            | 12.4                  | 12.4                  | 1.000                            | 0.00%    |

| 1.05                         | 11.0                  | 10.0                  | 1.050                            | 0.00%    |

| 1.1                          | 10.7                  | 8.9                   | 1.103                            | -0.29%   |

| 1.2                          | 9.31                  | 6.7                   | 1.200                            | 0.00%    |

| 1.5                          | 12.4                  | 6.19                  | 1.502                            | -0.11%   |

Table 2. Recommended FB Resistor Values for Common Output Voltages (V<sub>REF</sub> = 0.5V) (Cont.)

| V <sub>OUT(TARGET)</sub> (V) | R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | V <sub>OUT(CALCULATED)</sub> (V) | Accuracy |

|------------------------------|-----------------------|-----------------------|----------------------------------|----------|

| 1.8                          | 10.2                  | 3.92                  | 1.801                            | -0.06%   |

| 1.9                          | 12.4                  | 4.42                  | 1.903                            | -0.14%   |

| 2.5                          | 12.4                  | 3.09                  | 2.506                            | -0.26%   |

| 3                            | 12.4                  | 2.49                  | 2.990                            | 0.33%    |

| 3.3                          | 10.7                  | 1.91                  | 3.301                            | -0.03%   |

| 3.6                          | 12.4                  | 2.00                  | 3.600                            | 0.00%    |

| 4.2                          | 12.1                  | 1.64                  | 4.189                            | 0.26%    |

| 4.5                          | 14.7                  | 1.84                  | 4.495                            | 0.12%    |

| 5                            | 12.4                  | 1.38                  | 4.993                            | 0.14%    |

| 5.1                          | 20.5                  | 2.23                  | 5.093                            | -0.09%   |

#### 1.1.4 **VBIAS**

If the input supply voltage ( $V_{IN}$ ) is less than 1.4V but greater than 1.1V, use a VBIAS voltage of 3V to 6.5V. If the input voltage exceeds 1.4V, the VBIAS pin does not have to be connected and can be left floating or shorted to GND.

#### 1.1.5 CNR/SS

Use a 1µF bypass capacitor between the CNR/SS pin and GND for optimal noise and ripple rejection performance. For LDO stability, a minimum capacitance of 100nF is required.

#### 1.1.6 VEN

The ENABLE feature of the LDOs can be exercised using the JP\_EN jumper. Short the VEN pin to VIN to automatically ENABLE the device when VIN is applied.

To DISABLE the LDO, connect the EN pin to GND.

To control the EN pin with a separate power supply, such as a function generator or logic signal from an MCU, remove the jumper from JP EN and connect the separate supply to the TP EN test point.

## 1.2 Recommended Equipment

- A VIN power supply to power up the LDO. The supply should be able to supply the load current the LDO needs to supply to its load.

- An EN power supply (such as a function generator, pulse generator, logic signal from an MCU, or a regular supply) to power EN. If not using an external EN power supply, tie EN to VIN for automatic enabling.

- A VBIAS power supply to power VBIAS for applications where V<sub>IN</sub> < 1.4V.</li>

- An electronic load or resistor load.

- Measurement equipment such as multimeters, oscilloscopes, and spectrum analyzers to evaluate the LDO.

### 1.3 Quick Start Guide

#### 1.3.1 Internal FB Resistor Configuration Start Guide

- 1. If not using an external supply on EN, skip step 6 and use the JP\_EN jumper to short EN to VIN for automatic enabling.

- 2. Use the JP\_FB jumper to short the SNS pin to VOUT.

- 3. Use jumpers to ground the required IC voltage set pins to obtain the required output voltage.

- 4. Twist the positive input lead and ground return lead from the input power supply together, forming a twisted pair power supply wire, keeping them as short as possible to minimize input inductance. Then, turn the supply off.

- 5. Connect the positive input lead of the VIN power supply to the VIN banana jack and the ground return lead to the GND IN banana jack.

- 6. (Optional) Connect the positive input lead of the VEN power supply to the TP\_EN and the ground lead to any input side GND, such as TP\_10. Turn the supply off.

- 7. (Optional) Connect the positive input lead of the VBIAS power supply to the VBIAS banana jack and the ground lead to the GND\_VBIAS banana jack. Turn the supply off.

- 8. Connect the electronic or resistor load between VOUT and GND. The positive lead should be connected to the VOUT banana jack, and the ground return lead should be connected to the GND OUT banana jack.

- 9. Power up all the necessary power supplies followed by the load (if using an electronic load).

- 10. Verify the output voltage with a voltmeter and/or oscilloscope.

#### 1.3.2 External FB Resistor Configuration Start Guide

- 1. If not using an external supply on EN, skip step 6 and use the JP\_EN jumper to short EN to VIN for automatic enabling.

- 2. Use the JP FB jumper to short the top of R TOP to the VOUT.

- 3. Populate the R\_TOP and R\_BOT resistor divider to obtain the required output voltage.

- 4. Twist the positive input lead and ground return lead from the input power supply together, keeping them as short as possible to minimize input inductance. Then, turn the supply off.

- 5. Connect the positive input lead of the VIN power supply to the VIN banana jack and the ground return lead to the GND\_IN banana jack.

- 6. (Optional) Connect the positive input lead of the VEN power supply to the TP\_EN and the ground lead to any input side GND, such as TP\_10. Turn the supply off.

- 7. (Optional) Connect the positive input lead of the VBIAS power supply to the VBIAS banana jack and the ground lead to the GND\_VBIAS banana jack. Turn the supply off.

- 8. Connect the electronic or resistor load between VOUT and GND. The positive lead should be connected to the VOUT banana jack, and the ground return lead should be connected to the GND\_OUT banana jack.

- 9. Power up all the necessary power supplies followed by the load (if using an electronic load).

- 10. Verify the output voltage with a voltmeter and/or oscilloscope.

# 2. Board Design

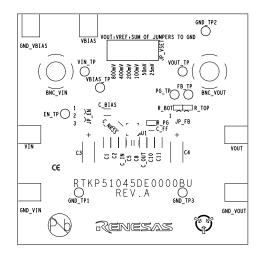

Figure 4. RTKP51045DE0000BU Evaluation Board (Top)

# 2.1 PCB Layout Guidelines

The following are recommendations for the PCB layout to achieve optimal LDO performance:

- Ensure the input and output capacitors have a good ground connection and place them as close to the IC as possible.

- The FB pin trace should be short, direct, and away from other noisy traces.

- Place them as close as possible to the IC if using external FB resistors.

- The package thermal EPAD is the largest heat conduction path for the package. Solder it to a copper pad on the PCB underneath the part. The PCB thermal pad should have as many plated vias as possible to increase the heat flow from the package thermal EPAD to the inner PCB areas and/or the bottom PCB area. Add thermal vias around the PCB package to help improve heat spread from the package to other board layers. Keep the vias small but not so small that their inside diameter prevents the solder from wicking through the holes during reflow. For efficient heat transfer, the vias must have low thermal resistance. Do not use thermal relief patterns to connect the vias. It is essential to have a complete connection of the plated through-hole to each plane. The top copper GND layer that the EPAD is connected to is the least thermally resistant path for heat flow. To this end, minimize the components and traces that cut this layer.

# 2.2 Schematic Diagrams

Figure 5. RTKP51045DE0000BU Schematic Diagram

## 2.3 Bill of Materials

| Qty | Reference<br>Designator            | Description                                                  | Manufacturer          | Manufacturer Part<br>Number |

|-----|------------------------------------|--------------------------------------------------------------|-----------------------|-----------------------------|

| 5   | C_BIAS, C_IN, C_OUT<br>C2, C10     | CAP, SMD, 0805, 10µF, 16V, 10%, X7R, RoHS                    | Samsung               | CL21B106KOQNNNE             |

| 2   | C1, C11                            | CAP, SMD, 0805, 47µF, 10V, 20%, X5R, RoHS                    | Murata                | GRM21BR61A476ME15           |

| 0   | C_FF                               | CAP, SMD, 0603, DNP-PLACE HOLDER, RoHS                       | -                     | -                           |

| 1   | C_NRSS                             | CAP, SMD, 0805,1µF, 16V, 10%, X7R, RoHS                      | Kemet                 | C0805C105K4RACTU            |

| 0   | C3, C4                             | CAP, SMD, 1206, DNP-PLACE HOLDER, RoHS                       | -                     | -                           |

| 0   | C5, C8                             | CAP, SMD, 0603, DNP-PLACE HOLDER, RoHS                       | -                     | -                           |

| 3   | VIN, VOUT, VBIAS                   | CONN-BANANA JACK, INSULATED, ORANGE, NYLON, RoHS             | Johnson<br>Components | 108-0906-001                |

| 3   | GND_VIN,<br>GND_VOUT,<br>GND_VBIAS | CONN-BANANA JACK, FE MALE, TH,<br>W/SOLDER TABS, BROWN, RoHS | Cinch                 | 108-0908-001                |

| 2   | BNC_VIN, BNC_VOUT                  | CONN-BNC, RECEPTACLE, TH, 4 POST, 50Ω, GOLDCONTACT, RoHS     | Amphenol              | 31-5329-52RFX               |

| 3   | VIN_TP, VOUT_TP,<br>VBIAS_TP       | CONN-MINI TEST PT, VERTICAL, RED, RoHS                       | Keystone              | 5000                        |

| 3   | GND_TP1-GND_TP3                    | CONN-MINI TEST PT, VERTICAL, BLK, RoHS                       | Keystone              | 5001                        |

| 3   | EN_TP, FB_TP, PG_TP                | CONN-MINI TEST POINT, VERTICAL, WHITE, RoHS                  | Keystone              | 5002                        |

| 1   | JP_VSET                            | CONN-HEADER, 2×6, BRKAWY-2×36, 2.54mm, RoHS                  | BERG/FCI              | 67996-272HLF                |

| Qty | Reference<br>Designator | Description                                           | Manufacturer | Manufacturer Part<br>Number |

|-----|-------------------------|-------------------------------------------------------|--------------|-----------------------------|

| 2   | JP_EN, JP_FB            | CONN-HEADER,1×3, BREAKAWY 1×36, 2.54mm, RoHS          | BERG/FCI     | 68000-236HLF                |

| 0   | R_BOT, R_TOP            | RESISTOR, SMD, 0603, 0.1%, MF, DNP-PLACE<br>HOLDER    | -            | -                           |

| 1   | R_PG                    | RES, SMD, 0603,10K, 1/10W, 1%, TF, RoHS               | Venkel       | CR0603-10W-1002FT           |

| 1   | U1                      | RRP51045 LDO, 20-QFN, Ultra Loise Noise High PSSR LDO | Renesas      | RRP51045GNP#HC0             |

# 2.4 Board Layout

Figure 6. Assembly Layer

Figure 8. Second Layer

Figure 7. Top Layer

Figure 9. Third Layer

Figure 10. Bottom Layer

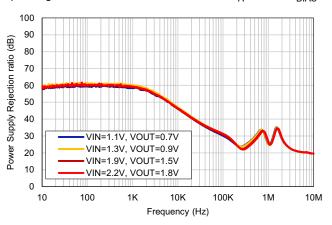

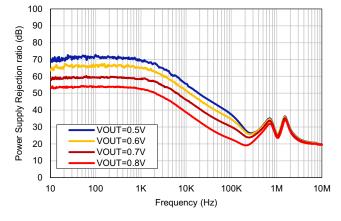

# 3. Typical Performance Graphs

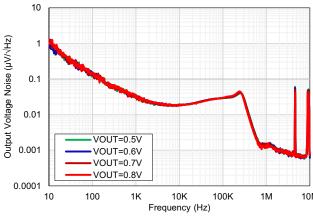

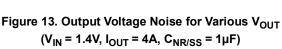

Operating conditions unless otherwise noted:  $T_A$  = 25°C,  $V_{BIAS}$  = open, and PG pulled up to  $V_{OUT}$  with  $10k\Omega$ .

Figure 11. PSRR vs Frequency for Various  $V_{OUT}$  ( $V_{IN}$  =  $V_{OUT}$  + 0.4V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 12. PSRR vs Frequency for Various  $V_{OUT}$  ( $V_{IN}$  = 1.1V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 14. Output Voltage Noise for Various  $V_{OUT}$ ( $V_{IN} = V_{OUT} + 0.3V$ ,  $I_{OUT} = 4A$ ,  $C_{NR/SS} = 1\mu F$ )

# 4. Ordering Information

| Part Number       | Description               |

|-------------------|---------------------------|

| RTKP51045DE0000BU | RRP51045 Evaluation Board |

# 5. Revision History

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.00     | Sep 3, 2024 | Initial release |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.