## PTX105R/RA2E1 Quick Connect (QC) Demo

This document describes how to use the PTX IoT Reader demo application with the Renesas [e<sup>2</sup> studio](#) and running it on the [Renesas EK-RA2E1](#) evaluation board with a [PTX105RQC](#) PMOD™ board.

## Contents

|                                                       |    |

|-------------------------------------------------------|----|

| 1. Introduction.....                                  | 2  |

| 2. Requirements.....                                  | 2  |

| 2.1 Hardware .....                                    | 2  |

| 2.2 Software .....                                    | 3  |

| 3. PTX105R Quick-Connect (QC) Board.....              | 3  |

| 4. EK-RA2E1 Evaluation Kit.....                       | 3  |

| 5. Hardware Setup .....                               | 4  |

| 6. IoT Reader Demo Application.....                   | 4  |

| 6.1 IoT Reader Demo Application Package.....          | 4  |

| 7. Running the Example Application.....               | 6  |

| 8. Using IoT Reader Library in a Custom Project ..... | 9  |

| 8.1 Integrating the Library in a Custom Project.....  | 10 |

| 8.2 Supported Architectures .....                     | 10 |

| 8.3 Platform-Specific Implementation.....             | 10 |

| 9. PTX105R QC Schematic.....                          | 11 |

| 10. Revision History .....                            | 11 |

## Figures

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Figure 1. PTX105RQC and EK-RA2E1 Boards .....                       | 2  |

| Figure 2. PTX105R Quick-Connect (QC) Board .....                    | 3  |

| Figure 3. Connecting the PTX105RQC and EK-RA2E1 Boards.....         | 4  |

| Figure 4. Software Package .....                                    | 4  |

| Figure 5. Application Flow Diagram.....                             | 5  |

| Figure 6. Application Output Example on the SEGGER RTT Viewer ..... | 5  |

| Figure 7. Import Projects Windows.....                              | 6  |

| Figure 8. Debug Configuration Windows .....                         | 7  |

| Figure 9. Application Startup Window.....                           | 8  |

| Figure 10. J-Link RTT Viewer Window .....                           | 8  |

| Figure 11. RTT Viewer Terminals Window .....                        | 9  |

| Figure 12. IoT-Reader SW Architecture .....                         | 10 |

| Figure 13. PTX105R-DB-RB QFN56-IOT QC Schematic.....                | 11 |

## 1. Introduction

This document describes the usage of the PTX IoT Reader demo application using e<sup>2</sup> studio and running it on the Renesas EK-RA2E1 evaluation board with a PTX105RQC board attached to the PMOD connector. For more information, see the [PTX105R NFC Reader Evaluation Kit and PMOD Demonstration](#) video.

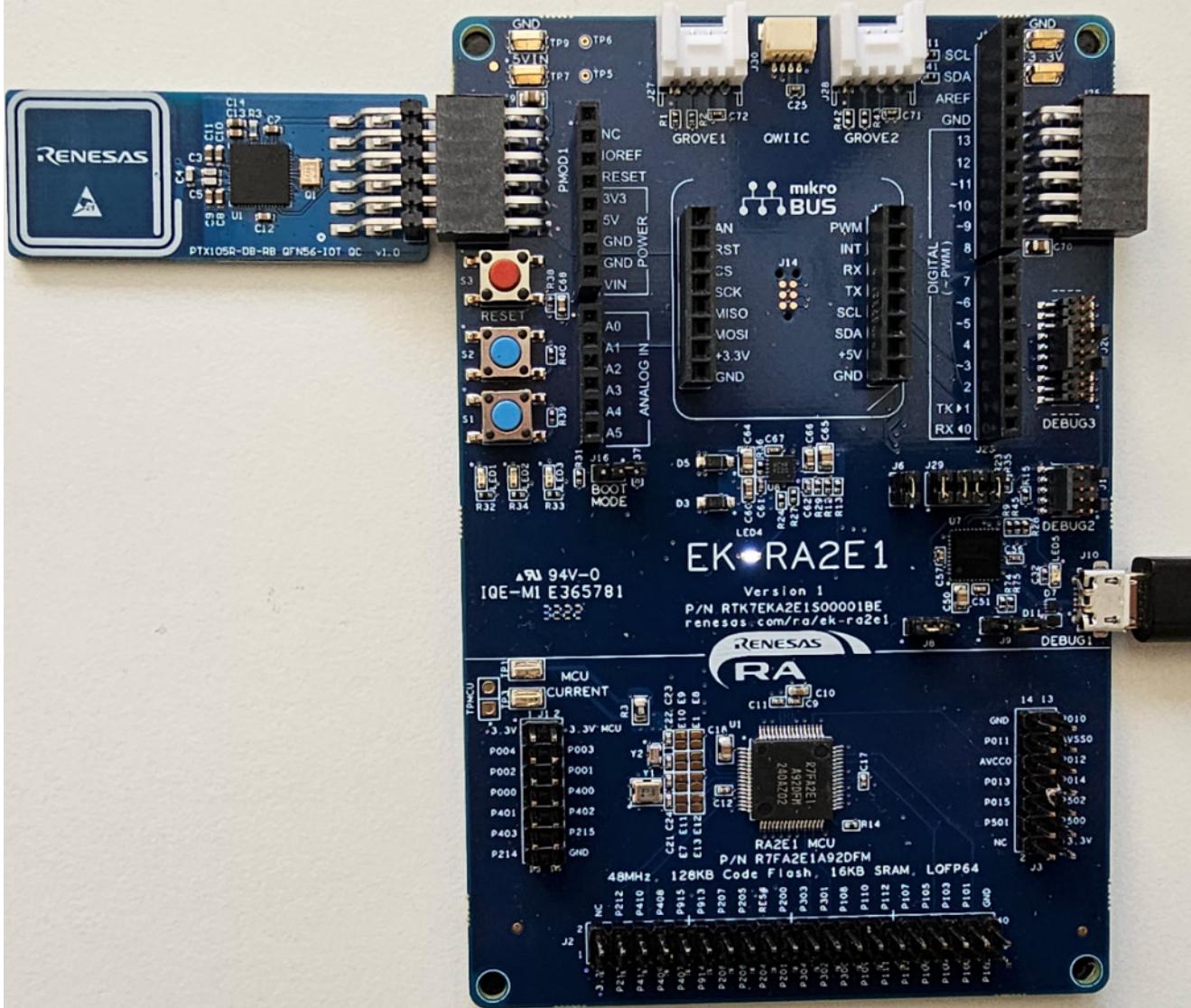

Figure 1. PTX105RQC and EK-RA2E1 Boards

## 2. Requirements

### 2.1 Hardware

- Renesas EK-RA2E1 (Evaluation Kit for RA2E1 MCU group)

- PTX105R Quick-Connect board

- Micro USB cable

## 2.2 Software

- Windows® 10 operating system

- [e2 Studio](#): Version 2025-01 or above

- [Flexible Software Package](#) FSP: Version 5.6.0 or above

- Toolchain GCC ARM Embedded (Version 13.3.1.arm-13-24)

- [SEGGER](#) J-Link® USB Serial Drivers

- [SEGGER](#) J-Link Real-Time Transfer (RTT) Viewer (virtual terminal emulation application). It is included in J-Link Software and Documentation Pack.

- [IoT-Reader \(Non-OS\) SDK v7.2.0](#)

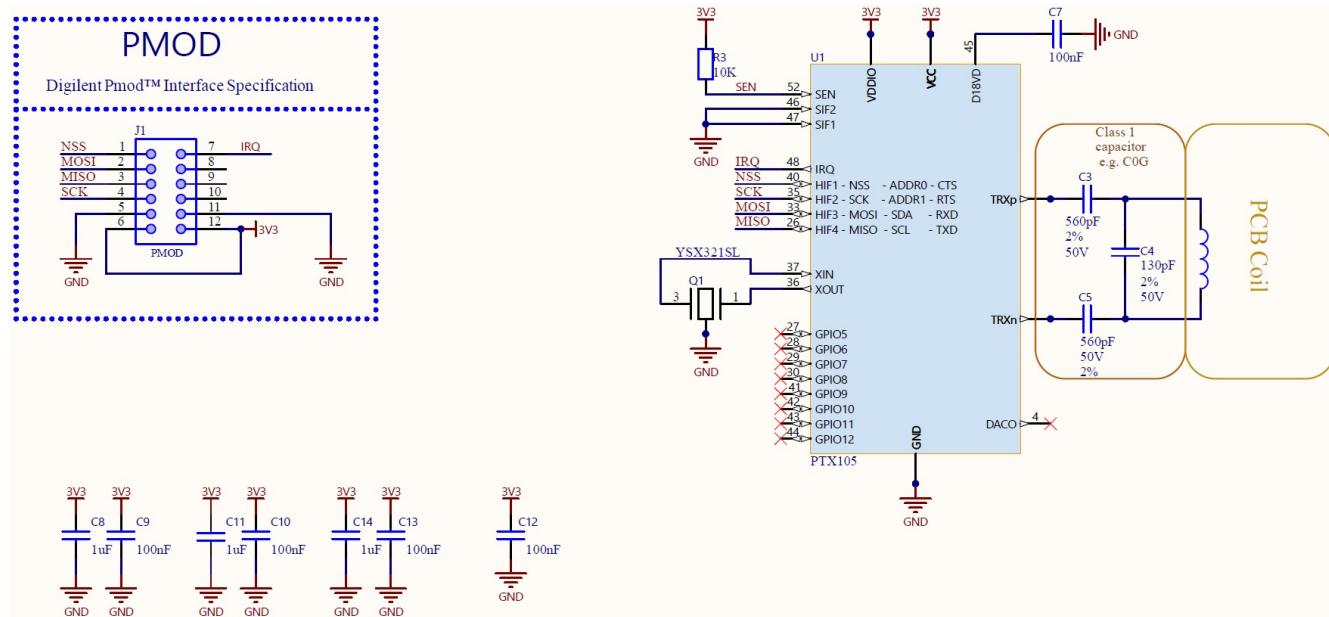

## 3. PTX105R Quick-Connect (QC) Board

The compact design of the PTX105R Quick-Connect board allows user's to add NFC functionality to their design.

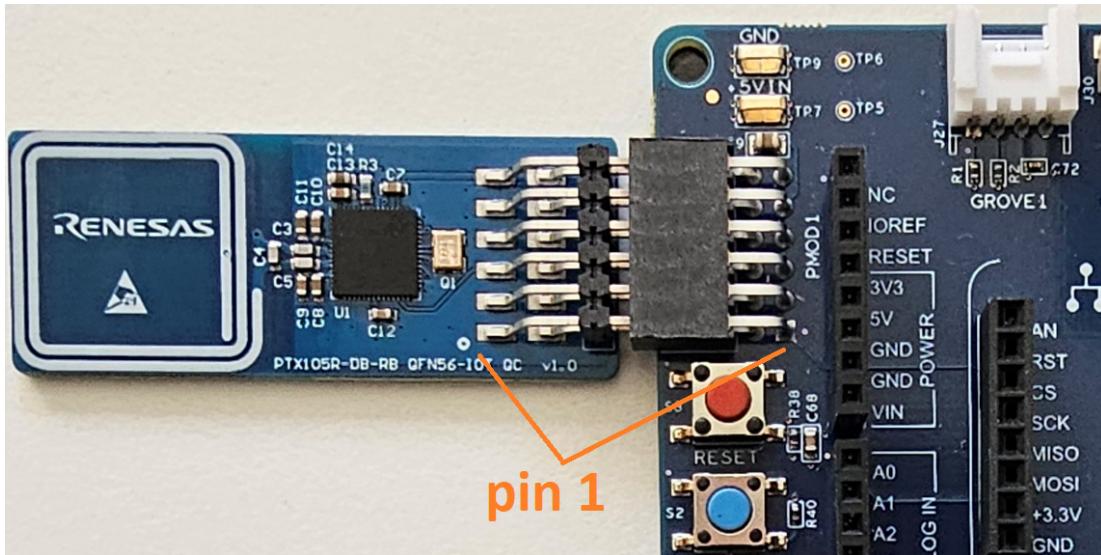

Figure 2. PTX105R Quick-Connect (QC) Board

The module contains a PTX105R chip with a  $20 \times 20$  mm loop antenna. The board can be connected directly to the Renesas EK-RA2E1 via the PMOD connector. The SPI and IRQ pins are used for the communication and the required operating current is drawn from the 3V3 pin.

A detailed schematic can be found in the [PTX105R QC Schematic](#) section.

## 4. EK-RA2E1 Evaluation Kit

For more information about the RA2E1 board and evaluation kit, visit the [EK-RA2E1](#) page.

## 5. Hardware Setup

1. Connect the PTX105R Quick-Connect board to the EK-RA2E1 PMOD1 connector (J26).

Figure 3. Connecting the PTX105RQC and EK-RA2E1 Boards

2. Plug in the micro-USB communication cable to the debugger USB connector (J10) on EK-RA2E1. When the cable is connected, the EK-RA2E1 board supplies the PTX105R Quick-Connect board with 3.3V.

## 6. IoT Reader Demo Application

The demo provides a reference implementation of an IoT-Reader with multiple card-type detection capabilities, running on a RA2E1 Arm Cortex®-M23 as an example host target platform.

### 6.1 IoT Reader Demo Application Package

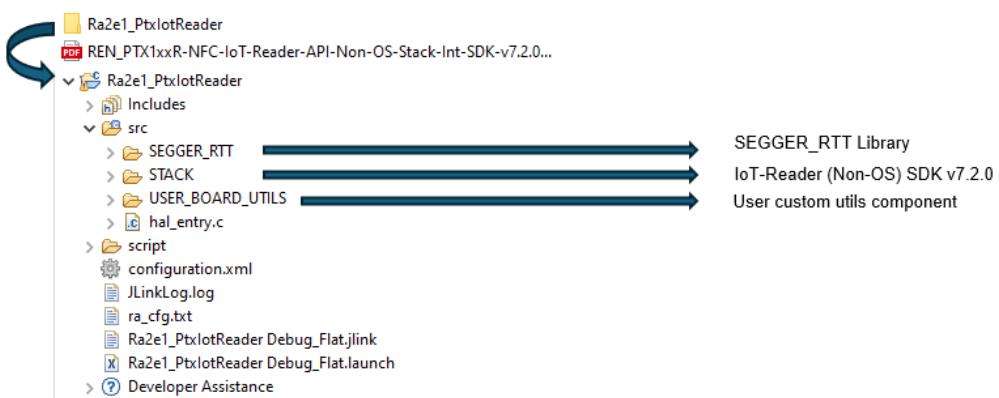

The delivered package contains the User Integration Manual for IoT-Reader (Non-OS) SDK v7.2.0 and the ready to use e<sup>2</sup> Studio project.

Figure 4. Software Package

This solution is intended for platforms without an operating system.

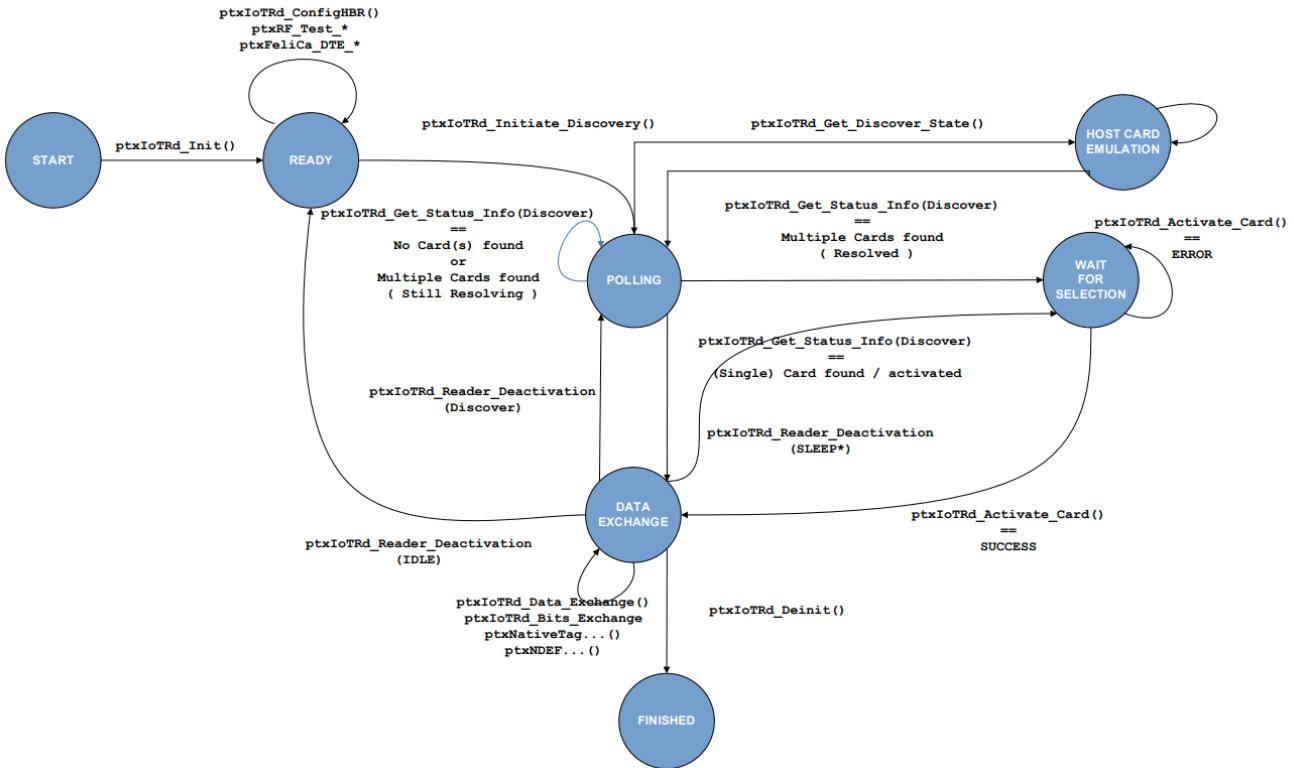

The application demonstrates the performance of the PTX105R for IoT applications and offers full support for all technologies: A, B, F, V type cards. It implements all steps required to initialize the PTX105R and to discover, activate, communicate, and deactivate a tag as described in [Figure 5](#).

Figure 5. Application Flow Diagram

The application starts automatically after the demo kit is powered up. When a card is detected, it performs example data exchange depending on the card type and protocol.

Figure 6 shows an example of the application output on the SEGGER RTT Viewer.

```

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-A; SENS_RES: 4400; NFCID1_LEN: 07; NFCID1: 0415913A36A120; SEL_RES: 00; Protocol: T2T

00> TX = 3000

00> RX = 041591083A36A1208D480000E1103E0000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

```

Figure 6. Application Output Example on the SEGGER RTT Viewer

When a card is placed in the field, the user LED 3 (red) is blinking indicating that there is an ongoing transaction.

## 7. Running the Example Application

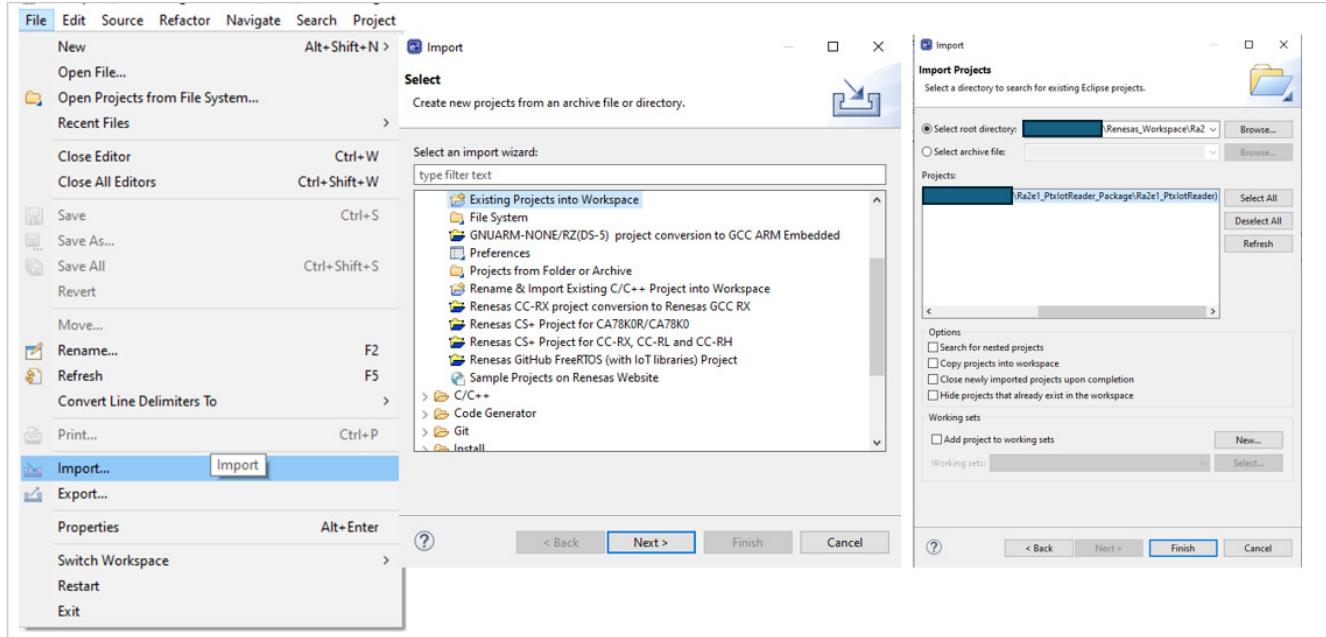

1. Click **File** → **Import** to import the project into the workspace.

Figure 7. Import Projects Windows

2. Build the project by clicking on **Project** → **Build Project** or using the keyboard shortcut **Ctrl+B**.

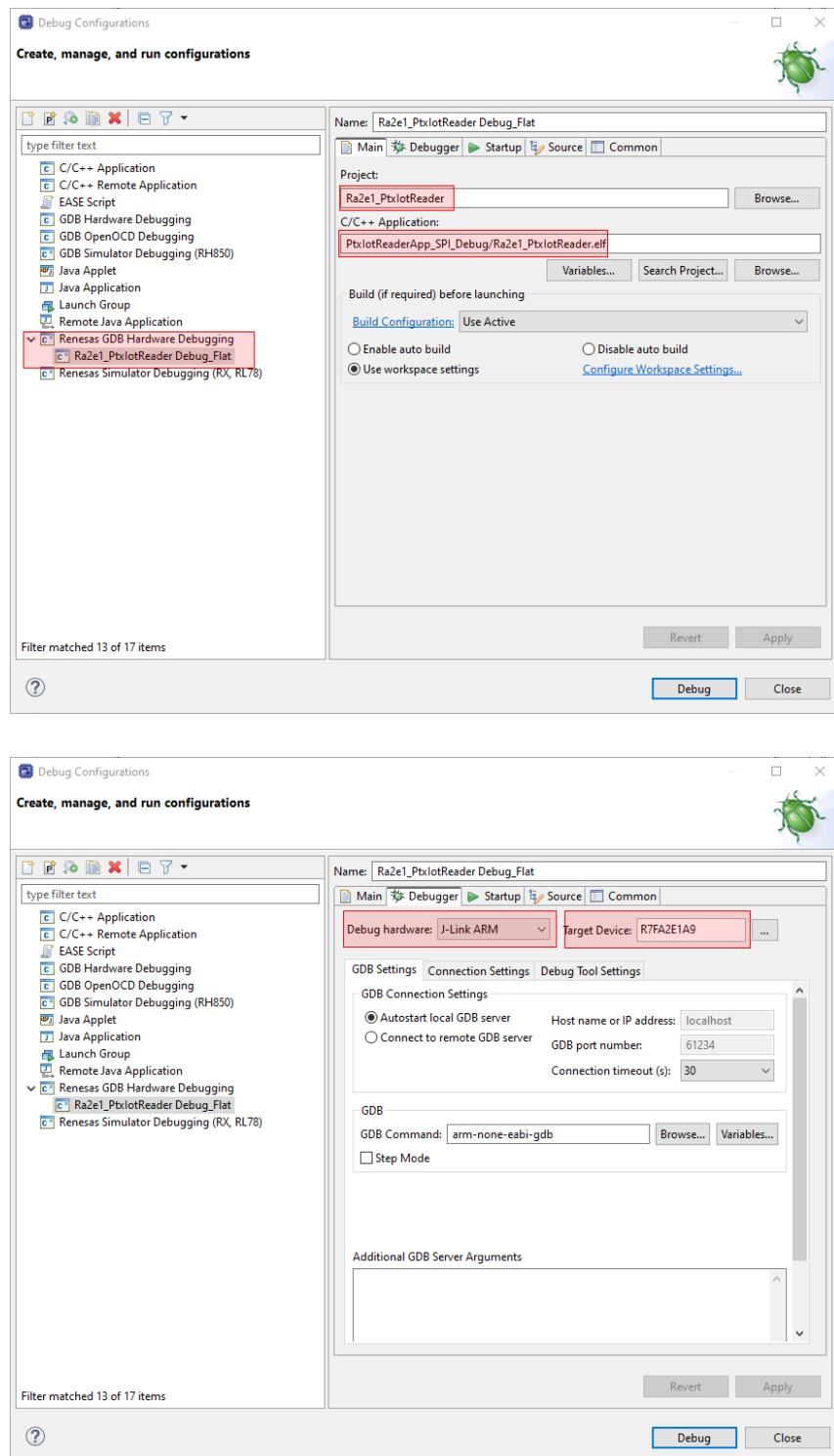

3. Flash the application. After plugging in the debug micro USB cable, go to **Run** → **Debug Configurations**, double-click on *Renesas GDB Hardware Debugging*, and setup the debugger (see [Figure 8](#)).

4. Click **Debug** to flash the application on the board.

## PTX105R/RA2E1 Quick Connect (QC) Demo Quick Start Guide

Figure 8. Debug Configuration Windows

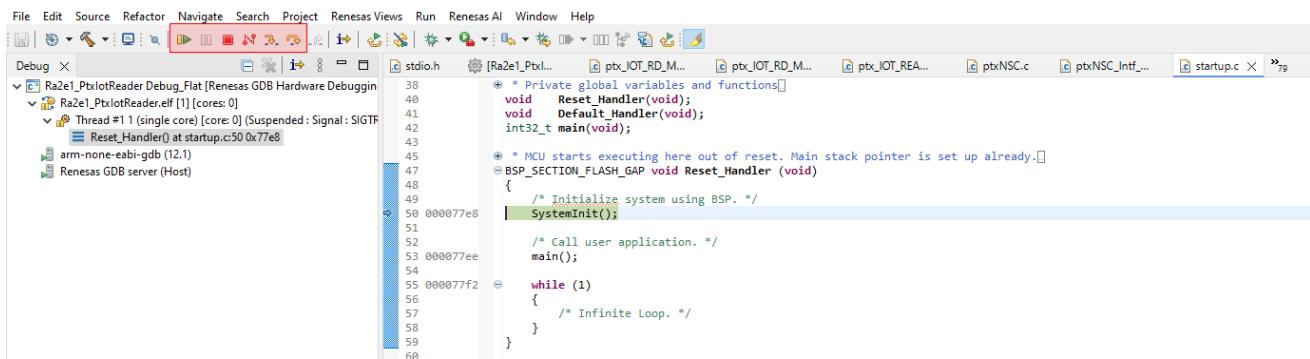

5. When completed, click **Resume** twice to start the application (see [Figure 9](#)).

## PTX105R/RA2E1 Quick Connect (QC) Demo Quick Start Guide

Figure 9. Application Startup Window

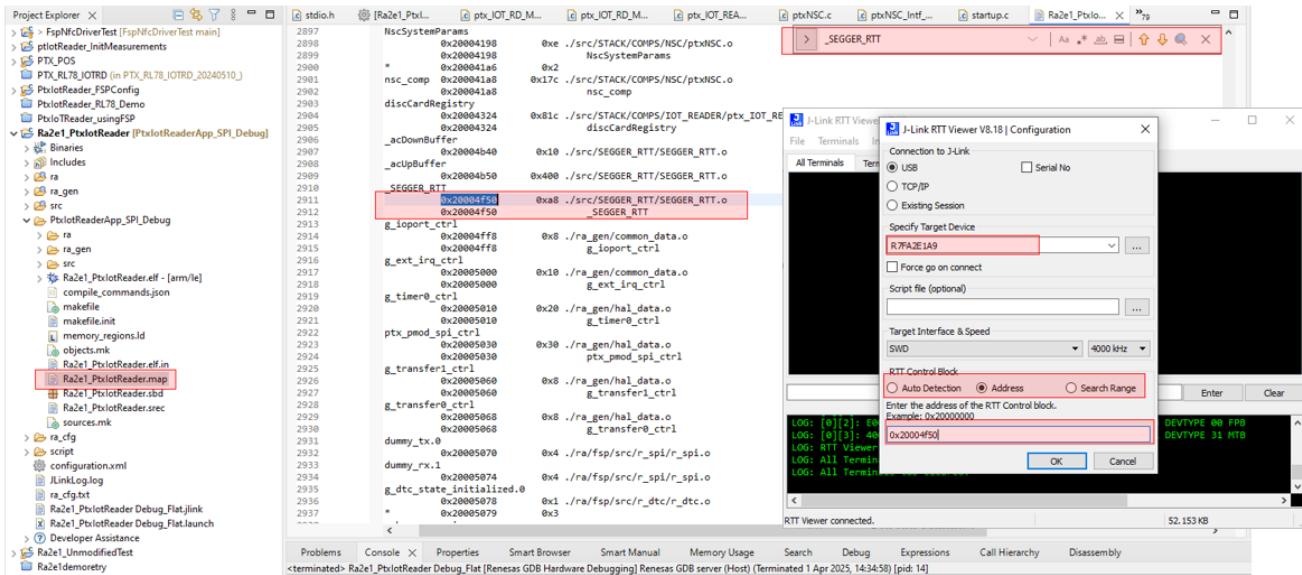

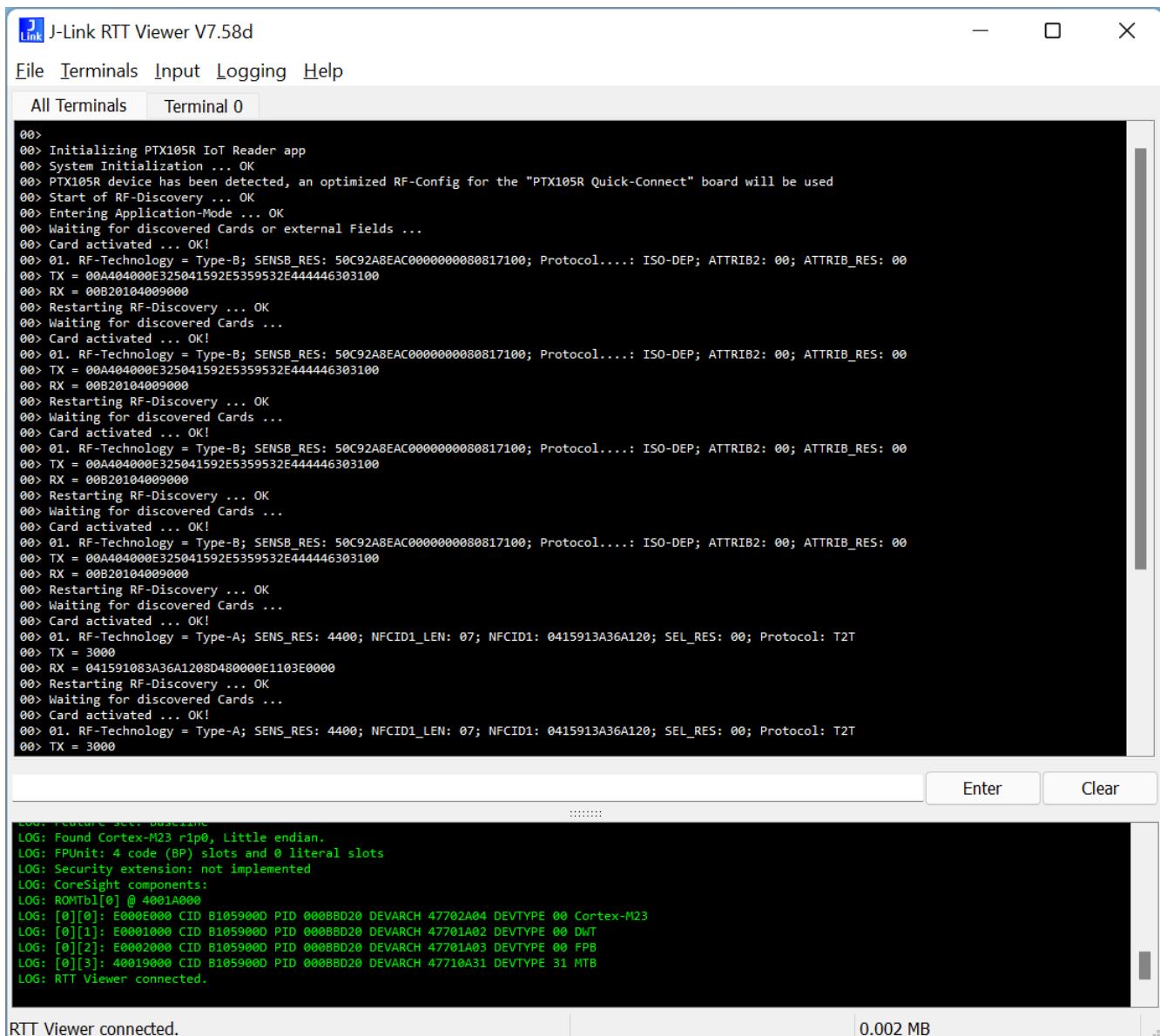

### 6. To view the application output, open the SEGGER RTT Viewer using device **R7FA2E1A9**.

When using Auto Detection option for the RTT Control Block, J-Link RTT Viewer may not be able to find the SEGGER\_RTT variable in RAM memory due to restrictions on memory access imposed by TrustZone settings made by the Renesas Device Partition Manager. Restrictions are typically applied for TrustZone Example Projects if the RTT Control Block cannot be found by RTT Viewer. This can result in the output from an Example Project not being visible in the RTT Viewer Console with Auto Detection.

The recommended approach is to search \_SEGGER\_RTT variable in the map file, generated upon successfully building a configuration of a Project, which is by default located in the address space for on-chip SRAM.

Figure 10. J-Link RTT Viewer Window

7. Once the SEGGER terminal is connected, the user can place a card in the field and view the terminal.

```

00> Initializing PTX105R IoT Reader app

00> System Initialization ... OK

00> PTX105R device has been detected, an optimized RF-Config for the "PTX105R Quick-Connect" board will be used

00> Start of RF-Discovery ... OK

00> Entering Application-Mode ... OK

00> Waiting for discovered Cards or external Fields ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-B; SENSB_RES: 50C92A8EAC000000080817100; Protocol....: ISO-DEP; ATTRIB2: 00; ATTRIB_RES: 00

00> TX = 00A404000E325041592E5359532E444446303100

00> RX = 00B20104009000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-B; SENSB_RES: 50C92A8EAC000000080817100; Protocol....: ISO-DEP; ATTRIB2: 00; ATTRIB_RES: 00

00> TX = 00A404000E325041592E5359532E444446303100

00> RX = 00B20104009000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-B; SENSB_RES: 50C92A8EAC000000080817100; Protocol....: ISO-DEP; ATTRIB2: 00; ATTRIB_RES: 00

00> TX = 00A404000E325041592E5359532E444446303100

00> RX = 00B20104009000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-B; SENSB_RES: 50C92A8EAC000000080817100; Protocol....: ISO-DEP; ATTRIB2: 00; ATTRIB_RES: 00

00> TX = 00A404000E325041592E5359532E444446303100

00> RX = 00B20104009000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-B; SENSB_RES: 50C92A8EAC000000080817100; Protocol....: ISO-DEP; ATTRIB2: 00; ATTRIB_RES: 00

00> TX = 00A404000E325041592E5359532E444446303100

00> RX = 00B20104009000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-A; SENSB_RES: 4400; NFCID1_LEN: 07; NFCID1: 0415913A36A120; SEL_RES: 00; Protocol: T2T

00> TX = 3000

00> RX = 041591083A36A1208D480000E1103E0000

00> Restarting RF-Discovery ... OK

00> Waiting for discovered Cards ...

00> Card activated ... OK!

00> 01. RF-Technology = Type-A; SENSB_RES: 4400; NFCID1_LEN: 07; NFCID1: 0415913A36A120; SEL_RES: 00; Protocol: T2T

00> TX = 3000

```

RTT Viewer connected. 0.002 MB

Figure 11. RTT Viewer Terminals Window

## 8. Using IoT Reader Library in a Custom Project

The PTX IoT Reader library provides an API for the following set of functions:

- Initialize the IOTRD API and NSC Stack

- Initialize the PTX105R chip

- Select a specific card in case multiple cards and/or protocols were discovered

- Retrieve card details like technical and/or activation parameters etc.

- Exchange RF-data and bitstreams

- Stop RF-communication

The complete list of available API's can be found in the project directory

**src/STACK/COMPS/IOT\_READER/ptx\_IOT\_READER.h**.

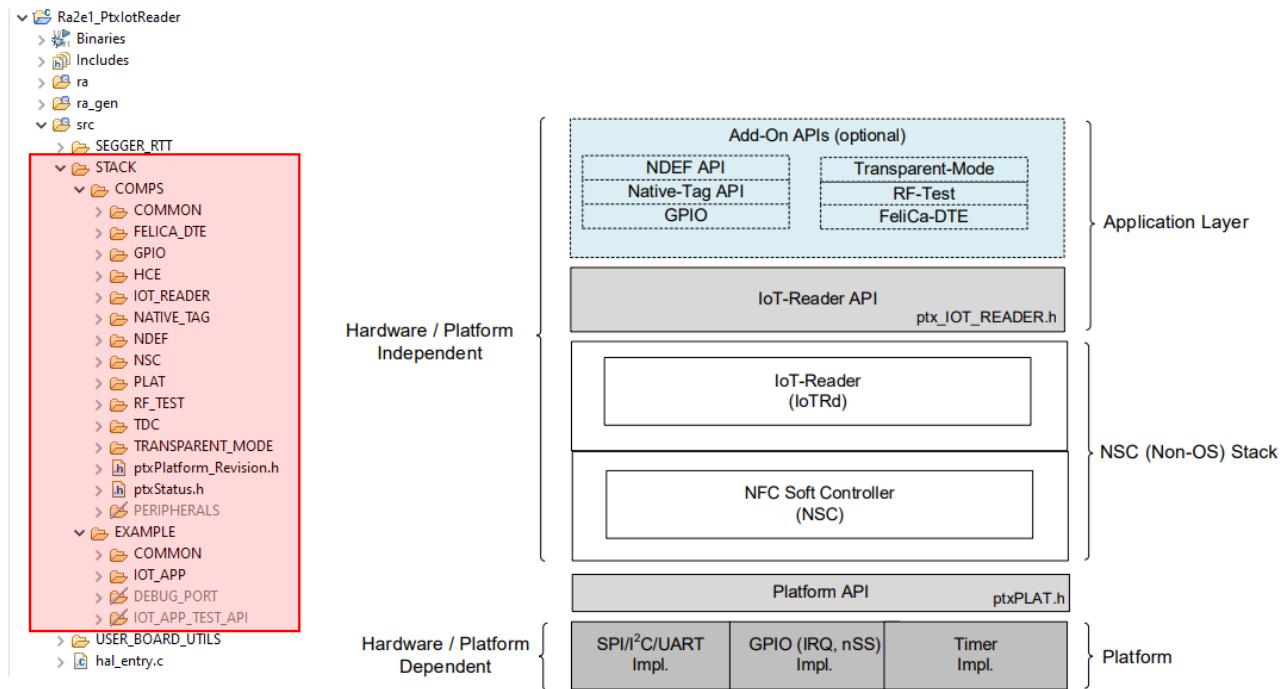

## 8.1 Integrating the Library in a Custom Project

Figure 12. IoT-Reader SW Architecture

The IoT-Reader (Non-OS) SDK V7.2.0 is a source code collection so it can be easily integrated in any custom project. From Software Architecture point of view, the “Platform” layer is the only Hardware specific Software Component, and it must be reimplemented by the user.

The IoT-Reader (Non-OS) SDK V7.2.0 provides a reference implementation for RA4M2 Family. For this Demo purpose the “Platform” layer was adapted for EK-RA2E1 board with minimal effort.

## 8.2 Supported Architectures

Although the EK-RA2M1 platform is an ARM Cortex®-M23, IoT-Reader (Non-OS) SDK V7.2.0 being delivered as source code collection makes it independent of the target architecture.

If the user encounters any kind of incompatibility due to platform architecture or Toolchain support can be requested by contacting Renesas [technical support](#).

## 8.3 Platform-Specific Implementation

As the SDK is common for all implementations, it must not use any hardware-dependent resources. The PLAT module can be used to define the interface functions to be implemented by the user. The required function declarations can be found in `ptxPLAT.h`. These functions must be individually implemented for the actual hardware.

The `ptxPLAT.c` code contains the basic low-level functions that the library uses for allocating memory area for objects, initializing and controlling timers, doing communication across SPI, etc.

The RA2E1 platform-specific implementation is located in `ptxPLAT.c`, but with the Renesas FSP platform API, the implementation is compatible with any variant of an RA family MCU. In this case, the device pin assignment might be the only configuration that needs to be adjusted.

## 9. PTX105R QC Schematic

Figure 13. PTX105R-DB-RB QFN56-IOT QC Schematic

## 10. Revision History

| Revision | Date         | Description                                                                                                                                                                                                           |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.01     | Apr 03, 2025 | <ul style="list-style-type: none"> <li>Updated e<sup>2</sup> Studio and FSP versions</li> <li>Updated content and figures based on new software package release (sections 2.2, 6, 6.1, 7, 8, 8.1, and 8.2)</li> </ul> |

| 1.00     | Sep 25, 2024 | Initial release.                                                                                                                                                                                                      |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).