#### ISL71148SLH

Single Event Effects (SEE) Testing of the ISL71148SLH 8-Channel 14-Bit 900/480ksps SAR ADC

#### Introduction

The intense proton and heavy-ion environment encountered in space can cause a variety of Single Event Effects (SEE) in electronic circuitry, including Single Event Upset (SEU), Single Event Transient (SET), Single Event Functional Interrupt (SEFI), Single Event Latch-Up (SEL), Single Event Gate Rupture (SEGR), and Single Event Burnout (SEB). SEE can lead to system-level performance issues such as disruption, degradation, and destruction. Individual electronic components should be characterized for predictable and reliable space system operation to determine their SEE response. This report discusses the results of SEE testing performed on the ISL71148SLH product. The device is offered with radiation assurance screening to 75krad(Si) at 10mrad(Si)/s.

#### **SEE Summary**

The ISL71148SLH proved to be free of Destructive Single Event Effects (DSEE) including SEL at supply voltages up to AV<sub>CC</sub> = 6.2V, DV<sub>CC</sub> = 4.6V, and V<sub>REF</sub> = 3.6V with a die temperature of 125°C when irradiated with normal incidence gold for a Linear Energy Transfer (LET) of  $86\text{MeV}\cdot\text{cm}^2/\text{mg}$ . These voltages are above the operating condition maximum values to provide an additional margin for end applications. During DSEE testing, the devices were exposed to a total fluence of  $5\times10^6\text{ion/cm}^2$ .

The SET testing was performed under irradiation with normal incidence gold (86MeV·cm²/mg), silver (46MeV·cm²/mg), argon (8.6MeV·cm²/mg), and neon (2.7MeV·cm²/mg). The ISL71148SLH experienced SET events, which were defined in two ways.

- The first type of SET was defined as any CH1 ADC code that was recorded outside a ±20 code window range from its median code. No observed SETs lasted longer than three samples. The data shows that out of all SETs observed under a gold, silver, argon, and neon heavy ion exposure, 79.3%, 83.5%, 89.4%, and 96.7% were less than 100 codes in magnitude, respectively.

- The second type of SET was defined as a channel information bit error. The ISL71148SLH sequences through all eight channels from 0 to 7 in repeating order. If a channel was improperly selected, this would indicate a channel information bit SET. There were a total of 16 SETs recorded under a gold and silver heavy ion exposure and there were no SETs recorded under a argon or neon heavy ion exposure.

A SEFI was defined as a SET that needed user intervention to recover its normal operation. No SEFIs were recorded for this device.

During all SET testing, the devices were exposed to a total fluence of 2x10<sup>6</sup>ion/cm<sup>2</sup> and a sufficient number of devices under test (DUTs) were used to keep the cumulative dose to under 8.88krad(Si). Previous tests on precision SAR ADCs on this process node showed that SET errors start to quench as the effective total dose is increased.

## **Part Description**

The ISL71148SLH is a radiation hardened 8-channel high-precision 14-bit, 900/480ksps SAR Analog-to-Digital Converter (ADC) that operates from -55°C to +125°C and is available in a 48 Ld TQFP. The ADC core is preceded by 8 fully differential analog input channels, followed by a buffered 8 to 1 multiplexer and a PGA (Programmable Gain Amplifier). The device features a peak SNR of 83.2dBFS when operating at 900ksps. With the PGA enabled, sampling rates up to 480ksps are supported. The PGA can be bypassed to increase the sample rate to 900ksps.

The product features 900/480ksps throughput with no data latency and features excellent linearity and dynamic accuracy. The ISL71148SLH offers a high-speed SPI-compatible serial interface that supports logic ranging from 2.2V to 3.6V using a separate digital I/O supply pin. Moreover, it offers a separate low-power mode (LPM) pin that reduces power dissipation at lower sample rates. An external reference applied to the  $V_{REF}$  pin with a supported input range of 2.4V to 2.6V determines the analog input signal range.

### **ISL71148SLH SEE Test Report**

# **Contents**

| 1. | SEE Testing                | 3    |

|----|----------------------------|------|

|    | .1 Objective               | 3    |

|    | .2 Facility                | 3    |

|    | .3 Setup                   | 3    |

| 2. | Results                    | 5    |

|    | 2.1 DSEE Results           | 5    |

|    | 2.2 SET Results            | 6    |

| 3. | SET Mitigation Options     | . 16 |

| 4. | Discussion and Conclusions | . 16 |

| 5. | Revision History           | . 16 |

## 1. SEE Testing

### 1.1 Objective

The testing was intended to find the limits for the supply voltages set by the onset of Destructive Single Event Effects (DSEE) at a LET of 86MeV·cm²/mg (normal incidence gold). Additional testing was intended to identify and quantify SETs and SEFIs occurring in the output sample codes of the ISL71148SLH. The SET studies included irradiation with normal incidence gold (86MeV·cm²/mg), silver (46MeV·cm²/mg), argon (8.6MeV·cm²/mg), and neon (2.7MeV·cm²/mg).

### 1.2 Facility

SEE testing was done at the Texas A&M University (TAMU) Radiation Effects Facility of the Cyclotron Institute in College Station, Texas. This facility is coupled to a K500 superconducting cyclotron that can supply a wide range of ion species and flux. The SEE testing was performed in September of 2023. The devices tested were drawn from lot F6W628.

### 1.3 Setup

The ISL71148SLH was SEE evaluated using a general-purpose engineering evaluation board that allowed various application configurations to be used. External power supplies provided ±10V to the evaluation board. The specific configurations changed with the type of testing. For DSEE testing, the individual supply voltages for analog input, AV<sub>CC</sub>, DV<sub>CC</sub>, and V<sub>REF</sub> were driven directly from an external power supply with currents monitored using an ammeter. External power supplies provided AV<sub>CC</sub> and DV<sub>CC</sub> voltages for the SET testing, while all other board voltages were provided from the onboard LDOs and precision voltage references. The onboard LDOs kept noise to a minimum and allowed for fine resolution of SET detection.

For the DSEE testing, the ADC input clock was set to a 900.901ksps sampling rate with the PGA bypassed. AV $_{CC}$  was increased in 0.1V steps until a DSEE was observed or 6.5V was reached. DV $_{CC}$  was set to 4.6V and V $_{REF}$  to 3.6V. The maximum sampling rate and voltages were used for AV $_{CC}$ , DV $_{CC}$ , and V $_{REF}$  to achieve the worst-case conditions. The monitored parameters for the ADC are listed in Table 1.

| Parameter Monitored             | Failure Criteria |

|---------------------------------|------------------|

| AV <sub>CC</sub> Supply Current | ±10%             |

| DV <sub>CC</sub> Supply Current | ±10%             |

| V <sub>REF</sub> Supply Current | ±10%             |

Table 1. Monitored Parameters and Failure Criteria for DSEE Testing

The ISL71148SLH was tested under five conditions for SET testing as given in Table 4. The ISL71148SLH has a normal mode and a low-power mode. In each mode, the PGA can be enabled or bypassed. These configurations result in four possible test modes. The fifth test mode is achieved by enabling the SCAN function of the ISL71148SLH. The SCAN function sequences through selecting the eight input channels, beginning with Channel 0 and ending with Channel 7. As long as the ISL71148SLH SCAN function is enabled, it sequentially cycles through the selection of channels. When operating in the fifth test mode, the ISL71148SLH is in normal mode, with the PGA bypassed to achieve the maximum sampling rate. Additional clocks on SDO were provided for the information bits (info bits). For configurations in which the PGA was bypassed, additional clocks were provided only for the channel info bits, but when the PGA was enabled, additional clocks were provided for the channel and gain info bits. For all SET tests, AV<sub>CC</sub> supply was set to 4.5V, DV<sub>CC</sub> was set to 2.5V, and V<sub>REF</sub> was set to 2.5V. The AV<sub>CC</sub> voltage corresponds to the minimum voltage required for the ISL71148SLH. The ISL71148SLH was operated at the maximum sampling rate for each given mode.

For all five test configurations, an onboard DAC (digital to analog converter) was used to drive Channels 0 and 2 through 7 to independent values across the range of the ISL71148SLH. The onboard amplifier driver circuit provided a DC input to Channel 1. In the first four configurations where SCAN was not enabled, Channel 1 was the observed channel. All other channels were driven to independent values different from Channel 1. The input conditions for all eight channels are summarized in Table 2.

Table 2. Channel Input Differential Voltages and Input Sources for SET Testing

| ADC ± Channel | Input Voltage | Differential Input Voltage (V) | Input Source       |

|---------------|---------------|--------------------------------|--------------------|

| +0            | 0             | -2.4                           | DAC                |

| -0            | 2.4           | -2.4                           | DAC                |

| +1            | 1.25          | 0                              | Amp Driver Circuit |

| -1            | 1.25          |                                | Amp Driver Circuit |

| +2            | 0             | -1.4                           | DAC                |

| -2            | 1.4           | -1.4                           | DAC                |

| +3            | 0             | -0.7                           | DAC                |

| -3            | 0.7           | -0.7                           | DAC                |

| +4            | 0.7           | 0.7                            | DAC                |

| -4            | 0             | 0.7                            | DAC                |

| +5            | 1.2           | 4.0                            | DAG                |

| -5            | 0             | 1.2                            | DAC                |

| +6            | 1.8           | 4.0                            | DAC                |

| -6            | 0             | 1.8                            | DAC                |

| +7            | 2.4           | 2.4                            | DAC                |

| -7            | 0             | 2.4                            | DAC                |

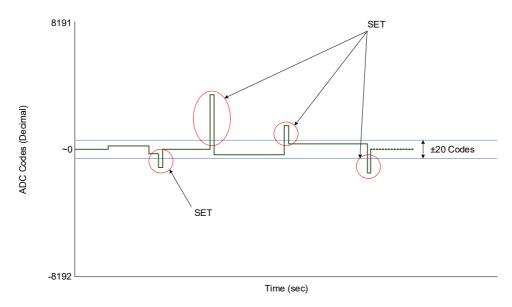

The ISL71148SLH evaluation board contains a Complex Programmable Logic Device (CPLD), which takes the serial output data from the ADC and converts it into parallel data. This data is inputted to a logic analyzer, where it is observed for SETs. Figure 1 shows the SET detection threshold that is configured for Channel 1 inside the logic analyzer.

The ADC input was set to approximately midscale using an amplifier circuit on the ISL71148SLH engineering evaluation board driving the ADC analog input. Setting the ADC analog input to a mid-scale value enables the observation of positive and negative excursions in the output codes of the ISL71148SLH. For every run, the median code for Channel 1 was used to set the ±20 code threshold window while the other seven channels were logged so that they could be used when post-processing the SET data. If the output code of the ADC went beyond the specified threshold, it was counted as a SET. Moreover, the recorded median codes for all channels determined if a channel was improperly selected. In addition, the channel information bits were also monitored to determine if the SET occurred on the channel bits or data bits. If a SET occurs by a wrong channel selection, the improperly selected channel can be identified by the value of the output code. The ±20 code threshold was found by operating the ISL71148SLH and observing no output code excursion beyond the threshold with no beam at the TAMU facility.

Figure 1. SET Detection Threshold

### 2. Results

#### 2.1 DSEE Results

DSEE testing of the ISL71148SLH was performed on four parts in September 2023.

DSEE of the ISL71148SLH was tested with normal incidence gold for  $86\text{MeV}\cdot\text{cm}^2/\text{mg}$  at a die temperature of  $125^{\circ}\text{C}\ \pm 10^{\circ}\text{C}$  with  $DV_{CC}$  and  $V_{REF}$ , held constant at maximum values of 4.6V and 3.6V, respectively.  $AV_{CC}$  was initially set to 6.2V and increased in 0.1V steps until DSEE was observed. The ISL71148SLH was set to normal operating mode with the PGA bypassed and the sample rate set to 900.901ksps. Before, during, and after irradiation, three parameters (Table 1) were monitored to check for signs of DSEE. The results of this testing for the ISL71148SLH are presented in Table 3. Failures to the  $\pm 10\%$  delta criteria for the supply currents are indicated with red text.

|     |                      |             | I <sub>AVCC</sub> |              |             | I <sub>DVCC</sub> |              |             | I <sub>REF</sub> |              |

|-----|----------------------|-------------|-------------------|--------------|-------------|-------------------|--------------|-------------|------------------|--------------|

| DUT | AV <sub>CC</sub> (V) | Pre<br>(mA) | Post<br>(mA)      | Delta<br>(%) | Pre<br>(mA) | Post<br>(mA)      | Delta<br>(%) | Pre<br>(μA) | Post<br>(μA)     | Delta<br>(%) |

|     | 6.2                  | 25.00       | 25.05             | 0.17         | 3.89        | 3.88              | 0            | 94.7        | 97.5             | 2.87         |

| 1   | 6.3                  | 25.48       | 25.48             | -0.01        | 3.88        | 3.88              | 0            | 97.4        | 98.25            | 0.87         |

| 1   | 6.4                  | 25.92       | 25.93             | 0.05         | 3.88        | 3.88              | 0            | 98.1        | 100.1            | 2.00         |

|     | 6.5                  | 26.379      | 49.40             | 46.60        | 3.88        | 3.88              | 0            | 101.5       | 101.7            | 0.20         |

|     | 6.2                  | 20.69       | 20.72             | 0.14         | 3.69        | 3.41              | -8.22        | 39.5        | 39.4             | -0.25        |

| 2   | 6.3                  | 21.15       | 21.14             | -0.02        | 3.51        | 3.78              | 7.09         | 38.3        | 38.9             | 1.54         |

| 2   | 6.4                  | 21.5        | 21.65             | 0.69         | 4.00        | 3.03              | -32.24       | 36          | 36.8             | 2.17         |

|     | 6.5                  | 22.1        | 69.79             | 68.33        | 3.52        | 4.53              | 22.33        | 35          | 21               | -66.67       |

| 3   | 6.2                  | 21.52       | 21.51             | -0.05        | 3.84        | 3.84              | 0.00         | 59.9        | 60.5             | 0.99         |

|     | 6.3                  | 21.87       | 66.5              | 67.12        | 3.84        | 3.83              | -0.26        | 60.4        | 55.7             | -8.44        |

Table 3. DSEE Testing Results for LET = 86MeV·cm<sup>2</sup>/mg [1]

|     |                      |             | I <sub>AVCC</sub> |              |             | I <sub>DVCC</sub> |              |             | I <sub>REF</sub> |              |

|-----|----------------------|-------------|-------------------|--------------|-------------|-------------------|--------------|-------------|------------------|--------------|

| DUT | AV <sub>CC</sub> (V) | Pre<br>(mA) | Post<br>(mA)      | Delta<br>(%) | Pre<br>(mA) | Post<br>(mA)      | Delta<br>(%) | Pre<br>(µA) | Post<br>(μA)     | Delta<br>(%) |

| 1   | 6.2                  | 21          | 20.997            | -0.02        | 1.55        | 1.55              | -0.06        | 45.7        | 44.6             | -2.47        |

| 4   | 6.3                  | 21.35       | 21.35             | 0.00         | 2.32        | 1.60              | -45.05       | 43.3        | 43.7             | 0.92         |

Table 3. DSEE Testing Results for LET = 86MeV·cm<sup>2</sup>/mg [1] (Cont.)

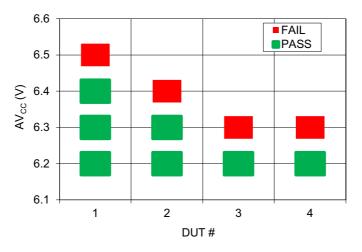

Two devices failed at  $AV_{CC} = 6.3V$  by violating the conditions in Table 1 for  $AV_{CC}$  and  $DV_{CC}$  current. All devices passed at  $AV_{CC} = 6.2V$ ,  $DV_{CC} = 4.6V$ , and  $V_{REF} = 3.6V$ .

Figure 2. DSEE Pass/Fail Summary

#### 2.2 SET Results

Single event transient testing was performed on the ISL71148SLH under the conditions listed in Table 4. The sequence in which these conditions were implemented was alternated from one DUT to the next in the order of 1-2, then 2-1 for normal mode tests and 3-4, then 4-3 for low power mode tests. The alternating order of the tests in normal and low power modes was implemented to detect any potential dependency on cumulative dose effects. Test condition #5 was specifically implemented to verify the channel sequencer of the ISL71148SLH, which is enabled by asserting the SCAN pin and was treated separately from modes 1 through 4. In SCAN mode, the ISL71148SLH sequences through all eight channels from 0 to 7 in repeating order. If a channel was improperly selected, this would indicate a channel information bit SET. For example, a sequence with a SET in the info bits might look like this: 0-1-2-6-4-5-6-7. This shows that the info bits were out of sequence for one sample, but that the overall sequence would still rotate through all eight channels correctly outside of the one sample where the info bits were incorrect. The sample rate of the ISL71148SLH changes depending on the operating mode and the state of the PGA. When the PGA is enabled, an additional 1 $\mu$ s of sampling time is needed, and when LPM is enabled, the CSB pulse width must be increased from 150ns to 500ns. The sample rate for each operating mode is shown in Table 4. To detect potential AV<sub>CC</sub> voltage-related or sample rate-related issues, the ISL71148SLH was tested at the minimum analog supply voltage of AV<sub>CC</sub> = 4.5V.

<sup>1.</sup> Each entry represents change across an irradiation of 2x10<sup>6</sup>ion/cm<sup>2</sup>.

**Table 4. SET Test Conditions**

|                  | Test Condition #1 | Test Condition #2 | Test Condition #3 | Test Condition #4 | Test Condition #5 |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| AV <sub>CC</sub> | 4.5V              | 4.5V              | 4.5V              | 4.5V              | 4.5V              |

| DV <sub>CC</sub> | 2.5V              | 2.5V              | 2.5V              | 2.5V              | 2.5V              |

| V <sub>REF</sub> | 2.5V              | 2.5V              | 2.5V              | 2.5V              | 2.5V              |

| Operating Mode   | Normal            | Normal            | Low Power         | Low Power         | Normal            |

| PGA Mode         | Enabled           | Bypassed          | Enabled           | Bypassed          | Bypassed          |

| SCAN             | Disabled          | Disabled          | Disabled          | Disabled          | Enabled           |

| Sample Rate      | 456.621ksps       | 900.901ksps       | 393.701ksps       | 684.932ksps       | 900.901ksps       |

| Input Channel    | 1                 | 1                 | 1                 | 1                 | 0-7               |

The results from previous testing with the ISL73141SEH indicated a cumulative dose effect on the SET events when the total dose exceeded 8.88krad(Si). Therefore, for all SET test runs, the cumulative dose was limited to less than 8.88krad(Si) to ensure a maximum number of observable SETs.

The values in Table 5 represent the maximum cumulative dose seen by any device for each given test condition.

**Table 5. Maximum Cumulative Dose During SET Testing**

| Test Condition | LET = 2.7MeV·cm <sup>2</sup> /mg<br>(krad(Si)) | LET = 8.6MeV·cm <sup>2</sup> /mg<br>(krad(Si)) | LET = 46MeV·cm <sup>2</sup> /mg<br>(krad(Si)) | LET = 86MeV·cm <sup>2</sup> /mg<br>(krad(Si)) |

|----------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| #1             | 5.75                                           | 4.94                                           | 2.75                                          | 8.26                                          |

| #2             | 5.75                                           | 4.94                                           | 2.75                                          | 5.50                                          |

| #3             | 5.92                                           | 5.49                                           | 2.75                                          | 5.50                                          |

| #4             | 5.92                                           | 5.49                                           | 2.75                                          | 5.50                                          |

| #5             | 5.57                                           | 4.40                                           | 4.13                                          | 2.75                                          |

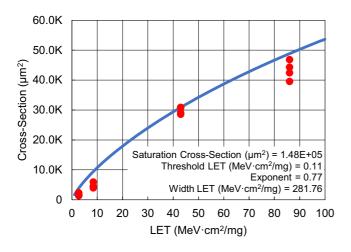

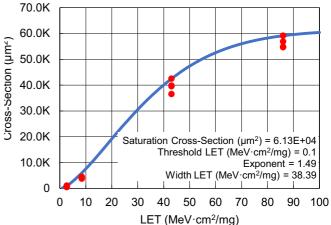

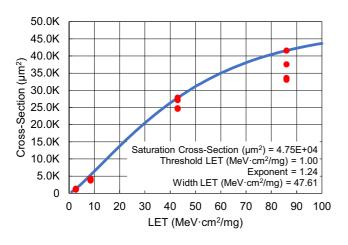

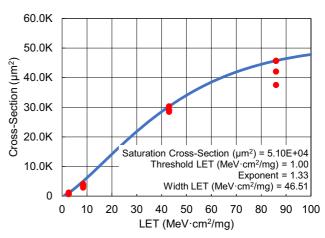

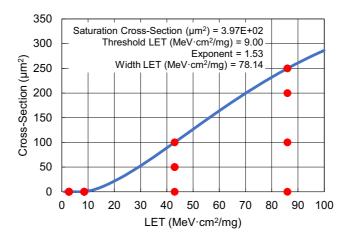

The cross-section vs LET curves for test conditions #1 through #4 are shown in Figure 3 through Figure 6. The cross-section vs LET curves show a range of saturation values from  $4.75 \times 10^4 \mu m^2$  to  $1.48 \times 10^5 \mu m^2$ . Figure 7 represents the cross section for test condition #5. This figure shows a saturation value of  $3.92 \times 10^2 \mu m^2$ . The data errors for condition #5 were also evaluated by recording the ±20 code threshold for the expected value on that channel.

The conditions of test condition #5 and test condition #2 are the same except that SCAN mode is enabled for test condition #5. Therefore, the data errors observed in SCAN mode aligned with those observed during test condition #2. This result shows that the number of SETs are independent of channel selection.

The test implementation was slightly different for test condition #5 compared to the other four test conditions. Unlike test conditions #1 through #4, the ADC data was not observed using a logic analyzer for test condition #5. Instead, all ADC sample data was collected and stored in memory during the radiation exposure. The stored data was subsequently post-processed using the algorithm illustrated in Figure 1, but instead of looking at channel 1 only, it tested all 8 channels. In addition, this software performed a check on the info bits to determine if a SET had occurred with respect to the sequencing of the ADC channels.

Figure 3. SET Cross-Section Test Condition #1

Figure 4. SET Cross-Section Test Condition #2

Figure 5. SET Cross-Section Test Condition #3

Figure 6. SET Cross-Section Test Condition #4

Figure 7. SET Cross-Section Test Condition #5 - Information Bits

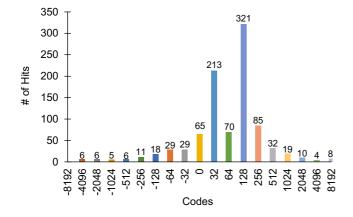

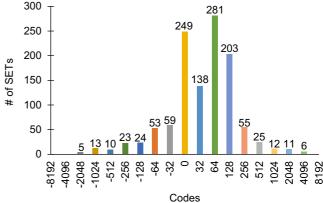

The data show that of all SETs observed under gold, silver, argon, and neon heavy ion exposure, 79.3%, 83.5%, 89.4%, and 96.7% were less than 100 codes in magnitude, respectively. 99.999% of SETs only lasted for a single sample. The single SET lasting three consecutive samples only occurred with a LET value of 86MeV·cm<sup>2</sup>/mg. There were no consecutive sample SETs observed at LET values of 8.6MeV·cm<sup>2</sup>/mg and 2.7MeV·cm<sup>2</sup>/mg.

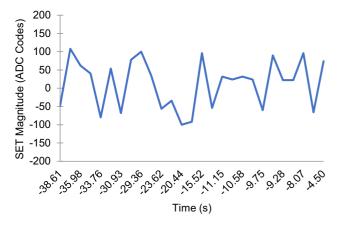

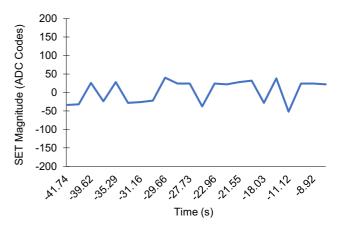

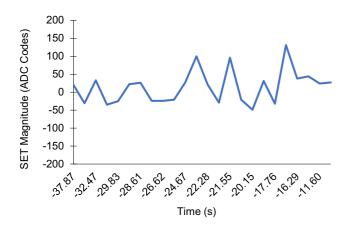

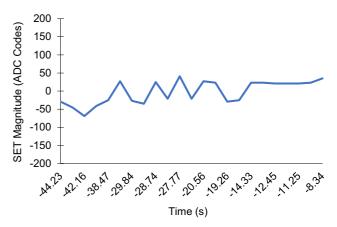

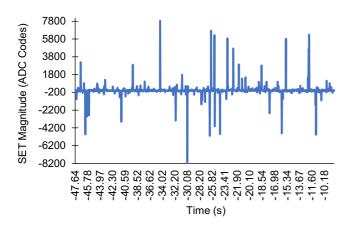

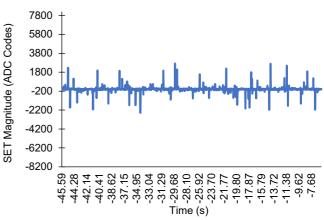

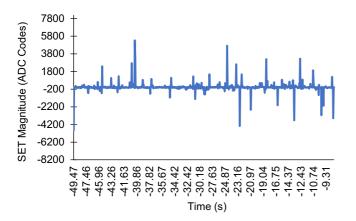

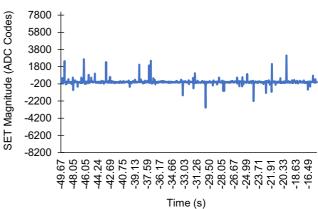

Figure 8 through Figure 15 show the ADC output code versus the time of SETs recorded on different test runs. In these figures, the run time varies slightly per run due to its dependency on flux and fluence, and a 0s value is defined as the end time of the heavy ion exposure. These figures only show the SETs and not all the samples captured. Therefore, the SETs represented in the graph are not necessarily consecutive. Figure 8 through Figure 11 are results of runs taken under a LET of 2.7MeV·cm²/mg, and Figure 12 through Figure 15 under an LET of 86MeV·cm²/mg. Table 6 and Table 7 show a detailed summary of all runs executed.

Figure 8. SET at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #1: Normal Mode, PGA Gain = 2

Figure 9. SET at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #2: Normal Mode, PGA Bypassed

Figure 10. SET at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #3: Low Power Mode, PGA Gain = 2

Figure 11. SET at LET = 2.7MeV⋅cm²/mg, Test Condition #4: Low Power Mode, PGA Bypassed

Figure 12. SET at LET = 86MeV·cm<sup>2</sup>/mg, Test Condition #1: Normal Mode, PGA Gain = 2

Figure 13. SET at LET = 86MeV·cm<sup>2</sup>/mg, Test Condition #2, Normal Mode, PGA Bypassed

Figure 14. SET at LET = 86MeV·cm<sup>2</sup>/mg, Test Condition #3: Low Power Mode, PGA Gain = 2

Figure 15. SET at LET = 86MeV·cm<sup>2</sup>/mg, Test Condition #4: Low Power Mode, PGA Bypassed

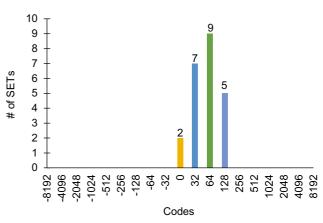

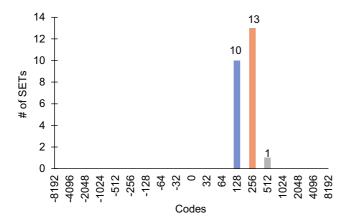

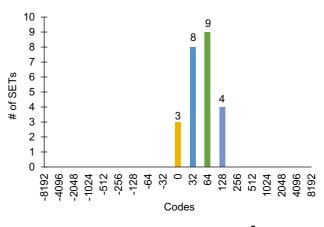

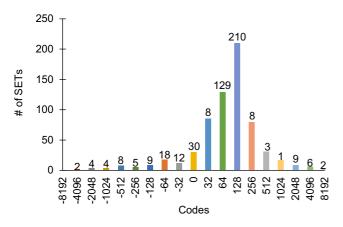

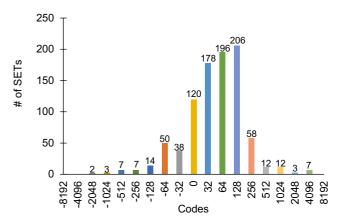

For the SET test runs shown in Figure 8 through Figure 15, a set of histograms were generated and are shown in Figure 16 through Figure 23. Even at the highest LET (86MeV·cm2/mg) 79.32% of the SETs were within 100 codes or less of the expected code value. The histogram plots show that the distribution of the SET codes is slightly shifted to a positive scale.

Figure 16. Histogram at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #1: Normal Mode, PGA Gain = 2

Figure 17. Histogram at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #2: Normal Mode, PGA Bypassed

Figure 18. Histogram at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #3: Low Power Mode, PGA Gain = 2

Figure 19. Histogram at LET = 2.7MeV·cm<sup>2</sup>/mg, Test Condition #4: Low Power Mode, PGA Bypassed

Figure 20. Histogram at LET = 86MeV⋅cm²/mg, Test Configuration #1: Normal Mode, PGA Gain = 2

Figure 21. Histogram at LET = 86MeV⋅cm²/mg, Test Configuration #2: Normal Mode, PGA Bypassed

Figure 22. Histogram at LET = 86MeV·cm<sup>2</sup>/mg, Test Configuration #3: Low Power Mode, PGA Gain = 2

Figure 23. Histogram at LET = 86MeV·cm²/mg, Test Configuration #4: Low Power Mode, PGA Bypassed

All SET test runs are given in Table 6. Information is provided on the test conditions including LET value, DUT number, test condition, sample rate, and TID. The test results are given in terms of total SET, two consecutive sample SET, percentage of SET less than 100 codes in magnitude, and percentage of samples SET free.

The total fluence was limited to 2x10<sup>6</sup>ion/cm<sup>2</sup> for all test runs. Overall, the data shows that the number of SETs decrease as the LET decreases. In addition, the average magnitude of the SET observed stays relatively small (less than 256 LSB deviation) across all LET even at the highest LET tested at 86MeV·cm<sup>2</sup>/mg. The ISL71148SLH returned to normal operation after every SET observed, except for the 15 double consecutive errors stated in Table 6. Moreover, no SEFIs were observed during any test run.

| LET<br>(MeV·cm <sup>2</sup> /mg) | DUT | Condition | Sample<br>Rate<br>(ksps) | Approx.<br>TID<br>(krad(Si)) | Total<br>SET | 2<br>Sample<br>SET | % SET<br><100<br>Codes |

|----------------------------------|-----|-----------|--------------------------|------------------------------|--------------|--------------------|------------------------|

|                                  | 8   | #2        | 900901                   | 5.5                          | 1097         | 1                  | 81.313                 |

|                                  | 8   | #1        | 456621                   | 8.26                         | 848          | 0                  | 74.057                 |

|                                  | 7   | #1        | 456621                   | 2.75                         | 936          | 0                  | 76.175                 |

|                                  | 7   | #2        | 900901                   | 5.5                          | 1137         | 0                  | 84.433                 |

|                                  | 25  | #2        | 900901                   | 2.75                         | 1183         | 3                  | 83.686                 |

|                                  | 25  | #1        | 456621                   | 5.5                          | 791          | 2                  | 74.842                 |

|                                  | 26  | #1        | 456621                   | 2.75                         | 886          | 1                  | 73.702                 |

| 86                               | 26  | #2        | 900901                   | 5.5                          | 1093         | 3                  | 83.074                 |

| 00                               | 9   | #4        | 684932                   | 2.75                         | 912          | 0                  | 82.566                 |

|                                  | 9   | #3        | 393701                   | 5.5                          | 661          | 0                  | 77.307                 |

|                                  | 10  | #3        | 393701                   | 2.75                         | 831          | 0                  | 77.377                 |

|                                  | 10  | #4        | 684932                   | 5.5                          | 750          | 0                  | 78.133                 |

|                                  | 11  | #4        | 684932                   | 2.75                         | 914          | 0                  | 84.136                 |

|                                  | 11  | #3        | 393701                   | 5.5                          | 672          | 0                  | 72.470                 |

|                                  | 12  | #3        | 393701                   | 2.75                         | 751          | 0                  | 77.230                 |

|                                  | 12  | #4        | 684932                   | 5.5                          | 841          | 0                  | 80.856                 |

Table 6. Test Condition #1, #2, #3, and #4 SET Results (Cont.)

| LET<br>(MeV·cm²/mg) | DUT | Condition | Sample<br>Rate<br>(ksps) | Approx.<br>TID<br>(krad(Si)) | Total<br>SET | 2<br>Sample<br>SET | % SET<br><100<br>Codes |

|---------------------|-----|-----------|--------------------------|------------------------------|--------------|--------------------|------------------------|

|                     | 17  | #2        | 900901                   | 1.376                        | 796          | 1                  | 86.181                 |

|                     | 17  | #1        | 456621                   | 2.752                        | 615          | 0                  | 80.000                 |

|                     | 18  | #1        | 456621                   | 1.376                        | 581          | 2                  | 78.141                 |

|                     | 18  | #2        | 900901                   | 2.752                        | 791          | 0                  | 87.611                 |

|                     | 19  | #2        | 900901                   | 1.376                        | 731          | 1                  | 88.372                 |

|                     | 19  | #1        | 456621                   | 2.752                        | 571          | 0                  | 79.159                 |

|                     | 20  | #1        | 456621                   | 1.376                        | 618          | 0                  | 78.803                 |

| 46                  | 20  | #2        | 900901                   | 2.752                        | 850          | 1                  | 85.059                 |

| 40                  | 21  | #4        | 684932                   | 1.376                        | 580          | 0                  | 87.241                 |

|                     | 21  | #3        | 393701                   | 2.752                        | 492          | 0                  | 83.333                 |

|                     | 22  | #3        | 393701                   | 1.376                        | 557          | 0                  | 79.713                 |

|                     | 22  | #4        | 684932                   | 2.752                        | 606          | 0                  | 86.964                 |

|                     | 23  | #4        | 684932                   | 1.376                        | 569          | 0                  | 85.237                 |

|                     | 23  | #3        | 393701                   | 2.752                        | 495          | 0                  | 78.586                 |

|                     | 24  | #3        | 393701                   | 1.376                        | 542          | 0                  | 78.967                 |

|                     | 24  | #4        | 684932                   | 1.376                        | 581          | 0                  | 87.952                 |

|                     | 17  | #2        | 900901                   | 4.672                        | 90           | 0                  | 94.444                 |

|                     | 17  | #1        | 456621                   | 4.944                        | 119          | 0                  | 86.555                 |

|                     | 18  | #1        | 456621                   | 4.672                        | 90           | 0                  | 88.889                 |

|                     | 18  | #2        | 900901                   | 4.944                        | 80           | 0                  | 93.750                 |

|                     | 19  | #2        | 900901                   | 4.672                        | 75           | 0                  | 94.667                 |

|                     | 19  | #1        | 456621                   | 4.944                        | 87           | 0                  | 86.207                 |

|                     | 20  | #1        | 456621                   | 4.672                        | 79           | 0                  | 79.747                 |

| 9.6                 | 20  | #2        | 900901                   | 4.944                        | 85           | 0                  | 92.941                 |

| 8.6                 | 21  | #4        | 684932                   | 5.216                        | 70           | 0                  | 92.857                 |

|                     | 21  | #3        | 393701                   | 5.488                        | 84           | 0                  | 84.524                 |

|                     | 22  | #3        | 393701                   | 5.216                        | 78           | 0                  | 91.026                 |

|                     | 22  | #4        | 684932                   | 5.488                        | 70           | 0                  | 95.714                 |

|                     | 23  | #4        | 684932                   | 5.216                        | 57           | 0                  | 92.982                 |

|                     | 23  | #3        | 393701                   | 5.488                        | 81           | 0                  | 83.951                 |

|                     | 24  | #3        | 393701                   | 5.216                        | 74           | 0                  | 81.081                 |

|                     | 24  | #4        | 684932                   | 5.488                        | 82           | 0                  | 93.902                 |

Table 6. Test Condition #1, #2, #3, and #4 SET Results (Cont.)

| LET<br>(MeV·cm²/mg) | DUT | Condition | Sample<br>Rate<br>(ksps) | Approx.<br>TID<br>(krad(Si)) | Total<br>SET | 2<br>Sample<br>SET | % SET<br><100<br>Codes |

|---------------------|-----|-----------|--------------------------|------------------------------|--------------|--------------------|------------------------|

|                     | 17  | #2        | 900901                   | 5.6608                       | 22           | 0                  | 100.00                 |

|                     | 17  | #1        | 456621                   | 5.7472                       | 27           | 0                  | 92.593                 |

|                     | 18  | #1        | 456621                   | 5.6608                       | 32           | 0                  | 93.750                 |

| •                   | 18  | #2        | 900901                   | 5.7472                       | 17           | 0                  | 100.00                 |

|                     | 19  | #2        | 900901                   | 5.6608                       | 10           | 0                  | 100.00                 |

|                     | 19  | #1        | 456621                   | 5.7472                       | 30           | 0                  | 90.000                 |

|                     | 20  | #1        | 456621                   | 5.6608                       | 46           | 0                  | 97.826                 |

| 2.7                 | 20  | #2        | 900901                   | 5.7472                       | 15           | 0                  | 100.00                 |

| 2.1                 | 21  | #4        | 684932                   | 5.8336                       | 23           | 0                  | 100.00                 |

|                     | 21  | #3        | 393701                   | 5.92                         | 21           | 0                  | 100.00                 |

|                     | 22  | #3        | 393701                   | 5.8336                       | 24           | 0                  | 95.833                 |

|                     | 22  | #4        | 684932                   | 5.92                         | 17           | 0                  | 100.00                 |

|                     | 23  | #4        | 684932                   | 5.8336                       | 13           | 0                  | 100.00                 |

|                     | 23  | #3        | 393701                   | 5.92                         | 24           | 0                  | 91.667                 |

|                     | 24  | #3        | 393701                   | 5.8336                       | 27           | 0                  | 96.296                 |

|                     | 24  | #4        | 684932                   | 5.92                         | 13           | 0                  | 100.00                 |

Table 7. Test Condition #5 Information bits SET Results

| LET<br>(MeV·cm²/mg) | DUT | Sample Rate<br>(ksps) | SCAN | Approx.<br>TID<br>(krad(Si)) | Total Info<br>bits<br>SET | Total Samples |

|---------------------|-----|-----------------------|------|------------------------------|---------------------------|---------------|

|                     | 13  | 900901                | Yes  | 2.75                         | 5                         | 31981568      |

| 86                  | 14  | 900901                | Yes  | 2.75                         | 4                         | 31981568      |

| 00                  | 15  | 900901                | Yes  | 2.75                         | 2                         | 31981568      |

|                     | 16  | 900901                | Yes  | 2.75                         | 0                         | 31981568      |

|                     | 13  | 900901                | Yes  | 4.13                         | 0                         | 31981568      |

| 46                  | 14  | 900901                | Yes  | 4.13                         | 1                         | 31981568      |

| 40                  | 15  | 900901                | Yes  | 4.13                         | 1                         | 31981568      |

|                     | 16  | 900901                | Yes  | 4.13                         | 2                         | 31981568      |

|                     | 13  | 900901                | Yes  | 4.4                          | 0                         | 31981568      |

| 0.6                 | 14  | 900901                | Yes  | 4.4                          | 0                         | 31981568      |

| 8.6                 | 15  | 900901                | Yes  | 4.4                          | 0                         | 31981568      |

|                     | 16  | 900901                | Yes  | 4.4                          | 0                         | 31981568      |

Table 7. Test Condition #5 Information bits SET Results (Cont.)

| LET<br>(MeV·cm²/mg) | DUT | Sample Rate<br>(ksps) | SCAN | Approx.<br>TID<br>(krad(Si)) | Total Info<br>bits<br>SET | Total Samples |

|---------------------|-----|-----------------------|------|------------------------------|---------------------------|---------------|

| 2.7                 | 17  | 900901                | Yes  | 5.57                         | 0                         | 31981568      |

|                     | 18  | 900901                | Yes  | 5.57                         | 0                         | 31981568      |

|                     | 15  | 900901                | Yes  | 5.57                         | 0                         | 31981568      |

|                     | 16  | 900901                | Yes  | 5.57                         | 0                         | 31981568      |

Table 8. Test Condition #1, #2, #3, and #4 SET Results Per Condition

| LET<br>(MeV·cm²/mg) | Condition | Average #SET / Run |  |

|---------------------|-----------|--------------------|--|

|                     | #1        | 865                |  |

| 86                  | #2        | 1128               |  |

| 00                  | #3        | 729                |  |

|                     | #4        | 854                |  |

|                     | #1        | 596                |  |

| 46                  | #2        | 792                |  |

| 40                  | #3        | 522                |  |

|                     | #4        | 584                |  |

|                     | #1        | 94                 |  |

| 8.6                 | #2        | 83                 |  |

| 0.0                 | #3        | 79                 |  |

|                     | #4        | 70                 |  |

|                     | #1        | 34                 |  |

| 2.7                 | #2        | 16                 |  |

| ۷.1                 | #3        | 21                 |  |

|                     | #4        | 17                 |  |

**Table 9. Test Condition #5 Data SET Results**

| LET<br>(MeV·cm²/mg) | Sample Rate<br>(ksps) | SCAN | Approx.<br>TID<br>(krad(Si)) | Average #SET /<br>Run | Total Samples |

|---------------------|-----------------------|------|------------------------------|-----------------------|---------------|

| 86                  | 900901                | Yes  | 2.75                         | 1281                  | 31981568      |

| 46                  | 900901                | Yes  | 4.13                         | 709                   | 31981568      |

| 8.6                 | 900901                | Yes  | 4.4                          | 79                    | 31981568      |

| 2.7                 | 900901                | Yes  | 5.57                         | 18                    | 31981568      |

## 3. SET Mitigation Options

The ISL71148SLH experiences SETs when exposed to radiation. These SETs are small in magnitude with most below 256 LSBs of deviation from the expected value. Most SETs last for a single sample with less than 15 observed SET lasting for two consecutive samples. Only one SET lasted three consecutive samples. To mitigate these events, some possible options are as follows:

- Collect a large number of samples and average them to reduce the effects of a SET within those samples.

Averaging many samples reduces the impact of any SET that may be present in the collected data. The application would dictate the number of samples required to reduce SETs below any appreciable system-level effect

- In an application where a known range of values is expected, omit a set of samples if they are outside a defined window. This method is similar to the detection of SETs presented in this report. In this case, if samples are collected outside the expected range, they are disregarded, and another acquisition of data occurs.

- Use a combination of the first two options. This option collects a large number of samples, discards any sample

beyond an application-based threshold window, and averages the remaining samples. If a set of sample data is

collected with an expected value of 8200 and an expected range of 8150 to 8250, any code outside of this

range is discarded while the remaining samples are averaged.

### 4. Discussion and Conclusions

The ISL71148SLH proved to be DSEE immune up to an  $AV_{CC}$  = 6.2V,  $DV_{CC}$  = 4.6V, and  $V_{REF}$  = 3.6V when irradiated with normal incidence of gold at 86MeV·cm<sup>2</sup>/mg. The testing was completed with a die temperature of 125°C ±10°C.

The ISL71148SLH exhibited mostly single-sample low-magnitude SETs. For conditions #1 through 4, the saturation cross-sections ranged from  $4.75\times10^4\mu\text{m}^2$  to  $1.48\times10^5\mu\text{m}^2$ . The highest saturation cross-section was for test condition #1, where the ISL71148SLH was operated in normal mode with the PGA gain set to a value of 2. The next highest cross-section was for test condition #2, which was also operated in normal mode but with the PGA bypassed. The data errors in test condition #5 were similar to those from condition #2, indicating that the channel sequencer has little impact. The lowest saturation cross-section was for condition #5, with a value of  $3.97\times10^2\mu\text{m}^2$  when looking at the information bits, which shows that few SETs were observed in the channel sequencer operation.

Out of all SETs observed, 15 lasting two consecutive samples were observed, with most lasting for a single sample and only one lasting for three consecutive samples. The SET remains at a relatively low average magnitude up to a LET of 86MeV·cm²/mg. The data shows that of all SETs observed under gold, silver, argon, and neon heavy ion exposure, 79.3%, 83.5%, 89.4%, and 96.7% were less than 100 codes in magnitude, respectively. The SET data exhibits that the ISL71148SLH does not experience large magnitude SET on average and that when a SET occurs, the device recovers after one sample 99.999% of the occasions.

In addition, no SEFIs were observed, and the ADC returned to the expected code value range without user intervention at all LET values tested.

Overall, the SEE data illustrate that the ISL71148SLH is well-suited for space applications, offering robust DSEE performance and SET with minimal impact on the end application.

# 5. Revision History

| Rev. | Date         | Description                    |  |

|------|--------------|--------------------------------|--|

| 1.01 | Jul 3, 2024  | Updated VREF value in Table 4. |  |

| 1.00 | Apr 22, 2024 | initial release                |  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.