# **inter<sub>sil</sub>**"

### ISL75052SEH

Single-Event Performance

## TEST REPORT

AN1851 Rev 0.00 November 10, 2014

### Introduction

The intense proton and heavy ion environment encountered in space applications can cause a variety of Single-Event Effects (SEE) in electronic circuitry, including Single-Event Upset (SEU), Single-Event Transient (SET), Single-Event Functional Interrupt (SEFI), Single-Event Latch-up (SEL), Single-Event Burnout (SEB) and Single-Event Gate Rupture (SEGR). SEE can lead to system-level performance issues including disruption, degradation and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response.

This report discusses the results of Intersil's SEE testing of the ISL75052SEH LDO. Testing was carried out with two objectives in mind. The first was to establish safe operating limits with regard to input voltage and incident ion linear energy transport (LET). The second was to establish the characteristics of SET under normal operating conditions.

Note: Throughout this document LET<sub>EFF</sub> is used to indicate effective linear energy transfer in units of MeV\*cm<sup>2</sup>/mg. For brevity the units are omitted and should be understood throughout the rest of the document.

## **Executive Summary of Results**

#### Damaging SEE (SEB, SEGR, or SEL)

No damage was recorded for parts tested at  $V_{IN} \le 15.0V$ , LET<sub>EFF</sub> = 86 (Au at normal incidence), and case temperature at +125°C ±10°C. Parts were tested both disabled (i.e.  $V_{OUT} = 0.0V$ ) and with  $V_{OUT} = 14.0V$  and  $I_{OUT} = 1.8A$ .

#### Single-Event Functional Interrupt (SEFI)

No SEFI were observed during any of the testing, and no SET on power-good (PG) to a 0.5V trigger was captured either.

#### Single-Event Transient (SET)

No  $V_{OUT}$  SETs were observed in excess of a  $V_{OUT}$  deviation window of +35mV and -20mV.

No power-good (PG) SET were found for an observational threshold of 0.5V.

The output capacitance was composed of two tantalum capacitors (T541X107M025AH6510) with nominal values of 100 $\mu F$  and 60m $\Omega$  ESR.

#### **Part Description**

The ISL75052SEH is a radiation hardened, single output LDO specified for a maximum output current of 1.5A. The device is specified to operate from input voltages over the 4.0V to 13.2V range. Attainable output voltages are bounded by a 0.6V reference on the low end and a 225mV dropout at 1.5A or 75mV at 0.5A. The output is adjustable based on an external resistor divider. The 16-lead dual in-line ceramic flatpack has a metal pad on the bottom to facilitate thermal management. The part has an enable input (EN) and an open-drain power-good (PG) signal.

#### **Irradiation Test Facility**

Testing was performed at the Radiation Effects Facility of Texas A&M University's (TAMU) Cyclotron Institute in College Station, Texas. The TAMU facility is coupled to a K500 super-conducting cyclotron, which is capable of generating a wide range of ion species with the various energy, flux and fluence levels needed for SEE testing. Details about the facility and the ion beams can be found on the TAMU Cyclotron Institute web site (<u>http://cyclotron.tamu.edu/ref/</u>). The testing reported here was done March 7, 2013.

#### **Reference Documents**

- ISL75052SEH Datasheet

- ISL75052SEH Evaluation Board User Guide

- ISL75052SEH Radiation Test Report

- SMD (<u>5962-13220</u>)

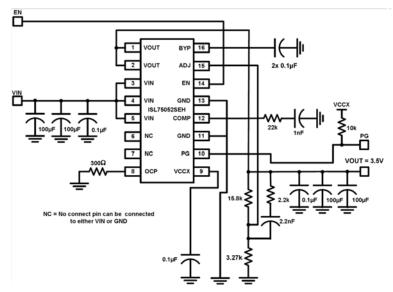

FIGURE 1. SCHEMATIC USED FOR SEE TESTING

#### **SEE Testing Description**

SEE testing was carried out with samples mounted on the engineering evaluation boards. Loading was provided by an electronic load. The schematic of the board is shown in Figure 1.

Digital multimeters monitored input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>) and input current (I<sub>IN</sub>). In disabled test cases the leakage current to the output (ILK) was monitored. For damaging SEE (SEB, SEGR, SEL) studies the parts were heated with a film heater on the back of the circuit board to +125 °C ±10 °C case temperature. The heater current to achieve the desired case temperature was determined prior to the TAMU trip and applied during testing. Parameters V<sub>OUT</sub>, I<sub>IN</sub> and ILK were monitored before and after irradiation as indications of part damage. For the SET studies the case temperature was left to ambient. V<sub>OUT</sub> and PG (power-good) were used as the triggering signal for a LeCroy wave Runner 4-channel digital oscilloscope to capture SET. Other channels that were simultaneously captured the reference voltage (BYP), and the parts internally generated low voltage supply (VCCX).

## Damaging SEE Testing and Results (SEB, SEGR, SEL)

The test matrix run for damaging SEE on the ISL75052 appears in Table 1. The same four parts (device under test, DUT) were used for all the testing and accumulated about 55krad(Si) by the end of the testing. The parameters monitored pre and post irradiation to look for damage are listed with the actual measurements. The measurement variations are all within the on-site measurement repeatability so there is no evidence of damage.  $V_{IN} = 14.7V$  was the intended goal for passing SEE without damage, while the  $V_{IN} = 15.0V$  was an effort to document some margin against that goal.

| UNIT | V <sub>IN</sub><br>(V) | <sup>I</sup> оит<br>(A) | V <sub>OUT</sub><br>(V) |        | l <sub>IN</sub><br>(mA)<br>I <sub>OUT</sub> = 0 |      | ILK<br>(nA)<br>V <sub>OUT</sub> = 0 |      |

|------|------------------------|-------------------------|-------------------------|--------|-------------------------------------------------|------|-------------------------------------|------|

|      |                        |                         | PRE                     | POST   | PRE                                             | POST | PRE                                 | POST |

| DUT1 | 14.7                   | Disabled                |                         |        | 9.5                                             | 9.5  | 200                                 | 200  |

|      | 14.7                   | 1.8                     | 14.011                  | 14.012 | 24.8                                            | 24.6 |                                     |      |

|      | 15.0                   | Disabled                |                         |        | 9.7                                             | 9.8  | 270                                 | 255  |

|      | 15.0                   | 1.8                     | 14.011                  | 14.012 | 24.7                                            | 24.8 |                                     |      |

| DUT2 | 14.7                   | Disabled                |                         |        | 9.5                                             | 9.5  | 260                                 | 260  |

|      | 14.7                   | 1.8                     | 13.978                  | 13.980 | 24.1                                            | 24.2 |                                     |      |

|      | 15.0                   | Disabled                |                         |        | 9.7                                             | 9.8  | 290                                 | 280  |

|      | 15.0                   | 1.8                     | 13.980                  | 13.979 | 24.4                                            | 24.3 |                                     |      |

| DUT3 | 14.7                   | Disabled                |                         |        | 9.5                                             | 9.5  | 260                                 | 260  |

|      | 14.7                   | 1.8                     | 13.973                  | 13.975 | 23.9                                            | 23.7 |                                     |      |

|      | 15.0                   | Disabled                |                         |        | 9.7                                             | 9.8  | 325                                 | 332  |

|      | 15.0                   | 1.8                     | 13.969                  | 13.969 | 24.2                                            | 24.1 |                                     |      |

| DUT4 | 14.7                   | Disabled                |                         |        | 9.5                                             | 9.5  | 330                                 | 330  |

|      | 14.7                   | 1.8                     | 14.040                  | 14.040 | 24.0                                            | 24.0 |                                     |      |

|      | 15.0                   | Disabled                |                         |        | 9.7                                             | 9.7  | 365                                 | 350  |

|      | 15.0                   | 1.8                     | 14.051                  | 14.051 | 24.3                                            | 24.1 |                                     |      |

#### TABLE 1. DAMAGING SEE TESTING MATRIX

NOTE: Each of the 16 tests listed was done with Au at 0° (LET<sub>EFF</sub> = 86), T<sub>C</sub> = +125°C, and flux of  $5x10^4$  ion\*cm<sup>-2</sup>\*s<sup>-1</sup> to fluence of  $1x10^7$  ion/cm<sup>2</sup>.

#### Damaging SEE (SEB, SEGR, SEL) Discussion

Conservatively the data in <u>Table 1</u> represents a fluence of  $8 \times 10^7$ ion/cm<sup>2</sup> at V<sub>IN</sub> 14.7V and LET<sub>EFF</sub> = 86 without a failure. This corresponds to a nominal cross section of  $1.25 \times 10^{-8}$  cm<sup>2</sup>, which is smaller than any active device in the product and so is a very strong statement against damage susceptibility at LET<sub>EFF</sub> = 86. The clean results at V<sub>IN</sub> = 15.0V provide evidence of extra margin against the 14.7V product claim for SEB, SEGR, and SEL free operation.

#### **SET Testing and Results**

SET testing was done with gold (Au) at zero degrees incidence for  $LET_{EFF} = 86$ . The device temperature was left to the ambient conditions. The output voltage ( $V_{OUT}$ ) was set to 3.5V for all tests. Four units were tested with irradiation runs at each of three different conditions:  $V_{IN} = 4.0V$  and  $I_{OUT} = 0.1A$ ,  $V_{IN} = 4.0V$  and  $I_{OUT} = 1.5A$ , and  $V_{IN} = 13.2V$  and  $I_{OUT} = 0.1A$ . The first two conditions cover a load range for low supply headroom (0.5V between  $V_{IN}$  and  $V_{OUT}$ ) and the last condition looks at high supply headroom (9.7V). In the last case, the current was only tested at 0.1A because of thermal considerations. It was anticipated that the high load current and low headroom condition (nearest drop-out) would be the worst case for negative transients, and the low load current and high headroom case would be the worst for positive transients. This was indeed found to be the case.

Oscilloscope triggering on V<sub>OUT</sub> was set to capture transients with ±10mV V<sub>OUT</sub> deviations and also ±75mV V<sub>OUT</sub> deviations. The BYP and VCCX were also captured on any V<sub>OUT</sub> trigger for information on the origin of the SET. The captures were set to start 20µs prior to the trigger and end 80µs after the trigger.

No SETs were captured with the  $\pm 75$ mV trigger during  $1 \times 10^7$ ion/cm<sup>2</sup> of each run. The  $\pm 10$ mV transients were plentiful; capturing was terminated at roughly 200 SET captures for each run. The 200 SET count limit was reached at about  $2 \times 10^6$

#### **Composite Plots**

ion/cm<sup>2</sup> for  $I_{OUT} = 0.1A$ , but was reached at about  $1.3 \times 10^{6}$  ion/cm<sup>2</sup> for the 1.5A load. This reflects the generation of negative transients achieving the trigger value with the higher load current (1.5A); the same SET at the lower load current (0.1A) did not reach the trigger value and so were not captured.

No SET on PG (power-good, to a -0.5V trigger) was registered.

| RUN | DUT | V <sub>IN</sub> | Ιουτ | COUNT | TERMINATING<br>FLUENCE |  |  |  |  |

|-----|-----|-----------------|------|-------|------------------------|--|--|--|--|

| 421 | 1   | _               | 0.1  | 201   | 1.92E+06               |  |  |  |  |

| 424 | 2   |                 |      | 200   | 1.88E+06               |  |  |  |  |

| 427 | 3   |                 |      | 202   | 1.96E+06               |  |  |  |  |

| 430 | 4   | 4.0             |      | 202   | 2.02E+06               |  |  |  |  |

| 422 | 1   |                 | 1.5  | 202   | 1.22E+06               |  |  |  |  |

| 425 | 2   |                 |      | 202   | 1.18E+06               |  |  |  |  |

| 428 | 3   |                 |      | 206   | 8.66E+05               |  |  |  |  |

| 431 | 4   |                 |      | 272   | 1.54E+06               |  |  |  |  |

| 423 | 1   |                 | 0.1  | 201   | 2.22E+06               |  |  |  |  |

| 426 | 2   | 100             |      | 202   | 1.89E+06               |  |  |  |  |

| 429 | 3   | - 13.2          |      | 202   | 1.90E+06               |  |  |  |  |

| 432 | 4   |                 |      | 202   | 1.52E+06               |  |  |  |  |

#### TABLE 2. SUMMARY OF VOUT SET TESTING

#### **SET Composite Plots and Discussion**

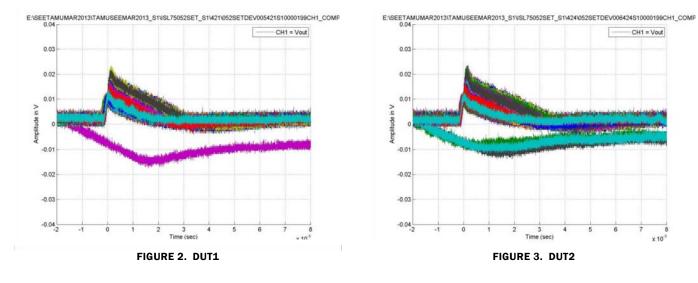

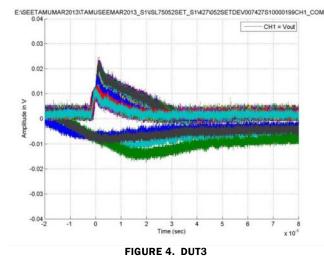

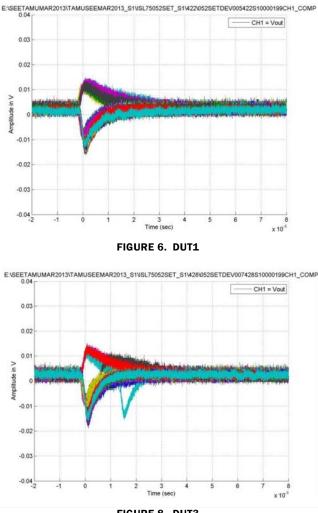

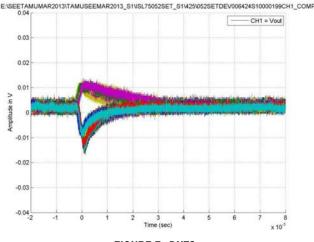

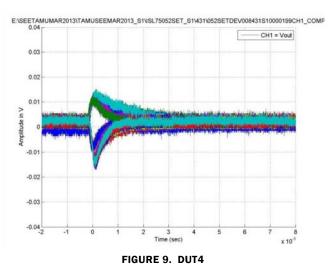

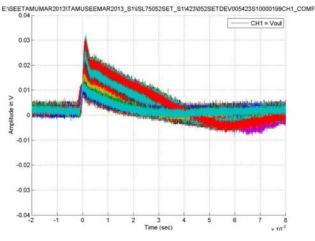

The following plots give a qualitative look at the SET populations captured. For each of the three operating conditions tests has a plot for each of the four DUTs. These plots are composites of the first 200.

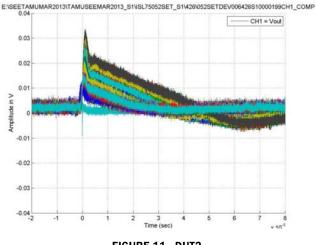

#### All SET captured for each DUT at $V_{IN}$ = 4.0V, $V_{OUT}$ = 3.5V, $I_{OUT}$ = 0.1A. Time (abscissa) is 10µs/div and

$V_{\mbox{OUT}}\xspace$  (ordinate) is 10mV/div.

#### **Composite Plots**

All SET captured for each DUT at  $V_{IN}$  = 4.0V,  $V_{OUT}$  = 3.5V,  $I_{OUT}$  = 0.1A. Time (abscissa) is 10µs/div and

$V_{OUT} \mbox{ (ordinate) is } 10 mV/div. \mbox{ (Continued)}$

The vast majority of the SET for V<sub>IN</sub> = 4.0V and I<sub>OUT</sub> = 0.1A are fast, positive transients indicating a rapid increase in the current being supplied by the ISL75052SEH beyond the load demand (0.1A). The fast, positive transients peak about 2µs to 3µs after they start with a small spike at the top. The small spike at top of the SET is due to the excess current encountering the high frequency impedance of C<sub>OUT</sub>. The falling edge of this spike indicates the real SET is over in less than 5µs. However, C<sub>OUT</sub> has been overcharged in that time so that V<sub>OUT</sub> is now above the setting. Since the ISL75052 has no active pull-down device, the excess V<sub>OUT</sub> can only decay away through the load and feedback divider. The 0.1A load and the C<sub>OUT</sub> value then set the rate of decay of the V<sub>OUT</sub> overvoltage (200µF at 0.1A for 0.5mV/µs or 5mV/div in the figures).

The few slow, negative transients begin with the characteristic discharge rate of  $C_{OUT}$  indicating the part has stopped supplying current. A bottom  $V_{OUT}$  is reached above -20mV at which time the parts supply of current resumes. A relatively slow (100s of  $\mu$ s) recovery back to the nominal  $V_{OUT}$  ensues. These slow, negative  $V_{OUT}$  transients correlated to small drops in the reference voltage (BYP) used for regulation. The entire  $V_{OUT}$  SET can then be understood on the basis of a slight dropping of BYP due to the ion. For the -20mV events seen here at  $V_{OUT}$  = 3.5V, the driving SET deviation in BYP is only about -3mV.

All the captured transients in Figures 6 through 9 are bounded by a window of +25mV and -20mV deviation. These correspond to+1% and -0.6% of the 3.5V output. At lower output voltages the absolute magnitudes would be expected to apply; for a 1V output the relative deviations would become +3.5% and -2%.

FIGURE 5. DUT4

#### **Composite Plots**

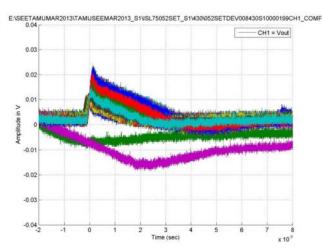

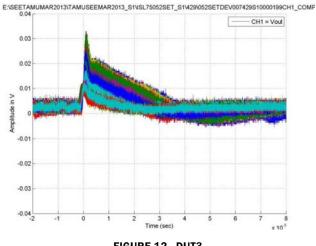

100 SET captured for each of DUTs 1 through 4 at VIN = 4.0V, VOUT = 3.5V, IOUT = 1.5A. Time (abscissa) is 10µs/div and  $V_{OUT}$  (ordinate) is 10mV/div.

FIGURE 8. DUT3

FIGURE 7. DUT2

that similar BYP events would look significantly different from those in Figures 10 through 13 other than a more rapid decline followed by the same slow recovery.

These captured transients for I<sub>OUT</sub> = 1.5A are bounded by +15mV and -20mV. This is less in both directions than the previous case.

With 1.5A of load current, the dominant form of SET captured switched to a fast, negative transient. The high loading draws VOLT down rapidly now when the device current being supplied is interrupted. At the lower load (0.1A) the same SET would not have resulted in a V<sub>OUT</sub> drop large enough to reach the 10mV trigger. So it is not that any new SET form has appeared, it is just that the SET are amplified by the higher load to the point of capture. The fast, negative transient have a duration of only a few microseconds (the precipitous fall in  $V_{\mbox{OUT}}$  set by the load current). Then the loop control recovers  $V_{OUT}$  in about 20µs.

There are still some fast, positive transients. These are actually the same transients seen in Figures 10 through 13, but the higher load demand has modified the captured forms a bit. The rise is not quite as fast and the spike at the top is gone. This is an indication that the charging of  $C_{OUT}$  is much reduced; this is also supported by the lower VOUT ramp starts.

There were no slow, negative transients observed. There is no obvious reason for this to be the case. However, given the correlation to the BYP disturbances, there is no reason to believe

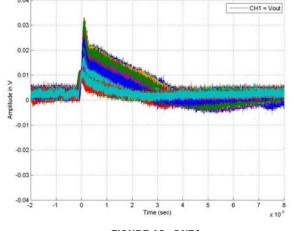

## **Composite Plots** 200 SET captured for each of DUTs 1 through 4 at V<sub>IN</sub> = 13.2V, V<sub>OUT</sub> = 3.5V, I<sub>OUT</sub> = 0.1A. Time

(abscissa) is 10µs/div and  $V_{\mbox{OUT}}$  (ordinate) is 10mV/div.

FIGURE 10. DUT1

FIGURE 11. DUT2

FIGURE 12. DUT3

E:SEETAMUMAR2013\TAMUSEEMAR2013\_S1VSL75052SET\_S1V29/052SETDEV007429S10000199CH1\_COMP

FIGURE 13. DUT4

For the case of V<sub>IN</sub> = 13.2V and I<sub>OUT</sub> = 0.1A the fast, positive transients again dominate as they did in Figures 2 through 5 (V<sub>IN</sub> = 4.0V, I<sub>OUT</sub> = 0.1A). However, with more V<sub>IN</sub> headroom (9.7V above V<sub>OUT</sub>) both the spike at the top of the SET and the residual charging of C<sub>OUT</sub> are larger. This indicates that more current is being pushed during the SET. Clearly the worst case positive SET are found for low load currents and high headroom on V<sub>IN</sub>.

There is still one slow, negative transient that correlates to a minuscule drop in BYP.

Under these conditions the transients are bounded by +35mV and -15mV. Over all three operational conditions the observed transients are bounded by a +35mV and -20mV window.

#### **Further SET Discussion**

No SEFIs, PG SETs, or V<sub>OUT</sub> SETs in excess of  $\pm 75$ mV were observed to the full 1x10<sup>7</sup> ion/cm<sup>2</sup> in each of the 12 SET runs (4 DUTs, 3 conditions). This puts rather comfortable bounds on any possible cross section for events. At the very least, 4x10<sup>7</sup> ion/cm<sup>2</sup> failed to generate these events for each of the three operating conditions. Taken together, a fluence of 1.2x10<sup>8</sup> ion/cm<sup>2</sup> yielded no events.

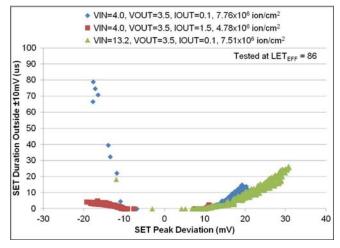

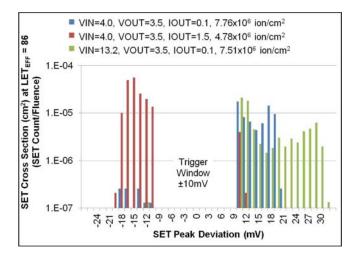

A MATLAB program was applied to the SET data to extract the peak deviation and the time duration outside the  $\pm 10$ mV deviation window. The deviations were calculated based on the VOUT of that trace prior to triggering, so there is a small offset from the absolute scales of the SET plots. The results are plotted in Figure 14. This clearly shows a SET deviation window (+33mV, -20mV) and highlights two types of SET. Most SETs are a short disturbance followed by a recovery time that depends on the loading conditions. At light loading (0.1A) the positive SET are larger and require time to discharge C<sub>OUT</sub>. At high loading (1.5A) negative SET dominate due to interruption in current, and the recovery proceeds immediately after that SET when control loop reasserts itself and supplies recovery current. The long negative SET are due to small drops in the reference voltage and require a longer time to recover.

#### FIGURE 14. SET DURATION VERSUS SET PEAK DEVIATION FOR ALL CAPTURED DATA

Another way to look at the SET population is to consider the cross section presented by the various SET magnitudes. This approach yields the plot in Figure 15. The small population of long, negative SET so obvious in Figure 14 corresponds to the very small cross section negative events in Figure 15.

FIGURE 15. SET REPRESENTED AS CROSS SECTION BY EVENT VOUT PEAK DEVIATION

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338