概览

简介

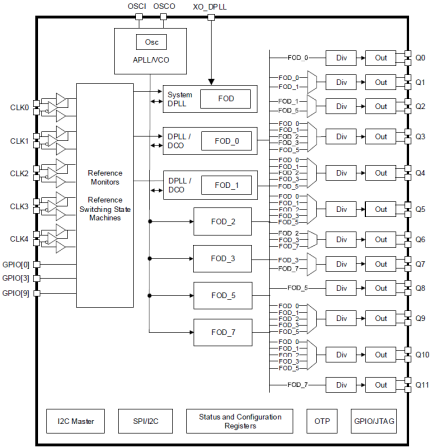

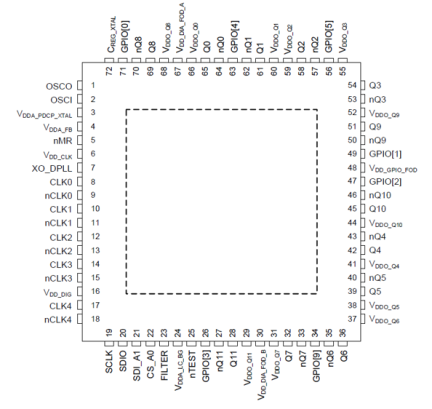

The RC32112A regenerates and distributes ultra-low jitter clock outputs and features up to 6 independent frequency domains that can be either locked to the external reference clock or locked to a free-run crystal or oscillator. Digital PLLs (DPLLs) support hitless reference switching between references from redundant timing sources. The device supports multiple independent timing channels for: IEEE 1588 clock synthesis; SyncE clock generation; jitter attenuation and radio clock generation including SYSREF generation for converters. Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs ultra-low-jitter clocks that can directly synchronize SERDES running at up to 56Gbps; as well as CPRI/OBSAI, SONET/SDH ADC/DAC. The device is ideal for use in 100G/200G/400G/800G telecom switch line cards, fabric cards and wireless small cell applications.

特性

- Two timing channels and six independent frequency domains

- Output jitter below 100fs RMS

- Digital PLLs (DPLLs) lock to any frequency from 0.5kHz to 1GHz

- DPLLs / Digitally Controlled Oscillators (DCOs) generate any frequency from 0.5Hz to 1GHz

- DCO outputs can be aligned in phase and frequency with the outputs of any DPLL or DCO

- Can be used as a jitter attenuator, clock generator, or synchronizer

- Reference monitors qualify/disqualify references depending on LOS, activity, frequency monitoring and/or LOS input pins

- Automatic reference selection state machines select the active reference for each DPLL based on the reference monitors, priority tables, revertive / non-revertive and other programmable settings

- Device requires a crystal oscillator or fundamental-mode crystal: 25MHz to 54MHz

- The device can configure itself automatically after reset via:

- Internal Customer-programmable One-Time Programmable memory

- Standard external I2C EPROM via separate I2C Master Port

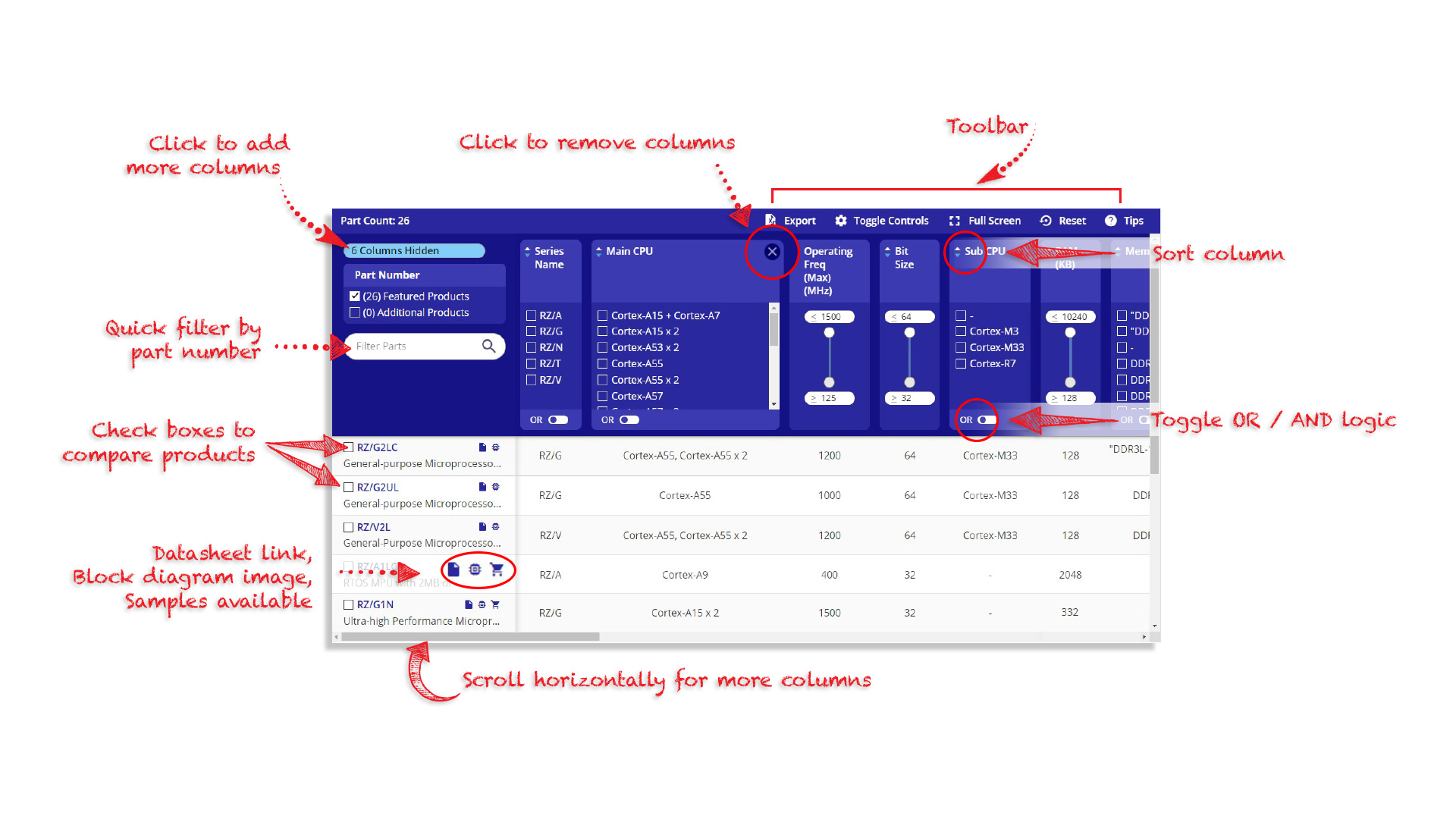

产品对比

应用

设计和开发

软件与工具

软件与工具

| Software title

|

Software type

|

公司

|

|---|---|---|

| Timing Commander Timing Commander™ 是一个基于 Windows™ 的创新软件平台,通过这个平台,系统设计工程师可以通过直观且灵活的图形用户界面 (GUI) 对精密的计时设备进行配置、编程和监控。

|

Code Generator | 瑞萨电子 |

1 item

|

||

模型

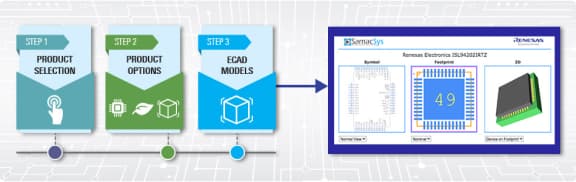

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

视频和培训

Introducing the IDT ClockMatrix™ family of devices - high-performance, precision timing solutions designed to simplify clock designs for applications with up to 100 Gbps interface speeds.

They can be used anywhere in a system to perform critical timing functions, such as clock generation, frequency translation, jitter attenuation and phase alignment. A range of devices in the family support BBU, OTN, SyncE, synthesizer and jitter attenuator applications with several density options for each.

For more information, visit www.idt.com/clockmatrix.