ClockMatrix 系列器件是高性能、高精度时序解决方案,能为接口速度最大800Gpbs的应用简化时钟设计。

此器件可以用于系统中的任何地方,以执行关键的时序功能,如时钟生成、频率转换、抖动衰减和相位校准。此器件可用于在无线基带、DU、CU、RU、前传或回传网络上精确同步 IEEE 1588 时间戳单元 (TSU) 和 SyncE 端口。 此系列器件支持多个独立时钟通道:IEEE 1588 时钟合成;SyncE 时钟生成;抖动衰减和射频时钟生成(包括转换器的 SYSREF 生成)。 所有输入到输入、输入到输出和输出到输出相位偏差均可精确管理。 此器件输出的超低抖动时钟可以直接应用于112Gbps 运行的 SERDES,以及 CPRI/OBSAI、SONET/SDH ADC/DAC 和 IEEE 1588 TSU。 为了便于在 IEEE 1588 系统中实施同步,瑞萨电子可在有许可证的情况下,免费提供 PTP 时钟管理器软件。

主要特征包括:

- 灵活 – PLL 通道可单独配置为合成器、抖动衰减器或DCO

- 集成 – 单个封装提供最多 8 个 DPLL 和 14 路输出

- 性能 – RMS 抖动低至 88fs(典型值)

- 标准合规 – IEEE 1588、OTN 和 SyncE

- 可编程 – I2C、SPI 或 OTP

- 设备监控 – 一种内置功能,用于监控参考时钟输入、DPLL 和 APLL 失锁、保持状态

- 多种尺寸可选 – 144-BGA 到 48-QFN,多种封装选择

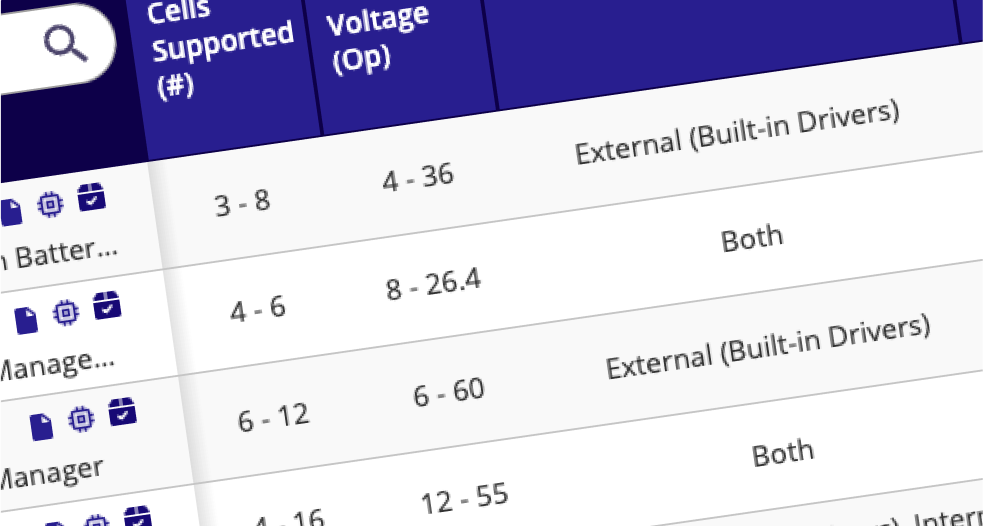

产品选择器

产品选择器