概览

简介

The 71V416 3.3V CMOS SRAM is organized as 256K x 16. All bidirectional inputs and outputs of the 71V416 are LVTTL-compatible and operation is from a single 3.3V supply. Fully static asynchronous circuitry is used, requiring no clocks or refresh for operation.

特性

- JEDEC Center Power / GND pinout for reduced noise.

- Equal access and cycle times

- – Commercial and Industrial: 10/12/15ns

- One Chip Select plus one Output Enable pin

- Bidirectional data inputs and outputs directly

- LVTTL-compatible

- Low power consumption via chip deselect

- Upper and Lower Byte Enable Pins

- Single 3.3V power supply

- Available in 44-pin, 400 mil plastic SOJ, 44-pin, 400 mil TSOP Type II, and 48-pin BGA packages

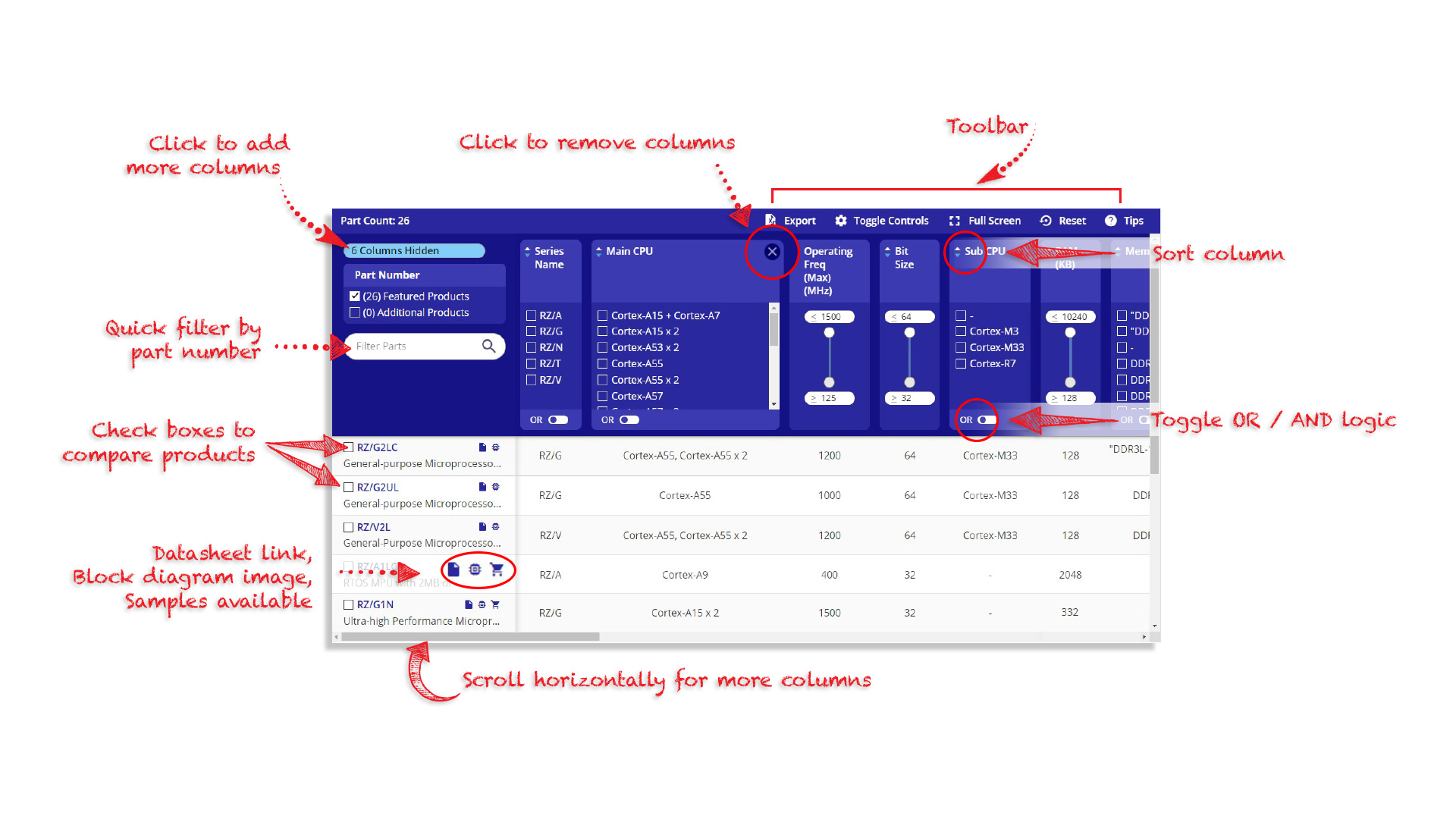

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.