概览

描述

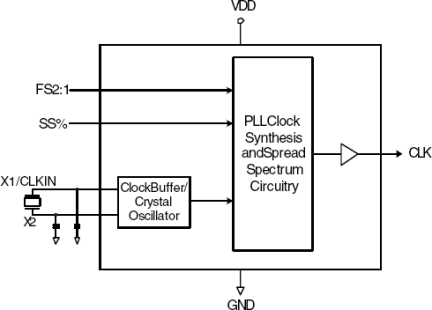

The 181-51 generates a low EMI output clock from a clock or crystal input. The device uses IDT's proprietary mix of analog and digital Phase-Locked Loop (PLL) technology to spread the frequency spectrum of the output, thereby reducing the frequency amplitude peaks by several dB. The 181-51 offers center spread selection of +/-0.625% and +/-1.875%. Refer to the MK1714-01/02 for the widest selection of input frequencies and multipliers. IDT offers a complete line of EMI reducing clock generators. Consult us when you need to remove crystals and oscillators from your board.

特性

- Pin and function compatible to Cypress W181-51

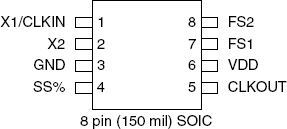

- Packaged in 8-pin SOIC

- Provides a spread spectrum output clock

- Accepts a clock input and provides same frequency dithered output

- Input frequency of 28 to 75 MHz for Clock input

- Peak reduction by 7dB - 14dB typical on 3rd - 19th odd harmonics

- Spread percentage selection for +/-0.625% and +/-1.875%

- Operating voltage of 3.3 V and 5 V

- Advanced, low-power CMOS process

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。

产品选项

当前筛选条件