概览

描述

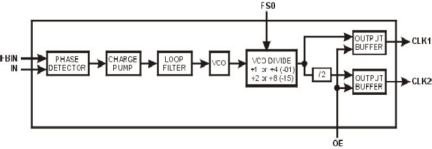

The 9173B provide the analog PLL circuit blocks to implement a frequency multiplier. Because the device is configured to use an external divider in the PLL clock feedback path, a large divider can be used to result in a large frequency multiplication ratio. This is useful when using a low frequency input clock to generate a high frequency output clock. The 9173B contains a phase detector, charge pump, loop filter, and voltage-controlled oscillator (VCO). The 674-01 can be used as the external feedback divider. A common application of the 9173B is the implementation of a video genlock circuit. Because of this, the 9173B inputs operate on the negative-going clock edge. The 9173B is pin and function compatible to the AV9173-01/15.

特性

- Phase-detector/VCO circuit block

- Ideal for genlock system

- Reference clock range 12 kHz to 1 MHz for full output clock range

- Output clock range of 1.25 to 75 MHz (-01), and 0.625 to 37.5 MHz (-15). See "Allowable Input Frequency to Output Frequency" table for conditions

- On-chip loop filter

- Single 5 V power supply

- Low power CMOS technology

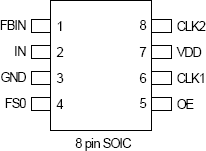

- 8-pin SOIC package

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件