概览

描述

2.5V Wide Range Frequency DDR1 Clock Driver (45MHz - 233MHz)

特性

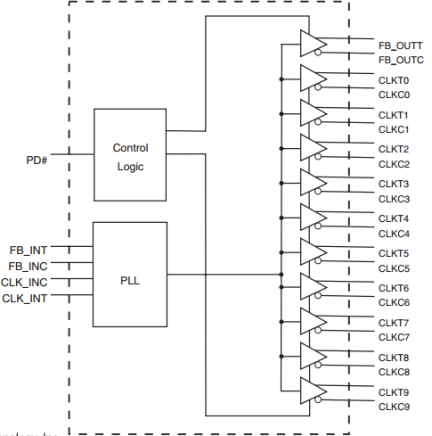

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- PD# for power management

- Spread Spectrum-tolerant inputs

- Auto PD when input signal removed

- Choice of static phase offset available, for easy board tuning

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

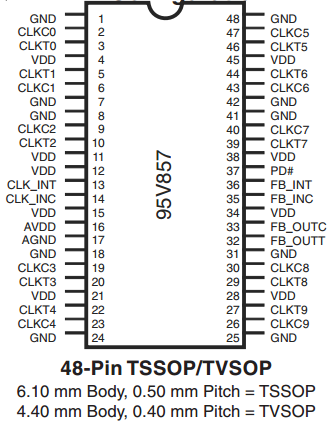

产品选项

当前筛选条件