概览

描述

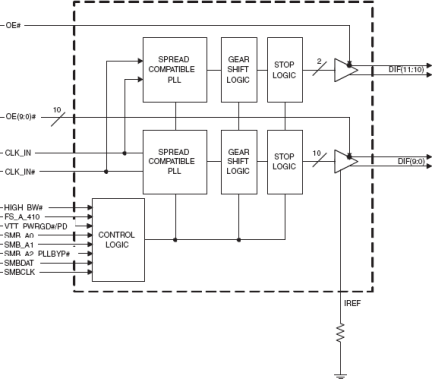

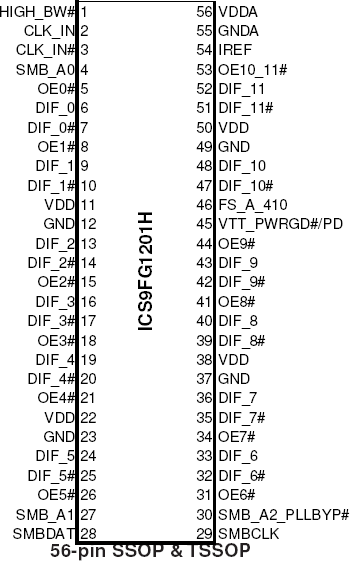

IDT9FG1201 follows the Intel DB1200G Differential Buffer Specification. This buffer provides 12 output clocks for CPU Host Bus, PCIe Gen1, or Fully Buffered DIMM applications. The outputs are configured with two groups. Both groups (DIF 9:0) and (DIF 11:10) can be equal to or have a gear ratio to the input clock. A differential CPU clock from a CK410B+ main clock generator, such as the IDT932S421, drives the IDT9FG1201. The IDT9FG1201 can provide outputs up to 400MHz.

特性

- Power up default is all outputs in 1:1 mode

- DIF_(9:0) can be "gear-shifted" from the input CPU Host Clock

- DIF_(11:10) can be "gear-shifted" from the input CPU Host Clock

- Spread spectrum compatible

- Supports output clock frequencies up to 400 MHz

- 8 Selectable SMBus addresses

- SMBus address determines PLL or Bypass mode

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件