概览

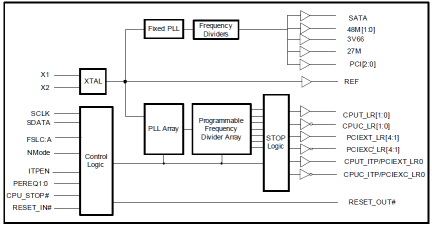

描述

Ultra low power main clock for VIA VX900 chipset

特性

- Features/Benefits:

- Supports programmable spread percentage and frequency

- Uses external 14.318MHz crystal, external crystal load caps are required for frequency tuning

- Low power differential clock outputs (No 50Ω resistor to GND needed)

- Programmable output skew

- Programmable watchdog safe frequency

- Integrated 33ohm series resistor on all differential outputs

- Low power supply voltage support for differential outputs

- Meets PCIEX Gen2 specifications

- Uses 1.5V core voltage for ultra low power design

- Output programmable slew rate controls

- Key Specifications:

- CPU output cycle-cycle jitter < 85ps

- PCIEX output cycle-cycle jitter < 125ps

- +/- 100ppm frequency accuracy for all output clocks

- CPU-AGP skew ~ 1.1ns typical

- AGP-PCIA skew ~ 1.06ns typical

- AGP-PCIB skew ~ 1.46ns typical

- CPU1-PCIA skew ~ 2.16ns typical

- CPU1-PCIB skew ~ 2.46ns typical

产品对比

应用

文档

相关文档

请登录后开启订阅

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 344 KB | |

| EOL 通告 | PDF 160 KB | |

| 产品变更通告 | PDF 39 KB | |

| 产品变更通告 | PDF 611 KB | |

| 产品变更通告 | PDF 611 KB | |

| 产品变更通告 | PDF 596 KB | |

| 产品变更通告 | PDF 544 KB | |

| 产品变更通告 | PDF 95 KB | |

| 产品变更通告 | PDF 50 KB | |

9 items

|

||

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件