概览

描述

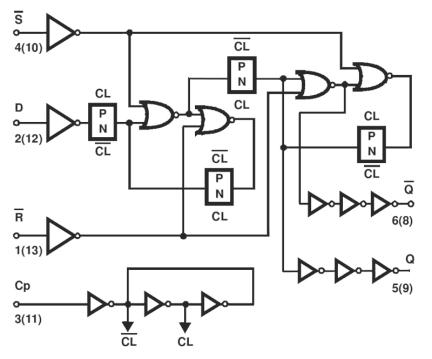

The Intersil ACTS74MS is a radiation hardened Dual D flip-flop with Set(s) and Reset (R). The logic level at data input is transferred to the output during the positive transition of the clock. The Set and Reset are independent from the clock and accomplished by a low level on the appropriate input. The ACTS74MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of the radiation hardened, high-speed, CMOS/SOS logic family. The ACTS74MS is supplied in a 14-lead Ceramic Flatpack (K suffix) or a 14-lead Ceramic Dual-In-Line package (D suffix).

特性

- Devices QML qualified in accordance with MIL-PRF-38535

- Detailed electrical and screening requirements are contained in SMD# 5962-96713 and Renesas' Intersil QM Plan

- 1.25 micron radiation hardened SOS CMOS

- Total dose >300K RAD (Si)

- Single Event Upset (SEU) immunity: <1 x 10-10 errors/bit/day (Typ)

- SEU LET threshold >100 MEV-cm2/mg

- Dose rate upset >1011 RAD (Si)/s, 20ns pulse

- Dose rate survivability >1012 RAD (Si)/s, 20ns pulse

- Latch-up free under any conditions

- Military temperature range -55 °C to +125 °C

- Significant power reduction compared to ALSTTL logic

- DC operating voltage range 4.5V to 5.5V

- Input logic levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input current ≤ 1µA at VOL, VOH

- Fast propagation delay 20ns (Max), 13ns (Typ)

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件