概览

描述

Support is limited to customers who have already adopted these products.

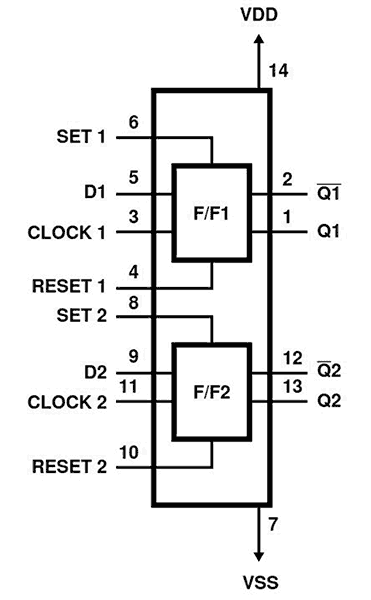

CD4013BMS consists of two identical, independent data type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs and Q and Q outputs. These devices can be used for shift register applications, and, by connecting Q output to the data input, for counter and toggle applications. The logic level present at the D input is transferred to the Q output during the positive going transition of the clock pulse. Setting or resetting is independent of the clock and is accomplished by a high level on the set or reset line, respectively. The CD4013BMS is supplied in these 14 lead outline packages: Braze Seal DIP H4Q Frit Seal DIP H1B Ceramic Flatpack H3W

特性

- High-Voltage Type (20V Rating)

- Set-Reset Capability

- Static Flip-Flop Operation - Retains State Indefinitely With Clock Level Either "High" Or "Low"

- Medium-Speed Operation - 16 MHz (typ.) Clock Toggle Rate at 10V

- Standardized Symmetrical Output Characteristics

- 100% Tested for Quiescent Current at 20V

- Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and +25°C

- Noise Margin (Over Full Package Temperature Range): 1V at VDD = 5V 2V at VDD = 10V 2.5V at VDD = 15V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件