概览

描述

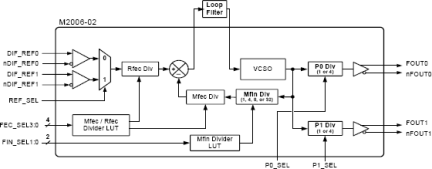

The M2006-02 is a Voltage Controlled SAW Oscillator (VCSO) based clock generator PLL designed for clock frequency translation and jitter attenuation. The device supports both forward and inverse FEC (Forward Error Correction) clock multiplication ratios, pin-selected from pre-programming look-up tables.

特性

- Pin-selectable PLL divider ratios support forward and inverse FEC ratio translation, including:

- 255/238 (OTU1) Mapping and 238/255 De-mapping

- 255/237 (OTU2) Mapping and 237/255 De-mapping

- 255/236 (OTU3) Mapping and 236/255 De-mapping

- Supports input reference and VCSO frequencies up to 700MHz, supports loop timing modes (Specify VCSO frequency at time of order)

- Low phase jitter < 0.5ps RMS typical (12kHz to 20MHz or 50kHz to 80MHz)

- Supports active switching between inverse-FEC and non-FEC clock ratios (same VCSO center frequency)

- Ideal for complex ratio FEC ratio translation and for use with an unstable reference (i.e., similar to the M2006-12 - and pin-compatible - but without the Hitless Switching and Phase Build-out functions)

- Commercial and Industrial temperature grades

- Single 3.3V power supply

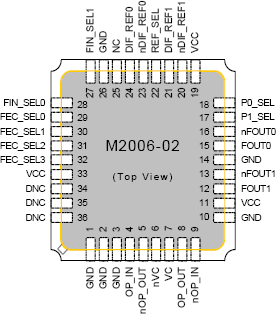

- Small 9mm x 9mm SMT (surface mount) package

- Pb-free/Compliant to EC RoHS Directive (RoHS 6/6)

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件