概览

描述

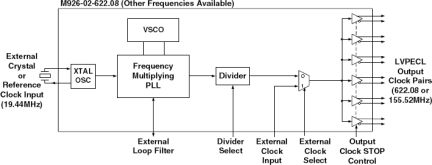

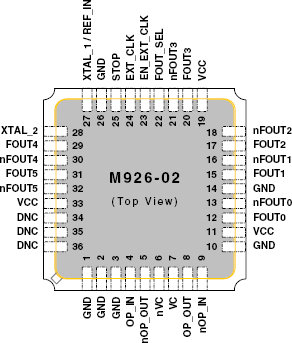

The M926-02 is a Phase-Locked Loop (PLL) based clock generator that uses an internal Voltage Controlled SAW Oscillator (VCSO) to produce a very low jitter output clock. From the M926-02-622.0800, an output clock frequency of 622.08 or 155.52MHz is provided from six LVPECL clock output pairs. (Other frequencies are available; consult the factory.) The accuracy of the output frequency is assured by the internal PLL that phase-locks the internal VCSO to the reference input frequency (19.44MHz for the M926-02-622.0800). The input reference can either be an external crystal, utilizing the internal crystal oscillator, or a stable external clock source such as a packaged crystal oscillator.

特性

- Output clock frequency range: 150MHz to 700MHz (Consult the factory for frequency availability)

- Selectable divider chooses one of two frequencies

- Six identical LVPECL output pairs (same frequency)

- Jitter 0.7ps RMS (at 622.08MHz, over 12kHz to 20MHz), typ.

- Ideal for OC-48/STM-16 clock reference

- Output-to-output skew < 100ps

- External XTAL or LVCMOS reference input

- Selectable external feed-through clock input

- STOP clock control (Logic 1 stops output clocks)

- Integrated SAW (surface acoustic wave) delay line

- Single 3.3V power supply

- Small 9mm x 9mm SMT (surface mount) package

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件