概览

描述

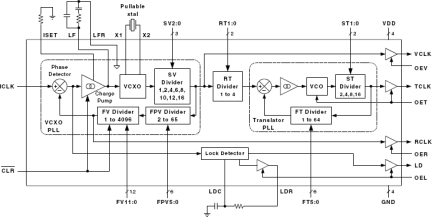

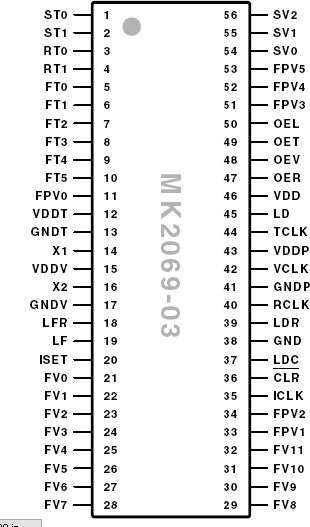

The MK2069-03 is a Voltage Controlled Crystal Oscillator (VCXO) based clock generator that offers system synchronization, jitter attenuation, and frequency translation. It can accept an input clock over a wide range of frequencies and produces a de-jittered, low phase noise clock output. The device is optimized for user configuration by providing access to all major PLL divider functions. No power-up programming is needed as configuration is pin selected. External VCXO loop filter components provide an additional level of performance tailoring. The MK2069-03 features a very wide range VCXO PLL feedback divider, allowing high-frequency multiplication ratios and therefore the input of very low input reference frequencies. The lock detector (LD) output serves as a clock status monitor. The clear (CLR) input enables rapid synchronization to the phase of a newly selected input clock while eliminating the generation of extra clock cycles and wander caused by memory in the PLL feedback divider. CLR also serves as a temporary holdover function when kept low.

特性

- Wide range VCXO PLL feedback divider allows high-frequency multiplication ratios and the input of very low input reference frequencies

- Input clock frequency of <1kHz to 13.5MHz

- Output clock frequency of 500kHz to 160MHz

- PLL lock status output

- VCXO-based clock generation offers very low jitter and phase noise generation, even with low frequency or jittery input clock.

- PLL Clear function (CLR input) allows the VCXO to free-run, offering a short-term holdover function.

- 2nd PLL provides frequency translation of VCXO PLL to higher or alternate output frequencies.

- Device will free-run in the absence of an input clock (or stopped input clock) based on the VCXO frequency pulled to minimum frequency limit.

- Low-power CMOS technology

- 56-pin TSSOP package

- Single 3.3V power supply

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件