概览

描述

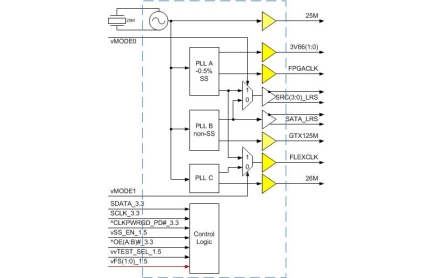

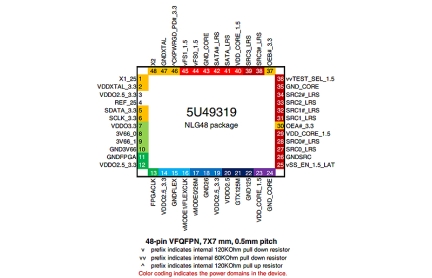

The IDT5U49319 is a very low power clock for Freescale P10xx and P20xx MCU’s. It uses a 1.5V core and Low-Power HCSL (LP-HCSL) differential outputs for minimal power consumption. The SATA and SRC outputs are PCIe Gen1/2 compatible.

特性

- Various outputs are configurable to run in power down; supports Wake_On_LAN

- FPGA clock frequency is selectable via SMBus; allows low-power system standby

- Strapping pin sources SRC outputs from either spreading or non-spreading PLL; maximum system flexibility

- FLEX clock is pin selectable to be FPGA clock or USB PHY clock; maximum system flexibility

- TEST pin tri-states all outputs; speeds up board test

- External 25MHz crystal; supports tight ppm

- OE# pins; support SRC power management

- Low power differential clock outputs; reduced power and board space

- Differential outputs internally terminated to 100ohm differential impedance; reduced board space

- Space-saving 7x7mm 48-pin VFQFPN with 0.5mm pad pitch; reduced board space without the need for fine pitch assembly techniques

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件