概览

描述

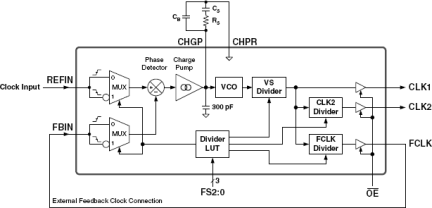

The MK1575-01 is a clock recovery Phase-Locked Loop (PLL) designed for clock synthesis and synchronization in cost sensitive applications. The device is optimized to accept a low-frequency reference clock to generate a high-frequency data or graphics pixel clock. External loop filter components allow tailoring of loop frequency response characteristics. For low jitter / phase noise requirements refer to the MK2069 products.

特性

- Long-term output jitter <2 nsec over 10 ?sec period

- External PLL clock feedback path enable "zero delay" I/O clock skew configuration

- Selectable internal feedback divider provides popular telecom and video clock frequencies (see tables below)

- Can optionally use external feedback divider to generate other output frequencies.

- Single 3.3 V supply, low-power CMOS

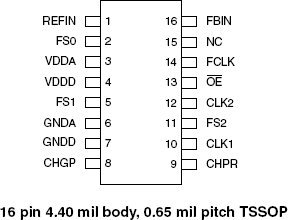

- Power-down mode and output tri-state (pin OE)

- Packaged in 16-pin TSSOP

- Pb (lead) free package

- Industrial temperature range available

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件