概览

描述

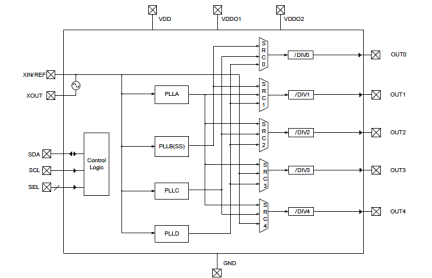

The 5P49EE502 is a programmable clock generator intended for low power, battery operated consumer applications. There are four internal PLLs, each individually programmable, allowing for up to five different output frequencies. The frequencies are generated from a single reference clock. The reference clock can come from either a TCXO or fundamental mode crystal. The 5P49EE502 can be programmed through the use of the I2C interfaces. The programming interface enables the device to be programmed when it is in normal operation or what is commonly known as in system programmable. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up. Each of the four PLLs has an 8-bit reference divider and a 11-bit feedback divider. This allows the user to generate four unique non-integer-related frequencies. The PLL loop bandwidth is programmable to allow the user to tailor the PLL response to the application. For instance, the user can tune the PLL parameters to minimize jitter generation or to maximize jitter attenuation. Spread spectrum generation is supported on one of the PLLs. Spread spectrum generation is supported on one of the PLLs. The device is specifically designed to work with display applications to ensure that the spread profile remains consistent for each HSYNC in order to reduce ROW noise. It also may operate in standard spread spectrum mode. There are total five 8-bit output dividers. The outputs are connected to the PLLs via the switch matrix. The switch matrix allows the user to route the PLL outputs to any output bank. This feature can be used to simplify and optimize the board layout. In addition, each output's slew rate and enable/disable function can be programmed.

特性

- Four internal PLLs

- Internal non-volatile EEPROM

- Internal I2C EEPROM master interface

- FAST (400kHz) mode I2C serial interfaces

- Input Frequencies – TCXO: 10 MHz to 40 MHz – Crystal: 8 MHz to 30 MHz

- Output Frequency Ranges: kHz to 120 MHz

- Each PLL has an 8-bit reference divider and a 11-bit feedback-divider

- 8-bit output-divider blocks

- One of the PLLs support Spread Spectrum generation capable of configuration to pixel rate, with adjustable modulation rate and amplitude to support video clock with no visible artifacts

- I/O Standards: – Outputs - 1.8V/2.5V/3.3 V LVTTL/ LVCMOS

- 2 independent adjustable VDDO groups.

- Programmable Slew Rate Control

- Programmable Loop Bandwidth Settings

- Programmable output inversion to reduce bimodal jitter

- Individual output enable/disable

- Power-down/Sleep mode – 10μA max in power down mode

- 1.8V VDD Core Voltage

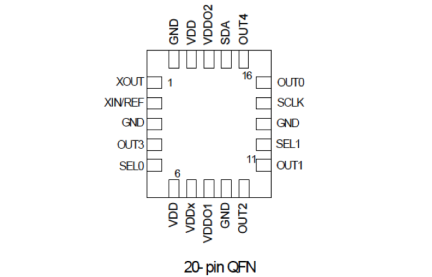

- Available in 20pin 3x3mm QFN packages

- -40 to +85 C Industrial Temp operation

产品对比

应用

设计和开发

软件与工具

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件

视频和培训

Description

Transcript