概览

描述

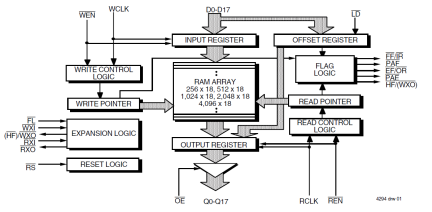

The 72V235 is a 2K x 18 first-in, first-out memory with clocked read and write controls. It is a 3.3V version of the 72235 FIFO and is applicable for a wide variety of data buffering needs, such as optical disk controllers, Local Area Networks (LANs), and interprocessor communication. It has 18-bit input and output ports. The Read Clock(RCLK) can be tied to the Write Clock for single clock operation or the two clocks can run asynchronous of one another for dual-clock operation.

特性

- 10 ns read/write cycle time

- 5V input tolerant

- IDT Standard or First Word Fall Through timing

- Single or double register-buffered Empty and Full flags

- Easily expandable in depth and width

- Asynchronous or coincident Read and Write Clocks

- Asynchronous or synchronous programmable Almost-Empty and Almost-Full flags with default settings

- Half-Full flag capability

- Output enable puts output data bus in high-impedance state

- Available in 64-pin TQFP and STQFP packages

- Industrial temperature range (–40C to +85C) is available

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。

产品选项

当前筛选条件