概览

描述

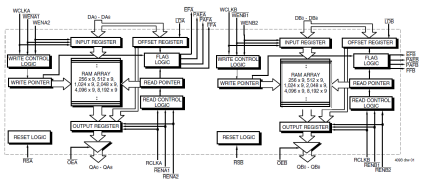

The 72V801is a 256 x 9 dual synchronous FIFO that is functionally equivalent to two 72V201 FIFOs in a single package with all associated control, data, and flag lines assigned to separate pins. Each FIFOs has a 9-bit input and output data port. The Read Clock can be tied to the Write Clock for single clock operation or the two clocks can run asynchronous of one another for dual clock operation.

特性

- Offers optimal combination of capacity, speed, and design flexibility in small footprint

- Ideal for prioritization, bidirectional, and width expansion applications

- 10 ns read/write cycle time

- 5V input tolerant

- Separate control lines and data lines for each FIFO

- Separate Empty, Full, programmable Almost-Empty and Almost-Full flags for each FIFO

- Enable puts output data lines in high-impedance state

- Available in 64-pin TQFP and STQFP packages

- Industrial temperature range (–40C to +85C) is available

产品对比

应用

设计和开发

产品选项

当前筛选条件