概览

描述

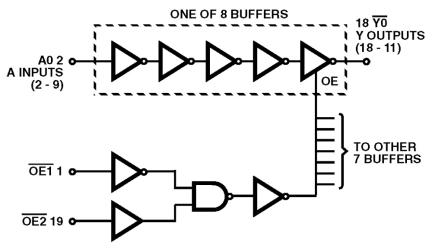

The Intersil HCTS540MS is a radiation hardened inverting octal buffer/line driver, with two active-low output enables. The output enable pins (OE1 and OE2) control the three-state outputs. If either enable is high, the outputs will be the high impedance state. For data output, both enables (OE1 and OE2) must be low. The HCTS540MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of the radiation hardened, high-speed, CMOS/SOS logic family. The HCTS540MS is supplied in a 20-lead ceramic flatpack (K suffix) or an SBDIP package (D suffix).

特性

- 3 micron radiation hardened CMOS SOS

- Total dose 200K RAD (Si)

- SEP effective LET no upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) immunity <2 x 10-9 errors/ bit-day (Typ)

- Dose rate survivability: >1 x 1012 RAD (Si)/s

- Dose rate upset >1010 RAD (Si)/s 20ns pulse

- Latch-up free under any conditions

- Fanout (over temperature range)

- Bus driver outputs 15 LSTTL loads

- Military temperature range: -55 °C to +125 °C

- Significant power reduction compared to LSTTL ICs

- DC operating voltage range: 4.5V to 5.5V

- LSTTL input compatibility

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input current levels Ii ≤5µA at VOL, VOH

产品对比

应用

文档

相关文档

请登录后开启订阅

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 413 KB | |

| 宣传手册 | PDF 467 KB | |

| 涨价通告 | PDF 360 KB | |

| 其他 | ||

| 产品咨询 | PDF 499 KB | |

| 产品变更通告 | PDF 230 KB | |

| 应用笔记 | PDF 224 KB | |

7 items

|

||

设计和开发

模型

ECAD 模块

点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。

产品选项

当前筛选条件