概览

描述

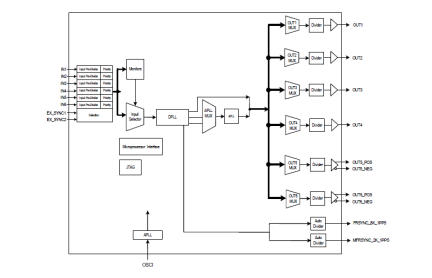

The 82V3398 is an integrated, single-chip solution for the Synchronous Equipment Timing Source (SETS) for Stratum 3, 4E, 4, SMC, EECOption1, EEC-Option2 clocks in SONET/SDH/Synchronous Ethernet equipment, DWDM, and wireless base stations. The device consists of a high-quality and configurable DPLL to provide a system clock for node timing synchronization within a SONET/SDH/Synchronous Ethernet network.

特性

- Integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 3, 4E, 4, SMC, EEC-Option 1, and EEC-Option 2 clocks

- Hitless reference switching to minimize DPLL output phase transients

- Programmable input-to-output phase offset adjustment

- Provides 6 output clocks from 1Hz (1PPS) to 644.53125MHz

- Provides 6 input clocks from 1Hz (1PPS) to 625MHz

- Internal DCO controlled by an external processor for IEEE 1588 clock generation

- Free-Run, Locked, and Holdover modes

- Automatic hitless selected input clock switch on clock failure

- 2kHz, 4kHz, 8kHz, or 1PPS frame sync input, 2kHz, 8kHz, or 1PPS frame sync output

- Output clocks for BITS, GPS, 3G, GSM, etc.

- PECL/LVDS and CMOS input/output technologies

- Master/Slave feature for system protection against single-chip failure

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件