封装信息

| CAD 模型: | View CAD Model |

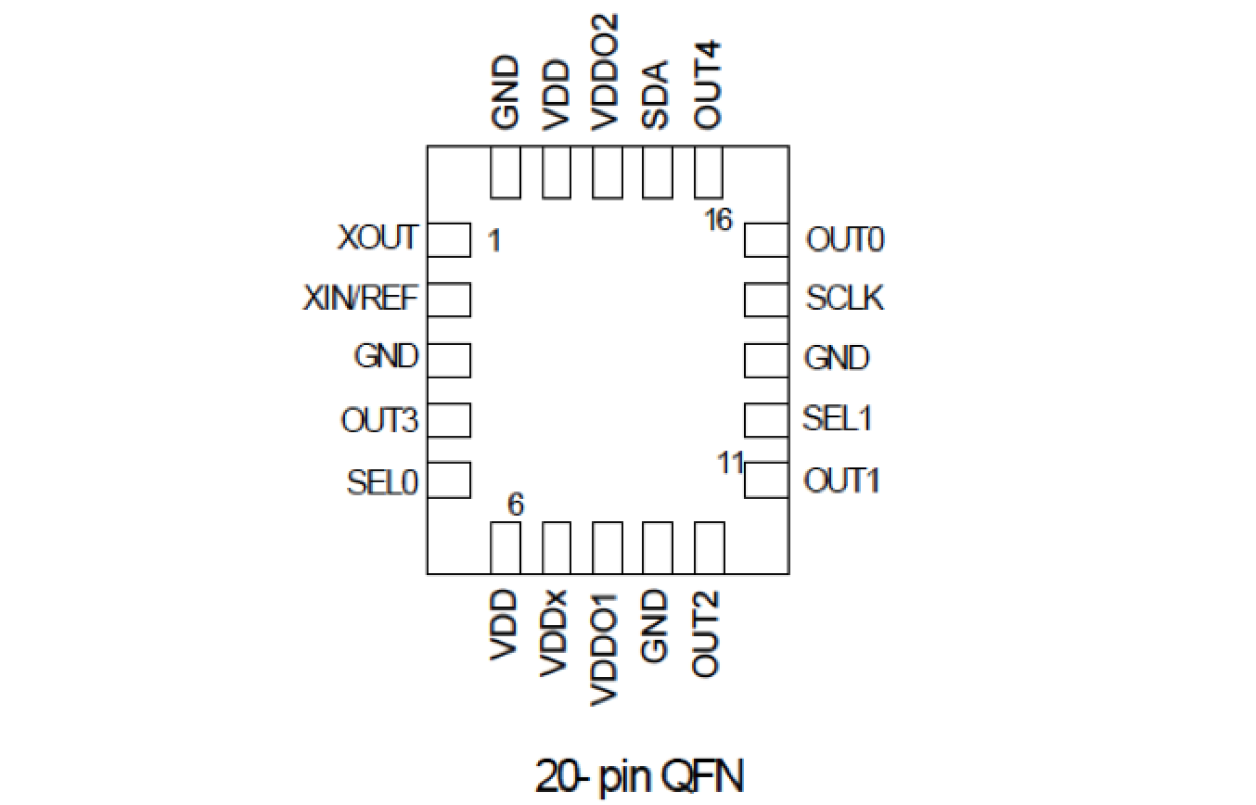

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NDG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 3.0 x 3.0 x 1.0 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Country of Assembly | THAILAND |

| Country of Wafer Fabrication | TAIWAN, USA |

| Advanced Features | Programmable Clock, Spread Spectrum, Reference Output |

| Core Voltage (V) | 1.8 |

| Family Name | VersaClock 3 LP |

| Input Freq (MHz) | 40 |

| Input Type | Crystal, LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 3 |

| MOQ | 2500 |

| Output Banks (#) | 5 |

| Output Freq Range (MHz) | 0.001 - 120 |

| Output Skew (ps) | 200 |

| Output Type | LVCMOS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Outputs (#) | 5 |

| Package Area (mm²) | 9 |

| Period Jitter Max P-P (ps) | 100 |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 3.0 x 3.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Product Category | VersaClock, Programmable Clocks |

| Prog. Clock | Yes |

| Prog. Interface | I2C, EEPROM |

| Reel Size (in) | 13 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 3 |

有关 5P49EE502 的资源

描述

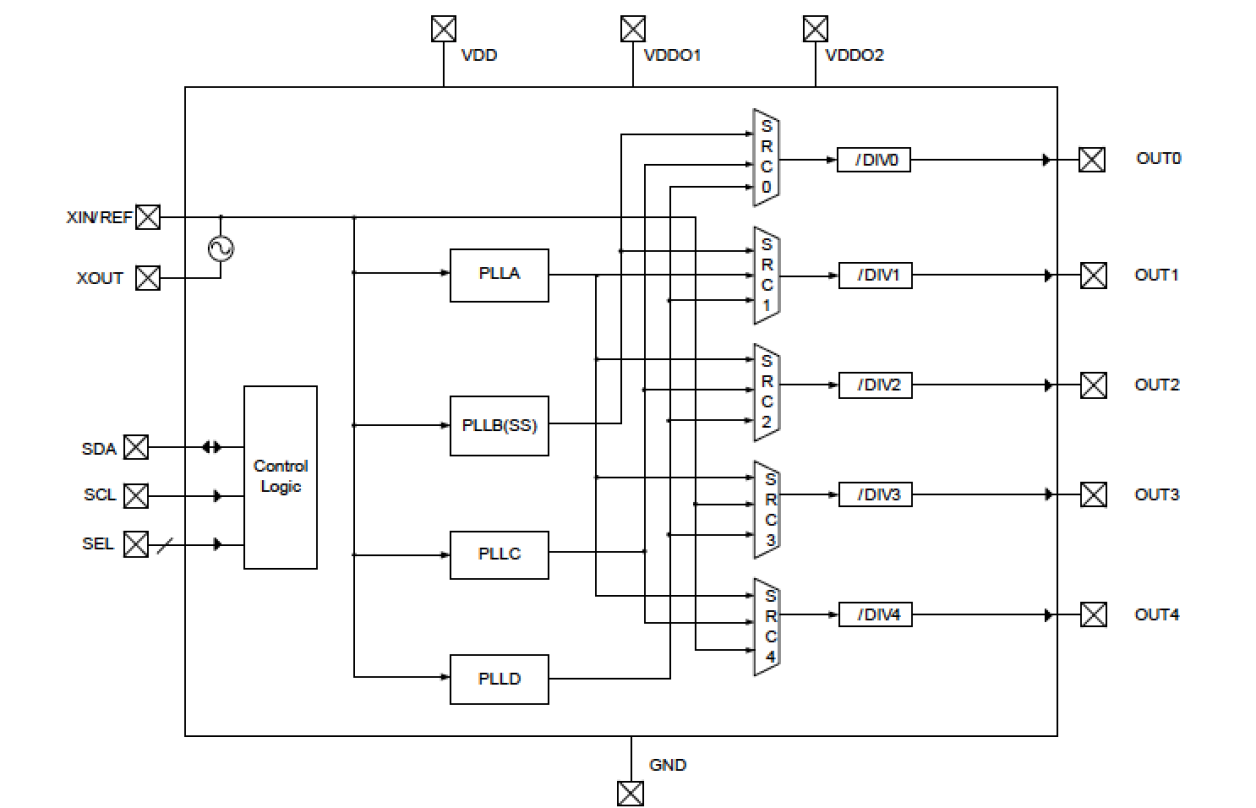

The 5P49EE502 is a programmable clock generator intended for low power, battery operated consumer applications. There are four internal PLLs, each individually programmable, allowing for up to five different output frequencies. The frequencies are generated from a single reference clock. The reference clock can come from either a TCXO or fundamental mode crystal. The 5P49EE502 can be programmed through the use of the I2C interfaces. The programming interface enables the device to be programmed when it is in normal operation or what is commonly known as in system programmable. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up. Each of the four PLLs has an 8-bit reference divider and a 11-bit feedback divider. This allows the user to generate four unique non-integer-related frequencies. The PLL loop bandwidth is programmable to allow the user to tailor the PLL response to the application. For instance, the user can tune the PLL parameters to minimize jitter generation or to maximize jitter attenuation. Spread spectrum generation is supported on one of the PLLs. Spread spectrum generation is supported on one of the PLLs. The device is specifically designed to work with display applications to ensure that the spread profile remains consistent for each HSYNC in order to reduce ROW noise. It also may operate in standard spread spectrum mode. There are total five 8-bit output dividers. The outputs are connected to the PLLs via the switch matrix. The switch matrix allows the user to route the PLL outputs to any output bank. This feature can be used to simplify and optimize the board layout. In addition, each output's slew rate and enable/disable function can be programmed.