封装信息

| CAD 模型: | View CAD Model |

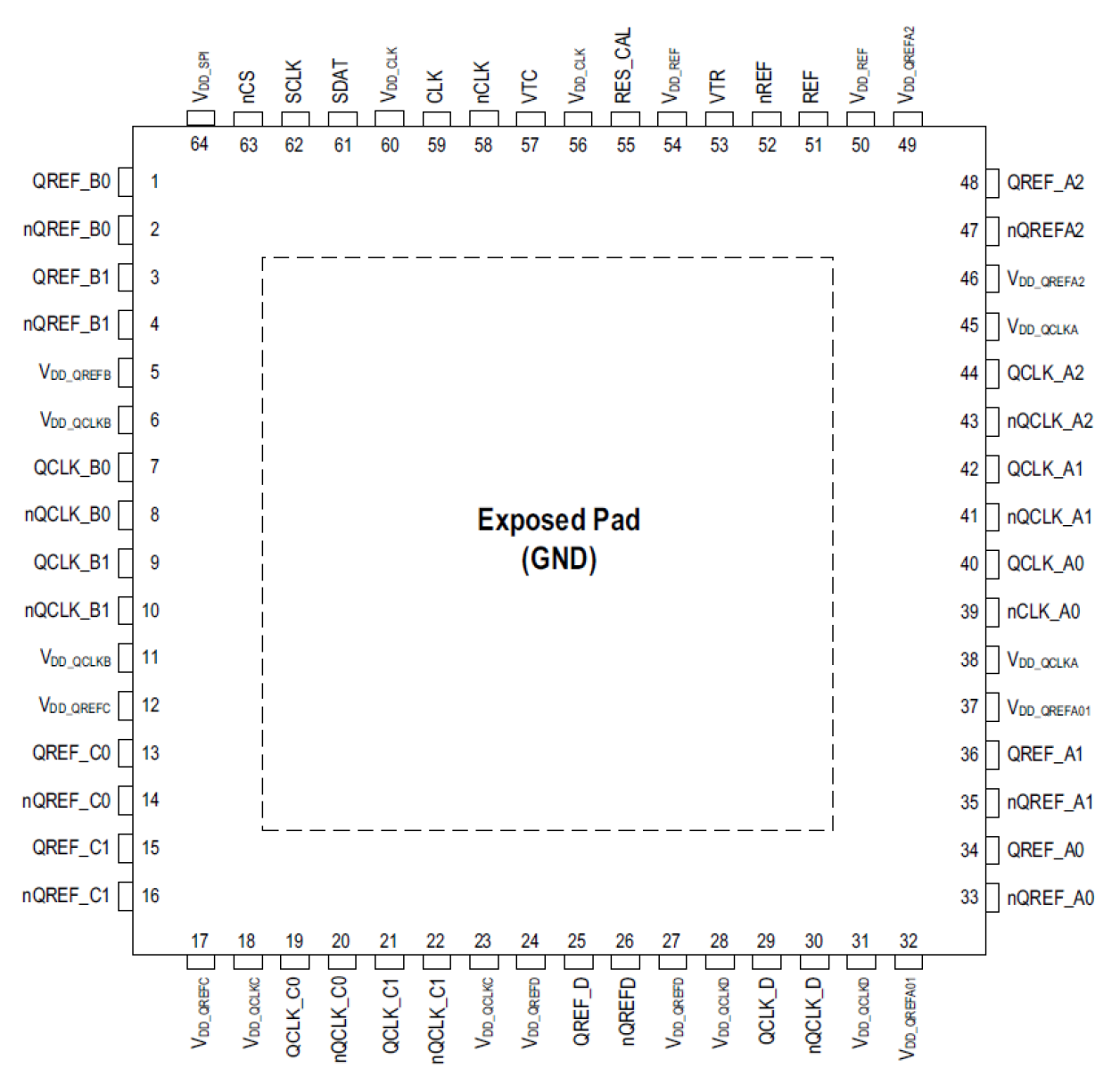

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG64 |

| Lead Count (#): | 64 |

| Pkg. Dimensions (mm): | 9.0 x 9.0 x 0.9 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 64 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 207 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C (Tc ≤ 105°C) |

| Country of Assembly | CHINA |

| Country of Wafer Fabrication | SINGAPORE |

| 105°C Max. Case Temp. | 1 |

| Adjustable Phase | Yes |

| Advanced Features | JESD204B, Dual Buffer, Individual output bank enable, Individual output enable, Per-bank divider, Universal outputs |

| Channels (#) | 2 |

| Core Voltage (V) | 3.3 |

| Divider Value | 1, 2, 4, 8, 12, 16 |

| Function | Buffer, Divider |

| Input Freq (MHz) | 3000 |

| Input Type | LVPECL, LVDS |

| Inputs (#) | 2 |

| Length (mm) | 9 |

| Longevity | 2040 4月 |

| MOQ | 207 |

| Noise Floor (dBc/Hz) | -158.8 |

| Output Banks (#) | 4 |

| Output Freq Range (MHz) | 3000 |

| Output Skew (ps) | 100 |

| Output Type | LVPECL, LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 16 |

| Package Area (mm²) | 81 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 9.0 x 9.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Price (USD) | $11.7713 |

| Requires Terms and Conditions | Requires acceptance of Terms and Conditions |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 9 |

| 已发布 | No |

有关 8V79S680 的资源

描述

8V79S680 是一款完全集成的时钟和 SYSREF 信号扇出缓冲器,适用于 JESD204B 应用。 该器件是专为无线基站无线电设备电路板设计的高性能时钟和转换器同步解决方案,符合 JESD204B 子类 0、1 和 2 标准。 该器件的主要功能是分配和扇出由 JESB204B 时钟发生器(如 8V19N480)生成的高频时钟和低频系统参考信号,从而扩展其扇出功能并提供额外的相位延迟。 8V79S680 经过优化,可提供相位噪声极低的时钟和精确、相位可调的 SYSREF 同步信号,满足 GSM、WCDMA、LTE、LTE-A 无线电板实施的要求。低偏移输出、低器件间偏移特性和快速输出上升/下降时间有助于系统设计实现跨器件的确定性时钟和 SYSREF 相位关系。

该器件将输入时钟和 JESD204B SYSREF 信号分配到四个扇出通道。 在每个通道中,输入时钟和 SYSREF 信号均扇出到多个时钟(QCLK)和 SYSREF(QREF)输出。 时钟信号可以在每个通道中进行分频。 可配置的相位延迟电路可用于时钟和 SYSREF 信号。 所有信号路径中的传播延迟都是完全确定的,以支持一个器件内时钟和 SYSREF 信号之间的固定相位关系。 时钟分频器可以旁路,以实现低延迟时钟路径。 该器件可辅助实现器件内部分频器之间以及多个器件之间的同步,消除分频器在电源和配置周期之间引入的相位模糊性。

每个通道支持高达 3GHz 的时钟频率。 在另一种配置中,例如 JESD204B 子类 0 和 2,SYSREF(QREF)输出可配置为常规时钟输出,从而为器件添加额外的时钟扇出。

所有输出在幅度配置、输出信号端接方面都非常灵活,并允许直流和交流耦合。 不使用时可禁用输出并关断电源。 SYSREF 输出预偏置功能可防止开机故障,并实现系统同步信号的交流耦合。

该器件通过一个三线 SPI 串行接口进行配置。 该器件采用无铅(RoHS 6)64 引脚 VFQFN 封装。扩展的温度范围支持无线基础设施、电信和网络终端设备的要求。 该器件属于 IDT 高性能时钟系列。