概览

描述

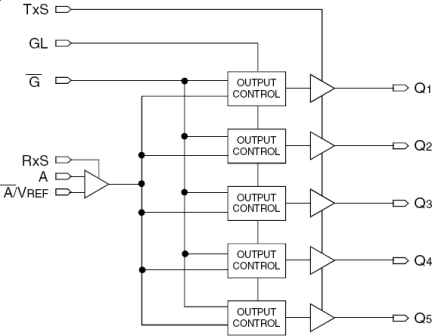

The 5T90533I 2.5V single data rate (SDR) clock buffer is a user-selectable single-ended or differential input to five single-ended outputs buffer built on advanced metal CMOS technology. The SDR clock buffer fanout from a single or differential input to five single-ended outputs reduces the loading on the preceding driver and provides an efficient clock distribution network. The 5T90533I can act as a translator from a differential HSTL, eHSTL, 1.8V/2.5V LVTTL, LVEPECL, or single-ended 1.8V/2.5V LVTTL input to HSTL, eHSTL, 1.8V/2.5V LVTTL outputs. Selectable interface is controlled by 3-level input signals that may be hard-wired to appropriate high-mid-low levels. Multiple power and grounds reduce noise.

特性

- Guaranteed Low Skew < 25ps (max)

- Very low duty cycle distortion

- High speed propagation delay < 2.5ns. (max)

- Up to 250MHz operation

- Very low CMOS power levels

- 1.5V VDDQ for HSTL interface

- Hot insertable and over-voltage tolerant inputs

- 3-level inputs for selectable interface

- Selectable HSTL, eHSTL, 1.8V / 2.5V LVTTL, or LVEPECL input interface

- Selectable differential or single-ended inputs and five single-ended outputs

- 2.5V VDD

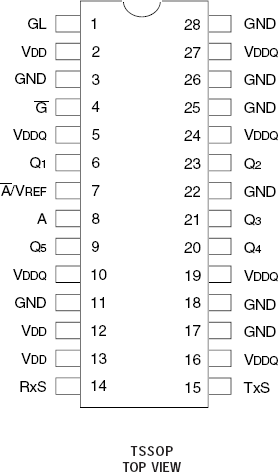

- Available in TSSOP package

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件