概览

描述

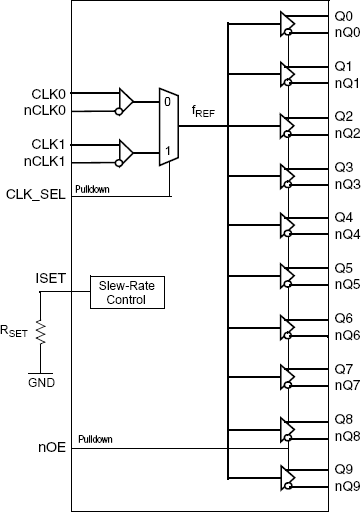

The 854110I is a high-performance differential LVDS clock fanout buffer. The device is designed for signal fanout of high-frequency, low phase-noise clock signals. The selected differential input signal is distributed to ten differential LVDS outputs. The 854110I is characterized to operate from a 2.5V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 854110I ideal for those clock distribution applications demanding well-defined performance and repeatability. The device offers an output slew rate control with four pre-set output transition times to solve crosstalk and EMI problems in complex board designs. A fail-safe input design forces the outputs to a defined state if differential clock inputs are open or shorted, see Table 3D.

特性

- Two differential input reference clocks

- Differential pair can accept the following differential input levels: LVPECL, LVDS

- Ten LVDS outputs

- Maximum clock frequency: 200MHz

- Output slew rate control

- Fail-safe differential inputs

- LVCMOS interface levels for all control inputs

- Output skew: 260ps (maximum), for fastest slew rate setting of 0.650 V/ns

- Part-to-part skew: 1.2ns (maximum)

- Full 2.5V supply voltage

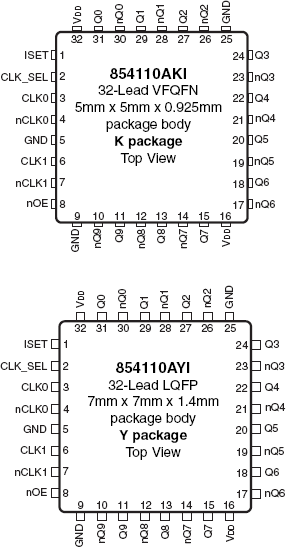

- Lead-free (RoHS 6) 32-Lead VFQFN and 32-Lead LQFP package

- -40°C to 85°C ambient operating temperature

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件