概览

描述

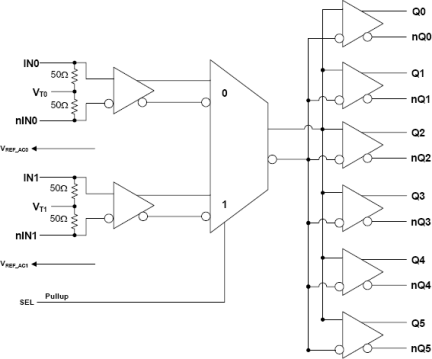

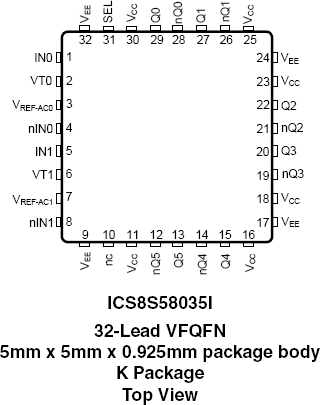

The 8S58035I is a high-speed 2-to-6 Differential-to-LVPECL fanout buffer. The 8S58035I is optimized for high-speed and very low output skew, making it suitable for use in demanding applications such as SONET, 1 Gigabit and 10 Gigabit Ethernet, and Fiber Channel. The internally terminated differential inputs and VREF_AC pins allow other differential signal families such as LVDS, LVDS, and CML to be easily interfaced to the input with minimal use of external components. The device also has a 2:1 MUX input, allowing for easy selection between two clock reference sources. The 8S58035I is packaged in a small 5mm x 5mm 32-pin VFQFN package which makes it ideal for use in space-constrained applications.

特性

- Six LVPECL outputs

- INx, nINx inputs can accept the following differential input levels: LVPECL, LVDS, CML

- 50Ω internal input termination to VT

- Two selectable differential input pairs

- Maximum output frequency: 3.2GHz

- Output Skew: 45ps (maximum)

- Part-to-part skew: 200ps (maximum)

- Additive phase jitter, RMS: 47fs (typical), (fREF = 622.08MHz, 12kHz to 20MHz, VCC = 3.3V)

- Propagation Delay: 580ps (maximum)

- LVPECL mode operating voltage supply range: VCC = 2.5V±5%, 3.3V±10%, VEE = 0V

- -40 °C to 85 °C ambient operating temperature

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件